Professional Documents

Culture Documents

MST776-I Mstar PDF

MST776-I Mstar PDF

Uploaded by

Bekti Yayang Mardya SaputraCopyright:

Available Formats

You might also like

- NET MAUI For C# Developers Jesse Liberty, Rodrigo Juarez, 2023 PacktDocument296 pagesNET MAUI For C# Developers Jesse Liberty, Rodrigo Juarez, 2023 PacktsvwerwolfNo ratings yet

- Manual C3VCM6 EngDocument50 pagesManual C3VCM6 Engpolliuy100% (1)

- TV 7 Mst726 Datasheet 535Document117 pagesTV 7 Mst726 Datasheet 535Денис ДенисовNo ratings yet

- Mstar Confidential for 深圳市江启科技有限公司 Internal Use Only: FeaturesDocument207 pagesMstar Confidential for 深圳市江启科技有限公司 Internal Use Only: FeaturesErroz RosadiNo ratings yet

- WDH-3500EC: Single Channel MPEG-2 SD EncoderDocument3 pagesWDH-3500EC: Single Channel MPEG-2 SD EncoderGoran BogdanovskiNo ratings yet

- DS-7304/7308/7316HWI-SH DVR: SeriesDocument3 pagesDS-7304/7308/7316HWI-SH DVR: SeriesakenterprisesosmuzaffarpurNo ratings yet

- OmniVision OV20880Document2 pagesOmniVision OV20880ady333No ratings yet

- Ledsync820C: Z Professional Solution To Drive Led WallsDocument3 pagesLedsync820C: Z Professional Solution To Drive Led WallsMauro Barragan SanchezNo ratings yet

- OmniVision OV16880Document2 pagesOmniVision OV16880ady333No ratings yet

- VP50 Dvdo 032807Document2 pagesVP50 Dvdo 032807Nizo Oeste PmdbNo ratings yet

- Hi3751 V320 Brief Data Sheet: Key Specifications Key FeaturesDocument4 pagesHi3751 V320 Brief Data Sheet: Key Specifications Key Featuresnani_amlprm5912No ratings yet

- Specification MST182VG V1.0Document10 pagesSpecification MST182VG V1.0RajeshNo ratings yet

- TSUMV59XUS MStar PDFDocument8 pagesTSUMV59XUS MStar PDFGustavo de Vargas DiasNo ratings yet

- Tsumv59xus PDFDocument8 pagesTsumv59xus PDFHamza Abbasi AbbasiNo ratings yet

- DS-7304/08/16HGHI-SH Series DVR: Physical InterfacesDocument2 pagesDS-7304/08/16HGHI-SH Series DVR: Physical InterfacesyansenNo ratings yet

- Selenio X100Document12 pagesSelenio X100Alexsandro Leite FigueirêdoNo ratings yet

- 8860 Brief DatasheetDocument5 pages8860 Brief DatasheetCourtney HernandezNo ratings yet

- Hi3798M V100 Brief Data SheetDocument3 pagesHi3798M V100 Brief Data Sheet王先生No ratings yet

- DS-7324/7332HWI-SH DVR: SeriesDocument2 pagesDS-7324/7332HWI-SH DVR: SeriesMauricio IbarraNo ratings yet

- IPM6102 64 Channels IP To Analog ModulatorDocument2 pagesIPM6102 64 Channels IP To Analog ModulatorElkaNo ratings yet

- Features: Video Decoder Scaling Engine/Panel InterfaceDocument10 pagesFeatures: Video Decoder Scaling Engine/Panel InterfaceMrbar BarstoynNo ratings yet

- M Vision Hd200Document2 pagesM Vision Hd200devon39No ratings yet

- Adv7340 7341 PDFDocument108 pagesAdv7340 7341 PDFTheotech EletronNo ratings yet

- Vigilance Series (New) PDFDocument2 pagesVigilance Series (New) PDFAbelRamadhanNo ratings yet

- Multi-Service Video Management Platform: Ultra SeriesDocument2 pagesMulti-Service Video Management Platform: Ultra SeriesJeronimo ReynosoNo ratings yet

- LCD TV ServiceDocument84 pagesLCD TV ServiceESLINC100% (1)

- Integrated Video Decoder and HDMI Receiver: Data SheetDocument20 pagesIntegrated Video Decoder and HDMI Receiver: Data SheetBruno MatonNo ratings yet

- схема и сервис мануал на английском Daytron DT32LUFB PDFDocument17 pagesсхема и сервис мануал на английском Daytron DT32LUFB PDFtonyroguez50No ratings yet

- Truvision NVR 22plus: Full Featured H.265 Network Video RecorderDocument2 pagesTruvision NVR 22plus: Full Featured H.265 Network Video RecorderAlexandra CăpraruNo ratings yet

- CV3393BL G 20 CultraviewDocument15 pagesCV3393BL G 20 CultraviewSamuel Ulises Leon GonzalezNo ratings yet

- Proview 7100Document4 pagesProview 7100Arif SriwidodoNo ratings yet

- Tmc-9700 Progressive Scan Full-Frame Color Camera: Imaging ProductsDocument4 pagesTmc-9700 Progressive Scan Full-Frame Color Camera: Imaging ProductsMonty^No ratings yet

- Castwin Encoder DME-8624S PDFDocument2 pagesCastwin Encoder DME-8624S PDFoscar carcassesNo ratings yet

- KX A4k8108n2Document1 pageKX A4k8108n2Brian MinhNo ratings yet

- TransdataDocument121 pagesTransdataFrancis P GarciaNo ratings yet

- Spesifikasi PLD 65UV5930Document4 pagesSpesifikasi PLD 65UV5930wulanluvspinkNo ratings yet

- lcd-mst6m48v2.0c 244 PDFDocument12 pageslcd-mst6m48v2.0c 244 PDFzulkarnain apriadiNo ratings yet

- Combined Pitot-Static Datasheet V2 0Document3 pagesCombined Pitot-Static Datasheet V2 0Fakhri GhrairiNo ratings yet

- 20221216 - 1864116 - UNV【Datasheet】XVR301-F Series-V1.00 EN - 958035 - 168459 - 0Document4 pages20221216 - 1864116 - UNV【Datasheet】XVR301-F Series-V1.00 EN - 958035 - 168459 - 0Alexis F Hernández BNo ratings yet

- DS-6916UDIBDecoder - V2.6.1Document4 pagesDS-6916UDIBDecoder - V2.6.1DILMER JAVIERNo ratings yet

- Visionav-Hd: Professional Audio and Video Capture CardDocument3 pagesVisionav-Hd: Professional Audio and Video Capture Cardorlando benavidesNo ratings yet

- Programmable 4K2K Video Signal Generator (Model: K-8890) : Displayport Hdmi MHLDocument2 pagesProgrammable 4K2K Video Signal Generator (Model: K-8890) : Displayport Hdmi MHLouyangxin1991No ratings yet

- Adv7393bcpz SMD Encoder Entegresi Lfcsp40 DatasheetDocument107 pagesAdv7393bcpz SMD Encoder Entegresi Lfcsp40 DatasheetSabri OkurNo ratings yet

- OmniVision OV4689Document2 pagesOmniVision OV4689Eric GirodNo ratings yet

- Cisco D9854Document8 pagesCisco D9854denismoraes.toNo ratings yet

- DS 9600ni STDocument3 pagesDS 9600ni STRaju RamNo ratings yet

- Vga To Cga Converter: MODEL: CV-02 Ver 1.1Document1 pageVga To Cga Converter: MODEL: CV-02 Ver 1.1Luis Otavio TrindadeNo ratings yet

- 8CH Multiviewer: Full HDDocument4 pages8CH Multiviewer: Full HDRobert Anderson Ordóñez BautistaNo ratings yet

- Multi-Service Video Management Platform: Ultra SeriesDocument2 pagesMulti-Service Video Management Platform: Ultra SeriesRodriguez JuanNo ratings yet

- Controller m70 4u e Datasheet20160815Document5 pagesController m70 4u e Datasheet20160815Agencia DigitalNo ratings yet

- Ds-6916udi (B)Document4 pagesDs-6916udi (B)LOURDES ESTHER DIEZ GUTIERREZNo ratings yet

- CV3393CH O 11 Specification V1.0Document22 pagesCV3393CH O 11 Specification V1.0Красимир КостадиновNo ratings yet

- OmniVision OV4689Document2 pagesOmniVision OV4689nilsNo ratings yet

- Digital TV Encoder ModulatorDocument5 pagesDigital TV Encoder ModulatorKaori MakimuraNo ratings yet

- DatasheetofDS-96128NI-M16 SNMP V4.61.410 20221208Document5 pagesDatasheetofDS-96128NI-M16 SNMP V4.61.410 20221208aaa.uae.itservicesNo ratings yet

- OmniVision OV9712-1DDocument2 pagesOmniVision OV9712-1Dady333No ratings yet

- BWFCPC-E8000 Multi Format HD EncoderDocument2 pagesBWFCPC-E8000 Multi Format HD EncoderSaeful AnwarNo ratings yet

- Single-Chip, Low Cost High-Definition HDMI 1.3 Video ProcessorDocument2 pagesSingle-Chip, Low Cost High-Definition HDMI 1.3 Video Processorpetetest_esNo ratings yet

- IV8WTESTDocument2 pagesIV8WTESTAbraham Lopez G.No ratings yet

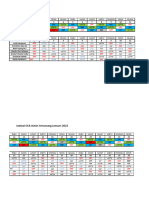

- Jadwal Olx Autos 2022-2Document41 pagesJadwal Olx Autos 2022-2Bekti Yayang Mardya SaputraNo ratings yet

- Diagnosa & RepairDocument8 pagesDiagnosa & RepairBekti Yayang Mardya SaputraNo ratings yet

- Ecs FT86Document1 pageEcs FT86Bekti Yayang Mardya SaputraNo ratings yet

- MST776-I Mstar PDFDocument12 pagesMST776-I Mstar PDFBekti Yayang Mardya SaputraNo ratings yet

- Marine Event Recorder: BergenDocument2 pagesMarine Event Recorder: BergenUFUKKKNo ratings yet

- Top 20 Matlab Interview Questions & Answers: 1) Explain What Is Matlab? Where Matlab Can Be Applicable?Document5 pagesTop 20 Matlab Interview Questions & Answers: 1) Explain What Is Matlab? Where Matlab Can Be Applicable?Shroni SharmaNo ratings yet

- Chapter 5 Documenting A NetworkDocument37 pagesChapter 5 Documenting A NetworkSYED AHMAD SHAUQI BIN SYED SHUHAIMINo ratings yet

- iOS 9 Day by DayDocument109 pagesiOS 9 Day by DayPhilli OneromNo ratings yet

- Automapper Documentation: Jimmy BogardDocument83 pagesAutomapper Documentation: Jimmy Bogardzafarkamal7No ratings yet

- Database System ArchitectureDocument21 pagesDatabase System ArchitectureDev BabbarNo ratings yet

- Universidad Del Magdalena Ingeniería Electrónica Diseño de Sistemas Digitales - Actividad Asincrónica 3Document3 pagesUniversidad Del Magdalena Ingeniería Electrónica Diseño de Sistemas Digitales - Actividad Asincrónica 3Angélica SamperNo ratings yet

- AC AnalysisDocument12 pagesAC AnalysisIan Benedict LavapieNo ratings yet

- CP1H Function BlocksDocument59 pagesCP1H Function BlocksSérgio Cardoso de OliveiraNo ratings yet

- Veeam Backup Azure Product OverviewDocument2 pagesVeeam Backup Azure Product Overviewsly_boss49No ratings yet

- Infinity Box PinFinderDocument25 pagesInfinity Box PinFinderDrago KraljNo ratings yet

- Ios Vs Android: Submitted To: Ms - Manmohak SandhuDocument11 pagesIos Vs Android: Submitted To: Ms - Manmohak SandhuSai Kiran100% (1)

- CH 12Document37 pagesCH 12miathegirl9No ratings yet

- Android Malware WhitepaperDocument13 pagesAndroid Malware Whitepaperjuhi_himanshiNo ratings yet

- Computer Organization and ArchitectureDocument12 pagesComputer Organization and ArchitecturepadmanabhanprathyushNo ratings yet

- Parallel ComputingDocument12 pagesParallel ComputingSaravanan Thangavelu100% (1)

- SWRAUTOTESTERDocument14 pagesSWRAUTOTESTERslawekNo ratings yet

- Wired ProtocolsDocument13 pagesWired Protocolsyouandme091223No ratings yet

- VMware AlignmentDocument2 pagesVMware Alignmentkuldeep_singh_144No ratings yet

- ABAP Outbound Proxy: CommunityDocument15 pagesABAP Outbound Proxy: CommunityRaviteja KanakaNo ratings yet

- Bitsler Script 2019 Hack For FreeDocument4 pagesBitsler Script 2019 Hack For FreeAbhimanyu ravidasNo ratings yet

- AGILE Refresher - Part 2Document61 pagesAGILE Refresher - Part 2rupesh naiduNo ratings yet

- Voltage and Current Divider Rules, Series, Parallel and Series-Parallel CircuitDocument13 pagesVoltage and Current Divider Rules, Series, Parallel and Series-Parallel CircuitMAHIRA TAJ A21ET0300No ratings yet

- A Feasibility Study On E-Class Record System: Eastern Samar State UniversityDocument45 pagesA Feasibility Study On E-Class Record System: Eastern Samar State UniversityjoshuaNo ratings yet

- Entuity EYE of The Storm Core EventsDocument186 pagesEntuity EYE of The Storm Core Eventsjesp_scribd100% (1)

- Django Interview QuestionsDocument4 pagesDjango Interview QuestionsAkbar AANo ratings yet

- P-Channel Enhancement Mode MOSFET: Product SummaryDocument5 pagesP-Channel Enhancement Mode MOSFET: Product SummaryAhmad Syafii LeongNo ratings yet

- Gujarat Technological University: Programming With Linux, Apache, Mysql, and PHP (Lamp)Document42 pagesGujarat Technological University: Programming With Linux, Apache, Mysql, and PHP (Lamp)Malathi SankarNo ratings yet

MST776-I Mstar PDF

MST776-I Mstar PDF

Uploaded by

Bekti Yayang Mardya SaputraOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

MST776-I Mstar PDF

MST776-I Mstar PDF

Uploaded by

Bekti Yayang Mardya SaputraCopyright:

Available Formats

MST776-I

Car TV Processor with PIP/POP and External SDRAM

Preliminary Product Brief Version 0.1

FEATURES

n Video Decoder n Video Processing

Ÿ Supports NTSC, PAL and SECAM video input Ÿ 2-D video de-interlacer

formats Ÿ Edge-oriented adaptive algorithm for smooth

Ÿ 2D NTSC and PAL comb-filter for Y/C low-angle edges

separation of CVBS input Ÿ PIP/POP with programmable size and location,

Ÿ Multiple CVBS and S-video inputs supports multi-video applications

司

Ÿ Supports Closed-caption and V-chip Ÿ 3-D video noise reduction for SDTV and 2-D

公

Ÿ Built-in anti-aliasing filter for analog-front-end video noise reduction for HDTV input

Ÿ ACC, AGC, and DCGC (Digital Chroma Gain Ÿ Brightness, contrast, saturation, and hue

Control) adjustment

限

n Analog Input

有

Ÿ 9-tap programmable multi-purpose FIR (Finite

技

Ÿ Supports RGB input format from PC, Impulse Response) filter

科 m

camcorders and GPS Ÿ Differential 3-band peaking engine

o

Ÿ Supports YCbCr inputs from conventional video Ÿ Vertical peaking

source and HDTV

鑫 .c

Ÿ Luminance Transient Improvement (LTI)

Ÿ Supports video input 480i, 480p, 576i, 576p,

泉 n

Ÿ Chrominance Transient Improvement (CTI)

a

聚 u

720p, 1080i; RGB input resolution in 640x480, Ÿ Black Level Extension (BLE)

市

800x480, 800x600(SVGA), and 1024x768(XGA)

u q

Ÿ White Level Extension (WLE)

.j

Ÿ 3-channel low-power 10-bit ADCs integration Ÿ Favor Color Compensation (FCC)

圳

for YCbCr or CVBS or S-Video; ADC frequency

w

Ÿ 3-channel gamma curve adjustment

up to 86MHz

深 w

Ÿ Independent 6 color of saturation, hue, and

w

Ÿ 3-channel 8-bit ADC for navigator RGB input; brightness control

ADC frequency up to 86MHz n Digital PWM Controller

Ÿ Supports RGB composite sync input (CSYNC), Ÿ Integrated general purpose digital PWM

SOY, SOG, HSYNC, and VSYNC control loop

Ÿ On-chip clock synthesizer and PLL Ÿ Programmable startup operating frequency

Ÿ Auto-position adjustment, auto-phase and period with output voltage regulation

adjustment, auto-gain adjustment, and Ÿ Programmable output current regulation;

auto-mode detection 40KHz~70KHz switching frequency, sync. to

n Digital Video Input HSYNC possible

Ÿ Supports ITU-R BT.656 digital video input and Ÿ Burst-mode or continuous-mode for output

progressive ITU-R BT.656 compatible input current regulation; 150Hz~300Hz burst-mode

format frequency, sync. to VSYNC possible

Ÿ Supports ITU-R BT.601 8/16-bit digital video Ÿ Programmable protection level for input

input voltage and fault detection

Ÿ Supports digital 666/888 input n LVDS/TTL Panel Interface

n Digital/Analog Output Ÿ Supports up to 8-bit single link LVDS

Ÿ 3-channel low-power 8-bit DAC for RGB output, Ÿ Supports up to 8-bit TTL panel output with

dynamic range 0.1-4.9 V TCON

Ÿ Supports digital panels up to 800x480,800x600

(SVGA), 960x540(QHD) and 1366x768(WXGA)

Version 0.1 -1- 11/23/2007

Copyright © 2007 MStar Semiconductor, Inc. All rights reserved.

Free Datasheet http://www.datasheet4u.com/

MST776-I

Car TV Processor with PIP/POP and External SDRAM

Preliminary Product Brief Version 0.1

Ÿ Programmable 24-bit (RGB888) digital output Ÿ Supports 10-bit gamma table

with HSYNC/VSYNC or 18-bit (RGB666) digital Ÿ Supports H/V sync out from CVBS for old NAVI

output with TCON system

Ÿ Supports various displaying modes Ÿ Built-in step-down PWM circuits for input 1.8V

Ÿ Supports horizontal panorama scaling and 3.3V

n 2D Graphics Engine Ÿ Built-in step-up boost circuits (for VGL and

Ÿ Line draw, rectangle draw/fill and color VGH)

expansion acceleration Ÿ DC/DC level adjustment circuit

Ÿ 16/256-color graphic OSD with two

司

Ÿ 16-bit data bus for external SDR DRAM frame

non-overlapping display windows buffer

公

限

Ÿ Graphic display path of 720x576 with Ÿ Supports up to 8MB external SDR DRAM

有

anti-flicker filter interface

Ÿ One video display path of 720x576 with H/V Ÿ Supports 1Mbx16 embedded SDR DRAM

scaling from 0.5 to 2

技

Ÿ Spread spectrum clocks

n Miscellaneous

科 m

Ÿ Optional 3.3V/5V TCON pads with

o

鑫 .c

Ÿ Built-in MCU programmable driving current

泉 n

Ÿ I2C bus interface for configuration setup Ÿ 216-pin LQFP package

BLOCK DIAGRAM 聚 u a

市 u q

圳 .j

深 ww

Digital RGB PIP/

Gamma

BT.656/601 ADC POP

w

Table

RGB Overlay

YPbPr TCON

Video Graphics To LCD

Y/C ADC Scaler

Decoder OSD VCOM Panel

CVBS

Touch Panel DC/DC

UART 2M bytes DPWM

Keypad GPIO MCU MIU

/ I2C SDRAM DPWM

Output

IR

8M bytes Feedback

SDRAM Voltage

Version 0.1 -2- 11/23/2007

Copyright © 2007 MStar Semiconductor, Inc. All rights reserved.

Free Datasheet http://www.datasheet4u.com/

MST776-I

Car TV Processor with PIP/POP and External SDRAM

Preliminary Product Brief Version 0.1

SYSTEM APPLICATION DIAGRAM

Flash / ROM 1.8/3.3V

Micro- PWM

Controller Step-Down

Back-light

TV / Cable Signal TV Tuner

司

Invertor

Video

公

Additional CVBS Decoder

DVD / VCD S-Video Signal

限

有

RGB ADC WVGA TFT Panel

Navigator TCON

800x480

HDTV YPbPr Signal YPbPr ADC

技

科 o m

鑫

Deinterlacer /

.c

泉 n

BT.656 TTL/LVDS

Scaler

聚 u a

2MB SDRAM

市 2MB SDRAM

u q

圳 w .j

深 w

GENERAL DESCRIPTION

w

The MST776-I is a high quality ASIC for Car TV and portable DVD player applications. It receives analog

NTSC/PAL/SECAM CVBS and S-Video inputs from TV tuners, DVD or VCR sources, including weak and distorted

signals, as well as analog RGB input from GPS systems. Automatic gain control (AGC) and 10-bit 3-channel

A/D converters provide high resolution video quantization. With automatic video source and mode detection,

users can easily switch and adjust variety of signal sources. Multiple internal adaptive PLLs precisely extract

pixel clock from video source and perform sharp color demodulation. PIP/POP is provided for multimedia

applications. Built-in line-buffer supports adaptive 2-D comb-filter, 2-D sharpening, and synchronization

stabler in a condensed manner. The output format of MST776-I supports 8-bit TTL or LVDS digital TFT-LCD

modules.

Version 0.1 -3- 11/23/2007

Copyright © 2007 MStar Semiconductor, Inc. All rights reserved.

Free Datasheet http://www.datasheet4u.com/

MST776-I

Car TV Processor with PIP/POP and External SDRAM

Preliminary Product Brief Version 0.1

PIN DIAGRAM (MST776-I)

VI_DATA[10]

VI_DATA[11]

VI_DATA[12]

VI_DATA[13]

VI_DATA[14]

VI_DATA[15]

VI_DATA[16]

VI_DATA[17]

VI_DATA[18]

VI_DATA[19]

VI_DATA[20]

VI_DATA[21]

VI_DATA[22]

VI_DATA[23]

VD_HSYNCO

VD_VSYNCO

AVDD_MPLL

VI_DATA[6]

VI_DATA[7]

VI_DATA[8]

VI_DATA[9]

MDATA[15]

MDATA[14]

MDATA[13]

MDATA[12]

MDATA[10]

MDATA[11]

HSYNCIN2

VSYNCIN2

MDATA[9]

MDATA[8]

MDATA[7]

MDATA[5]

MDATA[4]

MDATA[3]

MDATA[6]

MDATA[2]

MDATA[1]

MDATA[0]

VD_CLKO

VI_CLKIN

AVDD_MI

VDDP_33

VDDP_33

DQM[1]

DQM[0]

VDDC

VDDC

GND

GND

WEZ

GND

XIN

FB

216

215

214

213

212

211

210

209

208

207

206

205

204

203

202

201

200

199

198

197

196

195

194

193

192

191

190

189

188

187

186

185

184

183

182

181

180

179

178

177

176

175

174

173

172

171

170

169

168

167

166

165

164

163

XOUT 1 162 CASZ

GND 2 161 RASZ

VD[5] 3 Pin 1 160 CSZ

VD[4] 4 159 MCLK

VD[3] 5 158 MCLKE

VD[2] 6 157 BADR[0]

VD[1] 7 156 BADR[1]

VD[0] 8 155 MADR[3]

HSYNCIN1 9 154 MADR[2]

VSYNCIN1 10 153 GND

VCLAMP 11 152 VDDP_33

REFP 12 151 MADR[1]

REFM 13 150 MADR[0]

AVDD_33 14 149 MADR[10]

GND 15 148 MADR[11]

BINP 16 147 MADR[9]

SOGIN 17 146 MADR[8]

GINP 18 145 MADR[7]

RINP 19 144 MADR[6]

PBINP 20 143 MADR[5]

SOY 21 142 MADR[4]

YINP 22 141 DACR

YINM 23 140 DACG

PRINP 24 139 AVDD_DAC

PRINM 25 138 DACB

C1INP 26 137 GND

XXXXX

XXXXXXXX

MST776-I

C1INM 27 136 DAC_REFM

YS1INP 28 135 DAC_REFP

YS1INM 29 134 VCOM_DC

CVBS1P 30 133 VCOM_AC

CVBS2P 31 132 GND

AVDD_33 32 131 GND

GND 33 130 VDDC

AVDD_18 34 129 GND

PWM_REXT 35 128 AVDD_LPLL

AVDD_PWM 36 127 ROUT[7]

GND 37 126 ROUT[6]

PGOOD 38 125 ROUT[5]

PWM_FB1 39 124 ROUT[4]

SENSE1 40 123 ROUT[3]

VDDP50_PWM 41 122 ROUT[2]

PWMOUT1 42 121 ROUT[1]

GND 43 120 ROUT[0]

PWMOUT2 44 119 GOUT[7]

PWM_FB2 45 118 GOUT[6]

SENSE2 46 117 VDDP_33

VDDP50_PWM 47 116 GND

DRVBST 48 115 GOUT[5]

GND 49 114 GOUT[4]

CSBST 50 113 GOUT[3]

BOOSTON 51 112 GOUT[2]

FBBST 52 111 GOUT[1]

QOR 53 110 GOUT[0]

Q1 54 109 BOUT[7]

100

101

102

103

104

105

106

107

108

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

INT

HWRESET

SPI_SDO

VDDC

LHSYNC

SDA

LVSYNC

FB2_DPWM

FB1_DPWM

VIN

AVDD_DPWM

SAR_IN

UART1_RX

SPI_SCZ

UART1_TX

GND

GND

GND

CS

GND

DTCON[0]

BOUT[0]

BOUT[3]

BOUT[4]

BOUT[1]

BOUT[2]

BOUT[5]

BOUT[6]

VDDP50_TP

SPI_SCK

LCK

WAKEUP

SCL

Q2

SAR3

SAR2

SAR1

SAR0

TP_X1

TP_Y1

TP_X2

TP_Y2

VDDP_33

SPI_SDI

VDDP_33

VDDP_50

GPIO_P01

GPIO_P02

GPIO_P03

GPIO_P04

GPIO_P05

GPIO_P06

GPIO_P00

LDE

Note: This pin diagram is based on 8-bit TTL output.

Version 0.1 -4- 11/23/2007

Copyright © 2007 MStar Semiconductor, Inc. All rights reserved.

Free Datasheet http://www.datasheet4u.com/

MST776-I

Car TV Processor with PIP/POP and External SDRAM

Preliminary Product Brief Version 0.1

PIN DESCRIPTION

MCU Interface

Pin Name Pin Type Function Pin

SAR3 Analog Input SAR Low Speed ADC Input 3 61

SAR2 Analog Input SAR Low Speed ADC Input 2 62

SAR1 Analog Input SAR Low Speed ADC Input 1 63

SAR0 Analog Input SAR Low Speed ADC Input 0

司 64

SAR_IN Analog Input SAR Low Speed ADC Input for Keypad

公 66

SPI_SCK Output SPI Flash Serial Clock

限 81

SPI_SDI Output SPI Flash Data Input

有 82

SPI_SDO Input w/ 5V-tolerant

技

SPI Flash Data Output 83

SPI_SCZ Output

科

SPI Flash Chip Select

om

84

GPIO_P00-GPIO_P06 I/O w/ 5V-tolerant

鑫 .c

General Purpose Input/Output; 4mA driving 87-93

泉

strength

a n

INT Input

聚 External Interrupt Input

u 73

市 uq

CS Input w/ 5V-tolerant 3-Wire Serial Bus Chip Select; active high 77

SCL

圳

Input w/ 5V-tolerant

. j

3-Wire Serial Bus Clock Input 78

SDA

深

I/O w/ 5V-tolerant

w w

3-Wire Serial Bus Data; 4mA driving strength 79

HWRESET Schmitt Trigger Input

w/ 5V-tolerant w Hardware Reset; active high 80

Analog Video Interface

Pin Name Pin Type Function Pin

VCLAMP CVBS/YC Mode Clamp Voltage Bypass 11

REFP Internal ADC Top De-coupling Pin 12

REFM Internal ADC Bottom De-coupling Pin 13

PRINP Analog Input Analog Pr Input of HDTV 24

PRINM Analog Input Reference Ground for Analog Pr Input of HDTV 25

PBINP Analog Input Analog Pb Input of HDTV 20

SOY Analog Input Sync-on-Y Slicer Input 21

YINP Analog Input Analog Y Input of HDTV 22

YINM Analog Input Reference Ground for Analog Y Input of HDTV 23

BINP Analog Input Analog B Input of VGA 16

SOGIN Analog Input Sync-on-Green Slicer Input 17

GINP Analog Input Analog G Input of VGA 18

Version 0.1 -5- 11/23/2007

Copyright © 2007 MStar Semiconductor, Inc. All rights reserved.

Free Datasheet http://www.datasheet4u.com/

MST776-I

Car TV Processor with PIP/POP and External SDRAM

Preliminary Product Brief Version 0.1

Pin Name Pin Type Function Pin

RINP Analog Input Analog R Input of VGA 19

C1INP Analog Input Analog Chroma Input for TV S-Video1 / 26

Analog Composite Input of TV CVBS4

C1INM Analog Input Reference Ground for Analog Chroma Input of TV S-Video1 27

/ Analog Composite Input of TV CVBS4

YS1INP Analog Input Analog Luma Input of TV S-Video1 / 28

Analog Composite Input of TV CVBS3

司

YS1INM Analog Input

公

Reference Ground for Analog Luma Input of TV S-Video1 / 29

Analog Composite Input of TV CVBS3

限

CVBS1P Analog Input

有

Analog Composite Input for TV CVBS1 30

CVBS2P Analog Input

技

Analog Composite Input for TV CVBS2 31

HSYNCIN1/ Schmitt Trigger Input HSYNC /

科 om

9

CSYNC w/ 5V-tolerant

鑫

Composite Sync for GPS RGB Input 1

. c

VSYNCIN1 Schmitt Trigger Input VSYNC

泉 a n 10

聚 u

w/ 5V-tolerant

HSYNCIN2

市 q

Schmitt Trigger Input HSYNC for YPbPr/Digital RGB Input 2 206

w/ 5V-tolerant

圳 . ju

VSYNCIN2

深

w/ 5V-tolerant

w w

Schmitt Trigger Input VSYNC for YPbPr/Digital RGB Input 2 207

FB

w

Schmitt Trigger Input Fast Blank for GPS RGB Input

w/ 5V-tolerant

208

VD_HSYNCO Output Video Decoder Horizontal Sync Output for GPS 210

Synchronization

VD_VSYNCO Output Video Decoder Vertical Sync Output for GPS 211

Synchronization

VD_CLKO Output Video Decoder Display Clock Output for GPS 209

Synchronization

REFP_DAC DAC Top Reference Voltage Decoupling Cap. 1uF to Ground 135

REFM_DAC DAC Bottom Reference Voltage Decoupling Cap. 1uF to 136

Ground

DACB Analog Output Analog Video B Channel Output 138

DACG Analog Output Analog Video G Channel Output 140

DACR Analog Output Analog Video R Channel Output 141

Version 0.1 -6- 11/23/2007

Copyright © 2007 MStar Semiconductor, Inc. All rights reserved.

Free Datasheet http://www.datasheet4u.com/

MST776-I

Car TV Processor with PIP/POP and External SDRAM

Preliminary Product Brief Version 0.1

Digital Video Interface

Pin Name Pin Type Function Pin

VI_CLKIN Input w/ 5V-tolerant Digital Video Input Clock 205

VI_DATA[23:0] Input w/ 5V-tolerant Digital Video Input Data [23:0] 185-196,

199-204, 3-8

ROUT[7:0] Output w/ Pull-down Red Channel Output 127-120

司

Resistor

公

GOUT[7:0] Output w/ Pull-down Green Channel Output 119, 118,

Resistor 115-110

BOUT[7:0] Output w/ Pull-down Blue Channel Output; programmable 限 109-102

Resistor

有

DTCON[0] Output TCON Output

技 101

LCK Output w/ Pull-down

科

LCD Output Clock; 6mA driving strength

om

97

Resistor

鑫 . c

LVSYNC Output

泉 a

LCD VSYNC; 6mA driving strength

n 96

LHSYNC Output

聚 u

LCD HSYNC; 6mA driving strength

q

95

LDE Output

市 ju

Display Enable Output 94

圳 w .

深

Digital PWM Interface

w

Pin Name

QOR

Pin Type

Output

w

Function

Combined DPWM Output 1 and 2

Pin

53

Q1 Output DPWM Output 1 54

Q2 Output DPWM Output 2 55

FB2_DPWM Analog Input Input for 2nd Feedback Loop 57

FB1_DPWM Analog Input Input for 1st Feedback Loop 58

VIN Analog Input System Input Voltage Detection 59

Switching Power and PWM Interface

Pin Name Pin Type Function Pin

PWM_REXT Analog Input External Resistor to GND, 100k ohm Resistor for Internal 35

Reference Current

PGOOD Output Power Good Detector 38

PWM_FB1 Analog Input Error Voltage Feedback Input Pin for PWM1; voltage = 39

1.0V

SENSE1 Analog Input Sense Circuit Connection for PWM1 40

PWMOUT1 Output Switching Pulse Output for 3.3V DC-DC Converter 42

Version 0.1 -7- 11/23/2007

Copyright © 2007 MStar Semiconductor, Inc. All rights reserved.

Free Datasheet http://www.datasheet4u.com/

MST776-I

Car TV Processor with PIP/POP and External SDRAM

Preliminary Product Brief Version 0.1

Pin Name Pin Type Function Pin

PWMOUT2 Output Switching Pulse Output for 1.8V DC-DC Converter 44

PWM_FB2 Analog Input Error Voltage Feedback Input Pin for PWM2; voltage = 45

1.0V

SENSE2 Analog Input Sense Circuit Connection for PWM2 46

DRVBST Analog Output Boost Converter Driving Output 48

司

CSBST Analog Input Boost Converter Current Sense 50

公

BOOSTON Analog Output Boost Converter On/Off Switch Control 51

限

FBBST Analog Input Boost Converter Output Voltage Feedback 52

DRAM Interface 有

技

科 m

Pin Name Pin Type Function Pin

BADR[1:0] Output

鑫

DRAM Memory Bank Address

.c o 156, 157

泉 n

CASZ Output Column Address Strobe; active low 162

DQM[1:0] Output

聚 u a

Data Mask for Low Byte; active high 175, 174

DQS[3:0] I/O

市

Data Strobe

u q

MADR[11:0] Output

圳

DRAM Memory Address

w .j 148, 149, 147-142,

深

155, 154, 151, 150

MCLK

MCLKE

Output

Output w w

DRAM Memory Positive Differential Clock

DRAM Memory Clock Enable

159

158

MDATA[15:0] I/O DRAM Memory Data Bus 184-180, 178-176,

173-166

CSZ Output Chip Select; active low 160

RASZ Output Row Address Strobe; active low 161

WEZ Output Write Enable; active low 163

Touch Panel Interface

Pin Name Pin Type Function Pin

TP_X1 Analog I/O Touch Panel X-axis Input/Output 1 67

TP_Y1 Analog I/O Touch Panel Y-axis Input/Output 1 68

TP_X2 Analog I/O Touch Panel X-axis Input/Output 2 69

TP_Y2 Analog I/O Touch Panel Y-axis Input/Output 2 70

Version 0.1 -8- 11/23/2007

Copyright © 2007 MStar Semiconductor, Inc. All rights reserved.

Free Datasheet http://www.datasheet4u.com/

MST776-I

Car TV Processor with PIP/POP and External SDRAM

Preliminary Product Brief Version 0.1

UART Interface

Pin Name Pin Type Function Pin

UART1_RX Input w/5V-tolerant Universal Asynchronous Receiver 1 85

UART1_TX I/O w/5V-tolerant Universal Asynchronous Transmitter 1 86

VCOM Interface

Pin Name Pin Type Function

司 Pin

VCOM_AC Analog Output

公

Reference AC Voltage Output for Common Amplifier 133

VCOM_DC Analog Output

限

Reference DC Voltage Output for Common Amplifier 134

有

Misc. Interface

技

Pin Name Pin Type Function

科 om

Pin

XIN Analog Input

鑫

Crystal Oscillator Input

. c 216

泉 n

ua

XOUT Analog Output Crystal Oscillator Output 1

WAKEUP Input 聚 Device Wake Up

q

72

市 u

Power Pins 圳 w .j

Pin Name 深

Pin Type

wFunction Pin

AVDD_33

AVDD_18

3.3V Power

1.8V Power

w Analog Power

Analog Power

14, 32

34

AVDD_PWM 5V Power Analog PWM Power 36

AVDD_DPWM 3.3V Power DPWM Power 60

AVDD_LPLL 3.3V Power LPLL Power 128

AVDD_DAC 5V Power DAC Power 139

AVDD_MI 3.3V Power Memory Power 164

AVDD_MPLL 3.3V Power MPLL Power 215

VDDC 1.8V Power Digital Core Power 74, 130, 198, 212

VDDP50_PWM 5V Power PWM Power 41, 47

VDDP50_TP 5V Power Touch Panel Power 71

VDDP_50 3.3V/5V Power Digital Input/Output Power for TCON 100

VDDP_33 3.3V Power Digital Input/Output Power 76, 99, 117, 152, 179,

214

GND Ground Ground 2, 15, 33, 37, 43, 49, 56,

65, 75, 98, 116, 129,

131, 132, 137, 153, 165,

197, 213

Version 0.1 -9- 11/23/2007

Copyright © 2007 MStar Semiconductor, Inc. All rights reserved.

Free Datasheet http://www.datasheet4u.com/

MST776-I

Car TV Processor with PIP/POP and External SDRAM

Preliminary Product Brief Version 0.1

ELECTRICAL SPECIFICATIONS

Analog Interface Characteristics

Parameter MST776-I Unit

Min Typ Max

Resolution 10 Bits

ANALOG INPUT

Input Voltage Range

司

Minimum 0.5

公 V p-p

Maximum 1.5

限 V p-p

Input Bias Current

有 1 μA

SWITCHING PERFORMANCE

技

Maximum Conversion Rate

科 86

o m MSPS

Minimum Conversion Rate

鑫 12

.c

MSPS

Maximum PLL Clock Rate

泉 a n

86 MHz

聚 u

Minimum PLL Clock Rate 10 MHz

市 uq

PLL Jitter TBD ps p-p

Sampling Phase Tempco

圳 w .j 15 ps/°C

深

DIGITAL INPUTS

Input Voltage, High (VIH)

Input Voltage, Low (VIL) w w 0.7 VDDP

0.8

V

Input Current, High (IIH) -1.0 μA

Input Current, Low (IIL) 1.0 μA

Input Capacitance 5 pF

DIGITAL OUTPUTS

Output Voltage, High (VOH) VDD - 0.1 V

Output Voltage, Low (VOL) 0.1 V

Notes

1. With Timing Interval Analyzer (TIA) measurement

Specifications are subjected to change without notice.

Version 0.1 - 10 - 11/23/2007

Copyright © 2007 MStar Semiconductor, Inc. All rights reserved.

Free Datasheet http://www.datasheet4u.com/

MST776-I

Car TV Processor with PIP/POP and External SDRAM

Preliminary Product Brief Version 0.1

Absolute Maximum Ratings

Parameter Symbol Min Typ Max Units

5.0V Supply Voltages VVDD_50 -0.3 5.5 V

3.3V Supply Voltages VVDD_33 -0.3 3.6 V

1.8V Supply Voltages VVDD_18 -0.3 1.98 V

Input Voltage (5V tolerant inputs) VIN5Vtol -0.3 5.0 V

Input Voltage (non 5V tolerant inputs) VIN -0.3

司 VVDD_33 V

Ambient Operating Temperature TA -40

公 85 °C

Storage Temperature TSTG -40

限 150 °C

Junction Temperature TJ

有 150 °C

Thermal Resistance (Junction to Air) Natural θJA

技 TBD °C/W

Conversion

科 o m

Thermal Resistance (Junction to Case)

鑫

θJC

.c

TBD °C/W

泉 n

Natural Conversion

a

Note: Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. This is a

聚 u

stress rating only and does not imply functional operation of the device. Exposure to absolute maximum ratings for

q

市

extended periods may affect device reliability.

ORDERING GUIDE

圳 .j u

MARKING INFORMATION

ww

MST776-I

深

Model Temperature Package Package

Part Number

Range Description Option

MST776-I

MST776-I-LF

-40°C to +85°C

-40°C to +85°C

LQFP

LQFP

w216

216

Lot Number

Operation Code A

Note: Product suffix “-LF” represents lead-free version. Operation Code B

Date Code (YYWW)

DISCLAIMER

MSTAR SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE

TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. NO

RESPONSIBILITY IS ASSUMED BY MSTAR SEMICONDUCTOR ARISING OUT OF THE APPLICATION

OR USER OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY

LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

Electrostatic charges accumulate on both test equipment and human body and can discharge

without detection. MST776-I comes with ESD protection circuitry; however, the device may be

permanently damaged when subjected to high energy discharges. The device should be handled

with proper ESD precautions to prevent malfunction and performance degradation.

REVISION HISTORY

Document Description Date

MST776-I_pb_v01 Ÿ Initial release Nov 2007

Version 0.1 - 11 - 11/23/2007

Copyright © 2007 MStar Semiconductor, Inc. All rights reserved.

Free Datasheet http://www.datasheet4u.com/

MST776-I

Car TV Processor with PIP/POP and External SDRAM

Preliminary Product Brief Version 0.1

MECHANICAL DIMENSIONS

D1 A

A2

A1

司

公

限

有

技

科 m

E1

E

鑫 .c o

泉 a n

聚 q u

市 u

圳 w .j

深 w

L1

w c

Gauge Plane

θ

0.25mm

Seating Plane

b e

L

Symbol Millimeter Inch Symbol Millimeter Inch

Min. Nom. Max. Min. Nom. Max. Min. Nom. Max. Min. Nom. Max.

A - - 1.60 - - 0.063 θ 0° 3.5° 7° 0° 3.5° 7°

A1 0.05 - 0.15 0.002 - 0.006 L 0.45 0.60 0.75 0.018 0.024 0.030

A2 1.35 1.40 1.45 0.053 0.055 0.057 L1 1.00 REF. 0.039 REF.

D 26.00 1.024 b - 0.18 - - 0.007 -

D1 24.00 0.945 c - 0.08 - - 0.003 -

E 26.00 1.024 e 0.40 BSC 0.016 BSC

E1 24.00 0.945

Version 0.1 - 12 - 11/23/2007

Copyright © 2007 MStar Semiconductor, Inc. All rights reserved.

Free Datasheet http://www.datasheet4u.com/

You might also like

- NET MAUI For C# Developers Jesse Liberty, Rodrigo Juarez, 2023 PacktDocument296 pagesNET MAUI For C# Developers Jesse Liberty, Rodrigo Juarez, 2023 PacktsvwerwolfNo ratings yet

- Manual C3VCM6 EngDocument50 pagesManual C3VCM6 Engpolliuy100% (1)

- TV 7 Mst726 Datasheet 535Document117 pagesTV 7 Mst726 Datasheet 535Денис ДенисовNo ratings yet

- Mstar Confidential for 深圳市江启科技有限公司 Internal Use Only: FeaturesDocument207 pagesMstar Confidential for 深圳市江启科技有限公司 Internal Use Only: FeaturesErroz RosadiNo ratings yet

- WDH-3500EC: Single Channel MPEG-2 SD EncoderDocument3 pagesWDH-3500EC: Single Channel MPEG-2 SD EncoderGoran BogdanovskiNo ratings yet

- DS-7304/7308/7316HWI-SH DVR: SeriesDocument3 pagesDS-7304/7308/7316HWI-SH DVR: SeriesakenterprisesosmuzaffarpurNo ratings yet

- OmniVision OV20880Document2 pagesOmniVision OV20880ady333No ratings yet

- Ledsync820C: Z Professional Solution To Drive Led WallsDocument3 pagesLedsync820C: Z Professional Solution To Drive Led WallsMauro Barragan SanchezNo ratings yet

- OmniVision OV16880Document2 pagesOmniVision OV16880ady333No ratings yet

- VP50 Dvdo 032807Document2 pagesVP50 Dvdo 032807Nizo Oeste PmdbNo ratings yet

- Hi3751 V320 Brief Data Sheet: Key Specifications Key FeaturesDocument4 pagesHi3751 V320 Brief Data Sheet: Key Specifications Key Featuresnani_amlprm5912No ratings yet

- Specification MST182VG V1.0Document10 pagesSpecification MST182VG V1.0RajeshNo ratings yet

- TSUMV59XUS MStar PDFDocument8 pagesTSUMV59XUS MStar PDFGustavo de Vargas DiasNo ratings yet

- Tsumv59xus PDFDocument8 pagesTsumv59xus PDFHamza Abbasi AbbasiNo ratings yet

- DS-7304/08/16HGHI-SH Series DVR: Physical InterfacesDocument2 pagesDS-7304/08/16HGHI-SH Series DVR: Physical InterfacesyansenNo ratings yet

- Selenio X100Document12 pagesSelenio X100Alexsandro Leite FigueirêdoNo ratings yet

- 8860 Brief DatasheetDocument5 pages8860 Brief DatasheetCourtney HernandezNo ratings yet

- Hi3798M V100 Brief Data SheetDocument3 pagesHi3798M V100 Brief Data Sheet王先生No ratings yet

- DS-7324/7332HWI-SH DVR: SeriesDocument2 pagesDS-7324/7332HWI-SH DVR: SeriesMauricio IbarraNo ratings yet

- IPM6102 64 Channels IP To Analog ModulatorDocument2 pagesIPM6102 64 Channels IP To Analog ModulatorElkaNo ratings yet

- Features: Video Decoder Scaling Engine/Panel InterfaceDocument10 pagesFeatures: Video Decoder Scaling Engine/Panel InterfaceMrbar BarstoynNo ratings yet

- M Vision Hd200Document2 pagesM Vision Hd200devon39No ratings yet

- Adv7340 7341 PDFDocument108 pagesAdv7340 7341 PDFTheotech EletronNo ratings yet

- Vigilance Series (New) PDFDocument2 pagesVigilance Series (New) PDFAbelRamadhanNo ratings yet

- Multi-Service Video Management Platform: Ultra SeriesDocument2 pagesMulti-Service Video Management Platform: Ultra SeriesJeronimo ReynosoNo ratings yet

- LCD TV ServiceDocument84 pagesLCD TV ServiceESLINC100% (1)

- Integrated Video Decoder and HDMI Receiver: Data SheetDocument20 pagesIntegrated Video Decoder and HDMI Receiver: Data SheetBruno MatonNo ratings yet

- схема и сервис мануал на английском Daytron DT32LUFB PDFDocument17 pagesсхема и сервис мануал на английском Daytron DT32LUFB PDFtonyroguez50No ratings yet

- Truvision NVR 22plus: Full Featured H.265 Network Video RecorderDocument2 pagesTruvision NVR 22plus: Full Featured H.265 Network Video RecorderAlexandra CăpraruNo ratings yet

- CV3393BL G 20 CultraviewDocument15 pagesCV3393BL G 20 CultraviewSamuel Ulises Leon GonzalezNo ratings yet

- Proview 7100Document4 pagesProview 7100Arif SriwidodoNo ratings yet

- Tmc-9700 Progressive Scan Full-Frame Color Camera: Imaging ProductsDocument4 pagesTmc-9700 Progressive Scan Full-Frame Color Camera: Imaging ProductsMonty^No ratings yet

- Castwin Encoder DME-8624S PDFDocument2 pagesCastwin Encoder DME-8624S PDFoscar carcassesNo ratings yet

- KX A4k8108n2Document1 pageKX A4k8108n2Brian MinhNo ratings yet

- TransdataDocument121 pagesTransdataFrancis P GarciaNo ratings yet

- Spesifikasi PLD 65UV5930Document4 pagesSpesifikasi PLD 65UV5930wulanluvspinkNo ratings yet

- lcd-mst6m48v2.0c 244 PDFDocument12 pageslcd-mst6m48v2.0c 244 PDFzulkarnain apriadiNo ratings yet

- Combined Pitot-Static Datasheet V2 0Document3 pagesCombined Pitot-Static Datasheet V2 0Fakhri GhrairiNo ratings yet

- 20221216 - 1864116 - UNV【Datasheet】XVR301-F Series-V1.00 EN - 958035 - 168459 - 0Document4 pages20221216 - 1864116 - UNV【Datasheet】XVR301-F Series-V1.00 EN - 958035 - 168459 - 0Alexis F Hernández BNo ratings yet

- DS-6916UDIBDecoder - V2.6.1Document4 pagesDS-6916UDIBDecoder - V2.6.1DILMER JAVIERNo ratings yet

- Visionav-Hd: Professional Audio and Video Capture CardDocument3 pagesVisionav-Hd: Professional Audio and Video Capture Cardorlando benavidesNo ratings yet

- Programmable 4K2K Video Signal Generator (Model: K-8890) : Displayport Hdmi MHLDocument2 pagesProgrammable 4K2K Video Signal Generator (Model: K-8890) : Displayport Hdmi MHLouyangxin1991No ratings yet

- Adv7393bcpz SMD Encoder Entegresi Lfcsp40 DatasheetDocument107 pagesAdv7393bcpz SMD Encoder Entegresi Lfcsp40 DatasheetSabri OkurNo ratings yet

- OmniVision OV4689Document2 pagesOmniVision OV4689Eric GirodNo ratings yet

- Cisco D9854Document8 pagesCisco D9854denismoraes.toNo ratings yet

- DS 9600ni STDocument3 pagesDS 9600ni STRaju RamNo ratings yet

- Vga To Cga Converter: MODEL: CV-02 Ver 1.1Document1 pageVga To Cga Converter: MODEL: CV-02 Ver 1.1Luis Otavio TrindadeNo ratings yet

- 8CH Multiviewer: Full HDDocument4 pages8CH Multiviewer: Full HDRobert Anderson Ordóñez BautistaNo ratings yet

- Multi-Service Video Management Platform: Ultra SeriesDocument2 pagesMulti-Service Video Management Platform: Ultra SeriesRodriguez JuanNo ratings yet

- Controller m70 4u e Datasheet20160815Document5 pagesController m70 4u e Datasheet20160815Agencia DigitalNo ratings yet

- Ds-6916udi (B)Document4 pagesDs-6916udi (B)LOURDES ESTHER DIEZ GUTIERREZNo ratings yet

- CV3393CH O 11 Specification V1.0Document22 pagesCV3393CH O 11 Specification V1.0Красимир КостадиновNo ratings yet

- OmniVision OV4689Document2 pagesOmniVision OV4689nilsNo ratings yet

- Digital TV Encoder ModulatorDocument5 pagesDigital TV Encoder ModulatorKaori MakimuraNo ratings yet

- DatasheetofDS-96128NI-M16 SNMP V4.61.410 20221208Document5 pagesDatasheetofDS-96128NI-M16 SNMP V4.61.410 20221208aaa.uae.itservicesNo ratings yet

- OmniVision OV9712-1DDocument2 pagesOmniVision OV9712-1Dady333No ratings yet

- BWFCPC-E8000 Multi Format HD EncoderDocument2 pagesBWFCPC-E8000 Multi Format HD EncoderSaeful AnwarNo ratings yet

- Single-Chip, Low Cost High-Definition HDMI 1.3 Video ProcessorDocument2 pagesSingle-Chip, Low Cost High-Definition HDMI 1.3 Video Processorpetetest_esNo ratings yet

- IV8WTESTDocument2 pagesIV8WTESTAbraham Lopez G.No ratings yet

- Jadwal Olx Autos 2022-2Document41 pagesJadwal Olx Autos 2022-2Bekti Yayang Mardya SaputraNo ratings yet

- Diagnosa & RepairDocument8 pagesDiagnosa & RepairBekti Yayang Mardya SaputraNo ratings yet

- Ecs FT86Document1 pageEcs FT86Bekti Yayang Mardya SaputraNo ratings yet

- MST776-I Mstar PDFDocument12 pagesMST776-I Mstar PDFBekti Yayang Mardya SaputraNo ratings yet

- Marine Event Recorder: BergenDocument2 pagesMarine Event Recorder: BergenUFUKKKNo ratings yet

- Top 20 Matlab Interview Questions & Answers: 1) Explain What Is Matlab? Where Matlab Can Be Applicable?Document5 pagesTop 20 Matlab Interview Questions & Answers: 1) Explain What Is Matlab? Where Matlab Can Be Applicable?Shroni SharmaNo ratings yet

- Chapter 5 Documenting A NetworkDocument37 pagesChapter 5 Documenting A NetworkSYED AHMAD SHAUQI BIN SYED SHUHAIMINo ratings yet

- iOS 9 Day by DayDocument109 pagesiOS 9 Day by DayPhilli OneromNo ratings yet

- Automapper Documentation: Jimmy BogardDocument83 pagesAutomapper Documentation: Jimmy Bogardzafarkamal7No ratings yet

- Database System ArchitectureDocument21 pagesDatabase System ArchitectureDev BabbarNo ratings yet

- Universidad Del Magdalena Ingeniería Electrónica Diseño de Sistemas Digitales - Actividad Asincrónica 3Document3 pagesUniversidad Del Magdalena Ingeniería Electrónica Diseño de Sistemas Digitales - Actividad Asincrónica 3Angélica SamperNo ratings yet

- AC AnalysisDocument12 pagesAC AnalysisIan Benedict LavapieNo ratings yet

- CP1H Function BlocksDocument59 pagesCP1H Function BlocksSérgio Cardoso de OliveiraNo ratings yet

- Veeam Backup Azure Product OverviewDocument2 pagesVeeam Backup Azure Product Overviewsly_boss49No ratings yet

- Infinity Box PinFinderDocument25 pagesInfinity Box PinFinderDrago KraljNo ratings yet

- Ios Vs Android: Submitted To: Ms - Manmohak SandhuDocument11 pagesIos Vs Android: Submitted To: Ms - Manmohak SandhuSai Kiran100% (1)

- CH 12Document37 pagesCH 12miathegirl9No ratings yet

- Android Malware WhitepaperDocument13 pagesAndroid Malware Whitepaperjuhi_himanshiNo ratings yet

- Computer Organization and ArchitectureDocument12 pagesComputer Organization and ArchitecturepadmanabhanprathyushNo ratings yet

- Parallel ComputingDocument12 pagesParallel ComputingSaravanan Thangavelu100% (1)

- SWRAUTOTESTERDocument14 pagesSWRAUTOTESTERslawekNo ratings yet

- Wired ProtocolsDocument13 pagesWired Protocolsyouandme091223No ratings yet

- VMware AlignmentDocument2 pagesVMware Alignmentkuldeep_singh_144No ratings yet

- ABAP Outbound Proxy: CommunityDocument15 pagesABAP Outbound Proxy: CommunityRaviteja KanakaNo ratings yet

- Bitsler Script 2019 Hack For FreeDocument4 pagesBitsler Script 2019 Hack For FreeAbhimanyu ravidasNo ratings yet

- AGILE Refresher - Part 2Document61 pagesAGILE Refresher - Part 2rupesh naiduNo ratings yet

- Voltage and Current Divider Rules, Series, Parallel and Series-Parallel CircuitDocument13 pagesVoltage and Current Divider Rules, Series, Parallel and Series-Parallel CircuitMAHIRA TAJ A21ET0300No ratings yet

- A Feasibility Study On E-Class Record System: Eastern Samar State UniversityDocument45 pagesA Feasibility Study On E-Class Record System: Eastern Samar State UniversityjoshuaNo ratings yet

- Entuity EYE of The Storm Core EventsDocument186 pagesEntuity EYE of The Storm Core Eventsjesp_scribd100% (1)

- Django Interview QuestionsDocument4 pagesDjango Interview QuestionsAkbar AANo ratings yet

- P-Channel Enhancement Mode MOSFET: Product SummaryDocument5 pagesP-Channel Enhancement Mode MOSFET: Product SummaryAhmad Syafii LeongNo ratings yet

- Gujarat Technological University: Programming With Linux, Apache, Mysql, and PHP (Lamp)Document42 pagesGujarat Technological University: Programming With Linux, Apache, Mysql, and PHP (Lamp)Malathi SankarNo ratings yet