Professional Documents

Culture Documents

520 6936 01B Cpu Spike 1

520 6936 01B Cpu Spike 1

Uploaded by

zokiOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

520 6936 01B Cpu Spike 1

520 6936 01B Cpu Spike 1

Uploaded by

zokiCopyright:

Available Formats

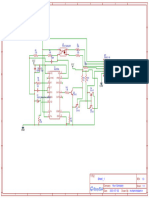

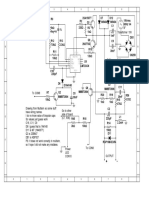

A B C D E

4 4

VDD

10k

10k

10k

10k

10k

10k

10k

10k

10k

VDD

U46

16

R168

R169

R180

74HC165D

R86

R87

R88

R89

R90

R92

CN25 10 b16: nDIP7

VCC

nSELECT R94 10k SER VDD

11 b15: nDIP6

1 nUP R95 10k A

12 b14: nDIP5

2 nDOWN R96 10k B C192

13 b13: nDIP4

3 nBACK R97 10k C 0.1µF

14

4 nLFLIP1 R98 10k D b12: nDIP3

3

5 nLFLIP2 R99 10k E b11: nDIP2

4

6 nRFLIP1 R170 10k F

5 b10: nDIP1

7 nRFLIP2 R171 10k G

6 9 b9: nDIP0

8 R181 10k H QH

3 nVBBGOOD b8: nRFLIP2 3

9

2 7

10 CLK QH b7: nRFLIP1

15

GND

11 nVBBGOOD INH b6: nLFLIP2

1

12 SH/LD b5: nLFLIP1

22-23-2121 VDD b4: nBACK

8

Molex b3: nDOWN

b2: nUP

b1: nSELECT

10k

10k

10k

10k

10k

10k

10k

10k

VDD b0:

U47 nVBBGOOD

16

R172

R173

R174

R175

R176

R177

R178

R179

74HC165D

S2 10

VCC

SER VDD

16 1 nDIP0 11

A

15 2 nDIP1 12

B C193

14 3 nDIP2 13

C 0.1µF

13 4 nDIP3 14

D

12 5 nDIP4 3

E

11 6 nDIP5 4

F

10 7 nDIP6 5

G SPI1_MISO

9 8 nDIP7 6 9 SPI1_MISO

H QH

219-8MST 2 7

SPI1_SPCK CLK QH

2 CTS Electrocomponents 15 2

GND

INH

1

VDD SH/LD

8

5

1 VCC

SPI1_NPCS0

4

2

GND

U49

3

VDD 74LVC1G00GV

Nexperia USA Inc

C199

0.1µF

1 1

Title

Stern Pinball CPU -- switch inputs

Size Document Number Rev

B 520-6936-01 B

Date: Monday, October 01, 2018 Sheet 2 of 8

A B C D E

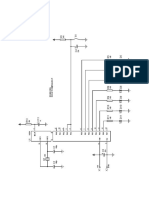

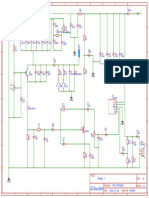

A B C D E

VDD VDD VDD1_0

VDDIOM0[3:0] - DDR2 SDRAM I/O, should be 1.8VDC VDD1_0 L9 VDDPLLA VDD1_0 L10 VDDPLLUTMI

VDDIOM1[3:0] - EBI I/O, port C (set to 3.3V) 10µH, 100mA 10µH, 100mA

I2S_SCK0

VDDIOP0 - peripherals I/O (3.3V) VDD I2S_SCK0

C140 C141 C142 C143 C144 C145 C146 C147 C148 C149 C150 C151 C152 C153 C154 C155 C156 C157 I2S_WS0

VDDIOP1 - LCD I/O (3.3V) I2S_WS0 VDD

R111 C158 R112 C159 I2S_SD0

VDDIOP2 - ISI I/O (not used for ISI, set to 3.3V) I2S_SD0

1 0.1µF 1 0.1µF

VDDBU - backup I/O (3.3V)

0.1µF, 16V 0.1µF, 16V 0.1µF, 16V

R31

R32

R33

R34

VDDANA - analog power supply (3.3V)

C160 C161

R40

R41

R42

R43

R44

VDDPLLA - PLLA (1.0V)

4.7µF, 6.3V 4.7µF, 6.3V

VDDPLLUTMI - PLLUTMI (1.0V) VDD VDD

VDDOSC - oscillator (3.3V) CN11 VDDPLLUTMI VDD

100k

100k

100k

100k

DO NOT PLACE VDDBU VDDOSC

68k

68k

68k

68k

10k

VDDCORE - core voltage (1.0V) 2 1

+ + R35 0 NTRST VDD L11 VDDOSC VDDPLLA

VDDUTMIC - UDPHS and UHPHS UTMI+ core supply (1.0V) 4 3 CN13

+ + TDI 10µH, 100mA VDD VDD1_8 VDD VDD1_0 MCI0_DA3 R49 27

VDDUTMII - UDPHS and UHPHS UTMI+ interface supply 6 5

+ + TMS C66 VDD MCI0_CDA R50 27 1 VDD

8 7

(3.3V) + + TCK 27pF 2

10 9

+ + R39 0 RTCK R113 C162 U12 3 C69 SD1

12 11

+ + TDO 1 0.1µF C67 AT91SAM9G45C-CU MCI0_CK R51 27 4

14 13

VBB = 48VDC (input)

M14

G10

G11

G12

G13

D16

U11

H11

U18

+ + 5

K10

V14

K13

P11

V13

E18

V17

L12

L13

16 15 R45 0 NRST 12pF Y2 Atmel

H3

D4

K9

E3

F6

+ + 12.000 MHz MCI0_DA0 R52 27 6

18 17

VA = 24VDC (audio amps) + + 7

1

20 19 VDD C163 C68 MCI0_DA1 R53 27

VDDPLLA

VDDIOP00

VDDIOP01

VDDIOM00

VDDIOM01

VDDIOM02

VDDIOM03

VDDIOM10

VDDIOM11

VDDIOM12

VDDIOM13

VDDOSC

VDDCORE0

VDDCORE1

VDDCORE2

VDDCORE3

VDDPLLUTMI

+ + 8

VDDIOP1

VDDIOP2

VDDBU

VDDANA

VDDUTMIC

VDDUTMII

R46 4.7µF, 6.3V Y3 27pF MCI0_DA2 R47 27 MT3

4 VNB = 9.0VDC (node bus) SBH11-NBPC-D10-SM-BK 0 32.768kHz XIN V12

XIN PA0/MCI0_CK/TCLK3

L1 MCI0_CK 9

CD

MT3

MT4

MT4 4GB Class 4 SD Card 4

Sullins R48 XOUT V11 M1 MCI0_CDA MT5 SD4/4GB

VCC = 5.0VDC (HDMI pin 18) XOUT PA1/MCI0_CDA/TIOA3 WP MT5

4

0 C70 L5 MCI0_DA0 MT6 Kingston

DO NOT PLACE DO NOT PLACE XIN32 PA2/MCI0_DA0/TIOB3 MCI0_DA1 GND MT6

C1 N1

VDD = 3.3VDC ICE INTERFACE 12pF XOUT32 D1

XIN32

XOUT32

PA3/MCI0_DA1/TCKL4

PA4/MCI0_DA2/TIOA4

L6 MCI0_DA2

JTAGSEL M2 MCI0_DA3 DM1AA-SF-PEJ(21)

VDD1_8 = 1.8VDC S1 PA5/MCI0_DA3/TIOB4

PA6/MCI0_DA4/ETX2

M3 ETX2 Hirose

NRST R54 10k ETX3

VDD1_0 = 1.0VDC PTS645SL50SMTR LFS

VDDBU PA7/MCI0_DA5/ETX3

M4 SD CARD INTERFACE MCI0

RESET C&K Components

NRST F3

C3

SHDN PA8/MCI0_DA6/ERX2

L7

N2

ERX2

ERX3

DDR_A[0:13] WKUP PA9/MCI0_DA7/ERX3 VDD

M5 ETX0

U13 PA10/ETX0 VDD VDD

TCK U10 P1 ETX1

MT47H32M16NF-25E:H TCK PA11/ETX1

TDI R10 N3 ERX0

Micron DDR_D[0:15] TDI VDDIOP0 PA12/ERX0 C71 U14 CN12

TDO V10 P2 ERX1

TDO PA13/ERX1 0.1µF MAX3243CDB

R139

R140

DDR_A0 M8 G8 DDR_D0 TMS P10 M6 ETXEN 1

26

A0 DQ0 TMS VDDBU PA14/ETXEN TI

DDR_A1 M3 G2 DDR_D1 JTAGSEL E4 N4 ERXDV 6

A1 DQ1 VDD1_8 VDD1_8 VDD1_8 VDD1_8 RTCK JTAGSEL PA15/ERXDV VDD RS232_RXD2

DDR_A2 M7 H7 DDR_D2 R11 N5 ERXER 28 2

A2 DQ2 RTCK VDDIOP0 VDDIOP0 PA16/ERXER C1+

DDR_A3 N2 H3 DDR_D3 N6 ETXCK 7

A3 DQ3 C73 C74 C75 C76 3.3V PA17/ETXCK C72 RS232_TXD2

4.7k

4.7k

DDR_A4 N8 H1 DDR_D4 NRST M10 R1 EMDC 27 3

A4 DQ4 NRST PA18/EMDC 0.1µF

V+

C77

DDR_A5 N3 H9 DDR_D5 P3 EMDIO 8

A5 DQ5 PA19/EMDIO CSDA 0.1µF

R36

R56

R57

DDR_A6 N7 F1 DDR_D6 NTRST N10 R2 CSDA 24 4

A6 DQ6 NTRST PA20/TWD0 CSCL

C1-

DDR_A7 P2 F9 DDR_D7 VDD T11 P4 CSCL 1 9

A7 DQ7 0.1µF, 16V BMS PA21/TWCK0 nDMRST

C2+

DDR_A8 P8 C8 DDR_D8 T1 5

A8 DQ8 R145E EBI0_DDR_D0 PA22/MCI1_CDA/SCK3 nSTATUS R85 C78

DDR_A9 P3 C2 DDR_D9 DDR_D0 12 5 R16 P5 D5 3

A9 DQ9 VDD1_8 VDD1_8 VDD1_8 VDD1_8 R145F EBI0_DDR_D1 DDR_D0 PA23/MCI1_DA0/RTS3 150 0.1µF

V-

C79

10k

10k

10k

DDR_A10 M2 D7 DDR_D10 DDR_D1 11 6 R15 R3 1 2

A10 DQ10 R145H EBI0_DDR_D2 DDR_D1 PA24/MCI1_DA1/CTS3 0.1µF

DDR_A11 P7

A11 DQ11

D3 DDR_D11

C80 C81 C82 C83

DDR_D2 9

R145C

8

EBI0_DDR_D3

T14

DDR_D2 PA25/MCI1_DA2/PWM3

T2 nDMISP 2 C2- EIA-232D USART2 COM PORT

DDR_A12 R2 D1 DDR_D12 DDR_D3 14 3 P15 T3 nDMRDY

A12 DQ12 R143H EBI0_DDR_D4 DDR_D3 PA26/MCI1_DA3/TIOB2 TXD2 VDD

DDR_A13 R8 D9 DDR_D13 DDR_D4 9 8 P16 U1 ETXER 14 9

A13 DQ13 R143F EBI0_DDR_D5 DDR_D4 PA27/MCI1_DA4/ETXER VDDBU

B1 DDR_D14 DDR_D5 11 6 P17 U3 ERXCK

DQ14 R145G EBI0_DDR_D6 DDR_D5 PA28/MCI1_DA5/ERXCK

DDR_BA0 L2 B9 DDR_D15 DDR_D6 10 7 R14 U2 ECRS

BA0 DQ15 0.1µF, 16V R145D EBI0_DDR_D7 DDR_D6 PA29/MCI1_DA6/ECRS TXD1 D7

DDR_BA1 L3 DDR_D7 13 4 P14 R4 ECOL 13 10

BA1 VDD1_8 R146H EBI0_DDR_D8 DDR_D7 PA30/MCI1_DA7/ECOL nERST ZHCS500TA

A1 DDR_D8 9 8 N15 V1

VDD VDD1_8 VDD1_8 VDD1_8 VDD1_8 R145A EBI0_DDR_D9 DDR_D8 PA31/MCI1_CK/PCK0

E1 DDR_D9 16 1 N16

VDD R143G EBI0_DDR_D10 DDR_D9 RTS1

J9 ~250mA DDR_D10 10 7 P18 T4 12 11

R149 0 DDR_ODT VDD C84 C85 C86 C87 R143D EBI0_DDR_D11 DDR_D10 PB0/SPI0_MISO C128

K9 M9 DDR_D11 13 4 N17 V2 SPI0_MOSI

ODT VDD R143E EBI0_DDR_D12 DDR_D11 PB1/SPI0_MOSI BT2 D52 0.1µF

R1 DDR_D12 12 5 N18 V3 SPI0_SPCK

VDD R145B EBI0_DDR_D13 DDR_D12 PB2/SPI0_SPCK CR2032 ZHCS500TA

DDR_D13 15 2 N14 U4 SPI0_NPCS0 20

R146F EBI0_DDR_D14 DDR_D13 VDDIOP0 PB3/SPI0_NPCS0 TXD1 Energizer

DDR_CKE K2 J1 DDR_D14 11 6 M15 R5

CKE VDDL 0.1µF, 16V R146G EBI0_DDR_D15 DDR_D14 3.3V PB4/TXD1 RXD1

DDR_D15 10 7 M16 V4

DDR_D15 PB5/RXD1 TXD2

DDR_CK J8 A9 T5 RXD2 19 4

CK VDDQ VDD1_8 VDD1_8 VDD1_8 VDD1_8 DDR_A0 R143B EBI0_DDR_A0 PB6/TXD2 RXD2 D8

DDR_nCK K8 C1 15 2 M17 U5

nCK VDDQ R147H EBI0_DDR_A1 DDR_A0 PB7/RXD2 TXD3 ZHCS500TA

C3 DDR_A1 9 8 L14 T12 TXD3

VDDQ C88 C89 C90 C91 R143C EBI0_DDR_A2 DDR_A1 PB8/TXD3/ISI_D8 RXD3 CN16

C7 DDR_A2 14 3 M18 N11 RXD3 RXD1 18 5

DDR_nCS VDDQ R146D EBI0_DDR_A3 DDR_A2 VDDIOP2 PB9/RXD3/ISI_D9

L8 C9 DDR_A3 13 4 L15 U13 1

nCS VDDQ R146E EBI0_DDR_A4 DDR_A3 3.3V PB10/TWD1/ISI_D10

E9 DDR_A4 12 5 L16 M11 6

VDDQ R143A EBI0_DDR_A5 DDR_A4 PB11/TWCK1/ISI_D11 RS232_RXD1 BT1

DDR_nCAS L7 G1 DDR_A5 16 1 L18 P6 DRXD CTS1 17 6 2 Use CR2032 20 mm

nCAS VDDQ 0.1µF, 16V R144H EBI0_DDR_A6 DDR_A5 PB12/DRXD RS232_RTS1 1065

DDR_nRAS K7 G3 DDR_A6 9 8 L17 R6 DTXD 7 3V coin cell

nRAS VDDQ R147F EBI0_DDR_A7 DDR_A6 PB13/DTXD SPI1_MISO RS232_TXD1 Keystone

G7 DDR_A7 11 6 K14 M7 SPI1_MISO 3

VDDQ R146B EBI0_DDR_A8 DDR_A7 PB14/SPI1_MISO SPI1_MOSI VDD RS232_CTS1

DDR_nWE K3 G9 DDR_A8 15 2 K15 V5 16 7 8

nWE VDDQ R146C EBI0_DDR_A9 DDR_A8 VDDIOP0 PB15/SPI1_MOSI/CTS0 SPI1_SPCK CN2

DDR_A9 14 3 K16 T6 SPI1_SPCK 4

3 DDR_DQM1 R144G EBI0_DDR_A10 DDR_A9 3.3V PB16/SPI1_SPCK/SCK0 SPI1_NPCS0 3

B3 J2 DDR_VREF DDR_A10 10 7 K18 U6 SPI1_NPCS0 9

UDM VREF R144F EBI0_DDR_A11 DDR_A10 PB17/SPI1_NPCS0/RTS0 1 nDMRST

DDR_DQM0 F3 DDR_A11 11 6 K17 N7 RXD0 15 8 5 nDMRST

LDM C92 R147G EBI0_DDR_A12 DDR_A11 PB18/RXD0/SPI0_NPCS1 TXD0 2

DDR_DQS1 B7 A3 DDR_A12 10 7 J14 P7 nDMISP nDMISP

UDQS VSS R148G EBI0_DDR_A13 DDR_A12 PB19/TXD0/SPI0_NPCS2 DTXD 3

A8 E3 DDR_A13 10 7 J15 P12 VDD 23 FORCEON nDMRDY nDMRDY

nUDQS/NU VSS DDR_A13 PB20/ISI_D0 DRXD 4

DDR_DQS0 F7

LDQS VSS

J3

DDR_CK R144E EBI0_DDR_CK PB21/ISI_D1

T15

5 VDD 22 FORCEOFF EIA-232D USART1 COM PORT SPI0_NPCS0 SPI0_NPCS0

E8 N1 12 5 J18 R12 21 INVALID SPI0_SPCK SPI0_SPCK

nLDQS/NU VSS 0.1µF, 16V DDR_nCK R144C DDR_CLK PB22/ISI_D2 6

P9 14 3 EBI0_DDR_nCK H18 T16 SPI0_MOSI SPI0_MOSI

VSS DDR_CKE R148H #DDR_CLK PB23/ISI_D3

9 8 EBI0_DDR_CKE J16 N12

DDR_nCS R147D DDR_CKE PB24/ISI_D4

A7 13 4 EBI0_DDR_nCS H14 M12

VSSQ DDR_CS PB25/ISI_D5

25

B2 DDR_nWE 12 R148E 5 EBI0_DDR_nWE H15 VDDIOP2 U14 DEBUG PORT

VSSQ DDR_nRAS R144D DDR_WE 3.3V PB26/ISI_D6

B8 13 4 EBI0_DDR_nRAS J17 M13

VSSQ DDR_nCAS R144B DDR_RAS PB27/ISI_D7

D2 15 2 EBI0_DDR_nCAS H17 N13

VSSQ DDR_CAS PB28/ISI_PCK

D8 R13

VSSQ DDR_DQM0 12 R147E PB29/ISI_VSYNC

E7 5 EBI0_DDR_DQM0 G14 T13

VSSQ DDR_DQM1 11 R148F DDR_DQM0 PB30_ISI_HSYNC

F2 6 EBI0_DDR_DQM1 H16 P13

VSSQ DDR_DQM1 PB31/ISI_MCK/PCK1

F8

VSSQ DDR_DQS0 16 R144A nLRSHDN

H2 1 EBI0_DDR_DQS0 G18 A8

VSSQ DDR_DQS1 15 R148B DDR_DQS0 PC0/DQM2 LRMUTE

H8 2 EBI0_DDR_DQS1 G15 E9

VSSQ DDR_DQS1 PC1/DQM3 LRGAIN0 ETX0 LRGAIN1

B8 ETX0 LRGAIN1

I2C ADDRESSES:

DDR_BA0 PC2/A19 VDD VDD

J7 14 R148C 3 EBI0_DDR_BA0 G17 C8 LRGAIN1 VDD VDD ETX1

ETX1 0101000x (50/51): main volume control

VSSDL DDR_BA1 DDR_BA0 PC3/A20

13 R148D 4 EBI0_DDR_BA1 G16 F9 nCSHDN ETX2

ETX2 LRGAIN0 LRGAIN0 0101001x (52/53): center volume control

DDR_BA1 PC4/A21/NANDALE CMUTE C183 C184 ETX3

A7 ETX3 0101010x (54/55): headphone volume control

PC5/A22/NANDCLE CGAIN0 0.1µF 0.1µF ETXEN

DDR_VREF A16 D8 ETXEN LRMUTE LRMUTE

DDR_VREF PC6/A23 0110001x (62/63): EEP1 (software write protect register)

8

SDRAM is 133 MHz or faster, 1.8V, 84 pin FBGA, A6 CGAIN1 U42 U43 ETXCK

PC7/A24 ETXCK 1010001x (A2/A3): EEP1 (normal read/write)

lead-free. E8 HPSHDN 7 7 nLRSHDN nLRSHDN

VCC

VCC

PC8/CFCE1 WP WP

16 R146A 1 R195 10k A17 C7 ERX0

ERX0

10110011 (B3): EEP1 (serial number read)

D0 PC9/CFCE2/RTS2 nVA_EN CSDA ERX1

D15 B6 nVA_EN 5 CSDA 5 ERX1 CGAIN1 CGAIN1

1010000x (A0/A1): EEP2

D1 PC10/NCS4/CFCS0/TCLK2 SDA SDA

16 R147A 1 C15 B7 nVNB_EN

nVNB_EN

CSCL 6 CSCL 6 ERX2

ERX2

D2 PC11/NCS5/CFCS1/CTS2 SCL SCL ERX3

B16 A5 ERX3 CGAIN0 CGAIN0

VDD D3 PC12/A25/CFRNW

15 R147B 2 B15 VDDIOM1 D7 3 3

D4 3.3V PC13/NCS2 A2 A2 ERXCK

D14 F8 2 2 ERXCK CMUTE CMUTE

GND

GND

D5 PC14/NCS3/NANDCS A1 A1

14 R147C 3 R196 10k C14 C6 VDD 1 1 ERXDV

ERXDV

D6 PC15/NWAIT A0 A0

A15 E7 nCSHDN nCSHDN

D7 PC16/D16

16 R148A 1 B14 B5 AT24MAC402-SSHM AT24C256C-SSHL ERXER

ERXER

D8 PC17/D17

4

D13 D6 EEP1 Atmel EEP2 Atmel HPSHDN

D9 PC18/D18 HPSHDN

C13 F7 256B 32kB ECOL

D10 PC19/D19 ECOL

E13 A4 ECRS

D11 PC20/D20 ECRS

B13 C5 CN28

D12 PC21/D21 EMDC

E12 B4 NRST EMDC

D13 PC22/D22 4 EMDIO

D12 E6 CSDA EMDIO

VDD1_8 D14 PC23/D23 3

C12 D5 CSCL

L7 10µH, 100mA D15 PC24/D24 2

A3 nERST nERST

PC25/D25 1

A10 C4

NCS0 PC26/D26

F10 A1

R103 R104 NCS1/SDCS PC27/D27

F11 A2

1 C129 1.5k NRD PC28/D28

C9 B2

0.1µF NWR0/NWE PC29/D29

D9 B3

NWR1/NBS1 PC30/D30

DDR_VREF A9 B1 LDIN

NWR3/NBS3 PC31/D31

C130 R105 F13 R7 I2S_SCK0

2 4.7µF, 6.3V C131 1.5k A0/NBS0 PD0/TK0/PWM3 2

F14 T7 I2S_WS0

0.1µF A1/NBS2/NWR2 PD1/TF0

F18 L8 I2S_SD0

A2 PD2/TD0 USB_ENB

F15 V6

A3 PD3/RD0 USB_FLGB

E14 M8

A4 PD4/RK0

F17 V7 EMDINTR

A5 PD5/RF0 USB_ENA

F16 N8

A6 PD6/AC97RX USB_FLGA

E17 U7

A7 PD7/AC97TX/TIOA5

E15 P8

A8 PD8/AC97FS/TIOB5

E16 R8

A9 PD9/AC97CK/TCLK5

D18 U8 AVR_MOSI

A10 VDDIOP0 PD10/TD1

D17 T8 AVR_MISO

A11 3.3V PD11/RD1

C18 V8 AVR_CLK In 10-bit acquisition mode:

A12 PD12/TK1/PCK0 VDD

B18 L9 VBB = ADC(VBBSENSE) / 15.875

A13 PD13/RK1

A18 U9 AVR_nRST VNB = ADC(VNBSENSE) / 115.15

A14 PD14/TF1

B17 M9

A15 PD15/RF1 VA = ADC(VASENSE) / 25.817

C10 N9 RTS1 hardware R130 ADC center

A16/B10 PD16/RTS1 R91

B10 V9 CTS1 version ohms (1%) value (10 bit)

A17/BA1 PD17/CTS1 10k, 0.100W, 1%

C17 R9 INT INT C 0

A18 PD18/SPI1_NPCS2/IRQ

T9 FIQ

PD19/SPI1_NPCS3/FIQ E 150.0k 0x3bc VDD

A11 D2 VASENSE VASENSE

DQS0 PD20/TIOA0 RT1 VDD F 69.8k 0x37c

E11 E1 TEMP

DQS1 PD21/TIOA1 NCP21XV103J03RA C201 VDD

B11 F1 VBBSENSE G 43.2k 0x33c

DQM0 PD22/TIOA2 0.1µF

D11 G2 VNBSENSE VNBSENSE H 29.4k 0x2f8

DQM1 VDDANA PD23/TCLK0 R129 U8B

F2 VBBSENSE VBBSENSE I 21.5k 0x2b8

3.3V PD24/SPI0_NPCS1/PWM0 TEMP 10k, 0.100W, 1% LPC811M001JDH16

G1 TEMP

12

PD25/SPI0_NPCS2/PWM1 LSENSE J 16.5k 0x27c NXP

B9 H1 LSENSE

SDA10 PD26/PCK0/PWM2 K 12.7k 0x23c

B12 H2 HWVER HWVER

VDD

SDCKE PD27/PCK1/SPI0_NPCS3 L 10.0k 0x200 DI AVR_MISO

F12 P9 15 1

SDWE PD28/TSADTRG/SPI1_NPCS1 nLCD_RESET R130 AVR_nRST PIO0.6/VDDCMP PIO0.13 AVR_MOSI

A13 L10 nLCD_RESET M 7.68k 0x1bc 3 2

SDCK VDDIOP0 PD29/TCLK1/SCK1 LCD_CLKSEL 43.2k, 0.100W, 1% RXD0 nRESET/PIO0.5 PIO0.12 FIQ

T10 LCD_CLKSEL N 5.90k 0x17c 4 7

VCC 3.3V PD30/TIOB0/SCK2 BL_PWM AVR_CLK PIO0.4/WAKEUP/nTRST PIO0.11

L11 BL_PWM 5 8

PD31/TIOB1/PWM1 O 4.53k 0x140 SWCLK/PIO0.3/TCK PIO0.10 NSTAT

SEE HARDWARE 6 10

C122 VCC P 3.32k 0x100 AVR_MOSI SWDIO/PIO0.2/TMS PIO0.9/XTALOUT ROb

G4 VERSION 9 11

0.1µF, 25V PE0/LCDPWR/PCK0 Q 2.32k 0x0c0 TXD0 PIO0.1/ACMP_I2/CLKIN/TDI PIO0.8/XTALIN TXEN

C11 F4 TABLE 16 14

CAS PE1/LCDMOD PIO0.0/ACMP_I1/TDO PIO0.7

VSS

A12 G5

FB2 U19 RAS PE2/LCDCC

F5 LCDVSYNC LCDVSYNC

PE3/LCDVSYNC

7

BLM21PG600SN1D MIC2026-2YM G7 LCDHSYNC

PE4/LCDHSYNC LCDHSYNC

13

Murata H5 LCDDOTCK PIO0.12 is ISP

LCDDOTCK

VIN

USB_ENA PE5/LCDDOTCK LCDDEN

8 1 VDD E2 G3 LCDDEN

CN20 C123 OUTA ENA USB_FLGA TSADVREF PE6/LCDDEN LCDD0

2 H6 LCDD[23:0]

0.1µF, 25V FLGA PE7/LCDD0/LCDD2

+ C124 G6 LCDD1

33µF, 6.3V PE8/LCDD1/LCDD3

H7 LCDD2

USB_ENB PE9/LCDD2/LCDD4 R102 D6 VCC

1 5 4 H8 LCDD3

VCC FB3 OUTB ENB USB_FLGB PE10/LCDD3/LCDD5 120

2 HDMA 3 G8 LCDD4 2 1 VDD

GND

D- BLM21PG600SN1D FLGB PE11/LCDD4/LCDD6 C51 C52 VCC

3 HDPA A14 J5 LCDD5

D+ Murata NSDCK PE12/LCDD5/LCDD7 18pF 0.1µF VCC

4 use PIOs to E10 H4 LCDD6

GND NANDWE PE13/LCDD6/LCDD10 VCC VCC R19 D2 U7 VNB

pull up D10 J3 LCDD7

SHELL NANDOE PE14/LCDD7/LCDD11

6

C125 flags VDDIOP1 J4 LCDD8 120 2 1 SN65HVD485ED CN3

PE15/LCDD8/LCDD12 VDD

8

0.1µF, 25V + C126 3.3V J2 LCDD9 VDD Y1 U8 C53 TI R141

UE27AE54100 33µF, 6.3V R74 39 T18 PE16/LCDD9/LCDD13 14.7456 MHz ATtiny2313A-SU 0.1µF DI 1k 1

J6 LCDD10 4

20

VCC

1 Amphenol FCI R75 39 R18 HFSDPA PE17/LCDD10/LCDD14 C54 Atmel RO DI D+ 2 1

J7 LCDD11 1 6 D+

HFSDMA PE18/LCDD11/LCDD15 RO DO/RI 3

1

J1 LCDD12 R20 18pF R22 D3

VCC

HDPA PE19/LCDD12/LCDD18 10k 120 D31 D+ 4

T17 J8 LCDD13 X1 5 2 1 VDD

CN21 HHSDPA PE20/LCDD13/LCDD19 LCDD14 PA0/XTAL1 5

HDMA R17 K1 X2 4 2 7 D-

GND

HHSDMA PE21/LCDD14/LCDD20 AVR_nRST PA1/XTAL2 RE DO/RI 6

K4 LCDD15 1 12 TXEN 3

R76 39 V15 PE22/LCDD15/LCDD21 PA2/nRESET/dW PB0/AIN0/PCINT0 DE D- 7

K2 LCDD16 13

R77 39 V16 HFSDPB/DFSDP PE23/LCDD16/LCDD22 TXD0 PB1/AIN1/PCINT1 DI VDD D- 8

1 K5 LCDD17 2 14

VCC HFSDMB/DFSDM PE24/LCDD17/LCDD23 PD0/RXD PB2/OC0A/PCINT2

1

2 HDMB K6 LCDD18 RXD0 3 15 A-2004-2-4-LPS-N-R

D- PE25/LCDD18 PD1/TXD PB3/OC1A/PCINT3

5

3 HDPB HDPB U15 K3 LCDD19 6 16 NSTAT U50 Assmann

D+ HHSDPB/DHSDP PE26/LCDD19 VDD PD2/CKOUT/INT0 PB4/OC1B/PCINT4 D32 D33

4 HDMB U16 K7 LCDD20 7 17 AVR_MOSI 1 VCC

GND HHSDMB/DHSDM PE27/LCDD20 PD3/INT1 PB5/MOSI/DI/SDA/PCINT5 AVR_MISO SMAJ6.5CA

K8 LCDD21 8 18 4

GNDCORE0

GNDCORE1

GNDCORE2

GNDCORE3

SHELL PE28/LCDD21 PD4/T0 PB6/MISO/DO/PCINT6

5

L3 LCDD22 9 19 AVR_CLK 2 Bourns CN22

GNDIOM0

GNDIOM1

GNDIOM2

GNDIOM3

GNDIOM4

GNDIOM5

GNDIOM6

GNDIOP0

GNDIOP1

U48

GNDUTMI

GNDANA

GNDOSC

PE29/LCDD22 ROb PD5/OC0B/T1 PB7/UCSK/SCL/PCINT7

V18 L2 LCDD23 VCC 1 11 GND

GNDBU

UE27AE54100 MT1 F1 VBG PE30/LCDD23 PD6/ICP 74LVC1G08GV R142 1

1 L4 LCDPWM LCDPWM 4

GND

PE31/PWM2/PCK1 2

3

VDD

TST

Amphenol FCI R78 2 NXP 1k

3

1

1 MT2 6.8k C127 GND

F2 10pF, 50V C198 4

USB HOST PORTS NODE BUS BRIDGE AND INTERFACE 5

C2

U17

D3

U12

H9

J9

J10

G9

H10

J11

C16

H12

H13

J12

J13

K11

K12

E5

10

1 MT3 0.1µF

6

1

R79 1k 74LVC1G08GV Title

MT4 F3 NXP 7 Stern Pinball CPU Board

1

8

1

A-2004-2-4-LPS-N-R Size Document Number Rev

MOUNTING HOLES FIDUCIALS Assmann D 520-6936-01 B

Date: Monday, October 01, 2018 Sheet 1 of 8

A B C D E

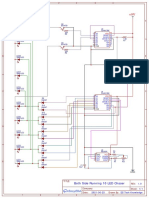

A B C D E

4 4

D40 D41 D42 D43 D44 D45 D46 D47 D48 D49

XQDAWT-00-0000-00000HDE5

CREE

3 3

VBB

1 TPAD7

D39 1 TPAD8

S1G-13-F

1 TPAD9

1 TPAD10

U33 1 TPAD11

C164 AP8801SG-13 R114

2.2µF 4 "Diodes, Inc." 1.1, 1/2W, 1% 1 TPAD12

VIN

1 1 TPAD13

SET

BL_PWM 8 L12 1 TPAD14

BL_PWM CTRL 470µH, 450mA

R161 5

SW1

GND1

GND2

330 6 D23

SW2

2 R115 CDBC560-G 2

2

7

1k Comchip

Vthd = 200 mV

Vref = 1.25V

Iled = Vctrl/Vref x Vthd/Rset

Vctrl = 3.3 x 1k / (330 + 1k) = 2.48V

Iled (target) = 350 mA

Rset = Vctrl/Vref x Vthd/Iled=2.48V/1.25V x 200mV/350mA=1.13 ohms

Rset = 1.1 ohms

Iled = 2.48/1.25 x 200mV/1.1 ohms = 360 mA

Power across Rset is (I^2)R = (360mA)^2 x 1.1 ohms = 143mW

1 1

Title

backlight

Size Document Number Rev

B 520-6936-01 B

Date: Monday, October 01, 2018 Sheet 4 of 8

A B C D E

A B C D E

4 VDD 4

FB18

AVDD

C108 C97

~53mA max C109 BLM21PG600SN1D 0.1µF 0.1µF

0.1µF Murata

VDDCR

C195 C96 VDD

R62

R63

R64

R65

1.0µF, 25V 470pF

U15 FB1

LAN8710A-EZC BLM21PG600SN1D

12

27

6

1

SMSC Murata

49.9

49.9

49.9

49.9

C110 CN17

VDDIO

VDDCR

VDD1A

VDD2A

27pF 5 29 TXP

XTAL1/CLKIN TXP 1

28 TXN

Y4 TXN 2

31 RXP

25.000 MHz RXP 3

30

C113 RXN 4

4

27pF XTAL2 5

RXN

6

C115 7

ETX0 0.022µF LEDG+ 8

ETX0 22

ETX1 TXD0 9

ETX1 23

ETX2 TXD1 C119 C120 C196 C197 LEDY+ 10

3 ETX2 24 3

ETX3 TXD2 10pF 10pF 10pF 10pF 11

ETX3 25 VDD

ETXEN TXD3 12

ETXEN 21

ETXCK R184 100 TXEN SHELL_0

ETXCK 20

TXCLK SHELL_1

ERX0 R183D SHELL_2

ERX0 13 4 11

ERX1 R183E RXD0/MODE0 SHELL_3

ERX1 12 5 10

ERX2 R183F RXD1/MODE1 J00-0065NL

ERX2 11 6 9

ERX3 R183G RXD2/RMIISEL Pulse

ERX3 10 7 8

RXD3/PHYAD2

ERXCK 9 R183H 8 7 9: left anode

ERXCK RXCLK/PHYAD1

ERXDV R185 100 26 3 R69 300, 0.100W, 5% 10: left cathode

ERXDV RXDV LED1/REGOFF

11: right cathode

VDD ERXER 14 R183C 3 13 2 R71 300, 0.100W, 5%

ERXER RXER/RXD4/PHYAD0 LED2/nINTSEL 12: right anode

ECOL 16 R183A 1 15 left is green (link/activity)

ECOL COL/CRS_DV/MODE2

ECRS 15 R183B 2 14 right is yellow (100Mb/s)

ECRS CRS

R182

1.5k EMDC 17

EMDC MDC

EMDIO 16

EMDIO MDIO

EMDINTR 18 32

EMDINTR INT/TXER/TXD4 RBIAS

2 nERST 19 R72 2

nERST

GND

nRST 12.1k, 0.063W, 1%

PAD

At reset:

PHYAD[2:0] should be driven low

MODE[2:0] should be driven high

RMIISEL should be driven low

From the boot loader drive nERST low, set the various

configuration pins, drive nERST high, then set the pins

back to inputs pulled high. nERST is PA31.

1 1

Title

Ethernet interface

Size Document Number Rev

B 520-6936-01 B

Date: Monday, October 01, 2018 Sheet 7 of 8

A B C D E

A B C D E

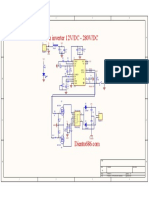

VBB

3.3VDC @ 500mA

D36 VCC D20 VDD VDD VDD

S1G-13-F DB3Y501KEL

+3.3V

9VDC @ 3A 1

R164 R191

+9V U9 3.83k, 0.100W, 1% R192 42.2k, 0.100W, 1%

VNB 1

U10 BD33KA5WFP 42.2k, 0.100W, 1%

C55 + C56 A8498SLJTR-T Rohm BOREF

8

470µF, 63V 0.22µF "Allegro MicroSystems, LLC" 2 4 VDD

4 VNB VIN OUT C58 R166 VDD 4

1

VIN

BOOT C59 L6 1µF, 6.3V VBB 2.26k, 0.100W, 1%

GND

0.01µF 68µH, 3A 1

CTL

8

nVNB_EN R197 10k 2 7

nVNB_EN ENB LX

8

R162 3 +

6

6 + C60 C57 42.2k, 0.100W, 1% 5 1 INT

VBIAS VCC + INT

3 470µF, 16V, low ESR 1µF, 6.3V 7 BO 2

TSET R23 VBBSENSE

-

U45A

6 -

6.34k, 0.100W, 1% C194 U45B LM393D

4

0.1µF, 16V R163 LM393D

1.8V @ 500mA

GND

PAD

4

R24 5 2.26k, 0.100W, 1% VDD

63.4k, 0.100W, 1% FB VCC D14 VDD1_8

4 DB3Y501KEL C185

PAD D4 R25 1 +1.8V

VBBSENSE

0.1µF, 16V

CDBC560-G 619, 0.100W, 1%

Comchip U31

1 TPAD3 BD18KA5WFP 48V / (42.2k + 2.26k) = 1.08 mA

VNB Rohm 48V x 1.08 mA = 52 mW

TP2 1 TPAD4 2 4 VBBsense = VBB x 2.26k / (42.2k + 2.26k) = VBB x 0.051

VIN OUT C136

R165 1µF, 6.3V

VBBsense(48V) = 48V*0.051 = 2.44V BROWN OUT DETECT

GND

3.83k, 0.100W, 1% BOREF(low)=1.18V

NODE BUS POWER SUPPLY 1

CTL BOREF(high)=1.29V

VNBSENSE C138 INT should assert (low) when VBB falls below 23.31V

3 VNBSENSE 3

6

1µF, 6.3V and should stay asserted until VBB rises above 25.36V

R167

2.26k, 0.100W, 1% VNBsense = VNB x 0.371 VA

VCC D15 VDD1_0 R193

DB3Y501KEL 42.2k, 0.100W, 1%

1 +1.0V

VASENSE

VBB VCC VNB VA VDD VASENSE

U32

BD10KA5WFP

1.0V @ 500mA R194

C139 Rohm VBB 3.83k, 0.100W, 1% VAsense = VA x 0.0832

1µF, 6.3V 2 4

R109 R133 R134 R135 R150 VIN OUT C137 D37

4.7k, 0.5W, 5% 300, 0.100W, 5% 680, 0.100W, 5% 2.2k, 0.250W, 5% 1.20k, 0.100W, 1% 1µF, 6.3V CDBC560-G

GND

1 Comchip

CTL

1

D13 D28 D29 D30

30VDC @ 3A

6

R151 R150 and R151 can be U6 +30V

VA 1

1.20k, 0.100W, 1% tuned to adjust the A8498SLJTR-T

8

VDDCORE turn-on C47 + C48 "Allegro MicroSystems, LLC"

470µF, 63V 0.22µF 1 VA

VIN

threshold. BOOT

2

C49 L5

2 0.01µF 68µH, 3A 2

VBB nVA_EN R198 10k 2 7

nVA_EN ENB LX

C173

3.3µF, 6.3WVDC, X5R 6 + C50

VBIAS VCC

D38 3 470µF, 35V, low ESR

S1G-13-F TSET R16

3

U41

-5.0V @ 60mA 6.34k, 0.100W, 1%

5

VCC TPS60402DBVT VCN

GND

PAD

U30 R125 5

C1+

C1-

A8498SLJTR-T 63.4k, 0.100W, 1% FB

8

"Allegro MicroSystems, LLC" ONLY USED BY

5.0V @ 3A 2 1 VCN

GND

IN OUT

4

PAD

C132+ C133 1 CENTER AUDIO D1 R18

VIN

470µF, 63V 0.22µF BOOT C134 L8 VCC C174 C175 CDBC560-G 174, 0.100W, 1%

CHANNEL

0.01µF 68µH, 3A 1 +5.0V Comchip

VCC

4

2 7 1 TPAD5

ENB LX 3.3µF, 6.3WVDC, X5R 3.3µF, 6.3WVDC, X5R

6 + C135 VDD TP3 1 TPAD6

VBIAS 470µF, 16V, low ESR

3

TSET R107

R106 6.34k, 0.100W, 1%

63.4k, 0.100W, 1% D50

AUDIO AMP POWER SUPPLY

GND

PAD

5 1 +48V DB3Y501KEL VDD

FB VBB

R108 VBB

4

PAD

1 D12 1.20k, 0.100W, 1% CN7 D51 1

CDBC560-G +48V R122 DB3Y501KEL

Comchip VBBS 5 82

nVBBGOOD

1 TPAD1 LSENSE 4

KEY 3 LSENSE

TPAD2 VBB GND 2 R190 Title

TP1 1

1 10k STERN Pinball CPU -- power supply

C200 26-63-4051

0.022µF Molex Size Document Number Rev

nVBBGOOD

B 520-6936-01 B

POWER IN

Date: Monday, October 01, 2018 Sheet 6 of 8

A B C D E

A B C D E

C179

1.0µF, 25V

CN27

1 LINE OUT

VDD 2 VA VA

CSCL 3

CSDA VDD

C28 C180 22-23-2031

0.1µF 1.0µF, 25V Molex VA + C9 + C10

U34 470µF 470µF

MCP4631T-104E/ML

15

4 Microchip Technology U2 4

TPA3123D2 CN1

10

12

19

20

VDD

1

3

CSCL 1 7 C13 C14 26-62-4056

SCL P1A 1.0µF, 25V L1 47uH, 2.9A 470µF, 50V Molex

CSDA 2

PVCCL1

PVCCL2

PVCCR1

PVCCR2

AVCC1

AVCC2

SDA SPKRL+

6 5 22

P1W LIN LOUT 5

+

C15 C16

0.22µF 0.39µF 4

13 5

A2 P1B C17 SPKRR+ 3

14 21

A1 C18 BSL L2 47uH, 2.9A 470µF, 50V 2

16

R1 HVC/A0 1.0µF, 25V 1

8 15

P0A ROUT

+

1, 0.100W, 5% 6 C19 C20

VDD RIN

9 0.22µF 0.39µF

P0W

+ 16

C1 C2 BSR

10

VSS1

VSS2

P0B

PAD

47µF 0.1µF R2 7 VA VA VA

1, 0.100W, 5% BYPASS

VDD nLRSHDN nLRSHDN 2

SD C22 C3 C4 C5

LRMUTE LRMUTE 4

MUTE

3

4

PAD

C11 + C12 ADDR: 0101000x 1.0µF, 25V 0.1µF 0.1µF 0.1µF

U1 47µF 0.1µF LRGAIN0 17

13

LRGAIN0 GAIN1

4

UDA1334ATS LRGAIN1 18 11

LRGAIN1 GAIN0 VCLAMP

VDDA

VDDD

PGNDR1

PGNDR2

VA VA VA

PGNDL1

PGNDL2

C24

AGND1

AGND2

I2S_SCK0 1 14 1.0µF, 25V

I2S_SCK0

GND

I2S_WS0 2 BCK VOUTL R136 C6 C7 C8

3 I2S_WS0 WS VCC VCN 3

I2S_SD0 3 10k 0.01µF 0.1µF 0.01µF

I2S_SD0 DATAI

23

24

13

14

8

9

PAD

10 VDD C98 C178

PLL0 0.1µF 0.1µF

6

SCLK/PLL1 C166 VDD

8

MUTE 0.1µF

9 16

DEEM/CLKOUT VOUTR U35 VCC VA

11 MCP4631T-104E/ML

15

SFOR0

8

7 12 Microchip Technology U36A

SFOR1 VREF(DAC) LM833DR R7 VCC U4

3 +

VDD

C21 + C23 CSCL 20k TPA3123D2 CN4

VSSA

1 7 1

VSSD

LEFT

10

12

19

20

SCL P1A

1

3

0.1µF CSDA 2 2 - R8 U37A C38 26-60-4020

47µF SDA 20k LM833DR 1.0µF, 25V L3 47uH, 2.9A Molex

6 3

PVCCL1

PVCCL2

PVCCR1

PVCCR2

+

AVCC1

AVCC2

P1W

1 5 22 SPKRC+

LIN LOUT 2

5

15

4

13 5 C181 R11 2 - C40 C41

VDD A2 P1B 1.0µF, 25V VCN 10k 0.22µF 0.39µF 1

14

A1 R9

16 21

HVC/A0 BSL

4

8 RIGHT 20k U37B C42 L4 47uH, 2.9A

P0A

-

MAIN AUDIO DAC 9 5 +

U36B

LM833DR

R10

20k

6

7

VCN 1.0µF, 25V

6

ROUT

15

C43

SPKRC-

C44

P0W RIN

+

7 5 0.22µF 0.39µF

10 C182 6 LM833DR 16

VSS1

VSS2

P0B - BSR

PAD

1.0µF, 25V

2 7 2

R159 R160 VCC VCN BYPASS VA VA

nCSHDN nCSHDN 2

SD

3

4

PAD

ADDR: 0101001x 10k 10k CMUTE 4 C45

CMUTE MUTE

Vout from UDA1334ATS is 0.9Vrms. Want to C168 C177 1.0µF, 25V

set gain such that full scale from DAC 0.1µF 0.1µF CGAIN1 17 + C35 + C36

CGAIN1 GAIN1

yields full swing on output (approx. 24V CGAIN0 18 11 470µF 470µF

CGAIN0 GAIN0 VCLAMP

p-p or 8.5Vrms).

PGNDR1

PGNDR2

VDD

PGNDL1

PGNDL2

C46

AGND1

AGND2

gain=20log(Vout/Vin)=20log(8.5/0.9)=19.5 1.0µF, 25V

GND

C167 VDD VCC

Input capacitor is calculated as 0.1µF

1/(2*PI*Z*fc) where Z is the amplifier's U38 R60 C99 R137

23

24

13

14

8

9

PAD

MCP4631T-104E/ML 20k, 0.100W, 5% VCC 0.1µF 10k

15

input impedance and fc is the -3dB cutoff

Microchip Technology VA VA VA

frequency (20Hz).

U18

VDD

gain=20: Cin=0.13 µF CSCL 1 7 LEFT C111 LM4881MX/NOPB C32 C33 C34

SCL P1A

8

gain=26: Cin=0.26 µF CSDA 2 0.33µF, 6.3V TI C112 CN18 0.01µF 0.1µF 0.01µF

SDA

+

6 2 1 HP_LEFT

VDD

P1W R61 INA OUTA 5

TPA3123D2 gain input strapping: 20k, 0.100W, 5% C114 4

13 5

A2 P1B 3

+

GAIN1 GAIN0 Gain Zinput -3 dB Cutoff R30 14 6 7 HP_RIGHT VA VA VA

VDD A1 INB OUTB 2

1 1 36 dB 9k 3Hz 0, 0.100W, 5% 16

HVC/A0 C116 1000µF, 6.3V 1 C29 C30 C31

8 RIGHT 5

GND

1 0 32 dB 15k 5Hz P0A 0.33µF, 6.3V SHDN SJ1-3535NG 0.1µF 0.1µF 0.1µF

3

0 1 26 dB 30k 11 Hz BYPASS CUI Inc.

1 9 1

0 0 20 dB 60k 18 Hz P0W R66 C117

4

10 20k, 0.100W, 5% 1.0µF, 25V

VSS1

VSS2

P0B

PAD

VDD

Title

3

4

PAD

ADDR: 0101010x R67 STERN Pinball CPU -- Audio

20k, 0.100W, 5%

R138 Size Document Number Rev

10k B 520-6936-01 B

HPSHDN

HEADPHONE AMPLIFIER

HPSHDN

Date: Monday, October 01, 2018 Sheet 5 of 8

A B C D E

A B C D E

4 4

VDD VDD

VDD

C169 C170 TO BOOT IN ISP MODE HOLD

0.1µF 0.1µF nDMISP LOW AND CYCLE nDMRST

U40 LOW THEN HIGH. TO BOOT

LPC1113FBD48/301

44

NORMALLY HOLD nDMISP HIGH AND

8

NXP

CYCLE nDMRST LOW THEN HIGH. VCC

VDD1

VDD2

FB11

6 3 nDMRST BLM21PG600SN1D

XTALIN nRESET/PIO0.0 nDMRST

4 nDMISP Murata

PIO0.1/CLKOUT/CT32B0_MAT2 nDMISP

10 SSEL0 CN24

PIO0.2/SSEL0/CT16B0_CAP0 SPI0_NPCS0

14 VDD

PIO0.3 1

15

PIO0.4/SCL 2

7 16

XTALOUT PIO0.5/SDA SCK0 3

22 SPI0_SPCK

PIO0.6/SCK0 4

23

PIO0.7/nCTS nDMRDY 26-60-4040

27 nDMRDY

PIO0.8/MISO0/CT16B0_MAT0 MOSI0 Molex

28 SPI0_MOSI

PIO0.9/MOSI0/CT16B0_MAT1

29

SWCLK/PIO0.10/SCK0/CT16B0_MAT2

R/PIO0_11/AD0/CT32B0_MAT3

32

POWER FOR

3

DOT MATRIX

3

33

R/PIO1.0/AD1/CT32B1_CAP0

34

R/PIO1.1/AD2/CT32B1_MAT0

35

R/PIO1.2/AD3/CT32B1_MAT1

39

SWDIO/PIO1.3/AD4/CT32B1_MAT2

40

PIO1.4/AD5/CT32B1_MAT3/WAKEUP

45

PIO1.5/nRTS/CT32B0_CAP0 TXD3

46 TXD3

PIO1.6/RXD/CT32B0_MAT0 RXD3

47 RXD3

PIO1.7/TXD/CT32B0_MAT1

9

PIO1.8/CT16B1_CAP0 FB12

17 DE CN23

PIO1.9/CT16B1_MAT0 DE1

30 1 2

PIO1.10/AD6/CT16B1_MAT1 RDATA1 + +

42 3 4

PIO1.11/AD7 RCLK1 + +

5 6

FB13 COLLATCH1 + +

2 COLLATCH 7 8

PIO2.0/nDTR/SSEL1 FB14 DOTCLK1 + +

13 DOTCLK 9 10

PIO2.1/nDSR/SCK1 SDATA1 + +

26 11 12

PIO2.2/nDCD/MISO1 FB15 + +

38 SDATA 13 14

PIO2.3/nRI/MOSI1 + +

19

PIO2.4

20

PIO2.5 XG4A-1432

1

PIO2.6 FB16 Omron Electronics Inc

11 RDATA

PIO2.7 FB17

12 RCLK

PIO2.8

2

PIO2.9

24

25 MMZ1608R301A TO DOT MATRIX 2

PIO2.10 TDK C186 C187 C188 C189 C190 C191

31

PIO2.11/SCK0 47pF 47pF 47pF 47pF 47pF 47pF

36

PIO3.0/nDTR

37

PIO3.1/nDSR

43

PIO3.2/nDCD

48

PIO3.3/nRI

18

PIO3.4

21

VSS1

VSS2

PIO3.5

5

41

1 1

Title

dot matrix display interface

Size Document Number Rev

B 520-6936-01 B

Date: Monday, October 01, 2018 Sheet 8 of 8

A B C D E

A B C D E

4 4

LCDD[23:0]

CN19

DF12(5.0)-50DP-0.5V

Hirose

1 2 LCDD1

LCDD0

3 4 LCDD3

LCDD2

5 6 LCDD5

LCDD4

7 8 LCDD7

LCDD6

9 10 LCDD9

LCDD8

11 12 LCDD11

LCDD10

13 14 LCDD13

LCDD12

15 16 LCDD15

3 LCDD14 3

17 18 LCDD17

LCDD16

19 20 LCDD19

LCDD18

21 22 LCDD21

LCDD20

23 24 LCDD23

LCDD22

LCDHSYNC 25 26 LCDVSYNC

LCDHSYNC 27 28 LCDVSYNC

LCDDEN LCDDOTCK

LCDDEN 29 30 LCDDOTCK

LCD_CLKSEL nLCD_RESET

LCD_CLKSEL 31 32 nLCD_RESET

LCDPWM LCDPWM

33 34

35 36

37 38

39 40

VDD 41 42

FB5 C102 C103 43 44

VCC 45 46

MMZ1608R301A 0.1µF 0.1µF

TDK FB4 C100 C101 47 48

VBB 49 50 VBB

MMZ1608R301A 0.1µF 0.1µF

TDK

2 LCDD7:0 = RED 2

LCDD15:8 = GREEN

MT7 MT8

USE KEYSTONE 24390 5.0mm M3 LCDD23:16 = BLUE

SPACER OR EQUIVALENT

1

COLOR DATA IS ALWAYS TOP-JUSTIFIED

(e.g., IF ONLY FIVE BITS OF RED ARE

USED THEY ARE MAPPED TO LCDD7:3)

1 1

Title

video interface

Size Document Number Rev

B 520-6936-01 B

Date: Monday, October 01, 2018 Sheet 3 of 8

A B C D E

You might also like

- DX Blame Mkii Supercharged SchematicDocument1 pageDX Blame Mkii Supercharged SchematicRodrigo Negrelli100% (1)

- SpaceX Annual ReportDocument2 pagesSpaceX Annual ReportKv AnimationsNo ratings yet

- 802 - Opb1310-Opm1310-Opb1312-Opm1312Document2 pages802 - Opb1310-Opm1310-Opb1312-Opm1312Bidu BiduNo ratings yet

- Tranca Microcontrolada PDFDocument1 pageTranca Microcontrolada PDFAlessandro AlvesNo ratings yet

- Stepper Steps 2speeds ReverseDocument1 pageStepper Steps 2speeds ReverseKamelNo ratings yet

- Sheet 1Document2 pagesSheet 1Huynh TrinhNo ratings yet

- GND GND: Caixa Multi Uso Pre Ampli + FonteDocument2 pagesGND GND: Caixa Multi Uso Pre Ampli + FonteLuis BagarelliNo ratings yet

- Schematic JBL+MAX12 2023-10-04+Document1 pageSchematic JBL+MAX12 2023-10-04+Claudean SoaresNo ratings yet

- Schematic Shift-Registers Sheet-1 20181117003103 PDFDocument1 pageSchematic Shift-Registers Sheet-1 20181117003103 PDFHà Văn ThạnhNo ratings yet

- Silowa 4 AstDocument1 pageSilowa 4 AstНиколай ИвановNo ratings yet

- IsiDocument1 pageIsiJoel EliséNo ratings yet

- Koch Studiotone Schematics 1401-1800Document3 pagesKoch Studiotone Schematics 1401-1800José Ramón Abella AldeguerNo ratings yet

- Amp Expandible PDFDocument21 pagesAmp Expandible PDFCarlos VasquezNo ratings yet

- Rock DriveDocument1 pageRock DrivetognonNo ratings yet

- Carl Martin - Rock DriveDocument3 pagesCarl Martin - Rock DriveJesse ArceNo ratings yet

- Montarbo 112sa PDFDocument1 pageMontarbo 112sa PDFOussama AzertaNo ratings yet

- Bal Card Schematic PDFDocument1 pageBal Card Schematic PDFHelder Fernandes FonsecaNo ratings yet

- Laney AH50Document2 pagesLaney AH50Zoeloe_2No ratings yet

- Drac 1Document1 pageDrac 1Al KaNo ratings yet

- It Ee09Document1 pageIt Ee09Leonardo PaulNo ratings yet

- Micro Terror JFETDocument1 pageMicro Terror JFETwalterdadaNo ratings yet

- Esquema Eletrico - MG10Document1 pageEsquema Eletrico - MG10Daniel Kessler Dan100% (1)

- Audio VU MeterDocument2 pagesAudio VU Meter202457100% (1)

- Schematic SG3525Document1 pageSchematic SG3525Muhammad AminNo ratings yet

- Ubo Kenotektek Amp - SCHDocument1 pageUbo Kenotektek Amp - SCHRonald Sander SrlNo ratings yet

- FreqC 16F628A ElementsDocument1 pageFreqC 16F628A Elementsjubeng100% (1)

- 2x Gain BTL With 2 Pcs Transistor: Main Supply 1x GAIN R13 18K 2x GAIN R13 4K7Document2 pages2x Gain BTL With 2 Pcs Transistor: Main Supply 1x GAIN R13 18K 2x GAIN R13 4K7mdeky20No ratings yet

- Studiotone SchematicsDocument3 pagesStudiotone SchematicsatsukiNo ratings yet

- Schematic Mono-4558b Sheet-1 20180420211056 PDFDocument1 pageSchematic Mono-4558b Sheet-1 20180420211056 PDFAPLCTNNo ratings yet

- Power Digital Studio 700 Rev 1Document1 pagePower Digital Studio 700 Rev 1Lindomar ChavesNo ratings yet

- Ucd OCPDocument1 pageUcd OCPAlain Jaramillo RuizNo ratings yet

- De 20schema PDFDocument1 pageDe 20schema PDFSaker SahaguengNo ratings yet

- UcD FD1K Full Discrete Class D Amplifir Ver.1 - Feb2021Document1 pageUcD FD1K Full Discrete Class D Amplifir Ver.1 - Feb2021Azzuhry Miftman100% (1)

- M CH Inverter 12V/DC - 280V/DCDocument1 pageM CH Inverter 12V/DC - 280V/DCKhoa NguyễnNo ratings yet

- Inverterv3 PDFDocument1 pageInverterv3 PDFKhoa NguyễnNo ratings yet

- Schematic - The Both Side Running 10 Led Chaser - 2021-06-25Document1 pageSchematic - The Both Side Running 10 Led Chaser - 2021-06-25julio quatriniNo ratings yet

- PCB Wizard - Sun TrackerDocument2 pagesPCB Wizard - Sun TrackerArunkumar Murugappan100% (1)

- Cad Praktek Tugas 1.3: Nama: Cakra Rizky Fortuna KLS: To-2A NRP: 0920040020 A. Opamp Layout, PCB, Dan 3DDocument6 pagesCad Praktek Tugas 1.3: Nama: Cakra Rizky Fortuna KLS: To-2A NRP: 0920040020 A. Opamp Layout, PCB, Dan 3DcaktotNo ratings yet

- 50W Mono Low Voltage Amplifier Technical MrigankaDocument2 pages50W Mono Low Voltage Amplifier Technical Mrigankaluis albertoNo ratings yet

- FinalDocument1 pageFinalrcbp2167No ratings yet

- Equincy MeasurementDocument1 pageEquincy MeasurementVadivel RajaNo ratings yet

- TermometroDocument1 pageTermometroRafael Macfú100% (1)

- McBennett VCF - R27 RevDocument1 pageMcBennett VCF - R27 RevAdrianoEngelNo ratings yet

- SOCL-504 Modded Ver.1Document2 pagesSOCL-504 Modded Ver.1gjy56pbgr8No ratings yet

- 853D - V1Document1 page853D - V1asmedmirandaNo ratings yet

- Super Mini Micro UCD DiscreteDocument1 pageSuper Mini Micro UCD DiscreteAnggas HadaianNo ratings yet

- OsciladorDocument1 pageOsciladoranthony__123No ratings yet

- Apex Ax14 SCH PDFDocument2 pagesApex Ax14 SCH PDFNam TàoNo ratings yet

- Apex Ax14 SCH (Et)Document2 pagesApex Ax14 SCH (Et)Astom KumarNo ratings yet

- Apex Ax14 SCHDocument2 pagesApex Ax14 SCHHamass ShofwanuddinNo ratings yet

- APEX AXffffffffff PDFDocument2 pagesAPEX AXffffffffff PDFAurelio Moreno100% (1)

- Apex Ax14 SCH PDFDocument2 pagesApex Ax14 SCH PDFOnesimus Tozeyana100% (1)

- Spice Py Modelica JModelica EpsDocument35 pagesSpice Py Modelica JModelica EpsPeter MüllerNo ratings yet

- Schematic Mangava 2024-04-05Document1 pageSchematic Mangava 2024-04-05Luiz Augusto Freitas SantosNo ratings yet

- Circuito-Gerador de Sinais Com 555Document1 pageCircuito-Gerador de Sinais Com 555João Pedro da Silva RodriguesNo ratings yet

- KB620Document1 pageKB620vinayaravNo ratings yet

- 1 Con PicDocument1 page1 Con Picapi-3714448No ratings yet

- LP2985 150-Ma Low-Noise Low-Dropout Regulator With Shutdown: 1 Features 3 DescriptionDocument28 pagesLP2985 150-Ma Low-Noise Low-Dropout Regulator With Shutdown: 1 Features 3 DescriptionzokiNo ratings yet

- Galaga Renewal KitDocument8 pagesGalaga Renewal KitzokiNo ratings yet

- Marantz Sr7008 Receiver User ManualDocument286 pagesMarantz Sr7008 Receiver User ManualzokiNo ratings yet

- USB005 User GuideDocument5 pagesUSB005 User GuidezokiNo ratings yet

- 12C 508Document2 pages12C 508zokiNo ratings yet

- HDQ Communication Basics For Ti'S Battery Monitor Ics: Application ReportDocument8 pagesHDQ Communication Basics For Ti'S Battery Monitor Ics: Application ReportzokiNo ratings yet

- ROMs ProDocument6 pagesROMs ProzokiNo ratings yet

- Service Manual (Common) : Gn5Un Chassis Segment: SGDocument148 pagesService Manual (Common) : Gn5Un Chassis Segment: SGzokiNo ratings yet

- Galaxy Electrical Zener Diodes: FeaturesDocument5 pagesGalaxy Electrical Zener Diodes: FeatureszokiNo ratings yet

- NCP1380 Quasi-Resonant Current-Mode Controller For High-Power Universal Off-Line SuppliesDocument26 pagesNCP1380 Quasi-Resonant Current-Mode Controller For High-Power Universal Off-Line SupplieszokiNo ratings yet

- 32phh4200 88 Fhi HRVDocument3 pages32phh4200 88 Fhi HRVzokiNo ratings yet

- DRAMs ProDocument2 pagesDRAMs ProzokiNo ratings yet

- SMDIN100Document3 pagesSMDIN100zokiNo ratings yet

- SMD29130CCDocument1 pageSMD29130CCzokiNo ratings yet

- AC Input: Circuit Diagrams and PWB LayoutsDocument7 pagesAC Input: Circuit Diagrams and PWB LayoutszokiNo ratings yet

- 32pht4132 05 Fhi Eng PDFDocument2 pages32pht4132 05 Fhi Eng PDFzokiNo ratings yet

- 32phs4112 12 Fhi NLD PDFDocument2 pages32phs4112 12 Fhi NLD PDFzokiNo ratings yet

- Shaper Planner SlotterDocument49 pagesShaper Planner SlotterDeepak RaiNo ratings yet

- 5 NM RC65 10 and 17 Watts 17 W Part Number Made To OrderDocument3 pages5 NM RC65 10 and 17 Watts 17 W Part Number Made To OrderasdasdghtNo ratings yet

- Chiller Column Beam ErectionDocument6 pagesChiller Column Beam ErectionShrikant SawantNo ratings yet

- CCPS Guidelines For LOPC CasesDocument24 pagesCCPS Guidelines For LOPC CasesMuhammad Wahaj ButtNo ratings yet

- IPSS Hand BookDocument39 pagesIPSS Hand BookAaditya SharmaNo ratings yet

- Pfeifer Drako - Steel Wire Ropes PDFDocument40 pagesPfeifer Drako - Steel Wire Ropes PDFEdmundo CamposNo ratings yet

- Deep Copy and ShallowDocument6 pagesDeep Copy and ShallowAbhishek SrivastavaNo ratings yet

- Linker and LoadersDocument41 pagesLinker and LoadersVishal Kumkar50% (2)

- Online Reservation SystemDocument12 pagesOnline Reservation SystemBaloy N. Da Haus20% (5)

- Jenell Strachan - ResumeDocument2 pagesJenell Strachan - ResumejjastrachanNo ratings yet

- Opportunities Naturalfiber CompositesDocument35 pagesOpportunities Naturalfiber CompositesGopalMahantaNo ratings yet

- Pub 100426Document5 pagesPub 100426Milagros Chuyin100% (1)

- Ge 211 Student Enter Exit Survey 372 BlueDocument1 pageGe 211 Student Enter Exit Survey 372 BlueDanialNo ratings yet

- Properties of Common Spring MaterialsDocument2 pagesProperties of Common Spring MaterialsArnaldo Morbid CruzNo ratings yet

- Air Cooled Packaged Inverter Floor Standing Type - Heat Pump 50Hz - APCVDT1512Document54 pagesAir Cooled Packaged Inverter Floor Standing Type - Heat Pump 50Hz - APCVDT1512Phanhai Kaka100% (1)

- Articulo de RbiDocument23 pagesArticulo de RbiALberto AriasNo ratings yet

- Checklist of Generic Safety Hazards and RisksDocument10 pagesChecklist of Generic Safety Hazards and Riskstzoltek2368No ratings yet

- Voltage Amplification, Trail Cable Length & Power ShovelsDocument9 pagesVoltage Amplification, Trail Cable Length & Power ShovelsMaikPortnoyNo ratings yet

- 45 Series F Frame 74cc and 90cc Parts Manual (11007197 Rev AA Feb 2007)Document48 pages45 Series F Frame 74cc and 90cc Parts Manual (11007197 Rev AA Feb 2007)Alaa saidNo ratings yet

- SPM 4531 2007 Physics p2 BerjawapanDocument26 pagesSPM 4531 2007 Physics p2 Berjawapanpss smk selandar75% (4)

- Cooling System Cat C-15 & C-18Document5 pagesCooling System Cat C-15 & C-18Harzanyi MaldonadoNo ratings yet

- Pile Load Test Methodology - Kentledge Method - Cyclic-RoutineDocument10 pagesPile Load Test Methodology - Kentledge Method - Cyclic-RoutineHarshit DubeyNo ratings yet

- Build PropDocument8 pagesBuild PropYour FreedomNo ratings yet

- Abb Parts Fiser68261899 PDFDocument2 pagesAbb Parts Fiser68261899 PDFsuzell9fiorella9ascaNo ratings yet

- 4A2 Determination of Cohesive Arching Characteristics in Ore PassesDocument10 pages4A2 Determination of Cohesive Arching Characteristics in Ore Passesjbrevis2018No ratings yet

- AE 1350 Lecture Notes #7Document30 pagesAE 1350 Lecture Notes #7Mahesh IndeNo ratings yet

- Catalog Berkeley Pump Vertical Multi-Stage Booster BVM Series 284Document36 pagesCatalog Berkeley Pump Vertical Multi-Stage Booster BVM Series 284Edson Alonso Morales VegaNo ratings yet

- CSC248 Julai 22 QuizDocument9 pagesCSC248 Julai 22 QuizAdib AfhamNo ratings yet

- Arc Welding FaultsDocument7 pagesArc Welding FaultsleijuliaNo ratings yet