Professional Documents

Culture Documents

2019 2020 Ieee Vlsi Project Titles PDF

2019 2020 Ieee Vlsi Project Titles PDF

Uploaded by

NamrathaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

2019 2020 Ieee Vlsi Project Titles PDF

2019 2020 Ieee Vlsi Project Titles PDF

Uploaded by

NamrathaCopyright:

Available Formats

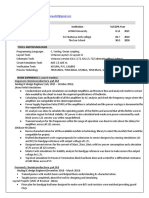

2019 - 2020 VLSI IEEE FINAL YEAR Projects @ JP iNFOTeCH

S.NO

Project IEEE 2019-20 VLSI Project Titles

Code

LOW POWER

1 JPV1901 A 0.3-V 37-nW 53-dB SNDR Asynchronous Delta–Sigma Modulator in 0.18-μm CMOS

2 JPV1902 A 12-bit, 2.5-bit/Phase Column-Parallel Cyclic ADC

3 JPV1903 A 16-bit 2.0-ps Resolution Two-Step TDC in 0.18-μm CMOS Utilizing Pulse-Shrinking Fine Stage With Built-

In Coarse Gain Calibration

4 JPV1904 A Dynamic Timing Error Avoidance Technique Using Prediction Logic in High-Performance Designs

5 JPV1905 A Wideband Low-Noise Variable-Gain Amplifier with a 3.4 dB NF and up to 45 dB gain tuning range in 130

nm CMOS

6 JPV1906 Analysis, Comparison, and Experimental Validation of a Class AB Voltage Follower With Enhanced

Bandwidth and Slew Rate

7 JPV1907 Column-Selection-Enabled 10T SRAM Utilizing Shared Diff-VDD Write and Dropped-VDD Read for Power

Reduction

8 JPV1908 Designing Efficient Circuits Based on Runtime-Reconfigurable Field-Effect Transistors

9 JPV1909 Exploiting Algorithmic Noise Tolerance for Scalable On-Chip Voltage Regulation

10 JPV1910 Fully Differential 4-V Output Range 14.5-ENOB Stepwise Ramp Stimulus Generator for On-Chip Static

Linearity Test of ADCs

11 JPV1911 Low-Power Near-Threshold 10T SRAM Bit Cells With Enhanced Data-Independent Read Port Leakage for

Array Augmentation in 32-nm CMOS

12 JPV1912 Many-Objective Sizing Optimization of a Class-C/D VCO for Ultralow-Power IoT and Ultralow-Phase-Noise

Cellular Applications

13 JPV1913 Multiloop Control for Fast Transient DC–DC Converter

14 JPV1914 Radiation-Hardened 14T SRAM Bitcell With Speed and Power Optimized for Space Application

HIGH SPEED AND SIGNAL PROCESSING

15 JPV1915 A 0.9-V 12-Gb/s Two-FIR Tap Direct DFE With Feedback-Signal Common-Mode Control

Contact: Dr.R.JAYAPRAKASH BE,MBA,M.Tech.,Ph.D., Mobile: (0)9952649690

Web: www.jpinfotech.org | Blog: www.jpinfotech.blogspot.com | Email: jpinfotechprojects@gmail.com

16 JPV1916 A 2.4-GHz Frequency-Drift-Compensated Phase-Locked Loop With 2.43 ppm/°C Temperature Coefficient

17 JPV1917 A High-Flexible Low-Latency Memory-Based FFT Processor for 4G, WLAN, and Future 5G

18 JPV1918 An Accurate and Noise-Resilient Spread-Spectrum Clock Tracking Aid for Digitally-Controlled Clock and

Data Recovery Loops

19 JPV1919 An Analog LO Harmonic Suppression Technique for SDR Receivers

20 JPV1920 An Area-Efficient 128-Channel Spike Sorting Processor for Real-Time Neural Recording With 0.175

μW/Channel in 65-nm CMOS

21 JPV1921 Analysis and Optimization of Multisection Capacitive DACs for Mixed-Signal Processing

22 JPV1922 CMOS First-Order All-Pass Filter With 2-Hz Pole Frequency

23 JPV1923 Design of Reconfigurable Digital IF Filter with Low Complexity

24 JPV1924 Feedforward-Cutset-Free Pipelined Multiply–Accumulate Unit for the Machine Learning Accelerator

25 JPV1925 Line Coding Techniques for Channel Equalization: Integrated Pulse-Width Modulation and Consecutive

Digit Chopping

26 JPV1926 Multiplier-free Implementation of Galois Field Fourier Transform on a FPGA

27 JPV1927 Power-Efficient Gm-C DSMs With High Immunity to Aliasing, Clock Jitter, and ISI

AREA EFFICIENT/ TIMING & DELAY REDUCTION

28 JPV1928 A Combined Arithmetic-High-Level Synthesis Solution to Deploy Partial Carry-Save Radix-8 Booth

Multipliers in Datapaths

29 JPV1929 A Decoder for Short BCH Codes With High Decoding Efficiency and Low Power for Emerging Memories

30 JPV1930 A High-Throughput Hardware Accelerator for Lossless Compression of a DDR4 Command Trace

31 JPV1931 An Energy-efficient Accelerator based on Hybrid CPU-FPGA Devices for Password Recovery

32 JPV1932 Area–Delay–Energy Efficient VLSI Architecture for Scalable In-Place Computation of FFT on Real Data

33 JPV1933 Area-Time Efficient Streaming Architecture for FAST and BRIEF Detector

34 JPV1934 Chaos-Based Bitwise Dynamical Pseudorandom Number Generator on FPGA

35 JPV1935 Efficient Design for Fixed-Width Adder-Tree

Contact: Dr.R.JAYAPRAKASH BE,MBA,M.Tech.,Ph.D., Mobile: (0)9952649690

Web: www.jpinfotech.org | Blog: www.jpinfotech.blogspot.com | Email: jpinfotechprojects@gmail.com

36 JPV1936 Hardware-Efficient Post-processing Architectures for True Random Number Generators

37 JPV1937 Multistage Linear Feedback Shift Register Counters With Reduced Decoding Logic in 130-nm CMOS for

Large-Scale Array Applications

38 JPV1938 New Majority Gate Based Parallel BCD Adder Designs for Quantum-dot Cellular Automata

39 JPV1939 Rapid Balise Telegram Decoder with Modified LFSR Architecture for Train Protection Systems

PROJECT SUPPORT TO REGISTERED STUDENTS:

1) IEEE Base paper.

2) Abstract Document.

3) Future Enhancement (based on Requirement).

4) Modified Title / Modified Abstract (based on Requirement).

5) Complete Source Code/Simulation File/ Hardware Kit.

6) How to Run execution help file.

7) Software Packages

8) International Conference / International Journal Publication based on your

project.

OUR OTHER SALIENT FEATURES:

Number 1 Project Master in Pondicherry/Puducherry.

Guided more than 60,000 students.

Successfully conducted more than 25 International Conferences in all over

South India from 2013 to 2019.

For the academic year 2019- 2020, we have Signed MoU with Many

Engineering Colleges in all over India to Conduct International

Conferences in academic year 2019 – 2020, Where the Registered Students

of JP INFOTECH, can easily publish their Project Papers.

Contact: Dr.R.JAYAPRAKASH BE,MBA,M.Tech.,Ph.D., Mobile: (0)9952649690

Web: www.jpinfotech.org | Blog: www.jpinfotech.blogspot.com | Email: jpinfotechprojects@gmail.com

Published more than 6000 Research Articles of Our

Ph.D./M.Phil/ME/M.Tech./BE/B.Tech. Students in Leading

International Conferences and International Journals from 2013 to 2019.

From the year 2013 to 2019, we are Recognized and Awarded from the

following colleges: “Paavai College of Engg”, “Arjun College of

Technology”, “K.S.R. College of Engineering”, “Vetri Vinayaha College Of

Engineering And Technology”, “SKR Engineering College”, “Sree Sastha

Institute of Engineering and Technology”, “Jaya Engineering College”,

“V.P.Muthaiah Pillai Meenakshi Ammal Engineering College for Women”,

“Muthayammal Arts and Science College”, “Sri Raaja Raajan College of

Engineering and Technology”, “Latha Mathavan Engineering College”,

“Dr Pauls Engineering College”, “Jain College of Engineering”, “Manakula

Vinayagar Institute of Technology”, “CK College of Engineering &

Technology” etc.

Recognized and published article about JP INFOTECH and its director in

“THE HINDU”, “DINAKARAN” and many more newspapers and Media.

Leaders with more than 9+ years of experience

We assist and guarantee you to publish a paper on your project in

INTERNATIONAL JOURNAL PUBLICATIONS / INTERNATIONAL

CONFERENCE PUBLICATIONS.

NO FALSE PROMISES

100% Assurance for Project Execution

Valid Project Completion Certificate

100% PLACEMENT SUPPORT

Own Projects are also welcomed.

So don’t wait any more!!! Join us and be a part of us. Walk-in to our Office OR E-

mail us your requirements and Register your projects.

Contact: Dr.R.JAYAPRAKASH BE,MBA,M.Tech.,Ph.D., Mobile: (0)9952649690

Web: www.jpinfotech.org | Blog: www.jpinfotech.blogspot.com | Email: jpinfotechprojects@gmail.com

For any queries Contact:

Dr.R.JAYAPRAKASH BE,MBA,M.Tech.,Ph.D.,

Managing Director, JP INFOTECH.

MOBILE: (0)9952649690

EMAIL: jpinfotechprojects@gmail.com

WEBSITE: www.jpinfotech.org

Watch Video Demos on our Youtube Channel:

https://www.youtube.com/jpinfotechprojects

Contact: Dr.R.JAYAPRAKASH BE,MBA,M.Tech.,Ph.D., Mobile: (0)9952649690

Web: www.jpinfotech.org | Blog: www.jpinfotech.blogspot.com | Email: jpinfotechprojects@gmail.com

You might also like

- 50 Tapping Scripts Gene MonterastelliDocument27 pages50 Tapping Scripts Gene Monterastellilalek00100% (5)

- Solutions Debraj Ray 1Document62 pagesSolutions Debraj Ray 1Gaurav KawediaNo ratings yet

- GlobalFoundries 2014 US Tech Seminar - Proceeding Book PDFDocument316 pagesGlobalFoundries 2014 US Tech Seminar - Proceeding Book PDFWeikai SunNo ratings yet

- Report Analog IC DesignDocument2 pagesReport Analog IC DesignAvinash GuptaNo ratings yet

- AGV Project ReportDocument46 pagesAGV Project ReportPratheesh Pala100% (7)

- PA 31 - 350 Listas de Chequeo Piernera (Revision #4) PDFDocument6 pagesPA 31 - 350 Listas de Chequeo Piernera (Revision #4) PDFDany Rodriguez AlvarezNo ratings yet

- English Literacy NarrativeDocument4 pagesEnglish Literacy Narrativeapi-325516593No ratings yet

- Research Paper On RF ModuleDocument6 pagesResearch Paper On RF Moduleefe8zf19100% (1)

- Thesis On PWM TechniquesDocument9 pagesThesis On PWM TechniquesBuyCheapPapersMiramar100% (2)

- 0710ijcnc04 PDFDocument10 pages0710ijcnc04 PDFJam 234No ratings yet

- Anum Ahmed Pirkani UkDocument5 pagesAnum Ahmed Pirkani UkAnum AhmedNo ratings yet

- Ec6511 DSP Lab ManualDocument156 pagesEc6511 DSP Lab Manualramadossapece100% (5)

- Design of An Efficient Reversible Floating Point Arithmetic Unit For Digital Signal ProcessorsDocument265 pagesDesign of An Efficient Reversible Floating Point Arithmetic Unit For Digital Signal ProcessorsGOWTHAMI PNo ratings yet

- DC Report - 486,487,488Document13 pagesDC Report - 486,487,488Anvesh MagantiNo ratings yet

- Low Power Analog Electronics For Portable and Autonomous ApplicationsDocument40 pagesLow Power Analog Electronics For Portable and Autonomous ApplicationsparagaggNo ratings yet

- Latest Research Paper On FpgaDocument5 pagesLatest Research Paper On Fpgapykig1nupyf3100% (1)

- EDN Magazine April 7 2011Document58 pagesEDN Magazine April 7 2011Joyce GeorgeNo ratings yet

- Thesis Report On Low Power VlsiDocument7 pagesThesis Report On Low Power Vlsiashleylovatoalbuquerque100% (2)

- KhushiDocument15 pagesKhushiparwatenishikantNo ratings yet

- Use Analog For Better Performance-To-Power RatiosDocument4 pagesUse Analog For Better Performance-To-Power RatiosAdyPajuraNo ratings yet

- Shwetank-Sample CV Resume Asic PD RoleDocument7 pagesShwetank-Sample CV Resume Asic PD Rolesaugatguha2569No ratings yet

- Optical Cdma ThesisDocument5 pagesOptical Cdma Thesisjenniferriveraerie100% (2)

- Mounika.M: Education Program Institution %/CGPA YearDocument3 pagesMounika.M: Education Program Institution %/CGPA Yearmounika morampudiNo ratings yet

- Ieee Research Paper On VlsiDocument6 pagesIeee Research Paper On Vlsiebvjkbaod100% (1)

- Basit Mahmood: ObjectiveDocument2 pagesBasit Mahmood: ObjectivebasitNo ratings yet

- Cmos Ota ThesisDocument5 pagesCmos Ota Thesislisabrownolathe100% (2)

- EC8711 Lab Manual FinalDocument69 pagesEC8711 Lab Manual FinalGodwinNo ratings yet

- Vidyavardhini's College of Engineering & Technology Department of Electronics and Telecommunication EngineeringDocument10 pagesVidyavardhini's College of Engineering & Technology Department of Electronics and Telecommunication EngineeringRohitNo ratings yet

- Optimized Digital Filter Architectures For Multi-Standard RF TransceiversDocument15 pagesOptimized Digital Filter Architectures For Multi-Standard RF TransceiversvvigyaNo ratings yet

- FPGA Implementation of Digital Modulation Schemes Using Verilog HDLDocument10 pagesFPGA Implementation of Digital Modulation Schemes Using Verilog HDLIJRASETPublicationsNo ratings yet

- Cognitive Radio ThesisDocument4 pagesCognitive Radio Thesisafbtfcstf100% (2)

- Continuous Time Sigma Delta Adc ThesisDocument7 pagesContinuous Time Sigma Delta Adc ThesisPayToWriteAPaperCanada100% (2)

- Simulation of An Optical Fiber Point To Point Communication Link Using SimulinkDocument26 pagesSimulation of An Optical Fiber Point To Point Communication Link Using SimulinkMohammed KhairyNo ratings yet

- Column Bypassing Multiplier Implementation On FPGADocument17 pagesColumn Bypassing Multiplier Implementation On FPGAIJRASETPublicationsNo ratings yet

- ResumeDocument2 pagesResumeArnab DuttaNo ratings yet

- Edn 09 2010Document64 pagesEdn 09 2010thắng100% (2)

- 1 - 30 - VLSI Major Project Titles List 2021Document3 pages1 - 30 - VLSI Major Project Titles List 2021Chakhila 123No ratings yet

- An-Cm-257 Random Pulse Width Modulation For Three-Phase Inverter ApplicationsDocument14 pagesAn-Cm-257 Random Pulse Width Modulation For Three-Phase Inverter ApplicationsLawson SangoNo ratings yet

- Quadrature Vco ThesisDocument6 pagesQuadrature Vco Thesisafknowudv100% (2)

- Operational Transconductance Amplifier Research PaperDocument6 pagesOperational Transconductance Amplifier Research PaperafeawjjwpNo ratings yet

- Resume LayoutDocument10 pagesResume LayoutvijaykannamallaNo ratings yet

- ADS Advanced Design SystemDocument82 pagesADS Advanced Design SystemphithucNo ratings yet

- Design and Implementation of Digital Speedometer: A Project Report OnDocument47 pagesDesign and Implementation of Digital Speedometer: A Project Report OnShanky KumarNo ratings yet

- VLSI SymposiaDocument20 pagesVLSI SymposiaaetherdexNo ratings yet

- Research Paper On Channel CodingDocument4 pagesResearch Paper On Channel Codingegw4qvw3100% (1)

- Mwjournalmwj201401 DLDocument158 pagesMwjournalmwj201401 DL120v60hzNo ratings yet

- Modified Gate Diffusion Input Technique: A New Technique For Enhancing Performance in Full Adder CircuitsDocument8 pagesModified Gate Diffusion Input Technique: A New Technique For Enhancing Performance in Full Adder CircuitsManjunath RNo ratings yet

- Design and Memory Optimization of Hybrid Gate Diffusion Input Numerical Controlled OscillatorDocument9 pagesDesign and Memory Optimization of Hybrid Gate Diffusion Input Numerical Controlled OscillatorIJRES teamNo ratings yet

- Analog Design Methodology Jnotor r3Document17 pagesAnalog Design Methodology Jnotor r3Manjunath ReddyNo ratings yet

- Resume For Amit SinghDocument2 pagesResume For Amit SinghAmit SinghNo ratings yet

- 64 IETSMT2012May AKOHDocument9 pages64 IETSMT2012May AKOHHEIN HTET ZAWNo ratings yet

- Dept. of Ece, Sreebuddha College of Engineering 1Document34 pagesDept. of Ece, Sreebuddha College of Engineering 1SARATH MOHANDASNo ratings yet

- Multi-Functional Electronics Calculator ReportDocument49 pagesMulti-Functional Electronics Calculator Reportguddu kambleNo ratings yet

- CMW500 - Wireless Device Production Test PDFDocument34 pagesCMW500 - Wireless Device Production Test PDFAlvaro Cea CamposNo ratings yet

- Research Paper On QPSKDocument6 pagesResearch Paper On QPSKjhnljzbnd100% (1)

- Low Power, High Performance PMOS Biased Sense AmplifierDocument9 pagesLow Power, High Performance PMOS Biased Sense AmplifierIJRASETPublicationsNo ratings yet

- Vedha Technologies: Technology: Embedded (Atmel/Pic/Arm) S.No Ieee Titles CodeDocument8 pagesVedha Technologies: Technology: Embedded (Atmel/Pic/Arm) S.No Ieee Titles CodeGurudath VenkatramanNo ratings yet

- Synopsis New2Document16 pagesSynopsis New2ZK football TVNo ratings yet

- Thesis On Pipeline AdcsDocument6 pagesThesis On Pipeline Adcsamyholmesmanchester100% (2)

- Modified Gate Diffusion Input Technique: A New Technique For Enhancing Performance in Full Adder CircuitsDocument8 pagesModified Gate Diffusion Input Technique: A New Technique For Enhancing Performance in Full Adder CircuitsPhoenixinnovations supportNo ratings yet

- s41870 022 01060 2.pdf - 2024 02 27 - 21 34 26Document3 pagess41870 022 01060 2.pdf - 2024 02 27 - 21 34 26varshasrinithiNo ratings yet

- College Final Year Projects List - FPGA VLSI Projects List 2012 - 2013Document10 pagesCollege Final Year Projects List - FPGA VLSI Projects List 2012 - 2013Devansh MehtaNo ratings yet

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsFrom EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsNo ratings yet

- Naas ProposalDocument6 pagesNaas ProposalzeusNo ratings yet

- Sub Module 13.1 Theory of FlightDocument56 pagesSub Module 13.1 Theory of FlightteacherNo ratings yet

- Execute PlanDocument1 pageExecute PlanMayline LegaspiNo ratings yet

- Annexure ADocument1 pageAnnexure Atoocool_sashi100% (2)

- 1-5 Wages and SalarieDocument40 pages1-5 Wages and SalarieKvng LearNo ratings yet

- Microwave: LAB ReportDocument14 pagesMicrowave: LAB Reportmakhzom alshhumiNo ratings yet

- FTS-3 (CODE-B) - QP - Solution 30-03-2020 - E - 0 PDFDocument26 pagesFTS-3 (CODE-B) - QP - Solution 30-03-2020 - E - 0 PDFaleemhakNo ratings yet

- Scientific Method Test Study Guide2Document4 pagesScientific Method Test Study Guide2Gabriel TaylorNo ratings yet

- SFCR1 2021Document7 pagesSFCR1 2021rona sumodioNo ratings yet

- Thesis Statement Cafeteria FoodDocument7 pagesThesis Statement Cafeteria Foodafbwszvft100% (1)

- Venezuelan Food Glossary Ver6Document1 pageVenezuelan Food Glossary Ver6Peter BehringerNo ratings yet

- Paradise Mislaid: How We Lost Heaven and How We Can Regain ItDocument223 pagesParadise Mislaid: How We Lost Heaven and How We Can Regain Itlemonslover100% (2)

- ABO Blood Group DiscrepanciesDocument9 pagesABO Blood Group DiscrepanciesRichard SiahaanNo ratings yet

- Screenshot 2023-01-03 at 6.11.33 PM PDFDocument4 pagesScreenshot 2023-01-03 at 6.11.33 PM PDFtamanna groverNo ratings yet

- Journal Pre-Proof: Developments in The Built EnvironmentDocument25 pagesJournal Pre-Proof: Developments in The Built EnvironmentPutri DartamanNo ratings yet

- GRIHADocument14 pagesGRIHAManthan MahajanNo ratings yet

- Reading: Rowell de Guia Bataan Peninsula State UniversityDocument16 pagesReading: Rowell de Guia Bataan Peninsula State UniversityRojane FloraNo ratings yet

- CNMI Percolation Testing ManualDocument91 pagesCNMI Percolation Testing ManualEfren Jr. OricaNo ratings yet

- OIPD in LinguisticsDocument7 pagesOIPD in LinguisticsBela AtthynaNo ratings yet

- DLL - Mathematics 5 - Q1 - W5Document10 pagesDLL - Mathematics 5 - Q1 - W5aleeza ROXASNo ratings yet

- Jan Bremmer Initiation Into The Mysteries of The Ancient World PDFDocument260 pagesJan Bremmer Initiation Into The Mysteries of The Ancient World PDFDanilo Bevilacqua100% (1)

- Power PointDocument17 pagesPower PointphilipnanoyNo ratings yet

- BAED Bens Short Quiz 1Document5 pagesBAED Bens Short Quiz 1Luisa RadaNo ratings yet

- Social LoafingDocument15 pagesSocial LoafingAkash MeenaNo ratings yet

- CVCS Lesson Morda AllDocument29 pagesCVCS Lesson Morda Alli am henryNo ratings yet