Professional Documents

Culture Documents

NJ8812 GECPlesseySemiconductors PDF

NJ8812 GECPlesseySemiconductors PDF

Uploaded by

Linchys_880 ratings0% found this document useful (0 votes)

12 views6 pagesOriginal Title

NJ8812_GECPlesseySemiconductors.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

Download as pdf

0 ratings0% found this document useful (0 votes)

12 views6 pagesNJ8812 GECPlesseySemiconductors PDF

NJ8812 GECPlesseySemiconductors PDF

Uploaded by

Linchys_88Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

Download as pdf

You are on page 1of 6

o PLESSEY

Solid State A INFORMATION

sare nlematon'sssuain nin Coors fre sg ote Pansy Scns ngs shih ora

Neen rete teat Bal gives tay terete, change nthout notice anough we woul expect hs parorranc

aan a resuer at orogcohon lake Radel 5 moat eases Passe contol you! local Plosey Semiconductors tos

{ocSeittsot cument states eer

NJ8812

CONTROL CIRCUIT FOR FREQUENCY SYNTHESIS

“The NJ8B12 is an N-channel MOS integrated circul that

proves al the decoding and controling cicutry for

Frequency synthesises, ft Is intended 10 be used in

Conjunction with 2modulus.prescaler suc as the et pacer

‘SPa703 to produce a universal binary coded synthesise for .

mabile radio appiications.

FEATURES .

High Frequency Range

Low Pia Count

Direct interface to ROM or PROMS

Preset Channel Spacings 20, 25, 30kH2 278 Sub

Mulipes

: oote

High Comparison Frequency pris

Low Level Sinewave Crystal OscilatorInp it up to Be

some Fig Pn connections

‘Systems Clock Available — Constant Data Select

Prequeney of 1 2kH2. (Reference Oscilator

=48MHe)

Microp:ocessor Compatioie

GENERAL DESCRIPTION

“Tne NJB#12 can be described by 9 system blocks: the

reference divider, the programmable ‘divider and the

phasetrequency comparator a shown In Fig2. Ali control

Inputs and outputs are TTL compatible.

ELECTRICAL CHARACTERISTICS Fig? MlGBT2 Block oosrem

‘Test conditions (unless otherwise stated):

Vess0V 20.25

‘Temperature range: -20°C 1 +70°C

Characteristic Unit Conditions.

Osctator input ‘mv_|4MH2 reference oscillator AG cousied

RMS |sinewave FA, FBOIC.

Max. oscillator input frequency 10 MHz | 200mV RMS sinewave.

‘Supply curent 80 | 12 | ma |aldatainputs 01.

‘Max. counter input trequency 50 He | Inout TT compatible.

Ds10s20utput

High Lev! 24 v__ Joutputs TTL compatine,

Low Level on] v

Phase comparator output curent sink} 1 ma |0,0,05Vmax

805

‘The Retoronce Divider

The reference divide! is orvon externally rom a 48MHz

crystal oscar ang can be externally preset 10 one of

‘Sheen ‘division rats. These divsion rallos enable. ll

‘Commonly used eferonce frequencies tobe applied tothe

Dhaselrequency comparator. Selection is accomplished

Using the two pine FA.and FS. These pins may be

‘connected to ground (ogic 00 llt open eteuit (Ogle.

‘connected to. Data Select + Output or to Data Sect 3

Sutpal Onerip decoding enabies the latter two states 10

be recognised as independant states. All sirtesn

‘elections may be latched anehip by grounding the Data

Select 2 output. Table 1 gives relerence frequencies that

canbe preset using adaMiz crystal oscilato.

"The data select outputs (crystal oscilator requency

+4096) ae independent o he preset reference trequency

Programmable Divider

‘The programmable division section of the Nu8612

consists ota SHI programmable vider and an Bit

programmable divider The Got diver controls the

‘moguls of the external prescaler and the Bait counter

Getermines the total count period, The SPB7ORNJBET2

Combination is capable of dividing by all integer values

between 1600 and 11898, When the Aange pin on the

INiBB12 is grounded the programme range is shifted 10

between 6720 and 16958

“The programing data is multiplexed as 3 words of ¢

bite and’! of2 bite completing a 14-bt binary number. This

input data may be stored on chip by grounding the Oata

‘Select 2 output ater seta vanster has cccurred (See Fig.)

‘Al-onchip mutiplexing may then be Inhibited, i desired,

by grounding Data Select" output

PheselFrequency Comparator

The outputs of the fixed and variable dividers on the

48812 are internally connected to. a phasefrequency

Comparator The comparator provides three open rain

‘ututs, The logic diagram is shown in Fig.

ee i

Fi93. Logie diagram

Data Selection

To programme the synthesiser the following

Information is requiec

1. The reference comparison frequency—typically equal

{othe channel spacing

2, The frequency a te VCO,

“The frequency programme Information is prosented to

the sevice mn multiplexed form, The reading of is data by

the device lg contoled by the two data select outputs ror

‘the device. This sequence is shown in Fig &

Fig Dale Resting diagram

806

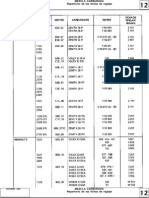

Slew [oe [on | oe

cam ee cen ee cee

oe | a | zs | oe | ns

pv | > | ws | te | am

ose | ses | sare | oars | ars

Ghonelteecee [tare me sou

Tow angeaanay | te0—cay | woanaee | 0am

ie ce (eae ees lect

lowtargroare) | wo=nea | womeo | mo—wra

anemone | or2—voe | eonaeo | woe)

ccaartpeng [a a iam

Tortargeamn | eons? | woo-m0 | eo ane

aowrargsonn | aaeceen | szo—veno | ena—vzre

[Channel Spacing aoe ‘3.125kHE ‘S.75kHz

Seranecia | Naa ate | co= sro aoc

norrargonmn | ieanees | ti0—s00 | zez—ose

ie

Te-ebulde he Forint or» ge YOO. Dh sorso

1 re a ears Sateen manta be dct ae

i wae 5

Scaaee oe sore

Progeermme Numizes | ome R 5. Write down number before decimal place:

woe :

tore (=V60 Inguneyn t 1 tty pat oa

cose 1 deere newer oe umber

Re ) (WORD ‘A +B’) 8

ge number (R= 1600 rang

(R= 6720 ange ~0}

Te programme number is converted to 14 bt binary

number and fs segregated as 3 words of bits and 1 word

of 2s

“The least significant word is fst entered during the

Data Read 1 time slot via the nuts D,, Dy, Dy and D, and

‘the most significant ast (Data Read 4th St

‘The second ‘east signfieant word contains only two

bits entered via the inputs D, and D,, Data presented to he

Inputs, and D, ding the Second ime sit is ignored by

the nose

For example, with a. VCO frequency of 121, 2MH2 and

channel pacing of 25KHE

few

czas

R= 1600

Naas

Conversion to a 14-bit binary number is performed as

follows:

‘The decimal numbers obtained for words °C’ and ‘0°

may be direct converted to it binary words, whe the

Secimal number for words A’ and’ wil convert fo a it

binary word. The last significant four bits of his word give

word A" while the two most significant bits give the least

Sonificant bits of word (the two most significant bits of

‘word 8" having ‘don't care’ states). These are presonted to

the cata inputs asin Table 3

os fos[o fo] ]

of? {+{of of «| woro~

ofo|x| x] of] o] wore

r+}o]}o}ol}o} a] wore

+] fofsf{ of + | worn

Tabled

‘The deta may be latched intemally by grounding the

sz ‘output. This Is useful when’ interfacing to 3

‘microprocessor, The NJBB12 is algo compatible with most

{Types of PROM and ROM for data coding application.

[APPLICATION NOTES.

‘The NJBBI2 Is designed for use in phase locked ‘cop

frequency synthesisers In these synthesiser, the voltage

Cconvolled oscilator (VCO) operates atthe output

frequency and the output frequency 1s divided down to a

Taterence frequency. Another signal at is reference

frequency is derwed trom the orystal controled reference

Ctcllator and the cvided VCO signal is compared at tis

frequency with the reference signal Ina phase ond

Frequency comparator The output signal derive from t

‘comparison consists of short pulses whose mark-space

‘avis such thal when the pulses ae integrated, a DC ieve,

Isobtained, which, when applied othe VCO, tock the loop

by maintaining the VCO on frequency.

Simple division 10 the reterence frequency in a fully

programmable divider is limites to tequencies of about

Eom and below, because of the difieulty of producing

fully programmable dividers However, a twomodulus

divider which divges by N and N 1 may be easly made. A

system as. shown in Fig then provides. for the

Brograrnmable division tobe done at lower requencies.

cone]

Fig modulus counter

The systern works a follows:

The twomodulvs counter divides by N41 until

counter "A'S full The twomodulus” stage then

‘vides by Nunti the M counter full The resultant

division ratio ig NMA,

Inthe NJBB12, the value of M is sot fo between 40 anc

296, while A Is programmed between 0 and $9. The ful

‘Seope of the NJ8BT2 ina eynthesisar Is achieved using 2

Sagres, such a8 tho SPBTOS. and under these conditions,

{he divaton ratio i Wom 1600 to 11839. By using the Range

input, the M counter programme i changed such thatthe

{son rato becomes 6720 10 16868,

"The retrence Wequency 1 derived trom a 48MHz

crystal by a programmed divider. This divder is

progtammned by the FA and FB Inputs: these may be ted 10

Ve togie "V}, Grourd (logic "0) or to O81” and DS2,

Spending upon the feference traquency required In

General the felerence frequency is made equal to the

hanne! spacing. a the higher he reference quency, the

taster it ff filer the contol line to the VCO to prevent

Spurious sidebands at reference frequency appearing on

theoutout

Phase Detector

{nthe NJBBT2, this circuit function is implemented by

the use of two D fype filpflops, These deve ‘open cain

utput FETS, and it these are taken to Ve via resistors,

\wavetome as shown in Fig6 may be expected

808

Fig Phase detector waveforms

wen out of lock, 2, and O, have no definite phase

relationship, These outputs may be combined in a sutabie

Creut 38 shown in Fig

oop Fiter Design

A simple approach wit provide a workable, but not

fnacestaniy optimum system. For more Getaled methods,

faterence fo one of the many textbooks is recommended!

‘The following method provides a simple design.

1. Choose the loop natural requency This frequency

Sects the eating lime of the 1o0p, an this satng

tim i, toa first order approximation, Oly, where ay

isin radians per second

2. Choose a value of damping factor to give adequate loop

Slalily without excessive overshoot. A salistacioy

‘alue 2 10. giving an overshoot of approximately 10%

8, Determine:

‘KV VOO Gain in radsyVot ac

Taney

here Ha isthe deviation in Hz fort volt

change onthe contol line.

N_=VCO TrequeneyReterence Frequency,

14, Choose Ry For convenience, 4.7K>R,>470R

5. Ry = Dia .C, where Dis the damping factor.

Bok,

98 Programming board

Retorence Oscillator Requirements

Because the frequency synthesiser etfectvely

multiples the -teleconceoscilator to the working

fRequency, any vanations or inaccuracies inthe reterence

Dscllator appear at the output. For this reason, the

Sccuracy ofthe reference oscllaor must be no worse than

that of the signal which ti required to synthesise, while

the signaltonoise ratlo must be as high as possible.

Incidental FM must be rinimised.

VCO Requirements

‘The VCO should cover the frequency range desired with

‘a suitable contr! ine voltage swing. In adtion ts power

fevol and © should be such as to maintain phase noise

‘ioebands as low as is required. tis requenty found that

{he high impedence contol ine fe very susceptible to

picking up stay signals sereening and careful decoupling

‘Of the VCO and ts supplies Is offen necessary. Buffering

between the VCO and the prescaler Is required to prevent

‘VEO modulation rom thie source, and dual gate MOSFETS:

te very useflin this poston.

‘ATypleal Synthesiner

Fig 9 shows a typical equency synthesise using the

NuBBt2 and SPR7GS. Programming is trom the binary

programming board of Fig8, or trom a suitably

programmed PROM oc ROM. It should be Noted tha! the

Binary programming board produces four ¢bit words, and

therefore, two ofthe is ae redundant (see Programming

the N82)

"The synthesiser of Fig uses a 40673 or similar dual

‘gate MOSFET as a bulfer prior to the SP8789 divider. The

free’ 2NS770 transistors provide a charge pump crcul

‘and the fourth a crystal oscillator This synthesiser draws,

Some 25mA maximum, excluding the VCO and. the

Programming system, and further development covid wel

Fecuce tie Curent appreciably. I modulation is required,

this may be applied to te conto! ne, proved that the

‘Beak deviation not such as to ive the loop out of lock

"The connection of ah LED from pin 10 of the NJBB2 to

‘5V via a 22k resistor wl provige an incicaton of lock, he

lame being alight when tna oop is unlocked.

AEE and the range pin are connected according to

the requirments. of frequency spacing and operating

frequency,

Performance, in terms of spurious sidebands and noise

‘depends upon construction and design ofthe VCO and PC

board, and good AF pracice should be followed with

regard to these components. n particular, attention should

Seong tobe VCO, acemning Farber appicatons

809

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5834)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (350)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (824)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (405)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Manual Descriptivo y de Reparabilidad Yamaha TZR80RRDocument38 pagesManual Descriptivo y de Reparabilidad Yamaha TZR80RRLinchys_88No ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Carburadores Solex - CaracteristicasDocument74 pagesCarburadores Solex - Caracteristicasapi-380678180% (10)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Consideraciones Sobre Los Ensayos de Homologación de Ruido de Las Motocicletas y Los Ciclomotores.Document56 pagesConsideraciones Sobre Los Ensayos de Homologación de Ruido de Las Motocicletas y Los Ciclomotores.Linchys_88No ratings yet

- Recuperación de Windows 10 en Woxter Zen 10Document2 pagesRecuperación de Windows 10 en Woxter Zen 10Linchys_88No ratings yet

- Sailor CRY2001 (Manual) PDFDocument40 pagesSailor CRY2001 (Manual) PDFLinchys_88No ratings yet

- Motorola TetraDocument66 pagesMotorola TetraLinchys_88No ratings yet

- Vema css21 Ita Web PDFDocument1,872 pagesVema css21 Ita Web PDFLinchys_88No ratings yet

- Serie 68Document10 pagesSerie 68Linchys_88No ratings yet

- FT Prensaestopas InoxidableDocument1 pageFT Prensaestopas InoxidableLinchys_88No ratings yet

- Instruccions FERVE F-2320-2330Document20 pagesInstruccions FERVE F-2320-2330Linchys_88No ratings yet

- Cajas de Derivacion en AluminioDocument1 pageCajas de Derivacion en AluminioLinchys_88No ratings yet

- Tait tpdh7d External PhotosDocument6 pagesTait tpdh7d External PhotosLinchys_88No ratings yet

- New Features!: Record I/Q Data On SD Card, Playback With SDR# SoftwareDocument6 pagesNew Features!: Record I/Q Data On SD Card, Playback With SDR# SoftwareLinchys_88No ratings yet

- Index PDFDocument334 pagesIndex PDFaadNo ratings yet

- Catálogo Estanca 55Document8 pagesCatálogo Estanca 55Linchys_88No ratings yet

- Catálogo Accesorios Ducati Performance 2007Document192 pagesCatálogo Accesorios Ducati Performance 2007Linchys_88No ratings yet

- Catálogo Estanca 55 Mureva (Enero 2015)Document2 pagesCatálogo Estanca 55 Mureva (Enero 2015)Linchys_88No ratings yet

- BTicino BTI-346841Document1 pageBTicino BTI-346841Linchys_88No ratings yet

- FH19C FH19SC CatalogDocument12 pagesFH19C FH19SC CatalogLinchys_88No ratings yet

- ZongShen W150 Parts CatalogueDocument12 pagesZongShen W150 Parts CatalogueLinchys_88No ratings yet

- Manual Mantenimiento Heavy EspaDocument125 pagesManual Mantenimiento Heavy EspaMouhcinNo ratings yet

- Visor Tpycea 4x26 Fusil Coruña FR-8Document2 pagesVisor Tpycea 4x26 Fusil Coruña FR-8Linchys_88No ratings yet

- Catálogo Yaesu VX-246Document2 pagesCatálogo Yaesu VX-246Linchys_88No ratings yet

- Astrophysics XIS 6545Document2 pagesAstrophysics XIS 6545Linchys_880% (1)