Professional Documents

Culture Documents

IT1204 Section 03 PDF

IT1204 Section 03 PDF

Uploaded by

Dress ntrCopyright:

Available Formats

You might also like

- Development and Deployment of Multiplayer Online Games, Vol. IIDocument437 pagesDevelopment and Deployment of Multiplayer Online Games, Vol. IItiyihis146100% (1)

- Laboratory Activities Computer Engineering Drafting and DesignDocument74 pagesLaboratory Activities Computer Engineering Drafting and DesignPaul Santos Nonat75% (4)

- Digital Logic Design (Cen-122) (2+1)Document26 pagesDigital Logic Design (Cen-122) (2+1)Komal AliNo ratings yet

- Lecture No 7, 8, 9 & 10Document96 pagesLecture No 7, 8, 9 & 10Muhammad AnasNo ratings yet

- Teachers Note - Section 03Document105 pagesTeachers Note - Section 03kkNo ratings yet

- 4 CH2 P2 Boolean Algebra ( (2.01) SEM 442Document44 pages4 CH2 P2 Boolean Algebra ( (2.01) SEM 442BadrNo ratings yet

- L5 DLD Boolean SimplificationDocument29 pagesL5 DLD Boolean SimplificationandreytagnoNo ratings yet

- Boolean Algebra and Logic SimplificationDocument30 pagesBoolean Algebra and Logic SimplificationAbdullah AftabNo ratings yet

- Digital Logic Design - Boolean AlgebraDocument17 pagesDigital Logic Design - Boolean AlgebraTroon SoonNo ratings yet

- Discrete Mathematics For Ece: Boolean Algebra and Logic SimplificationDocument41 pagesDiscrete Mathematics For Ece: Boolean Algebra and Logic SimplificationLykaShanineGabrielMendozaNo ratings yet

- Lecture 4 DLD Boolean Functions Switching Algebra and Logic Gates1Document27 pagesLecture 4 DLD Boolean Functions Switching Algebra and Logic Gates1Ruby PoddarNo ratings yet

- Chapter Three: Boolean Algebra and Logic SimplificationDocument30 pagesChapter Three: Boolean Algebra and Logic Simplificationmift ademNo ratings yet

- Digital Fundamentals: FloydDocument21 pagesDigital Fundamentals: FloydadilNo ratings yet

- Simplification (Minimization) of Logical FunctionsDocument15 pagesSimplification (Minimization) of Logical FunctionsErdem BahadirNo ratings yet

- Digital Logic DesignDocument41 pagesDigital Logic DesignAri BaderNo ratings yet

- DE Lecture 2Document26 pagesDE Lecture 2Shakawat Hossain ShifatNo ratings yet

- Logic Gates and K-MapDocument9 pagesLogic Gates and K-MapAditya Kumar SharmaNo ratings yet

- Digital Logic DesignDocument23 pagesDigital Logic DesignHaider AliNo ratings yet

- DLLec5b NotesDocument4 pagesDLLec5b NotesChintan MandalNo ratings yet

- Chapter 6 - Boolean - EEDocument43 pagesChapter 6 - Boolean - EEIrlan DinNo ratings yet

- 05 - Boolean FunctionDocument51 pages05 - Boolean FunctionSyamil AzrilzNo ratings yet

- Digital Logic & Computer Architecture: (Lesson 4)Document9 pagesDigital Logic & Computer Architecture: (Lesson 4)Muhammad FurqanNo ratings yet

- Logic Simplification SlideDocument46 pagesLogic Simplification Slideتوان ظاهيرو الدينNo ratings yet

- CH 04Document80 pagesCH 04nashitahalwaz95No ratings yet

- DLD Fundamentals FloydDocument44 pagesDLD Fundamentals FloydMuhammad AsadNo ratings yet

- Boolean AlgebraDocument31 pagesBoolean Algebraeverthing is here videos and statusNo ratings yet

- Module 4 - Boolean AlgebraDocument20 pagesModule 4 - Boolean AlgebraKejeindrranNo ratings yet

- Sheet 4Document8 pagesSheet 4Loay AhmedNo ratings yet

- 2 17 11 PDFDocument8 pages2 17 11 PDFAdamNo ratings yet

- Chapter 3 MinDocument19 pagesChapter 3 MinCybertron BadeeNo ratings yet

- Digital Fundamentals: FloydDocument32 pagesDigital Fundamentals: FloydTalha KhanNo ratings yet

- Dwaraka Doss Goverdhan Doss Vaishnav College CHENNAI - 106: Fundamentals of Digitial ElectronicsDocument25 pagesDwaraka Doss Goverdhan Doss Vaishnav College CHENNAI - 106: Fundamentals of Digitial ElectronicsRyuzz MalfoyNo ratings yet

- Boolean Algebra..Document40 pagesBoolean Algebra..Mini SharmaNo ratings yet

- 07 BooleanAlgebraDocument21 pages07 BooleanAlgebraGans GanesanNo ratings yet

- 003 Boolean AlgebraDocument19 pages003 Boolean AlgebraMarid CandraNo ratings yet

- 6.1 Lectures - Module4 - Digital ElectronicsDocument16 pages6.1 Lectures - Module4 - Digital ElectronicsSree dhathri DevaNo ratings yet

- Boolean Algebra PDFDocument20 pagesBoolean Algebra PDFTanuNo ratings yet

- C06 BooleanAlgebrasDocument7 pagesC06 BooleanAlgebrasNaseer ahmadNo ratings yet

- Unit 20 - Lecture 03Document30 pagesUnit 20 - Lecture 03Kusal DananjayaNo ratings yet

- C16 Canonical FormsDocument24 pagesC16 Canonical Formsyadhucr5577No ratings yet

- MIT18 02SC PB 3 CombDocument2 pagesMIT18 02SC PB 3 CombAbrar Ul HaqNo ratings yet

- ECSE-4760 Real-Time Applications in Control & Communications Experiments in Digital Logic DesignDocument24 pagesECSE-4760 Real-Time Applications in Control & Communications Experiments in Digital Logic DesignMitu BaralNo ratings yet

- Digital Logic DesignDocument36 pagesDigital Logic DesignnayabNo ratings yet

- Lec1snip2 DotprodDocument3 pagesLec1snip2 DotprodMohammad aneeb shinwariNo ratings yet

- (De) 1Document17 pages(De) 1Rahul BhatiNo ratings yet

- Computer Architecture: Nguyễn Trí ThànhDocument157 pagesComputer Architecture: Nguyễn Trí Thànhhoang.van.tuanNo ratings yet

- 48 606 Olteanu Emil 2Document6 pages48 606 Olteanu Emil 2nou channarithNo ratings yet

- Chapter 4Document28 pagesChapter 4Soman AunNo ratings yet

- Unit - 3 - Combinational Logic DesignDocument27 pagesUnit - 3 - Combinational Logic DesignAvinash SharmaNo ratings yet

- Boolean Algebra and Logic Gates: Basic TheoremsDocument18 pagesBoolean Algebra and Logic Gates: Basic Theoremsalma bella macaldoNo ratings yet

- Experiment No.1:Introduction To Basic Gates and Logic Simplification TechniquesDocument6 pagesExperiment No.1:Introduction To Basic Gates and Logic Simplification TechniquesAurongo NasirNo ratings yet

- ACFrOgBTICzbZgajnUi3e TJwOPELhujoXwlPaX W6TTCoJGxI5810vc8Yd8NTKdHf sa6SxtlxNAaDCVkmq4TLKWNsmbBzXPVYX93O4xjx7qKv-YC-m7kTL8FXxgrB5ZIGn0PTYziVtvC5ADp6UDocument35 pagesACFrOgBTICzbZgajnUi3e TJwOPELhujoXwlPaX W6TTCoJGxI5810vc8Yd8NTKdHf sa6SxtlxNAaDCVkmq4TLKWNsmbBzXPVYX93O4xjx7qKv-YC-m7kTL8FXxgrB5ZIGn0PTYziVtvC5ADp6UNijhum ChoudhuryNo ratings yet

- Week 3Document15 pagesWeek 3NaEem KhanNo ratings yet

- 15 Boolean Algebra 23 Jul 2018reference Material I - Boolean - AlgebraDocument19 pages15 Boolean Algebra 23 Jul 2018reference Material I - Boolean - Algebranayan agalNo ratings yet

- Fundamental of Digital Systems Unit II 08-3-2024Document57 pagesFundamental of Digital Systems Unit II 08-3-2024usamaabdurrahman.cseNo ratings yet

- Cat-1 July 2019 Cat-1 July 2019Document1 pageCat-1 July 2019 Cat-1 July 2019malaiNo ratings yet

- Anupam Sir DLD3Document117 pagesAnupam Sir DLD3Adhara MukherjeeNo ratings yet

- Lecture 030223Document55 pagesLecture 030223Divyansh SinghNo ratings yet

- Lec 08Document28 pagesLec 08bivaye4887No ratings yet

- Fundamentals of Computers: Boolean Algebra of Switching CircuitsDocument23 pagesFundamentals of Computers: Boolean Algebra of Switching CircuitsMD. Mohaiminul IslamNo ratings yet

- Standard-Slope Integration: A New Approach to Numerical IntegrationFrom EverandStandard-Slope Integration: A New Approach to Numerical IntegrationNo ratings yet

- SECTION 3 - Solving Equations and Inequalities PDFDocument23 pagesSECTION 3 - Solving Equations and Inequalities PDFDress ntrNo ratings yet

- Write Following Two Java Programs That Capable To Add and Subtract Given Two Numbers. Methods Without Passing ParametersDocument3 pagesWrite Following Two Java Programs That Capable To Add and Subtract Given Two Numbers. Methods Without Passing ParametersDress ntrNo ratings yet

- Section 1 - Number PDFDocument19 pagesSection 1 - Number PDFDress ntrNo ratings yet

- Introduction To Networks: 9.1 Uses of A NetworkDocument19 pagesIntroduction To Networks: 9.1 Uses of A NetworkDress ntrNo ratings yet

- 1.2.1 Electronic Computers Based On Digital SwitchingDocument22 pages1.2.1 Electronic Computers Based On Digital SwitchingDress ntrNo ratings yet

- Input and Output DevicesDocument27 pagesInput and Output DevicesDress ntrNo ratings yet

- New Text DocumentDocument1 pageNew Text DocumentDress ntrNo ratings yet

- HNDITSyllabus DetailedDocument318 pagesHNDITSyllabus DetailedDress ntrNo ratings yet

- HNDIT Curriculum Outline LatestDocument10 pagesHNDIT Curriculum Outline LatestDress ntrNo ratings yet

- AA13 EBA (Tam) AdDocument7 pagesAA13 EBA (Tam) AdDress ntrNo ratings yet

- (Aa15) Tpahghuj Njhopw GHLFSK Kfhikj JTKK Tpahghuj Njhopw GHLFSK Kfhikj JTKK Tpahghuj Njhopw GHLFSK Kfhikj JTKK Tpahghuj Njhopw GHLFSK Kfhikj JTKKDocument7 pages(Aa15) Tpahghuj Njhopw GHLFSK Kfhikj JTKK Tpahghuj Njhopw GHLFSK Kfhikj JTKK Tpahghuj Njhopw GHLFSK Kfhikj JTKK Tpahghuj Njhopw GHLFSK Kfhikj JTKKDress ntrNo ratings yet

- (Aa11) Epjpf FZF FPL L MBG Gilfs Epjpf FZF FPL L MBG Gilfs Epjpf FZF FPL L MBG Gilfs Epjpf FZF FPL L MBG GilfsDocument10 pages(Aa11) Epjpf FZF FPL L MBG Gilfs Epjpf FZF FPL L MBG Gilfs Epjpf FZF FPL L MBG Gilfs Epjpf FZF FPL L MBG GilfsDress ntrNo ratings yet

- TPDH TPDH TPDH TPDH: Kog GJPG GupikailajDocument7 pagesTPDH TPDH TPDH TPDH: Kog GJPG GupikailajDress ntrNo ratings yet

- Micom P211 OC & EF RelayDocument8 pagesMicom P211 OC & EF Relaysatya1417No ratings yet

- KS3 Maths OverviewDocument4 pagesKS3 Maths OverviewJakubNo ratings yet

- GA32-0378-05 Installation Planning 3490E F01Document136 pagesGA32-0378-05 Installation Planning 3490E F01paolovelaNo ratings yet

- Newton S Laws of Motion Lesson PlanDocument9 pagesNewton S Laws of Motion Lesson Plananon_212484834No ratings yet

- B-Tech Sample Internship Report FormatDocument6 pagesB-Tech Sample Internship Report FormatVAIBHAV DESHMUKHNo ratings yet

- Online Safety and Security PPTDocument17 pagesOnline Safety and Security PPTJEMNA PITOGONo ratings yet

- Gyro Skipper PlansDocument5 pagesGyro Skipper PlansJayantha KandegamaNo ratings yet

- Wiring Diagram: 5-1. LayoutDocument7 pagesWiring Diagram: 5-1. LayoutLuisMiguelCalvoNo ratings yet

- CPO Checklist FINALDocument22 pagesCPO Checklist FINALSW ChenNo ratings yet

- Script QoS PPPoEDocument5 pagesScript QoS PPPoEcabunga2014100% (2)

- 2023-Report-Annual-Marketing-En - Shared by WorldLine TechnologypdfDocument28 pages2023-Report-Annual-Marketing-En - Shared by WorldLine TechnologypdfThuy NghiemNo ratings yet

- UntitledDocument2,001 pagesUntitledmayraNo ratings yet

- Bitdefender GravityZone XDR Datasheet enDocument2 pagesBitdefender GravityZone XDR Datasheet entoretta1984No ratings yet

- Text Messaging Is Better Than ThinkingDocument1 pageText Messaging Is Better Than ThinkingClevanche LightbourneNo ratings yet

- Chapter 17-18 Conflict, Negotiation, and TechnologyDocument72 pagesChapter 17-18 Conflict, Negotiation, and TechnologyHaryadi WidodoNo ratings yet

- GSW Portfolio V02Document21 pagesGSW Portfolio V02أحمد فريد سعد عبد الفتاحNo ratings yet

- Digital Learning Materials Classification and ImplDocument14 pagesDigital Learning Materials Classification and ImplWild Rift00No ratings yet

- Practice Makes Regexp (Reuven M. Lerner, PHD)Document206 pagesPractice Makes Regexp (Reuven M. Lerner, PHD)riccardo.cavarra.rcNo ratings yet

- Analyzing Social Media Engagement and Its Effect On Online Product Purchase Decision BehaviorDocument9 pagesAnalyzing Social Media Engagement and Its Effect On Online Product Purchase Decision Behaviorhi.ashukaNo ratings yet

- Eps Unit 3Document24 pagesEps Unit 3Bhavana PedadaNo ratings yet

- HR Analytics 3rd ChapterDocument16 pagesHR Analytics 3rd ChapterAppu SpecialNo ratings yet

- KS0077 (78,79) Super Learning Kit For ArduinoDocument315 pagesKS0077 (78,79) Super Learning Kit For ArduinoАнтон ПыхаловNo ratings yet

- Data Sheet 3RP2525-1AW30Document6 pagesData Sheet 3RP2525-1AW30mahdi aghamohamadiNo ratings yet

- Fujitsu Air Conditioner OPERATING MANUALDocument6 pagesFujitsu Air Conditioner OPERATING MANUALTavrusNo ratings yet

- Lecture 9 BASIC-LINE-PROTECTIONDocument46 pagesLecture 9 BASIC-LINE-PROTECTIONmuaz_aminu1422No ratings yet

- Target Cyber Breach Report: "Security Is Only As Strong As The Weakest Link"Document5 pagesTarget Cyber Breach Report: "Security Is Only As Strong As The Weakest Link"Manjunath AbhiNo ratings yet

- Initial PagesDocument7 pagesInitial PagesLaxmisha GowdaNo ratings yet

- Software DevelopmentDocument272 pagesSoftware Developmentszpakos100% (1)

IT1204 Section 03 PDF

IT1204 Section 03 PDF

Uploaded by

Dress ntrOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

IT1204 Section 03 PDF

IT1204 Section 03 PDF

Uploaded by

Dress ntrCopyright:

Available Formats

IT 1204

Section 3.0

Boolean Algebra and Digital Logic

© 2009, University of Colombo School of Computing 1

Boolean Algebra

© 2009, University of Colombo School of Computing 2

Logic Equations to Truth Tables

X = A.B + A.B + AB

A B X

0 0

0 1

1 0

1 1

© 2009, University of Colombo School of Computing 3

Sum of Products

The OR operation performed on the products of the AND

operation

Fill the corresponding cells with 1 for each product, the

other cells with 0

A B X

X = ( A.B ) + ( A.B ) + ( A.B ) 0 0 1

A = 1, A = 0 0 1 1

B = 1, B = 0 1 0 0

1 1 1

© 2009, University of Colombo School of Computing 4

Product of Sums

The AND operation performed on the sums of the OR

operation

Fill the corresponding cells with 0 for each sum, the

other cells with 1

A B X

Y = ( A + B ).( A + B) 0 0 1

A = 0, A = 1 0 1 1

B = 0, B = 1 1 0 0

1 1 0

© 2009, University of Colombo School of Computing 5

Truth Tables to Logic Equations

• Sum of Products - consider 1s

A B X

– Consider A=1,B=1

0 0 1

X = ( A.B ) + ( A.B )

0 1 1

• Product of sums – consider 0s

1 0 0

– Consider A=0,B=0

1 1 0

X = ( A + B).( A + B)

© 2009, University of Colombo School of Computing 6

Your Turn: Exercise1

Convert the following equation which is in the form of

Product-of-sums into the form of Sum-of-products

f ( ABCD) = ( A + B + C )( A + B + C + D)( A + B + D)( A + C )

© 2009, University of Colombo School of Computing 7

Answer: Exercise1

f ( ABCD) = ( A + B + C )( A + B + C + D)( A + B + D)( A + C )

f ( ABCD) = ( A + B + C )( A + B + C + D)( A + B + D)( A + C )

f ( ABCD) = ( A + B + C ) + ( A + B + C + D) + ( A + B + D) + ( A + C )

f ( ABCD) = ( A.B.C ) + ( A.B.C.D) + ( A.B.D) + ( A.C )

f ( ABCD) = ( A.B.C ) + ( A.B.C.D) + ( A.B.D) + ( A.C )

© 2009, University of Colombo School of Computing 8

Boolean Postulates

0.0=0

1+1=1

0+0=0

1.1=1

1.0=0.1=0

1+0=0+1=1

© 2009, University of Colombo School of Computing 9

Laws of Boolean Algebra

Commutative Law

¾ A+B=B+A

¾ AB =BA

Associate Law

¾ (A + B) + C = A + (B + C)

¾ (A B) C = A (B C)

© 2009, University of Colombo School of Computing 10

Laws of Boolean Algebra

Distributive Law

¾ A (B + C) = A B + A C

¾ A + (BC) = (A + B) (A + C)

Identity Law

¾ A+A=A

¾ A.A =A

© 2009, University of Colombo School of Computing 11

Laws of Boolean Algebra

Redundancy Law

¾ A + AB = A

¾ A (A + B) = A

Demorgan’s Theorem

¾ (.A + B ) = A.B

¾

( A.B ) = A + B

© 2009, University of Colombo School of Computing 12

Laws of Boolean Algebra

. A.B + A.B = A

( A + B)( A + B) = A

. A+0 = A

A.0 = 0

© 2009, University of Colombo School of Computing 13

Laws of Boolean Algebra

. 1+ A = 1

1.A = A

. A + A = 1

A.A = 0

© 2009, University of Colombo School of Computing 14

Laws of Boolean Algebra

. A + A.B = A + B

A( A + B) = AB

© 2009, University of Colombo School of Computing 15

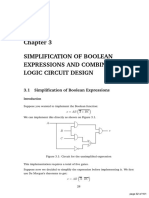

Implementation of Boolean Functions

A Boolean function can be realised in either SOP or

POS form

At this point, it would seem that the choice would

depend on whether the truth table contains more 1s

and 0s for the output function

The SOP has one term for each 1, and the POS has

one term for each 0

© 2009, University of Colombo School of Computing 16

Implementation of Boolean Functions

However, there are other considerations:

¾ It is generally possible to derive a simpler Boolean

expression from truth table than either SOP or

POS

¾ It may be preferable to implement the function with

a single gate type (NAND or NOR)

© 2009, University of Colombo School of Computing 17

Implementation of Boolean Functions

The significance of this is that, with a simpler

Boolean expression, fewer gates will be needed to

implement the function

Methods that can be used to achieve simplification

are:

¾ Algebraic Simplification

¾ Karnaugh Maps

© 2009, University of Colombo School of Computing 18

Your Turn: Algebraic Simplification

Simplify the following equation using Boolean

algebra laws

f ( ABC ) = ( A + B + C )( A + BC )

© 2009, University of Colombo School of Computing 19

Answer: Algebraic Simplification

f ( ABC ) = ( A + B + C )( A + BC )

f ( ABC ) = AA + ABC + AB + B BC + AC + BC C

f ( ABC ) = A(1 + BC + B + C ) + BC + BC C

f ( ABC ) = A + BC

© 2009, University of Colombo School of Computing 20

Karnaugh Maps

For purposes of simplification, the Karnaugh map is a

convenient way of representing a Boolean function of

a small number (up to 4 to 6) of variables

n

The map is an array of 2 squares, representing the

possible combinations of values of n binary variables

© 2009, University of Colombo School of Computing 21

Karnaugh Maps

The map can be used to represent any Boolean

function in the following way:

¾ Each square corresponds to a unique product in the

sum-of-products form.

¾ With a 1 value corresponding to the variable and a 0

value corresponding to the NOT of that variable

© 2009, University of Colombo School of Computing 22

Karnaugh Maps: 2 Values

A 0 1

B

0 0 1

1 1 1

X = A.B + A.B + AB

© 2009, University of Colombo School of Computing 23

Karnaugh Maps: 2 Values

The AB corresponds to the fourth square in the

Figure

For each such production in the function, 1 is

placed in the corresponding square

AB

00 01 11 10

1 1

F = AB + AB

© 2009, University of Colombo School of Computing 24

Karnaugh Maps: 3 Values

AB 00 01 11 10

C

0 1 1 0 0

1 0 0 1 1

X = A.B.C + A.B.C + A.B.C + A.B.C

© 2009, University of Colombo School of Computing 25

Karnaugh Maps: 4 Values

AB 00 01 11 10

CD

00 1 0 1 1

01 0 1 1 0

11 0 1 1 0

10 0 1 0 1

X = A.B.C.D + A.B.C.D + A.B.C.D + A.B.C.D + A.B.C.D + A.B.C.D + A.B.C.D + A.B.C.D

© 2009, University of Colombo School of Computing 26

Karnaugh Maps: Exercise 1

Simplify the following Karnaugh Map using Boolean

equations (Write your answers in both SOP and POS)

AB 00 01 11 10

C

0 0 1 0 0

1 1 1 0 1

© 2009, University of Colombo School of Computing 27

Karnaugh Maps: Answer

( A.B.C ) + ( A.B.C ) + ( A.B.C ) + ( A.B.C ) AB + BC

( A + B + C ).( A + B + C ).( A + B + C ).( A + B + C ) ( B + C ).( A + B)

AB 00 01 11 10

C

0 0 1 0 0

1 1 1 0 1

© 2009, University of Colombo School of Computing 28

Karnaugh Maps: Exercise 2

Simplify the following Karnaugh Map using Boolean

equations (Write your answers in both SOP and POS)

POS

AB 00 01 11 10

CD

00 1 0 0 1

01 0 1 1 0

11 0 0 1 0

10 1 0 0 1

© 2009, University of Colombo School of Computing 29

Karnaugh Maps: Answer

( A BC D) + ( ABC D) + ( ABC D) + ( ABC D) + ( ABCD) + ( A BC D) + ( ABC D)

B D + BC D + ABD

AB 00 01 11 10

CD

00 1 0 0 1

01 0 1 1 0

11 0 0 1 0

10 1 0 0 1

© 2009, University of Colombo School of Computing 30

Karnaugh Maps: Answer

( A + B + C + D).( A + B + C + D).( A + B + C + D).( A + B + C + D).

( A + B + C + D).( A + B + C + D).( A + B + C + D).( A + B + C + D).

( A + B + C + D)

( B + D).( B + D ).( A + C + D)

AB 00 01 11 10

CD

00 1 0 0 1

01 0 1 1 0

11 0 0 1 0

10 1 0 0 1

© 2009, University of Colombo School of Computing 31

Simplified Labeling of Karnaugh Maps

The labeling used in figure emphasizes the relationship

between variables and the rows and columns of the map

C

The two rows embraced by

the symbol A are those in

which the variable A has the

value 1; the rows not

B

embraced by the symbol A

are those in which A is 0 A

© 2009, University of Colombo School of Computing 32

Simplified Labeling of Karnaugh Maps

Once the map of a function is created, we can often write

a simple algebraic expression for it by noting the

arrangement of the 1s on the map

The principle is as follows:

¾ Any two squares that are adjacent differ in only one of

the variables

¾ If two adjacent squares both have an entry of 1, then

the corresponding product terms differ in only one

variable

¾ In such a case, the two terms can be merged by

eliminating that variable

© 2009, University of Colombo School of Computing 33

Simplified Labeling of Karnaugh Maps

For example, in following FIGURE, the two adjacent

squares correspond to the two terms ABCD and ABCD

CD

The function expressed is

ABCD + ABCD = ABD

1 1

AB

© 2009, University of Colombo School of Computing 34

Simplified Labeling of Karnaugh Maps

This process can be extended in several ways:

¾ First, the concept of adjacent can be extended to

include wrapping around the edge of the map

¾ Thus, the top square of a column is adjacent to

the bottom square, and the leftmost square of a

row is adjacent to the rightmost square

n

¾ Second, we can group not just 2 squares but 2

adjacent squares, that is, 4, 8, etc

© 2009, University of Colombo School of Computing 35

Your turn: Karnaugh Maps

CD

AB

© 2009, University of Colombo School of Computing 36

Answer: Karnaugh Maps

CD

AB

BCD

© 2009, University of Colombo School of Computing 37

Your turn: Karnaugh Maps

CD

1 1

AB

© 2009, University of Colombo School of Computing 38

Answer: Karnaugh Maps

CD

1 1

AB

ABD

© 2009, University of Colombo School of Computing 39

Your turn: Karnaugh Maps

CD

1 1 1 1

AB

© 2009, University of Colombo School of Computing 40

Answer: Karnaugh Maps

CD

1 1 1 1

AB

AB

© 2009, University of Colombo School of Computing 41

Your turn: Karnaugh Maps

CD

1 1

AB

1 1

© 2009, University of Colombo School of Computing 42

Answer: Karnaugh Maps

CD

1 1

AB

BC

1 1

© 2009, University of Colombo School of Computing 43

Your turn: Karnaugh Maps

CD

1 1 1 1

1 1 1 1

AB

© 2009, University of Colombo School of Computing 44

Answer: Karnaugh Maps

CD

1 1 1 1

1 1 1 1

AB

A

© 2009, University of Colombo School of Computing 45

Your turn: Karnaugh Maps

CD

1 1

1 1

AB

1 1

1 1

© 2009, University of Colombo School of Computing 46

Answer: Karnaugh Maps

CD

1 1

1 1

AB

C

1 1

1 1

© 2009, University of Colombo School of Computing 47

Simplified Labeling of Karnaugh Maps

In attempting to simplify, first look for the largest

grouping possible:

¾ When you are circling groups, you are allowed to

use the same 1 more than once

¾ If any isolated 1s remain after the groupings, then

each of these is circled as a group of 1s

¾ Finally, before going from the map to a simplified

Boolean expression, any group of 1s that is

completely overlapped by other groups can be

eliminated

© 2009, University of Colombo School of Computing 48

Karnaugh Maps: Overlapping Groups

CD

BC

00 01 11 10

00 01 11 10 00

0 1 1 1

A AB 01

1 1

11 1 1

F = AB + BC 10 1

F = BCD +ACD

© 2009, University of Colombo School of Computing 49

Your turn: Karnaugh Maps

CD

0 0 0 0

0 0 0 1

AB

1 1 0 1

1 1 1 1

© 2009, University of Colombo School of Computing 50

Answer: Karnaugh Maps

CD

F = AC + AB + BCD

0 0 0 0

F = (A+C).(A+B).(B+C+D)

0 0 0 1

AB

1 1 0 1

1 1 1 1

© 2009, University of Colombo School of Computing 51

Drawing a Circuit

© 2009, University of Colombo School of Computing 52

Drawing a Circuit

B+AC

© 2009, University of Colombo School of Computing 53

Drawing a Circuit

B+AC

© 2009, University of Colombo School of Computing 54

Logic Operators

© 2009, University of Colombo School of Computing 55

Logic Operations

Basic logic operators and logic gates

Boolean algebra

Combinational Circuits

Basic circuit design

© 2009, University of Colombo School of Computing 56

Basic Logic Operators and Logic Gates

AND

OR

NOT

XOR (Exclusive OR)

NOR

NAND

XNOR

© 2009, University of Colombo School of Computing 57

Buffer

A B

0 0

1 1

© 2009, University of Colombo School of Computing

AND Operation

. Operator

^ Operator A B A.B

A.B=A^B

0 0 0

0 1 0

1 0 0

1 1 1

© 2009, University of Colombo School of Computing

OR Operation

+ Operator

v Operator A B A+B

A+B=AvB

0 0 0

0 1 1

1 0 1

1 1 1

© 2009, University of Colombo School of Computing

NOT Operation

~ Operator

¬ Operator

A A’

0 1

A = ¬A =~ A = A'

1 0

© 2009, University of Colombo School of Computing

XOR Operation

Operator

A B A⊕ B

A⊕ B 0 0 0

0 1 1

1 0 1

1 1 0

© 2009, University of Colombo School of Computing

NAND Operation

( A.B) = ( A.B )' A B ( A.B)

0 0 1

0 1 1

1 0 1

1 1 0

© 2009, University of Colombo School of Computing

NOR Operation

( A + B) = ( A + B )' A B ( A + B)

0 0 1

0 1 0

1 0 0

1 1 0

© 2009, University of Colombo School of Computing

XNOR Operation

( A ⊕ B) A B ( A ⊕ B)

0 0 1

0 1 0

1 0 0

1 1 1

© 2009, University of Colombo School of Computing

Drawing Logic Gates

In addition to the basic gates, gates with 3,4, or

more inputs can be used

E.g. x + y + z can be implemented with a single

OR gate with 3 inputs

© 2009, University of Colombo School of Computing 66

Drawing Logic Gates

X = ( A + B )C

© 2009, University of Colombo School of Computing

Drawing Logic Gates

X = A + ( B.C ) + D

© 2009, University of Colombo School of Computing

Drawing Logic Gates

X = ( A.B) + ( A.C )

© 2009, University of Colombo School of Computing

Drawing Logic Gates

X = ( A + B ).(C + D).C

© 2009, University of Colombo School of Computing

Reducing Logic Gates

Reducing the number of inputs

¾ The number of inputs to a gate can be reduced by

connecting two (or more) inputs together

¾ The diagram shows a 3-input AND gate operating

as a 2-input AND gate

© 2009, University of Colombo School of Computing 71

Reducing Logic Gates

Reducing the number of inputs

¾ Reducing a NOT gate from a NAND or NOR gate

¾ The diagram shows this for a 2-input NAND gate

© 2009, University of Colombo School of Computing 72

Logic Gates

Typically, not all gate types are used in

implementation

¾ Design and fabrication are simpler if only one or

two types of gates are used

¾ Therefore, it is important to identify functionally

complete sets of gates

¾ This means that any Boolean function can be

implemented using only the gates in the set

© 2009, University of Colombo School of Computing 73

Logic Gates

The following are functionally complete sets:

¾ AND, OR, NOT

¾ AND, NOT

¾ OR, NOT

¾ NAND

¾ NOR

© 2009, University of Colombo School of Computing 74

Logic Gates

AND, OR, and NOT gates constitute a functionally

complete set, since they represent the 3 operations of

Boolean algebra

For the AND and NOT gates to form a functionally

complete set, there must be a way to synthesize the OR

operation from the AND and NOT operations

A+B = A.B

A OR B = NOT( ( NOT A) AND ( NOT B) )

© 2009, University of Colombo School of Computing 75

Logic Gates

Similarly, the OR and NOT operations are functionally

complete because they can be synthesize the AND

operation

A.B = A+B

A AND B = NOT( ( NOT A) OR ( NOT B) )

© 2009, University of Colombo School of Computing 76

Logic Gates

The AND, OR and NOT functions can be

implemented solely with NAND gates, and the same

thing for NOR gates.

For this reason, digital circuits can be, and frequently

are, implemented solely with NAND gates or solely

with NOR gates

© 2009, University of Colombo School of Computing 77

Logic Gates

The diagram shows how the NOT function can be

implemented solely with NAND gate

A A

© 2009, University of Colombo School of Computing 78

Logic Gates

The diagram shows how the AND function can be

implemented solely with NAND gate

A A.B

A.B

B

A

© 2009, University of Colombo School of Computing 79

Logic Gates

The diagram shows how the OR function can be

implemented solely with NAND gate

A

A

A+B

B

B

© 2009, University of Colombo School of Computing 80

Logic Gates

Gate Equivalent in NAND gates

NOT

AND

OR

NOR

© 2009, University of Colombo School of Computing 81

Your turn

Draw a diagram that shows how the NOT function

can be implemented solely with NOR gate

© 2009, University of Colombo School of Computing 82

Logic Gates

The diagram shows how the NOT function can be

implemented solely with NOR gate

A A

© 2009, University of Colombo School of Computing 83

Your turn

Draw a diagram that shows how the OR function

can be implemented solely with NOR gate

© 2009, University of Colombo School of Computing 84

Logic Gates

The diagram shows how the OR function can be

implemented solely with NOR gate

A A+B

A+B

© 2009, University of Colombo School of Computing 85

Your turn

Draw a diagram that shows how the AND function

can be implemented solely with NOR gate

© 2009, University of Colombo School of Computing 86

Logic Gates

The diagram shows how the AND function can be

implemented solely with NOR gate

A

A

A. B

B

B

© 2009, University of Colombo School of Computing 87

Substituting Gates in an Logic System

© 2009, University of Colombo School of Computing 88

Substituting Gates in an Logic System

© 2009, University of Colombo School of Computing 89

Substituting Gates in an Logic System

© 2009, University of Colombo School of Computing 90

Combinational Circuits

© 2009, University of Colombo School of Computing 91

Combinational Logic

Also called combinatorial logic

A type of logic circuit whose output is a function of

the present input only

© 2009, University of Colombo School of Computing 92

Half Adder

Finds the sum of two bits

The sum can be found

using the XOR operation

and the carry using the

AND operation

© 2009, University of Colombo School of Computing 93

Full Adder

We can change our half adder into to a full adder by

including gates for processing the carry bit

The truth table for a full adder is:

© 2009, University of Colombo School of Computing 94

Converting a Half Adder into a Full Adder

© 2009, University of Colombo School of Computing 95

Ripple-carry Adder (I)

Just as we combined half adders to make a full adder,

full adders can be connected in series

¾ The carry bit “ripples” from one adder to the next;

hence, this configuration is called a ripple-carry adder

O15 O1 O0

© 2009, University of Colombo School of Computing 96

Ripple-carry Adder (II)

Digits of

first number

Digits of

second number

1/2 1/2 1/2 1/2

Carry

1/2 1/2 1/2

Sum

© 2009, University of Colombo School of Computing 97

Adder

Adders (and other A3-A0 B3-B0

arithmetic circuits)

are usually drawn inputs

like this in block

diagrams

+

collections of parallel,

related wires like this are output

known as buses; they carry

multi-bit values between

out3-out0

components

© 2009, University of Colombo School of Computing 98

Decoder

Selects a memory location according a binary value

placed on the address lines of a memory bus

Decoders with n inputs can select any of 2n locations

© 2009, University of Colombo School of Computing 99

2-to-4 Decoder

If x = 0 and y = 1,

which output line

is enabled?

© 2009, University of Colombo School of Computing 100

Multiplexer

A multiplexer does the opposite of a decoder

Selects a single output from several inputs

¾ The particular input chosen for output is determined

by the value of the multiplexer’s control lines

¾ To select among n inputs, log2n control lines are

needed

© 2009, University of Colombo School of Computing 101

4-to-1 Multiplexer

If S0 = 1 and S1 = 0,

which input is

selected as output?

© 2009, University of Colombo School of Computing 102

Arithmetic

• Computers need to do more than just addition

– arithmetic: + – * / %

– logic: & | ~ << >>

• Need a circuit that can select operation to perform

© 2009, University of Colombo School of Computing 103

Arithmetic Logic Unit (ALU)

A B

more

operations

...

here

op op op op

0 + 1 * 2 & 3 <<

Multiplexer: a

MUX

0 1 2 3 ..

combinatorial op

circuit which

selects exactly op selects operation:

one input out 0 = add, 1 = multiply, ...

© 2009, University of Colombo School of Computing 104

Arithmetic Logic Unit (ALU)

A = 15 B=2

for

example:

compute

15 << 2

more

operations

here

op

0 +

op

1 *

op

2 &

op

3 << ...

other results also

MUX

0 1 2 3 ..

computed but op = 3

ignored by

multiplexer out = 60

© 2009, University of Colombo School of Computing 105

Sequential Logic – Memory

© 2009, University of Colombo School of Computing 106

Sequential Logic Circuits

Combinational logic circuits are perfect for situations

which require the immediate application of a Boolean

function to a set of inputs

But, here are times when we need a circuit to change

its value with consideration to its current state as well

as its inputs

¾ These circuits have to “remember” their current

state

Sequential logic circuits provide this functionality

© 2009, University of Colombo School of Computing 107

Sequencing Events

Sequential logic circuits require a means by which

events can be sequenced

¾ State changes are controlled by clocks

• A “clock” is a special circuit that sends electrical

pulses through a circuit

¾ Clocks produce electrical waveforms such as this one

¾ State changes occur in sequential circuits only when

the clock ticks

© 2009, University of Colombo School of Computing 108

Feedback in Sequential Logic Circuits

Sequential circuits rely on feedback to retain their

state values

Feedback in digital circuits occurs when an output is

looped back to the input

¾ Example,

If Q is 0 it will always be 0, if it is 1, it will always

be 1

© 2009, University of Colombo School of Computing 109

SR Flip-flop (Set-Reset) (I)

• The behavior of an SR flip-

flop is described by a

characteristic table

– Q(t) output at time t

– Q(t+1) output after the

next clock pulse

© 2009, University of Colombo School of Computing 110

SR Flip-flop: Block Diagram

S and R Q and Q =

Flip-flops are often input output

drawn like this in

block diagrams

S Q

CK

R Q

CK is read/write (“clock”

because this input is

connected to the computer’s

processor clock)

© 2009, University of Colombo School of Computing 111

SR Flip-flop (II)

The SR flip-flop has three inputs: S, R and Q(t)

¾ When both S and R are 1, the SR flip-flop is unstable

© 2009, University of Colombo School of Computing 112

JK Flip-flop (Jack Kilby)

Modified version of the SR flip-flop to provide a stable

state when both inputs are 1

© 2009, University of Colombo School of Computing 113

JK Flip-flop: Binary Counter

The low-order bit is

complemented at each

clock pulse

Whenever it changes from

1 to 0, the next bit is

complemented, and so on

through the other flip-flops

© 2009, University of Colombo School of Computing 114

D Flip-flop (Data)

Fundamental circuit of computer memory

Used to store 1 bit

Can be implemented with gates

Not combinatorial logic

¾ because current output may depend on previous

state

Example of sequential logic

¾ current output depends on inputs and prior output

© 2009, University of Colombo School of Computing 115

D Flip-flop

NOR gate: OR gate

followed by NOT gate

data in

data out

read/write control:

read/write 0 = read, 1 = write

© 2009, University of Colombo School of Computing 116

D Flip-flop: Writing

Try changing data in to 0

and watch data out

data in = 1 1

1

0

1

1

1 0

0 1

0

1

data out = 1

when read/write = 1,

read/write = 1 data out = data in

(write)

© 2009, University of Colombo School of Computing 117

D Flip-flop: Reading

data in = ? ?

0 0

0

1

? 0

? 1

0

0

data out = 1

when read/write = 0, no signals

read/write = 0 in box can change –- data out

(read) holds value regardless of data in

© 2009, University of Colombo School of Computing 118

D Flip-flop: Block Diagram

D = data Q = data

in out

D Q

CK

CK is read/write (“clock”

because this input is often

connected to the computer’s

processor clock)

© 2009, University of Colombo School of Computing 119

D Flip-flop: 4-bit Register

A register stores data

inside the CPU

© 2009, University of Colombo School of Computing 120

Memory

• Memory can store many bits independently

– register banks contain many flip-flops

• Need to identify which bit (flip-flop) to read or write

• Give each flip-flop a unique number (address)

© 2009, University of Colombo School of Computing 121

Memory: Circuit Diagram

Decoder: feeds input to selected output, 0 to all others

data in

D Q

address 0

CK

D Q

0

address 1

0 data

1 1

out

MUX

CK

DEC

2 2

3 3

D Q

... address 2 ...

CK

D Q

address address 3

CK

. . . millions more flip-

flip-flops . .

.

rd/wr

© 2009, University of Colombo School of Computing 122

Memory: Writing

Writing value

data in

1 to flip-flop

1

1

D Q

address 0

at address 2

0

CK

1 D Q

0

address 1

0 data

1 0 1

out

MUX

CK

DEC

2 2

3 1 D Q

3

...

1 1 address 2 ...

CK

1 D Q

address address 3

0

CK

2

. . . millions more flip-

flip-flops . .

.

1 rd/wr

© 2009, University of Colombo School of Computing 123

Memory: Reading

We just wrote Reading

data in

this value value from

D Q

address 0

flip-flop at

0

CK address 2

D Q

0

address 1

0 data

1 0 1

out

MUX

CK

DEC

2 2

3

D Q

1 3 1

...

1 0 1 address 2 ...

CK

D Q

address address 3

0

CK

2

. . . millions more flip-

flip-flops . .

.

0 rd/wr

© 2009, University of Colombo School of Computing 124

Memory: 4-words, 3 bits/word

© 2009, University of Colombo School of Computing 125

Summary (I)

Computers are implementations of Boolean logic

Boolean functions are completely described

by Truth Tables

Logic gates are small circuits that implement Boolean

operators

The basic gates are AND, OR and NOT

The “universal gates” are NOR and NAND

© 2009, University of Colombo School of Computing 126

Summary (II)

Computer circuits consist of combinational logic

circuits and sequential logic circuits

Combinational circuits produce outputs (almost)

immediately when their inputs change

Sequential circuits have internal states as well as

combinations of input and output logic

¾ The outputs may also depend on the states left behind

by previous inputs

¾ Sequential circuits require clocks to control their

changes of state

¾ The basic sequential circuit unit is the flip-flop

© 2009, University of Colombo School of Computing 127

Thank You

© 2009, University of Colombo School of Computing 128

You might also like

- Development and Deployment of Multiplayer Online Games, Vol. IIDocument437 pagesDevelopment and Deployment of Multiplayer Online Games, Vol. IItiyihis146100% (1)

- Laboratory Activities Computer Engineering Drafting and DesignDocument74 pagesLaboratory Activities Computer Engineering Drafting and DesignPaul Santos Nonat75% (4)

- Digital Logic Design (Cen-122) (2+1)Document26 pagesDigital Logic Design (Cen-122) (2+1)Komal AliNo ratings yet

- Lecture No 7, 8, 9 & 10Document96 pagesLecture No 7, 8, 9 & 10Muhammad AnasNo ratings yet

- Teachers Note - Section 03Document105 pagesTeachers Note - Section 03kkNo ratings yet

- 4 CH2 P2 Boolean Algebra ( (2.01) SEM 442Document44 pages4 CH2 P2 Boolean Algebra ( (2.01) SEM 442BadrNo ratings yet

- L5 DLD Boolean SimplificationDocument29 pagesL5 DLD Boolean SimplificationandreytagnoNo ratings yet

- Boolean Algebra and Logic SimplificationDocument30 pagesBoolean Algebra and Logic SimplificationAbdullah AftabNo ratings yet

- Digital Logic Design - Boolean AlgebraDocument17 pagesDigital Logic Design - Boolean AlgebraTroon SoonNo ratings yet

- Discrete Mathematics For Ece: Boolean Algebra and Logic SimplificationDocument41 pagesDiscrete Mathematics For Ece: Boolean Algebra and Logic SimplificationLykaShanineGabrielMendozaNo ratings yet

- Lecture 4 DLD Boolean Functions Switching Algebra and Logic Gates1Document27 pagesLecture 4 DLD Boolean Functions Switching Algebra and Logic Gates1Ruby PoddarNo ratings yet

- Chapter Three: Boolean Algebra and Logic SimplificationDocument30 pagesChapter Three: Boolean Algebra and Logic Simplificationmift ademNo ratings yet

- Digital Fundamentals: FloydDocument21 pagesDigital Fundamentals: FloydadilNo ratings yet

- Simplification (Minimization) of Logical FunctionsDocument15 pagesSimplification (Minimization) of Logical FunctionsErdem BahadirNo ratings yet

- Digital Logic DesignDocument41 pagesDigital Logic DesignAri BaderNo ratings yet

- DE Lecture 2Document26 pagesDE Lecture 2Shakawat Hossain ShifatNo ratings yet

- Logic Gates and K-MapDocument9 pagesLogic Gates and K-MapAditya Kumar SharmaNo ratings yet

- Digital Logic DesignDocument23 pagesDigital Logic DesignHaider AliNo ratings yet

- DLLec5b NotesDocument4 pagesDLLec5b NotesChintan MandalNo ratings yet

- Chapter 6 - Boolean - EEDocument43 pagesChapter 6 - Boolean - EEIrlan DinNo ratings yet

- 05 - Boolean FunctionDocument51 pages05 - Boolean FunctionSyamil AzrilzNo ratings yet

- Digital Logic & Computer Architecture: (Lesson 4)Document9 pagesDigital Logic & Computer Architecture: (Lesson 4)Muhammad FurqanNo ratings yet

- Logic Simplification SlideDocument46 pagesLogic Simplification Slideتوان ظاهيرو الدينNo ratings yet

- CH 04Document80 pagesCH 04nashitahalwaz95No ratings yet

- DLD Fundamentals FloydDocument44 pagesDLD Fundamentals FloydMuhammad AsadNo ratings yet

- Boolean AlgebraDocument31 pagesBoolean Algebraeverthing is here videos and statusNo ratings yet

- Module 4 - Boolean AlgebraDocument20 pagesModule 4 - Boolean AlgebraKejeindrranNo ratings yet

- Sheet 4Document8 pagesSheet 4Loay AhmedNo ratings yet

- 2 17 11 PDFDocument8 pages2 17 11 PDFAdamNo ratings yet

- Chapter 3 MinDocument19 pagesChapter 3 MinCybertron BadeeNo ratings yet

- Digital Fundamentals: FloydDocument32 pagesDigital Fundamentals: FloydTalha KhanNo ratings yet

- Dwaraka Doss Goverdhan Doss Vaishnav College CHENNAI - 106: Fundamentals of Digitial ElectronicsDocument25 pagesDwaraka Doss Goverdhan Doss Vaishnav College CHENNAI - 106: Fundamentals of Digitial ElectronicsRyuzz MalfoyNo ratings yet

- Boolean Algebra..Document40 pagesBoolean Algebra..Mini SharmaNo ratings yet

- 07 BooleanAlgebraDocument21 pages07 BooleanAlgebraGans GanesanNo ratings yet

- 003 Boolean AlgebraDocument19 pages003 Boolean AlgebraMarid CandraNo ratings yet

- 6.1 Lectures - Module4 - Digital ElectronicsDocument16 pages6.1 Lectures - Module4 - Digital ElectronicsSree dhathri DevaNo ratings yet

- Boolean Algebra PDFDocument20 pagesBoolean Algebra PDFTanuNo ratings yet

- C06 BooleanAlgebrasDocument7 pagesC06 BooleanAlgebrasNaseer ahmadNo ratings yet

- Unit 20 - Lecture 03Document30 pagesUnit 20 - Lecture 03Kusal DananjayaNo ratings yet

- C16 Canonical FormsDocument24 pagesC16 Canonical Formsyadhucr5577No ratings yet

- MIT18 02SC PB 3 CombDocument2 pagesMIT18 02SC PB 3 CombAbrar Ul HaqNo ratings yet

- ECSE-4760 Real-Time Applications in Control & Communications Experiments in Digital Logic DesignDocument24 pagesECSE-4760 Real-Time Applications in Control & Communications Experiments in Digital Logic DesignMitu BaralNo ratings yet

- Digital Logic DesignDocument36 pagesDigital Logic DesignnayabNo ratings yet

- Lec1snip2 DotprodDocument3 pagesLec1snip2 DotprodMohammad aneeb shinwariNo ratings yet

- (De) 1Document17 pages(De) 1Rahul BhatiNo ratings yet

- Computer Architecture: Nguyễn Trí ThànhDocument157 pagesComputer Architecture: Nguyễn Trí Thànhhoang.van.tuanNo ratings yet

- 48 606 Olteanu Emil 2Document6 pages48 606 Olteanu Emil 2nou channarithNo ratings yet

- Chapter 4Document28 pagesChapter 4Soman AunNo ratings yet

- Unit - 3 - Combinational Logic DesignDocument27 pagesUnit - 3 - Combinational Logic DesignAvinash SharmaNo ratings yet

- Boolean Algebra and Logic Gates: Basic TheoremsDocument18 pagesBoolean Algebra and Logic Gates: Basic Theoremsalma bella macaldoNo ratings yet

- Experiment No.1:Introduction To Basic Gates and Logic Simplification TechniquesDocument6 pagesExperiment No.1:Introduction To Basic Gates and Logic Simplification TechniquesAurongo NasirNo ratings yet

- ACFrOgBTICzbZgajnUi3e TJwOPELhujoXwlPaX W6TTCoJGxI5810vc8Yd8NTKdHf sa6SxtlxNAaDCVkmq4TLKWNsmbBzXPVYX93O4xjx7qKv-YC-m7kTL8FXxgrB5ZIGn0PTYziVtvC5ADp6UDocument35 pagesACFrOgBTICzbZgajnUi3e TJwOPELhujoXwlPaX W6TTCoJGxI5810vc8Yd8NTKdHf sa6SxtlxNAaDCVkmq4TLKWNsmbBzXPVYX93O4xjx7qKv-YC-m7kTL8FXxgrB5ZIGn0PTYziVtvC5ADp6UNijhum ChoudhuryNo ratings yet

- Week 3Document15 pagesWeek 3NaEem KhanNo ratings yet

- 15 Boolean Algebra 23 Jul 2018reference Material I - Boolean - AlgebraDocument19 pages15 Boolean Algebra 23 Jul 2018reference Material I - Boolean - Algebranayan agalNo ratings yet

- Fundamental of Digital Systems Unit II 08-3-2024Document57 pagesFundamental of Digital Systems Unit II 08-3-2024usamaabdurrahman.cseNo ratings yet

- Cat-1 July 2019 Cat-1 July 2019Document1 pageCat-1 July 2019 Cat-1 July 2019malaiNo ratings yet

- Anupam Sir DLD3Document117 pagesAnupam Sir DLD3Adhara MukherjeeNo ratings yet

- Lecture 030223Document55 pagesLecture 030223Divyansh SinghNo ratings yet

- Lec 08Document28 pagesLec 08bivaye4887No ratings yet

- Fundamentals of Computers: Boolean Algebra of Switching CircuitsDocument23 pagesFundamentals of Computers: Boolean Algebra of Switching CircuitsMD. Mohaiminul IslamNo ratings yet

- Standard-Slope Integration: A New Approach to Numerical IntegrationFrom EverandStandard-Slope Integration: A New Approach to Numerical IntegrationNo ratings yet

- SECTION 3 - Solving Equations and Inequalities PDFDocument23 pagesSECTION 3 - Solving Equations and Inequalities PDFDress ntrNo ratings yet

- Write Following Two Java Programs That Capable To Add and Subtract Given Two Numbers. Methods Without Passing ParametersDocument3 pagesWrite Following Two Java Programs That Capable To Add and Subtract Given Two Numbers. Methods Without Passing ParametersDress ntrNo ratings yet

- Section 1 - Number PDFDocument19 pagesSection 1 - Number PDFDress ntrNo ratings yet

- Introduction To Networks: 9.1 Uses of A NetworkDocument19 pagesIntroduction To Networks: 9.1 Uses of A NetworkDress ntrNo ratings yet

- 1.2.1 Electronic Computers Based On Digital SwitchingDocument22 pages1.2.1 Electronic Computers Based On Digital SwitchingDress ntrNo ratings yet

- Input and Output DevicesDocument27 pagesInput and Output DevicesDress ntrNo ratings yet

- New Text DocumentDocument1 pageNew Text DocumentDress ntrNo ratings yet

- HNDITSyllabus DetailedDocument318 pagesHNDITSyllabus DetailedDress ntrNo ratings yet

- HNDIT Curriculum Outline LatestDocument10 pagesHNDIT Curriculum Outline LatestDress ntrNo ratings yet

- AA13 EBA (Tam) AdDocument7 pagesAA13 EBA (Tam) AdDress ntrNo ratings yet

- (Aa15) Tpahghuj Njhopw GHLFSK Kfhikj JTKK Tpahghuj Njhopw GHLFSK Kfhikj JTKK Tpahghuj Njhopw GHLFSK Kfhikj JTKK Tpahghuj Njhopw GHLFSK Kfhikj JTKKDocument7 pages(Aa15) Tpahghuj Njhopw GHLFSK Kfhikj JTKK Tpahghuj Njhopw GHLFSK Kfhikj JTKK Tpahghuj Njhopw GHLFSK Kfhikj JTKK Tpahghuj Njhopw GHLFSK Kfhikj JTKKDress ntrNo ratings yet

- (Aa11) Epjpf FZF FPL L MBG Gilfs Epjpf FZF FPL L MBG Gilfs Epjpf FZF FPL L MBG Gilfs Epjpf FZF FPL L MBG GilfsDocument10 pages(Aa11) Epjpf FZF FPL L MBG Gilfs Epjpf FZF FPL L MBG Gilfs Epjpf FZF FPL L MBG Gilfs Epjpf FZF FPL L MBG GilfsDress ntrNo ratings yet

- TPDH TPDH TPDH TPDH: Kog GJPG GupikailajDocument7 pagesTPDH TPDH TPDH TPDH: Kog GJPG GupikailajDress ntrNo ratings yet

- Micom P211 OC & EF RelayDocument8 pagesMicom P211 OC & EF Relaysatya1417No ratings yet

- KS3 Maths OverviewDocument4 pagesKS3 Maths OverviewJakubNo ratings yet

- GA32-0378-05 Installation Planning 3490E F01Document136 pagesGA32-0378-05 Installation Planning 3490E F01paolovelaNo ratings yet

- Newton S Laws of Motion Lesson PlanDocument9 pagesNewton S Laws of Motion Lesson Plananon_212484834No ratings yet

- B-Tech Sample Internship Report FormatDocument6 pagesB-Tech Sample Internship Report FormatVAIBHAV DESHMUKHNo ratings yet

- Online Safety and Security PPTDocument17 pagesOnline Safety and Security PPTJEMNA PITOGONo ratings yet

- Gyro Skipper PlansDocument5 pagesGyro Skipper PlansJayantha KandegamaNo ratings yet

- Wiring Diagram: 5-1. LayoutDocument7 pagesWiring Diagram: 5-1. LayoutLuisMiguelCalvoNo ratings yet

- CPO Checklist FINALDocument22 pagesCPO Checklist FINALSW ChenNo ratings yet

- Script QoS PPPoEDocument5 pagesScript QoS PPPoEcabunga2014100% (2)

- 2023-Report-Annual-Marketing-En - Shared by WorldLine TechnologypdfDocument28 pages2023-Report-Annual-Marketing-En - Shared by WorldLine TechnologypdfThuy NghiemNo ratings yet

- UntitledDocument2,001 pagesUntitledmayraNo ratings yet

- Bitdefender GravityZone XDR Datasheet enDocument2 pagesBitdefender GravityZone XDR Datasheet entoretta1984No ratings yet

- Text Messaging Is Better Than ThinkingDocument1 pageText Messaging Is Better Than ThinkingClevanche LightbourneNo ratings yet

- Chapter 17-18 Conflict, Negotiation, and TechnologyDocument72 pagesChapter 17-18 Conflict, Negotiation, and TechnologyHaryadi WidodoNo ratings yet

- GSW Portfolio V02Document21 pagesGSW Portfolio V02أحمد فريد سعد عبد الفتاحNo ratings yet

- Digital Learning Materials Classification and ImplDocument14 pagesDigital Learning Materials Classification and ImplWild Rift00No ratings yet

- Practice Makes Regexp (Reuven M. Lerner, PHD)Document206 pagesPractice Makes Regexp (Reuven M. Lerner, PHD)riccardo.cavarra.rcNo ratings yet

- Analyzing Social Media Engagement and Its Effect On Online Product Purchase Decision BehaviorDocument9 pagesAnalyzing Social Media Engagement and Its Effect On Online Product Purchase Decision Behaviorhi.ashukaNo ratings yet

- Eps Unit 3Document24 pagesEps Unit 3Bhavana PedadaNo ratings yet

- HR Analytics 3rd ChapterDocument16 pagesHR Analytics 3rd ChapterAppu SpecialNo ratings yet

- KS0077 (78,79) Super Learning Kit For ArduinoDocument315 pagesKS0077 (78,79) Super Learning Kit For ArduinoАнтон ПыхаловNo ratings yet

- Data Sheet 3RP2525-1AW30Document6 pagesData Sheet 3RP2525-1AW30mahdi aghamohamadiNo ratings yet

- Fujitsu Air Conditioner OPERATING MANUALDocument6 pagesFujitsu Air Conditioner OPERATING MANUALTavrusNo ratings yet

- Lecture 9 BASIC-LINE-PROTECTIONDocument46 pagesLecture 9 BASIC-LINE-PROTECTIONmuaz_aminu1422No ratings yet

- Target Cyber Breach Report: "Security Is Only As Strong As The Weakest Link"Document5 pagesTarget Cyber Breach Report: "Security Is Only As Strong As The Weakest Link"Manjunath AbhiNo ratings yet

- Initial PagesDocument7 pagesInitial PagesLaxmisha GowdaNo ratings yet

- Software DevelopmentDocument272 pagesSoftware Developmentszpakos100% (1)