Professional Documents

Culture Documents

FAN7389 3-Phase Half-Bridge Gate-Drive IC: Features Description

FAN7389 3-Phase Half-Bridge Gate-Drive IC: Features Description

Uploaded by

Amjad ShehadaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

FAN7389 3-Phase Half-Bridge Gate-Drive IC: Features Description

FAN7389 3-Phase Half-Bridge Gate-Drive IC: Features Description

Uploaded by

Amjad ShehadaCopyright:

Available Formats

FAN7389 — 3-Phase Half-Bridge Gate-Drive IC

January 2013

FAN7389

3-Phase Half-Bridge Gate-Drive IC

Features Description

Floating Channel for Bootstrap Operation to +600 V The FAN7389 is a monolithic three-phase half-bridge

gate-drive IC designed for high-voltage, high-speed

Typically 350 mA/650 mA Sourcing/Sinking Current

driving MOSFETs and IGBTs operating up to +600 V.

Driving Capability for All Channels

Extended Allowable Negative VS Swing to -9.8 V for Fairchild’s high-voltage process and common-mode

Signal Propagation at VDD=VBS=15 V noise canceling technique provide stable operation of

high-side drivers under high-dv/dt noise circumstances.

Output In-Phase with Input Signal

An advanced level-shift circuit allows high-side gate

Over-Current Shutdown Turns off All Six Drivers driver operation up to VS = -9.8 V (typical) for VBS =15 V.

Matched Propagation Delay for All Channels The protection functions include under-voltage lockout

3.3 V and 5.0 V Input Logic Compatible and inverter over-current trip with an automatic fault-

clear function.

Adjustable Fault-Clear Timing

Over-current protection that terminates all six outputs

Built-in Advanced Input Filter can be derived from an external current-sense resistor.

Built-in Shoot-Through Prevention Logic An open-drain fault signal is provided to indicate that an

over-current or under-voltage shutdown has occurred.

Built-in Soft Turn-Off Function

The UVLO circuits prevent malfunction when VDD and

Common-Mode dv/dt Noise Canceling Circuit VBS are lower than the specified threshold voltage.

Built-in UVLO Functions for All Channels Output drivers typically source and sink 350 mA and

650 mA, respectively; which is suitable for three-phase

Applications half-bridge applications in motor drive systems.

3-Phase Motor Inverter Driver 28-SOIC

Air Conditioners

Washing Machines

General-Purpose Three-Phase Inverters

Ordering Information

Operating Packing

Part Number Package

Temperature Method

FAN7389MX1(1) 28-Lead, Small Outline Integrated Circuit Wide Body (SOIC) -40 to +125°C Tape & Reel

Note:

1. These devices passed wave soldering test by JESD22A-111.

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3

FAN7389 — 3-Phase Half-Bridge Gate-Drive IC

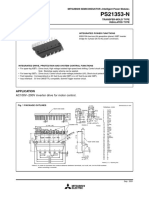

Typical Application Diagram

Figure 1. 3-Phase BLDC Motor Drive Application

Internal Block Diagram

Figure 2. Functional Block Diagram

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3 2

FAN7389 — 3-Phase Half-Bridge Gate-Drive IC

Pin Configuration

Figure 3. Pin Configuration

Pin Definitions

Pin Name Description

1 VDD Logic and low-side gate driver power supply voltage

2 HIN1 Logic Input 1 for high-side gate 1 driver

3 HIN2 Logic Input 2 for high-side gate 2 driver

4 HIN3 Logic Input 3 for high-side gate 3 driver

5 LIN1 Logic Input 1 for low-side gate 1 driver

6 LIN2 Logic Input 2 for low-side gate 2 driver

7 LIN3 Logic Input 3 for low-side gate 3 driver

8 FO Fault output with open drain (indicates over-current and low-side under-voltage)

9 CS Analog input for over-current shutdown

10 EN Logic input for shutdown functionality

11 RCIN An external RC network input used to define the fault-clear delay

12 VSS Logic ground

13 COM Low-side driver return

14 LO3 Low-side gate driver 3 output

15 LO2 Low-side gate driver 2 output

16 LO1 Low-side gate driver 1 output

17, 21, 25 NC No connect

18 VS3 High-side driver 3 floating supply offset voltage

19 HO3 High-side driver 3 gate driver output

20 VB3 High-side driver 3 floating supply

22 VS2 High-side driver 2 floating supply offset voltage

23 HO2 High-side driver 2 gate driver output

24 VB2 High-side driver 2 floating supply

26 VS1 High-side driver 1 floating supply offset voltage

27 HO1 High-side driver 1 gate driver output

28 VB1 High-side driver 1 floating supply

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3 3

FAN7389 — 3-Phase Half-Bridge Gate-Drive IC

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be

operable above the recommended operating conditions and stressing the parts to these levels is not recommended.

In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability.

The absolute maximum ratings are stress ratings only. TA=25°C, unless otherwise specified.

Symbol Parameter Min. Max. Unit

VS High-Side Floating Offset Voltage VB1,2,3-25.0 VB1,2,3+0.3 V

VB High-Side Floating Supply Voltage -0.3 625.0 V

VDD Low-Side and Logic-Fixed Supply Voltage -0.3 25.0 V

VHO High-Side Floating Output Voltage VHO1,2,3 VS1,2,3-0.3 VB1,2,3+0.3 V

VLO Low-Side Floating Output Voltage VLO1,2,3 -0.3 VDD+0.3 V

VIN Input Voltage (HINx, LINx, CS, and EN) -0.3 5.5 V

VFO Fault Output Voltage ( FO ) -0.3 VDD+0.3 V

PWHIN High-Side Input Pulse Width 500 ns

dVS/dt Allowable Offset Voltage Slew Rate ±50 V/ns

(2,3,4)

PD Power Dissipation 1.4 W

θJA Thermal Resistance 70 °C/W

TJ Junction Temperature 150 °C

TSTG Storage Temperature -55 150 °C

Notes:

2. Mounted on 76.2 x 114.3 x 1.6 mm PCB (FR-4 glass epoxy material).

3. Refer to the following standards:

JESD51-2: Integral circuits thermal test method environmental conditions - natural convection

JESD51-3: Low effective thermal conductivity test board for leaded surface-mount packages.

4. Do not exceed PD under any circumstances.

Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to Absolute Maximum Ratings.

Symbol Parameter Min. Max. Unit

VB1,2,3 High-Side Floating Supply Voltage VS1,2,3+10 VS1,2,3+20 V

VS1,2,3 High-Side Floating Supply Offset Voltage 6-VDD 600 V

VDD Low-Side and Logic Fixed Supply Voltage 10 20 V

VHO1,2,3 High-Side Output Voltage VS1,2,3 VB1,2,3 V

VLO1,2,3 Low-Side Output Voltage COM VDD V

VFO Fault Output Voltage ( FO ) COM VDD V

VCS Current-Sense Pin Input Voltage COM 5 V

VIN Logic Input Voltage (HIN1,2,3 and LIN1,2,3) COM 5 V

VSS Logic Ground -5 5 V

TA Ambient Temperature -40 +125 °C

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3 4

FAN7389 — 3-Phase Half-Bridge Gate-Drive IC

Electrical Characteristics

VBIAS (VDD, VBS1,2,3) = 15.0 V and TA = 25°C unless otherwise specified. The VIN and IIN parameters are referenced to

COM and are applicable to all six channels. The VO and IO parameters are referenced to VS1,2,3 and COM and are

applicable to the respective output leads: HO1,2,3 and LO1,2,3. The VDDUV parameters are referenced to COM. The

VBSUV parameters are referenced to VS1,2,3.

Symbol Parameter Conditions Min. Typ. Max. Unit

Low-Side Power Supply Section

IQDD Quiescent VDD Supply Current VLIN1,2,3=0 V or 5 V, EN=0 V 200 μA

IPDD Operating VDD Supply Current fLIN1,2,3=20 kHz, rms Value 400 μA

VDD Supply Under-Voltage Positive-Going

VDDUV+ VDD=Sweep 7.5 8.5 9.3 V

Threshold

VDD Supply Under-Voltage Negative-Going

VDDUV- VDD=Sweep 7.0 8.0 8.7 V

Threshold

VDD Supply Under-Voltage Lockout

VDDHYS VDD=Sweep 0.5 V

Hysteresis

Bootstrapped Power Supply Section

VBS Supply Under-Voltage Positive-Going

VBSUV+ VBS1,2,3=Sweep 7.5 8.5 9.3 V

Threshold

VBS Supply Under-Voltage Negative-Going

VBSUV- VBS1,2,3=Sweep 7.0 8.0 8.7 V

Threshold

VBS Supply Under-Voltage Lockout

VBSHYS VBS1,2,3=Sweep 0.5 V

Hysteresis

ILK Offset Supply Leakage Current VB1,2,3=VS1,2,3=600 V 10 μA

IQBS Quiescent VBS Supply Current VHIN1,2,3=0V or 5 V, EN=0V 10 50 80 μA

IPBS Operating VBS Supply Current fHIN1,2,3=20 kHz, rms Value 200 420 480 μA

Gate Driver Output Section

VOH High-Level Output voltage, VBIAS-VO IO=0 mA (No Load) 100 mV

VOL Low-Level Output voltage, VO IO=0 mA (No Load) 100 mV

(5)

IO+ Output HIGH Short-Circuit Pulse Current VO=0 V, VIN=5 V with PW≤10 µs 250 350 mA

VO=15 V, VIN=0 V with

IO- Output LOW Short-Circuit Pulsed Current(5) 500 650 mA

PW≤10 µs

Allowable Negative VS Pin Voltage for HIN

VS -9.8 -7.0 V

Signal Propagation to HO

Logic Input Section

VIH Logic "1" Input Voltage HIN1,2,3, LIN1,2,3 2.5 V

VIL Logic "0" Input Voltage HIN1,2,3, LIN1,2,3 0.8 V

IIN+ Logic Input Bias Current (HO=LO=HIGH) VIN=5 V 100 μA

IIN- Logic Input Bias Current (HO=LO=LOW) VIN=0 V 2 μA

RIN Logic Input Pull-Down Resistance 50 KΩ

Enable Control Section (EN)

VEN+ Enable Positive-Going Threshold Voltage 2.5 V

VEN- Enable Negative-Going Threshold Voltage 0.8 V

IEN+ Logic Enable “1” Input Bias Current VEN=5 V (Pull-Down=150KΩ) 33 μA

IEN- Logic Enable “0” Input Bias Current VEN=0 V 2 μA

Continued on the following page…

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3 5

FAN7389 — 3-Phase Half-Bridge Gate-Drive IC

Electrical Characteristics

VBIAS (VDD, VBS1,2,3) = 15.0 V and TA = 25°C unless otherwise specified. The VIN and IIN parameters are referenced to

COM and are applicable to all six channels. The VO and IO parameters are referenced to VS1,2,3 and COM and are

applicable to the respective output leads: HO1,2,3 and LO1,2,3. The VDDUV parameters are referenced to COM. The

VBSUV parameters are referenced to VS1,2,3.

Symbol Parameter Conditions Min. Typ. Max. Unit

Over-Current Protection Section

(5)

VCSTH+ Over-Current Detect Positive Threshold 400 500 600 mV

VCSTH- Over-Current Detect Negative Threshold(5) 440 mV

(5)

VCSHYS Over-Current Detect Hysteresis 60 mV

ICSIN Short-Circuit Input Current VCSIN=1 V 5 10 15 μA

ISOFT Soft Turn-Off Sink Current 25 40 55 mA

Fault Output Section

VRCINTH+ RCIN Positive-Going Threshold Voltage 3.3 V

VRCINTH- RCIN Negative-Going Threshold Voltage 2.6 V

VRCINHYS RCIN Hysteresis Voltage 0.7 V

IRCIN RCIN Internal Current Source CRCIN=2 nF 3 5 7 µA

VFOL Fault Output Low Level Voltage VCS=1 V, IFO=1.5 mA 0.2 0.5 V

RDSRCIN RCIN On Resistance IRCIN=1.5 mA 50 75 100 Ω

RDSFO Fault Output On Resistance IFO=1.5 mA 90 130 170 Ω

Note:

5. These parameters are guaranteed by design.

Dynamic Electrical Characteristics

TA=25°C, VBIAS (VDD, VBS1,2,3) = 15.0 V, VS1,2,3 = COM, CRCIN=2 nF, and CLoad = 1000 pF unless otherwise specified.

Symbol Parameter Conditions Min. Typ. Max. Unit

tON Turn-On Propagation Delay VLIN1,2,3=VHIN1,2,3=0 V, VS1,2,3=0 V 350 500 650 ns

tOFF Turn-Off Propagation Delay VLIN1,2,3=VHIN1,2,3=5 V, VS1,2,3=0 V 350 500 650 ns

tR Turn-On Rise Time VLIN1,2,3=VHIN1,2,3=0 V 20 50 100 ns

tF Turn-Off Fall Time VLIN1,2,3=VHIN1,2,3=5 V 10 30 80 ns

tEN Enable LOW to Output Shutdown Delay 400 500 600 ns

(6)

tCSBLT CS Pin Leading-Edge Blanking Time 200 300 400 ns

(7)

tCSFO Time from CS Triggering to FO From VCSC=1V to FO Turn-Off 630 ns

Time from CS Triggering to All Gate From VCSC=1V to Starting Gate

tCSOFF 640 ns

Outputs Turn-Off(7) Turn-Off

tFLTIN Input Filtering Time(8) (HINx, LINx, EN) 200 250 300 ns

tFLTCLR Fault-Clear Time 1.3 ms

DT Dead Time 250 300 350 ns

MDT Dead-Time Matching (All Six Channels) 50 ns

MT Delay Matching (All Six Channels) 50 ns

PM Output Pulse-Width Matching(6,9) PWIN > 1µs 50 100 ns

Notes:

6. These parameters are guaranteed by design.

7. These parameters are referenced to specified CRCIN(=2 nF), and proportional to value of CRCIN as shown in

Figure 43. It is strongly recommended that the capacitor on RCIN pin should be less than 5 nF.

8. The minimum width of the input pulse should exceed 500 ns to ensure the filtering time of the input filter is exceeded.

9. PM is defined as PWIN-PWOUT.

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3 6

FAN7389 — 3-Phase Half-Bridge Gate-Drive IC

Typical Characteristics

650 650

600 600

550 550

tON [ns]

tOFF [ns]

500 500

450 450

400 High-Side 400 High-Side

Low-Side Low-Side

350 350

-40 -20 0 20 40 60 80 100 120 -40 -20 0 20 40 60 80 100 120

Temperature [°C] Temperature [°C]

Figure 4. Turn-On Propagation Delay Figure 5. Turn-Off Propagation Delay

vs. Temperature vs. Temperature

100 80

90 70

80 60

70 50

tF [ns]

tR [ns]

60 40

50 30

40 20

High-Side High-Side

30 Low-Side 10

Low-Side

20 0

-40 -20 0 20 40 60 80 100 120 -40 -20 0 20 40 60 80 100 120

Temperature [°C] Temperature [°C]

Figure 6. Turn-On Rise Time vs. Temperature Figure 7. Turn-Off Fall Time vs. Temperature

600 2.0

1.8

550

tFLTCLR [ms]

1.6

tEN [ns]

500

1.4

450

1.2

400 1.0

-40 -20 0 20 40 60 80 100 120 -40 -20 0 20 40 60 80 100 120

Temperature [°C] Temperature [°C]

Figure 8. Enable LOW to Output Shutdown Delay Figure 9. Fault-Clear Time vs. Temperature

vs. Temperature

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3 7

FAN7389 — 3-Phase Half-Bridge Gate-Drive IC

Typical Characteristics (Continued)

400 50

350 25

MDT [ns]

DT [ns]

300 0

250 -25

DT1

DT2

200 -50

-40 -20 0 20 40 60 80 100 120 -40 -20 0 20 40 60 80 100 120

Temperature [°C] Temperature [°C]

Figure 10. Dead Time vs. Temperature Figure 11.Dead-Time Matching vs. Temperature

50 -7

40

-8

30

Delay Matching [ns]

20

-9

10

VS [V]

0 -10

-10

-11

-20

-30

MTON -12

-40 MTOFF

-50 -13

-40 -20 0 20 40 60 80 100 120 -40 -20 0 20 40 60 80 100 120

Temperature [°C] Temperature [°C]

Figure 12. Delay Matching vs. Temperature Figure 13.Allowable Negative VS Voltage

vs. Temperature

400 100

350

80

300

IQBS [μA]

IQDD [μA]

60

250

200

40

150

20

100

50 0

-40 -20 0 20 40 60 80 100 120 -40 -20 0 20 40 60 80 100 120

Temperature [°C] Temperature [°C]

Figure 14. Quiescent VDD Supply Current Figure 15. Quiescent VBS Supply Current

vs. Temperature vs. Temperature

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3 8

FAN7389 — 3-Phase Half-Bridge Gate-Drive IC

Typical Characteristics (Continued)

700 700

600 600

500 500

IPBS [μA]

IPDD [μA]

400 400

300 300

200 200

100 100

-40 -20 0 20 40 60 80 100 120 -40 -20 0 20 40 60 80 100 120

Temperature [°C] Temperature [°C]

Figure 16. Operating VDD Supply Current Figure 17.Operating VBS Supply Current

vs. Temperature vs. Temperature

9.5 9.5

9.0

9.0

8.5

VDDUV- [V]

VDDUV+ [V]

8.5 8.0

7.5

8.0

7.0

7.5 6.5

-40 -20 0 20 40 60 80 100 120 -40 -20 0 20 40 60 80 100 120

Temperature [°C] Temperature [°C]

Figure 18. VDD UVLO+ vs. Temperature Figure 19.VDD UVLO- vs. Temperature

9.5 9.0

9.0 8.5

VBSUV+ [V]

VBSUV- [V]

8.5 8.0

8.0 7.5

7.5 7.0

-40 -20 0 20 40 60 80 100 120 -40 -20 0 20 40 60 80 100 120

Temperature [°C] Temperature [°C]

Figure 20. VBS UVLO+ vs. Temperature Figure 21.VBS UVLO- vs. Temperature

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3 9

FAN7389 — 3-Phase Half-Bridge Gate-Drive IC

Typical Characteristics (Continued)

100 100

High-Side High-Side

Low-Side Low-Side

80 80

VOH [mV]

VOL [mV]

60 60

40 40

20 20

0 0

-40 -20 0 20 40 60 80 100 120 -40 -20 0 20 40 60 80 100 120

Temperature [°C] Temperature [°C]

Figure 22. High-Level Output Voltage vs. Temperature Figure 23.Low-Level Output Voltage vs. Temperature

3.0 3.0

2.5

2.5

VIL [V]

VIH [V]

2.0

2.0

1.5

1.5

1.0

1.0 0.5

-40 -20 0 20 40 60 80 100 120 -40 -20 0 20 40 60 80 100 120

Temperature [°C] Temperature [°C]

Figure 24. Logic HIGH Input Voltage vs. Temperature Figure 25.Logic LOW Input Voltage vs. Temperature

160 2.0

140

1.5

IIN+ [μA]

IIN- [μA]

120

1.0

100

0.5

80

60 0.0

-40 -20 0 20 40 60 80 100 120 -40 -20 0 20 40 60 80 100 120

Temperature [°C] Temperature [°C]

Figure 26. Logic Input HIGH Bias Current Figure 27.Logic Input LOW Bias Current

vs. Temperature vs. Temperature

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3 10

FAN7389 — 3-Phase Half-Bridge Gate-Drive IC

Typical Characteristics (Continued)

100 200

80 180

REN [KΩ]

RIN [KΩ]

60 160

40 140

20 120

0 100

10 12 14 16 18 20 10 12 14 16 18 20

Supply Voltage [V] Supply Voltage [V]

Figure 28. Input Pull-Down Resistance Figure 29.Enable Pin Pull-Down Resistance

vs. Supply Voltage vs. Supply Voltage

400 100

350

80

300

IQBS [μA]

IQDD [μA]

250 60

200 40

150

20

100

50 0

10 12 14 16 18 20 10 12 14 16 18 20

Supply Voltage [V] Supply Voltage [V]

Figure 30. Quiescent VDD Supply Current Figure 31.Quiescent VBS Supply Current

vs. Supply Voltage vs. Supply Voltage

700 700

600 600

500 500

IPDD [μA]

IPBS [μA]

400 400

300 300

200 200

100 100

10 12 14 16 18 20 10 12 14 16 18 20

Supply Voltage [V] Supply Voltage [V]

Figure 32. Operating VDD Supply Current Figure 33.Operating VBS Supply Current

vs. Supply Voltage vs. Supply Voltage

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3 11

FAN7389 — 3-Phase Half-Bridge Gate-Drive IC

Switching Time Definitions

Figure 34. Switching Time Waveform Definitions

Figure 35. Input / Output Timing Diagram

Figure 36. Detailed View of B and C Intervals During Over-Current Protection

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3 12

FAN7389 — 3-Phase Half-Bridge Gate-Drive IC

Applications Information

1. Dead Time 2.2 Shoot-Through Protection

The shoot-through protection circuitry prevents both

Dead time is automatically inserted whenever the dead

high- and low-side switches from conducting at the

time of the external two input signals (between HINx

same time, as shown Figure 39.

and LINx signals) is shorter than internal fixed dead

times (DT1 and DT2). Otherwise, external dead times

larger than internal dead times are not modified by the

gate driver and internal dead-time waveform definition is

shown in Figure 37.

Figure 37. Internal Dead-Time Definitions

2. Protection Function

2.1 Fault Out ( FO ) and Under-Voltage Lockout

The high- and low-side drivers include under-voltage

lockout (UVLO) protection circuitry that monitors the

supply voltage for VDD and VBS independently. It can be

designed to prevent malfunction when VDD and VBS are

lower than the specified threshold voltage. Also, the

UVLO hysteresis prevents chattering during power-

supply transitions. Moreover, the fault signal ( FO ) goes

to LOW state to operate reliably during power-on

events, when the power supply (VDD) is below the

under-voltage lockout high threshold voltage for the

circuit (during t1 ~ t2). The UVLO circuit is not otherwise

activated; shown Figure 38.

Figure 39. Shoot-Through Protection

2.3 Enable Input

When the EN pin is in HIGH state, the gate driver

operates normally. When a condition occurs that should

shut down the gate driver, the EN pin should be LOW.

The enable circuitry has an input filter; the minimum

input duration is specified by tFLTIN (typically 250 ns).

Figure 38. Waveforms for Under-Voltage Lockout

Figure 40. Output Enable Timing Waveform

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3 13

FAN7389 — 3-Phase Half-Bridge Gate Driver IC

2.4 Fault-Out ( FO ) and Over-Current Protection

FAN7389 provides an integrated fault output ( FO ) and

an adjustable fault-clear timer (tFLTCLR). There are two

situations that cause the gate driver to report a fault via

the FO pin. The first is an under-voltage condition of

low-side gate driver supply voltage (VDD) and the

second is when the current-sense pin (CS) recognizes a

fault. Once the fault condition occurs, the FO pin is

internally pulled to COM, the fault-clear timer is

activated, and all outputs (HO1,2,3 and LO1,2,3) of the

gate driver are turned off. The fault output stays LOW

until the fault condition has been removed and the fault-

clear timer expires. Once the fault-clear timer expires,

the voltage on the FO pin returns to pull-up voltage.

The fault-clear time (tFLTCLR) is determined by an internal

current source (IRCIN=5 μA) and an external CRCIN at the

RCIN pin, as shown in this equation:

Figure 42. RCIN and Fault-Clear Waveform Definition

C RCIN × VRCIN ,TH

t FLTCLR = [s ] (1) 2.5 Recommended RCIN

I RCIN Figure 43 shows timing of tCSOFF and tCSFO versus CRCIN.

It is strongly recommended that the capacitor on RCIN

The RDSRCIN of the MOSFET is a characteristic pin should be less than 5 nF in order to properly protect

discharge curve with respect to the external capacitor power devices in over-current situations.

CRCIN. The time constant is defined by the external

capacitor CRCIN and the RDSRCIN of the MOSFET. 1200

The output of current-sense comparator (CS_COMP) 1100

passes a noise filter, which inhibits an over-current 1000

shutdown caused by parasitic voltage spikes of VCS. 900

This corresponds to a voltage level at the comparator of 800

Time [ns]

VCSTH+ - VCSHYS= 500 mV - 60 mV =440 mV, 700

where VCSHYS=60 mV is the hysteresis of the current 600

comparator (CS_COMP) as shown in Figure 41.

500

tCSOFF

400

tCSFO

300

200

0 1 2 3 4 5 6 7 8 9 10 11 12

CRCIN [nF]

Figure 43. Timing of tCSOFF and tCSFO vs. CRCIN

Figure 41. Over-Current Protection 3. Noise Filter

3.1 Input Noise Filter

Figure 42 shows the waveform definitions of RCIN, FO

Figure 44 shows the input noise filter method, which has

and the low-side driver, which uses a soft turn-off symmetry duration between the input signal (tINPUT) and

method when an under-voltage condition of the low-side the output signal (tOUTPUT) and helps to reject noise

gate driver supply voltage (VDD) or the current-sense pin spikes and short pulses. This input filter is applied to the

(CS) recognizes a fault. Once a fault condition occurs, HINx, LINx, and EN inputs. The upper pair of waveforms

the FO pin is internally pulled to COM and all outputs (Example A) shows an input signal duration (tINPUT)

(HO1,2,3 and LO1,2,3) of the gate driver are turned off. much longer than input filter time (tFLTIN); it is

Low-side outputs decline linearly by the internal sink approximately the same duration between the input

current source (ISOFT=40 mA) for soft turn-off, as shown signal time (tINPUT) and the output signal time (tOUTPUT).

in Figure 42. The lower pair of waveforms (Example B) shows an

input signal time (tINPUT) slightly longer than input filter

time (tFLTIN); it is approximately the same duration

between input signal time (tINPUT) and the output signal

time (tOUTPUT).

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3 14

FAN7389 — 3-Phase Half-Bridge Gate Driver IC

Example A Figure 46 shows the characteristics of the input filters

INx tFLTIN

while receiving narrow ON and OFF pulses. If input

signal pulse duration, PWIN, is less than input filter time,

tINPUT

tFLTIN; the output pulse, PWOUT, is zero. The input signal

is rejected by input filter. Once the input signal pulse

tOUTPUT

duration, PWIN, exceeds input filter time, tFLTIN, the

output pulse durations, PWOUT, matches the input pulse

OUTx

durations, PWIN. FAN7389 input filter time, tFLTIN, is

about 250 ns for the high- and low-side outputs.

INx tFLTIN

Example B

tINPUT

tOUTPUT

Output duration is

same as input duration

OUTx

Figure 44. Input Noise Filter Definition

3.2. Short-Pulsed Input Noise Rejection Method

The input filter circuitry provides protection against

short-pulsed input signals (HINx, LINx, and EN) on the

input signal lines by applied noise signal.

If the input signal duration is less than input filter time

(tFLTIN), the output does not change states.

Example A and B of the Figure 45 show the input and

output waveforms with short-pulsed noise spikes with a

duration less than input filter time; the output does not Figure 46. Input Filter Characteristic of Narrow ON

change states.

Figure 45. Noise Rejecting Input Filter Definition

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3 15

FAN7389 — 3-Phase Half-Bridge Gate Driver IC

Package Dimensions

Figure 47. 28-Lead Small Outline Integrated Circuit (28-Wide Body SOIC)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifically the

warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/.

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3 16

FAN7389 — 3-Phase Half-Bridge Gate Driver IC

© 2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7389 • Rev. 1.0.3 17

You might also like

- Physics Project - Report On Logic GatesDocument25 pagesPhysics Project - Report On Logic GatesMAINAK MUKHERJEE88% (16)

- Logic Level Converter TXS0108EDocument16 pagesLogic Level Converter TXS0108ELuis TapiaNo ratings yet

- Batch-4 (B) - IR2110 Based Square Wave Inverter Using 555 TimerDocument37 pagesBatch-4 (B) - IR2110 Based Square Wave Inverter Using 555 TimerКети ТаневскаNo ratings yet

- Lm53603-Q1 (3 A), Lm53602-Q1 (2 A) 3.5 V To 36 V Wide-V Synchronous 2.1 MHZ Step-Down Converters For Automotive ApplicationsDocument42 pagesLm53603-Q1 (3 A), Lm53602-Q1 (2 A) 3.5 V To 36 V Wide-V Synchronous 2.1 MHZ Step-Down Converters For Automotive ApplicationsLuis Antonio Rosales TejadaNo ratings yet

- Analog Circuit Design Volume Three: Design Note CollectionFrom EverandAnalog Circuit Design Volume Three: Design Note CollectionRating: 3 out of 5 stars3/5 (2)

- STLD Lab Manual R19Document40 pagesSTLD Lab Manual R19RockRahil100% (3)

- VLSI Design - Lecture Notes, Study Material and Important Questions, AnswersDocument9 pagesVLSI Design - Lecture Notes, Study Material and Important Questions, AnswersM.V. TVNo ratings yet

- Fan 73892Document20 pagesFan 73892heribertosfaNo ratings yet

- Is Now Part ofDocument18 pagesIs Now Part ofSOLUCIÓN ELECTRÓNICANo ratings yet

- FAN73892 3-Phase Half-Bridge Gate-Drive IC: Features DescriptionDocument17 pagesFAN73892 3-Phase Half-Bridge Gate-Drive IC: Features DescriptionAugusto PereiraNo ratings yet

- Control Integrated Power System (Cipos™) Igcm04G60Ha: DatasheetDocument16 pagesControl Integrated Power System (Cipos™) Igcm04G60Ha: DatasheetNur ArifinNo ratings yet

- Control Integrated Power System (Cipos™) Ikcm15F60Ga: DatasheetDocument16 pagesControl Integrated Power System (Cipos™) Ikcm15F60Ga: DatasheetgemnsterNo ratings yet

- LN3C63 LiemicDocument13 pagesLN3C63 Liemichichem_scribdNo ratings yet

- Ir1161lpbf - Infineon Solutions For Transportation 24V To 60VDocument25 pagesIr1161lpbf - Infineon Solutions For Transportation 24V To 60VAnonymous R0s4q9X8No ratings yet

- FAN7392 High-Current, High-And Low-Side, Gate-Drive IC: Features DescriptionDocument18 pagesFAN7392 High-Current, High-And Low-Side, Gate-Drive IC: Features DescriptionRaghu RamanNo ratings yet

- FSBF 15CH60BT F50Document17 pagesFSBF 15CH60BT F50José SilvaNo ratings yet

- FSBB30CH60C D-1810022Document17 pagesFSBB30CH60C D-1810022Flavio SilvaNo ratings yet

- IC695ALG808Document5 pagesIC695ALG808Ganesh BangarNo ratings yet

- Driver Motore Passo PassoDocument12 pagesDriver Motore Passo Passogionp1No ratings yet

- Infineon IGCM20F60GAXKMA1 DatasheetDocument16 pagesInfineon IGCM20F60GAXKMA1 DatasheetJohn Delgado AnchicoqueNo ratings yet

- Bimos Ii Unipolar Stepper-Motor Translator/Driver: Absolute Maximum RatingsDocument8 pagesBimos Ii Unipolar Stepper-Motor Translator/Driver: Absolute Maximum RatingsJesusNo ratings yet

- MC3479 Stepper Motor Driver: FeaturesDocument10 pagesMC3479 Stepper Motor Driver: FeaturesHenry CastandNo ratings yet

- lm53602 q1 PDFDocument42 pageslm53602 q1 PDFMiguel Scq SclNo ratings yet

- Hitachi H48 C3 Axis AccelerometerDocument6 pagesHitachi H48 C3 Axis AccelerometerGHL AdaroNo ratings yet

- WWDocument14 pagesWWbrenda2606No ratings yet

- A 3953 SBDocument14 pagesA 3953 SBAndres Uribe100% (1)

- AD5662Document24 pagesAD5662mar_barudjNo ratings yet

- R5601T Series: Lithium-Ion/ Lithium Polymer Battery Management Analog Front-EndDocument32 pagesR5601T Series: Lithium-Ion/ Lithium Polymer Battery Management Analog Front-EndBenjamin garcia buronNo ratings yet

- Skhi 23 12Document11 pagesSkhi 23 12Shaun Dwyer Van HeerdenNo ratings yet

- Lm43600 Simple Switcher 3.5 V To 36 V 0.5 A Synchronous Step-Down Voltage ConverterDocument53 pagesLm43600 Simple Switcher 3.5 V To 36 V 0.5 A Synchronous Step-Down Voltage ConverterJoseph BernardNo ratings yet

- Ad5310 PDFDocument16 pagesAd5310 PDFErasmo Franco SNo ratings yet

- AD5300Document13 pagesAD5300mm6088873No ratings yet

- Ucc 27624Document37 pagesUcc 27624jonathan.boussoir2215No ratings yet

- Analog Servo Drive: Description Power RangeDocument7 pagesAnalog Servo Drive: Description Power RangeElectromateNo ratings yet

- Advanced Three Phase PWM Inverter ControDocument8 pagesAdvanced Three Phase PWM Inverter Controbehaoszi100% (1)

- Altivar Process ATV900 - ATV930U22N4 PDFDocument13 pagesAltivar Process ATV900 - ATV930U22N4 PDFKolawolé BAKARYNo ratings yet

- Automotive FET Driver For 3 Phase BLDC Motor: FeaturesDocument49 pagesAutomotive FET Driver For 3 Phase BLDC Motor: Featuresdhaniardian.2023No ratings yet

- FNB33060T: Motion SPM 3 SeriesDocument15 pagesFNB33060T: Motion SPM 3 Seriesphetronyo ferreira de oliveiraNo ratings yet

- Low Cost Green-Power PWM Controller With Low EMI Technique FeaturesDocument12 pagesLow Cost Green-Power PWM Controller With Low EMI Technique FeaturesRogeriomgoNo ratings yet

- 3.5 A Step Down Switching Regulator: FeaturesDocument28 pages3.5 A Step Down Switching Regulator: FeaturesClaudio ClaudioNo ratings yet

- ROSANcenovnik SRB 2013BAP1950 Kontroler Trofaznog Tiristorskog MostsDocument12 pagesROSANcenovnik SRB 2013BAP1950 Kontroler Trofaznog Tiristorskog MostsAleksa GajićNo ratings yet

- Float DriveDocument24 pagesFloat DriveEdy AchalmaNo ratings yet

- E Tended Environment: Analog Servo DriveDocument8 pagesE Tended Environment: Analog Servo DriveElectromateNo ratings yet

- Altivar Process ATV900 - ATV930D75N4Document14 pagesAltivar Process ATV900 - ATV930D75N4alexis roblesNo ratings yet

- VNH7040AYTR DatasheetDocument48 pagesVNH7040AYTR DatasheetStelian CrisanNo ratings yet

- High-Power Igbt Driver Data Sheet For 2Pd632Document11 pagesHigh-Power Igbt Driver Data Sheet For 2Pd632Narendra BholeNo ratings yet

- Altair 05 TRDocument27 pagesAltair 05 TRGenivaldo CostaNo ratings yet

- Amoled Driver STMDocument23 pagesAmoled Driver STManalog changeNo ratings yet

- Ic 695 Alg 808Document5 pagesIc 695 Alg 808Zaki nouiNo ratings yet

- Modulo Sauer Danfoss S5XDocument6 pagesModulo Sauer Danfoss S5Xrmartins_23947450% (2)

- Dual-Phase DC-DC Controller For AMD Mobile CPU: Features General DescriptionDocument7 pagesDual-Phase DC-DC Controller For AMD Mobile CPU: Features General Descriptionlordycarlos8588No ratings yet

- A3979 DatasheetDocument15 pagesA3979 DatasheetИван КосмонавтNo ratings yet

- FRC Jaguar Datasheet PDFDocument16 pagesFRC Jaguar Datasheet PDFJuan de Dios Alardín HernándezNo ratings yet

- Developing Islanding Arrangement Automatically For Grid On Sensing Bad Voltage or FrequencyDocument29 pagesDeveloping Islanding Arrangement Automatically For Grid On Sensing Bad Voltage or FrequencyNitin AdamNo ratings yet

- MAX77680 Datasheet and Technical InfoDocument9 pagesMAX77680 Datasheet and Technical InfojackNo ratings yet

- Data SheetDocument49 pagesData SheetMeselao Meselao MeselaoNo ratings yet

- Altivar Process ATV600 - ATV630C25N4Document13 pagesAltivar Process ATV600 - ATV630C25N4Mikhail YudhiantaraNo ratings yet

- Altivar Machine ATV340 - ATV340D22N4Document16 pagesAltivar Machine ATV340 - ATV340D22N4PhaniNo ratings yet

- BL Installation and Configuration: 2.2.2. Motor Supply ConnectionsDocument6 pagesBL Installation and Configuration: 2.2.2. Motor Supply ConnectionsAshokNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- FNA41060 / FNA41060B2: Motion SPM 45 SeriesDocument16 pagesFNA41060 / FNA41060B2: Motion SPM 45 SeriesAmjad ShehadaNo ratings yet

- PS21353-N 2 PDFDocument10 pagesPS21353-N 2 PDFAmjad ShehadaNo ratings yet

- PS21353-N 2 PDFDocument10 pagesPS21353-N 2 PDFAmjad ShehadaNo ratings yet

- Short Form Oct-11 PDFDocument15 pagesShort Form Oct-11 PDFAmjad ShehadaNo ratings yet

- Read The Entire Specification Before You Begin Working On This Project!Document5 pagesRead The Entire Specification Before You Begin Working On This Project!Muhammad ArslanNo ratings yet

- Chapter Five: Analysis and Synthesis of Combinational Logic CircuitsDocument38 pagesChapter Five: Analysis and Synthesis of Combinational Logic Circuitsewnetu kassaNo ratings yet

- Integrated Circuits Lecture NotesDocument9 pagesIntegrated Circuits Lecture NotesJoanna Fabricante100% (1)

- Quantum III PDFDocument252 pagesQuantum III PDFCesarNo ratings yet

- Obe Curriculum For The Course: RGPV (Diploma Wing) BhopalDocument22 pagesObe Curriculum For The Course: RGPV (Diploma Wing) Bhopalकिशोरी जूNo ratings yet

- WHOLEDEDocument91 pagesWHOLEDEDinesh PalavalasaNo ratings yet

- CS-301 Computer Systems: Course GoalsDocument7 pagesCS-301 Computer Systems: Course Goalsshumaila akramNo ratings yet

- Digital Fundamentals: With PLD ProgrammingDocument29 pagesDigital Fundamentals: With PLD ProgrammingNeslynNo ratings yet

- Course Outline (CSE-1101)Document4 pagesCourse Outline (CSE-1101)Mali PikNo ratings yet

- Module - 5 Introduction To VHDL 5.1: ObjectivesDocument14 pagesModule - 5 Introduction To VHDL 5.1: Objectivesabhilash gowdaNo ratings yet

- Shivani RepDocument43 pagesShivani RepShivani ChauhanNo ratings yet

- Pon Vidyashram Group of Schools: Chapter - 3 Boolean LogicDocument16 pagesPon Vidyashram Group of Schools: Chapter - 3 Boolean LogicADSaksoulNo ratings yet

- (Ebook pdf) Introduction to Computing Systems: From Bits & Gates to C & Beyond 3rd Edition Yale Patt - eBook PDF all chapterDocument69 pages(Ebook pdf) Introduction to Computing Systems: From Bits & Gates to C & Beyond 3rd Edition Yale Patt - eBook PDF all chapterweinskopolo12100% (4)

- Ee6311 Ldic Lab Manual 2013 RegulationDocument66 pagesEe6311 Ldic Lab Manual 2013 RegulationsujathaNo ratings yet

- Chapter Six: Standard Boolean Expression FormatsDocument16 pagesChapter Six: Standard Boolean Expression FormatsSUDHEER100% (1)

- Electronic Symbol - WDocument53 pagesElectronic Symbol - Waditya00012100% (1)

- CDLU BCA Syllabi New1324Document11 pagesCDLU BCA Syllabi New1324Baljinder KambojNo ratings yet

- Digital Electronics & MicroprocessorsDocument152 pagesDigital Electronics & MicroprocessorsAnonymous FRJktAGZmNo ratings yet

- Final Syll For WebsiteDocument169 pagesFinal Syll For WebsitegcdeshpandeNo ratings yet

- Half Adder and Full AdderDocument16 pagesHalf Adder and Full AdderkusumNo ratings yet

- Ece 2003Document3 pagesEce 2003gokulNo ratings yet

- Porta Lógica XORDocument7 pagesPorta Lógica XORLuiz BitencourtNo ratings yet

- Dec3033 Computer Architecture and Organization - SDocument7 pagesDec3033 Computer Architecture and Organization - Skshika meganathanNo ratings yet

- Warmly Welcome From My PresentationDocument59 pagesWarmly Welcome From My PresentationPrinces Ofattacker100% (4)

- BSC Comp SC - CBCSS Syllabus PDFDocument42 pagesBSC Comp SC - CBCSS Syllabus PDFSooraj krishnan v.sNo ratings yet

- 1.0 Computer System 2021 - 2022 StudentsDocument145 pages1.0 Computer System 2021 - 2022 Studentsnurain syuhadaNo ratings yet