Professional Documents

Culture Documents

Lab#2 (3x8 Decoder Using Gate Level and Data Flow Abstraction) Objectives

Lab#2 (3x8 Decoder Using Gate Level and Data Flow Abstraction) Objectives

Uploaded by

Amina TabassumOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lab#2 (3x8 Decoder Using Gate Level and Data Flow Abstraction) Objectives

Lab#2 (3x8 Decoder Using Gate Level and Data Flow Abstraction) Objectives

Uploaded by

Amina TabassumCopyright:

Available Formats

Lab#2

(3x8 Decoder using Gate Level and Data flow Abstraction)

Objectives:

“Design and verification of 2x4 & 3x8 Decoder using Gate Level and Data flow Abstraction in

ModelSim”

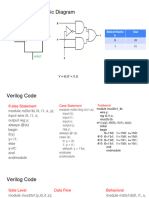

Decoder 2x4 using Gates Level

module decoder2x4 (O, S, E);

input[1:0] S; input E;

output[3:0] O;

wire w1, w2;

not (w1, S[1]);

not (w2, S[0]);

and (O[3], S[1],S[0],E);

and (O[2], S[1],w2,E);

and (O[1], w1,S[0],E);

and (O[0], w1,w2,E);

endmodule

module t_decoder2x4;

reg[1:0] S;

reg E;

wire[3:0] O;

decoder2x4 d1(O, S, E);

initial begin

S=2'b0; E=1'b1;

repeat(4)

#100 S=(S+2'b01);

#100 $finnish;

end

endmodule

Figure 1 2x4 decoder output

Decoder 3x8 using Gates Level

module decoder3x8(O,S);

input[2:0] S;

output[7:0] O;

wire w1;

not (w1, S[2]);

decoder2x4 d1(.O(O[3:0]), .S(S[1:0]), .E(w1));

decoder2x4 d0(.O(O[7:4]), .S(S[1:0]), .E(S[2]));

endmodule

module t_decoder3x8;

reg[2:0] S;

wire[7:0] O;

decoder3x8 d1(O,S);

initial begin

S=3'b0;

repeat(8)

#100 S=(S+3'b001);

#100 $finnish;

end

endmodule

Figure 2 3x8 Decoder output

Decoder 2x4 using Dataflow Abstraction

module decoder2x4_dataflow(O,E,S);

input[1:0] S; input E;

output[3:0] O;

assign O[0] = (~S[0] & ~S[1] & E);

assign O[1] = (S[0] & ~S[1] & E);

assign O[2] = (~S[0] & S[1] & E);

assign O[3] = (S[0] & S[1] & E);

endmodule

module t_decoder2x4_df;

reg[1:0] S; reg E;

wire[3:0] O;

decoder2x4_dataflow d1(O, E, S);

initial begin

S=2'b0; E=1'b1;

repeat(4)

#100 S=(S+2'b01);

#100 $finnish;

Figure 3 2x4 decoder output

Decoder 3x8 using Dataflow Abstraction

module decoder3x8_dataflow(O,S);

input[2:0] S;

output[7:0] O;

assign w1 = ~S[2];

decoder2x4_dataflow d1(.O(O[3:0]), .S(S[1:0]), .E(w1));

decoder2x4_dataflow d2(.O(O[7:4]), .S(S[1:0]), .E(S[2]));

endmodule

end

endmodule

module t_decoder3x8_df;

reg[2:0] S;

wire[7:0] O;

decoder3x8_dataflow d1(O,S);

initial begin

S=3'b0;

repeat(8)

#100 S=(S+1'b1);

#100 $finnish;

end

endmodule

Figure 4 3x8 Decoder output

You might also like

- HDL Verilog Programs Vtu 5th SemDocument12 pagesHDL Verilog Programs Vtu 5th SemNikhil KulkarniNo ratings yet

- 23ucc597 Asgn 4Document6 pages23ucc597 Asgn 423ucc597No ratings yet

- Buffer1 E23cseu2200 DDDocument7 pagesBuffer1 E23cseu2200 DDchipichipichapachapa2121No ratings yet

- Sonam Saini Assignment 4Document12 pagesSonam Saini Assignment 4sonams.ec.21No ratings yet

- Deber 3Document9 pagesDeber 3Ale ZamNo ratings yet

- Lab TaskDocument14 pagesLab TaskravinderNo ratings yet

- Experiment 4Document8 pagesExperiment 4Himanshu Rajan jainNo ratings yet

- A) Specify The Size of The Output (O) in Bits So The Overflow Can Never OccurDocument21 pagesA) Specify The Size of The Output (O) in Bits So The Overflow Can Never OccurJLM SSNo ratings yet

- Experiment No.4: 1X2 DecoderDocument12 pagesExperiment No.4: 1X2 DecoderRohit PanwarNo ratings yet

- SUPRIYADocument19 pagesSUPRIYARebba AkhilNo ratings yet

- VLSI Design Lab EC-16203 Experiment 4 ObjectiveDocument5 pagesVLSI Design Lab EC-16203 Experiment 4 ObjectiveBrajesh SainiNo ratings yet

- 21BCT0093 VL2022230504083 Ast08Document15 pages21BCT0093 VL2022230504083 Ast08Srinivasan UmaNo ratings yet

- Experiment: 1: ObjectDocument13 pagesExperiment: 1: ObjectAjay SinghNo ratings yet

- Raport: Limbaj de Descriere HARDWAREDocument8 pagesRaport: Limbaj de Descriere HARDWARENicolaeNo ratings yet

- E23CSEU1043 Sneha Assignment 7Document7 pagesE23CSEU1043 Sneha Assignment 7chipichipichapachapa2121No ratings yet

- Mux4X1 Using Operators (Dataflow) : Test BenchDocument9 pagesMux4X1 Using Operators (Dataflow) : Test BenchAnonymous L3zAMqRlzUNo ratings yet

- FALLSEM2022-23 BECE102L TH VL2022230104585 Reference Material I 10-09-2022 Module-3 PDFDocument92 pagesFALLSEM2022-23 BECE102L TH VL2022230104585 Reference Material I 10-09-2022 Module-3 PDFChiranjeev Vishnoi 21BCT0043No ratings yet

- Vlsi Manual 1Document54 pagesVlsi Manual 1jogeorge85No ratings yet

- Coe118 Assgn Abstraction LevelDocument9 pagesCoe118 Assgn Abstraction LevelTreksha DCNo ratings yet

- DecoderDocument2 pagesDecoderelisaaslanianNo ratings yet

- F Pga Chan de AssignmentDocument38 pagesF Pga Chan de AssignmentSubbuNaiduNo ratings yet

- Displaying Text Using Dot MatrixDocument10 pagesDisplaying Text Using Dot MatrixDhenie Mae AquinoNo ratings yet

- EE214 Exp1 Report Sharvari Medhe 20D070073Document15 pagesEE214 Exp1 Report Sharvari Medhe 20D070073Sharvari MedheNo ratings yet

- Introduction To Computer ProgrammingDocument12 pagesIntroduction To Computer ProgrammingFarhan Khan NiaZiNo ratings yet

- Ver I Log ExamplesDocument22 pagesVer I Log ExamplesDayanand Gowda KrNo ratings yet

- Logic Gates: AIM: To Design Basic Logic Gates Tool Used: CodeDocument35 pagesLogic Gates: AIM: To Design Basic Logic Gates Tool Used: CodeMALVIKANo ratings yet

- 04 - Verilog Codes For Basic Components (2021f)Document78 pages04 - Verilog Codes For Basic Components (2021f)伍建瑋No ratings yet

- Lab Results VlsiDocument18 pagesLab Results Vlsipankaj rangareeNo ratings yet

- Verilog Code For Some Combinational CircuitDocument19 pagesVerilog Code For Some Combinational CircuitBeshir Nurhassen Awoll 18BML0103No ratings yet

- Experiment 4Document4 pagesExperiment 4usutkarsh0705No ratings yet

- Verilog Tips & RulesDocument37 pagesVerilog Tips & RulesSharan ChaitanyaNo ratings yet

- My First Program On D Flip FlopDocument39 pagesMy First Program On D Flip FlopAswinCvrnNo ratings yet

- Vlsi Lab Manual Exp3Document6 pagesVlsi Lab Manual Exp3Huỳnh Mạnh CườngNo ratings yet

- Verilog HDL Introduction: ECE 554 Digital Engineering LaboratoryDocument79 pagesVerilog HDL Introduction: ECE 554 Digital Engineering LaboratoryBbsn EmbeddedNo ratings yet

- Digital Hardware Design Assignment: Verilog Codes and SimulationsDocument16 pagesDigital Hardware Design Assignment: Verilog Codes and SimulationsTeja Krishna Kopuri100% (2)

- Dataflow Modelling: 1) Logic GatesDocument39 pagesDataflow Modelling: 1) Logic Gateslilly jamesNo ratings yet

- VLSI Lab Manual Exercise ProblemsDocument38 pagesVLSI Lab Manual Exercise ProblemsPrakhar Kumar100% (1)

- CSE460 Lab ReportDocument18 pagesCSE460 Lab ReportKISHANU ROY JOYNo ratings yet

- 2:4 Decoder: DECODER: A Slightly More Complex Decoder Would Be The N-To-2n Type Binary Decoders. These TypesDocument6 pages2:4 Decoder: DECODER: A Slightly More Complex Decoder Would Be The N-To-2n Type Binary Decoders. These TypesPavithraRamNo ratings yet

- VLSI Design Lab EC-16203 Experiment 5Document6 pagesVLSI Design Lab EC-16203 Experiment 5Brajesh SainiNo ratings yet

- EncoderDocument10 pagesEncoderSiva Shankar0% (1)

- Verilog SlidesDocument24 pagesVerilog SlidesDeepikaa PoobalarajaNo ratings yet

- VerilogDocument30 pagesVerilogindrajeet4saravananNo ratings yet

- Nithin AssignmentDocument36 pagesNithin Assignmentmohammadakram99gmailNo ratings yet

- Following Is The Verilog Code For A 3-Bit 1-Of-9 Priority EncoderDocument5 pagesFollowing Is The Verilog Code For A 3-Bit 1-Of-9 Priority Encoderrameshbe048030No ratings yet

- Experiment-3: Aim: Activity1 Truth TableDocument7 pagesExperiment-3: Aim: Activity1 Truth TableHimanshu Rajan jainNo ratings yet

- Hardware Description Language: - Tool For Specifying Hardware Circuits Types of HDL: - VHDL - VerilogDocument17 pagesHardware Description Language: - Tool For Specifying Hardware Circuits Types of HDL: - VHDL - Verilogاسامه صلاح الدينNo ratings yet

- LAB #04 Task #01: Implement 4X1 Mux by Calling 2x1 Mux ?Document14 pagesLAB #04 Task #01: Implement 4X1 Mux by Calling 2x1 Mux ?kiranNo ratings yet

- Demux To ALUDocument13 pagesDemux To ALUkarry4galsNo ratings yet

- Lab 5Document13 pagesLab 5SHAHZAIB AHMAD QURESHINo ratings yet

- Department of Electronics & Communication Engineering: HDL Laboratory (18ecl58) Experiment No - 1Document8 pagesDepartment of Electronics & Communication Engineering: HDL Laboratory (18ecl58) Experiment No - 1mahalakshmim612No ratings yet

- Verilog - Mux, Demux, Encoder, DecoderDocument9 pagesVerilog - Mux, Demux, Encoder, Decoderavinashmasani7No ratings yet

- Digital Logic Design: Assignment# 3Document8 pagesDigital Logic Design: Assignment# 3Zojaan AheerNo ratings yet

- 21-CP-6 (Report13) DLDDocument11 pages21-CP-6 (Report13) DLDAlmaas ChaudryNo ratings yet

- Sample Eda Lab (Part-A) Manual: Simulation OutputDocument20 pagesSample Eda Lab (Part-A) Manual: Simulation Outputmdzakir_hussainNo ratings yet

- Verilog Code For Fir FilterDocument58 pagesVerilog Code For Fir FilterKishore KumarNo ratings yet

- HDL (Repaired)Document104 pagesHDL (Repaired)Vikas PakhretiaNo ratings yet

- Batch 2 SolutionDocument2 pagesBatch 2 SolutionJeswin EldhoNo ratings yet

- PAM 361 Eng. Comp. MethodsDocument4 pagesPAM 361 Eng. Comp. MethodsAmina TabassumNo ratings yet

- R-K Method MATLAB CodeDocument2 pagesR-K Method MATLAB CodeAmina TabassumNo ratings yet

- Name: Masood Salik BSEE-14-18 Convergence / Existence of DTFT and Gibbs PhenomenonDocument5 pagesName: Masood Salik BSEE-14-18 Convergence / Existence of DTFT and Gibbs PhenomenonAmina TabassumNo ratings yet

- Hw2ans PDFDocument3 pagesHw2ans PDFAmina TabassumNo ratings yet