Professional Documents

Culture Documents

N-Channel 600 V, 0.255 Ω Typ., 13 A Mdmesh M2 Power Mosfet In A To-220Fp Package

N-Channel 600 V, 0.255 Ω Typ., 13 A Mdmesh M2 Power Mosfet In A To-220Fp Package

Uploaded by

Erasmo Franco SOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

N-Channel 600 V, 0.255 Ω Typ., 13 A Mdmesh M2 Power Mosfet In A To-220Fp Package

N-Channel 600 V, 0.255 Ω Typ., 13 A Mdmesh M2 Power Mosfet In A To-220Fp Package

Uploaded by

Erasmo Franco SCopyright:

Available Formats

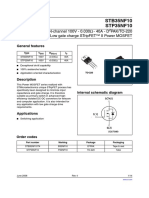

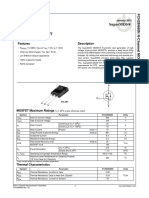

STF18N60M2

Datasheet

N-channel 600 V, 0.255 Ω typ., 13 A MDmesh M2

Power MOSFET in a TO-220FP package

Features

Order code VDS @TJmax RDS(on) max. ID

STF18N60M2 650 V 0.280 Ω 13 A

• Extremely low gate charge

3 • Excellent output capacitance (COSS) profile

2

1

• 100% avalanche tested

TO-220FP • Zener-protected

D(2)

Applications

• Switching applications

• LCC converters

G(1)

• Resonant converters

Description

This device is an N-channel Power MOSFET developed using MDmesh M2

S(3) AM15572v1_no_tab

technology. Thanks to its strip layout and an improved vertical structure, the device

exhibits low on-resistance and optimized switching characteristics, rendering it

suitable for the most demanding high efficiency converters.

Product status link

STF18N60M2

Product summary

Order code STF18N60M2

Marking 18N60M2

Package TO-220FP

Packing Tube

DS9710 - Rev 4 - June 2019 www.st.com

For further information contact your local STMicroelectronics sales office.

STF18N60M2

Electrical ratings

1 Electrical ratings

Table 1. Absolute maximum ratings

Symbol Parameter Value Unit

VGS Gate-source voltage ±25 V

Drain current (continuous) at TC = 25 °C 13 A

ID (1)

Drain current (continuous) at TC = 100 °C 8 A

IDM (2)

Drain current (pulsed) 52 A

PTOT Total power dissipation at TC = 25 °C 25 W

dv/dt (3) Peak diode recovery voltage slope 15 V/ns

dv/dt (4) MOSFET dv/dt ruggedness 50 V/ns

Insulation withstand voltage (RMS) from all three leads to external heat

VISO 2.5 kV

sink (t = 1 s; TC = 25 °C)

Tstg Storage temperature range

-55 to 150 °C

Tj Operating junction temperature range

1. Limited by maximum junction temperature.

2. Pulse width limited by safe operating area.

3. ISD ≤ 13 A, di/dt ≤ 400 A/µs; VDS(peak) < V(BR)DSS, VDD = 400 V

4. VDS ≤ 480 V

Table 2. Thermal data

Symbol Parameter Value Unit

Rthj-case Thermal resistance junction-case 5 °C/W

Rthj-amb Thermal resistance junction-ambient 62.5 °C/W

Table 3. Avalanche characteristics

Symbol Parameter Value Unit

Avalanche current, repetitive or not repetitive

IAR 3 A

(pulse width limited by Tjmax)

EAS Single pulse avalanche energy (starting Tj=25 °C, ID= IAR, VDD=50 V) 135 mJ

DS9710 - Rev 4 page 2/12

STF18N60M2

Electrical characteristics

2 Electrical characteristics

(TC = 25 °C unless otherwise specified).

Table 4. On /off states

Symbol Parameter Test conditions Min. Typ. Max. Unit

Drain-source breakdown

V(BR)DSS ID = 1 mA, VGS = 0 V 600 V

voltage

VGS = 0 V, VDS = 600 V 1 µA

Zero gate voltage

IDSS VGS = 0 V, VDS = 600 V,

drain current 100 µA

TC = 125 °C (1)

Gate-body leakage

IGSS VDS = 0 V, VGS = ± 25 V ±10 µA

current

VGS(th) Gate threshold voltage VDS = VGS, ID = 250 µA 2 3 4 V

Static drain-source

RDS(on) VGS = 10 V, ID = 6.5 A 0.255 0.280 Ω

on-resistance

1. Defined by design, not subject to production test.

Table 5. Dynamic

Symbol Parameter Test conditions Min. Typ. Max. Unit

Ciss Input capacitance - 791 - pF

VDS = 100 V, f = 1 MHz,

Coss Output capacitance - 40 - pF

VGS = 0 V

Crss Reverse transfer capacitance - 1.3 - pF

Coss eq. (1) Equivalent output capacitance VDS = 0 to 480 V, VGS = 0 V - 164.5 - pF

RG Intrinsic gate resistance f = 1 MHz, ID = 0 A - 5.6 - Ω

Qg Total gate charge VDD = 480 V, ID = 13 A, - 21.5 - nC

Qgs Gate-source charge VGS = 0 to 10 V (see - 3.2 - nC

Figure 14. Test circuit for gate

Qgd Gate-drain charge charge behavior) - 11.3 - nC

1. Coss eq. is defined as a constant equivalent capacitance giving the same charging time as Coss when VDS increases from 0

to 80% VDSS.

Table 6. Switching times

Symbol Parameter Test conditions Min. Typ. Max. Unit

td(on) Turn-on delay time VDD = 300 V, ID = 6.5 A, - 12 - ns

tr Rise time RG = 4.7 Ω, VGS = 10 V - 9 - ns

td(off) Turn-off delay time (see Figure 13. Test circuit for - 47 - ns

resistive load switching times

and Figure 18. Switching time

tf Fall time - 10.6 - ns

waveform)

DS9710 - Rev 4 page 3/12

STF18N60M2

Electrical characteristics

Table 7. Source-drain diode

Symbol Parameter Test conditions Min. Typ. Max. Unit

ISD Source-drain current - 13 A

ISDM (1) Source-drain current (pulsed) - 52 A

VSD (2) Forward on voltage ISD = 13 A, VGS = 0 V - 1.6 V

trr Reverse recovery time ISD = 13 A, di/dt = 100 A/µs - 305 ns

Qrr Reverse recovery charge VDD = 60 V (see - 3.3 µC

Figure 15. Test circuit for

IRRM Reverse recovery current inductive load switching and - 22 A

diode recovery times)

trr Reverse recovery time ISD = 13 A, di/dt = 100 A/µs - 417 ns

Qrr Reverse recovery charge VDD = 60 V, Tj = 150 °C - 4.6 µC

(see Figure 15. Test circuit for

IRRM Reverse recovery current inductive load switching and - 22 A

diode recovery times)

1. Pulse width limited by safe operating area.

2. Pulsed: pulse duration = 300 μs, duty cycle 1.5%.

DS9710 - Rev 4 page 4/12

STF18N60M2

Electrical characteristics (curves)

2.1 Electrical characteristics (curves)

Figure 1. Safe operating area Figure 2. Thermal impedance

AM15834v1

ID K GC20940

(A)

10 s

ai

re on)

si a DS(

th R 10 -1

in ax 10µs

n

it o by m

ra

pe ed

1 O imit

L 100µs

1ms

10 -2

Tj=150°C 10ms

0.1

Tc=25°C

Single

pulse

0.01 10 -3

0.1 1 10 100 VDS(V) 10 -4 10 -3 10 -2 10 -1 10 0 t p (s)

Figure 3. Output characteristics Figure 4. Transfer characteristics

AM15837v1 AM15838v1

ID ID

(A) VGS=7, 8, 9, 10V (A) VDS = 18V

30 30

25 25

6V

20 20

15 15

10 10

5V

5 5

4V

0 0

0 5 10 15 20 VDS(V) 0 2 4 6 8 10 VGS(V)

Figure 5. Gate charge vs gate-source voltage Figure 6. Static drain-source on-resistance

AM15839v1 AM15840v1

VGS VDS RDS(on)

(V) (V) (Ω)

VDS VGS=10V

12 0.270

VDD = 480 V 500

ID = 13 A

10

400 0.265

8

300 0.260

6

200 0.255

4

2 100 0.250

0 0 0.245

0 5 10 15 20 25 Qg (nC) 0 2 4 6 8 10 12 ID(A)

DS9710 - Rev 4 page 5/12

STF18N60M2

Electrical characteristics (curves)

Figure 8. Normalized gate threshold voltage vs.

Figure 7. Capacitance variations

temperature

AM15841v1

C

VGS(th) GIPG070815BQ6KLVTH

(pF)

(norm.)

ID = 250 µA

1.1

1000

Ciss

1.0

100

0.9

Coss

0.8

10

0.7

1 Crss

0.1 1 10 100 VDS (V) 0.6

-75 -25 25 75 125 TJ (°C)

Figure 9. Normalized on-resistance vs temperature Figure 10. Source-drain diode forward characteristics

AM15842v1

RDS(on) GIPG070815BQ6KLRON

VSD(V)

(norm.)

VGS = 10 V 1.4

2.4

1.2

2.0 TJ=-50°C

1.0

1.6

0.8

1.2

0.6 TJ=25°C

TJ=150°C

0.8 0.4

0.4 0.2

0.0 0.0

-75 -25 25 75 125 TJ (°C) 0 2 4 6 8 10 12 ISD(A)

Figure 11. Normalized V(BR)DSS vs temperature Figure 12. Output capacitance stored energy

AM15843v1

V(BR)DSS GIPG070815BQ6KLBDV Eoss

(norm.) (µJ)

ID = 1 mA

1.12 6

1.08 5

1.04 4

1.00 3

0.96 2

1

0.92

0.88 0

-75 -25 25 75 125 TJ (°C) 0 100 200 300 400 500 600 VDS (V)

DS9710 - Rev 4 page 6/12

STF18N60M2

Test circuits

3 Test circuits

Figure 13. Test circuit for resistive load switching times Figure 14. Test circuit for gate charge behavior

VDD

12 V 47 kΩ

1 kΩ

100 nF

RL

2200 3.3

+ μF μF VDD

VD IG= CONST

VGS 100 Ω D.U.T.

VGS

RG D.U.T. pulse width +

2.7 kΩ

2200 VG

pulse width μF

47 kΩ

1 kΩ

AM01468v1 AM01469v1

Figure 15. Test circuit for inductive load switching and

Figure 16. Unclamped inductive load test circuit

diode recovery times

A A A L

D VD

fast 100 µH

G D.U.T. diode 2200 3.3

S B 3.3 1000 + µF µF VDD

B B

25 Ω D

µF + µF VDD ID

G D.U.T.

+ RG S

Vi D.U.T.

_

pulse width

AM01471v1

AM01470v1

Figure 18. Switching time waveform

Figure 17. Unclamped inductive waveform

ton toff

V(BR)DSS

td(on) tr td(off) tf

VD

90% 90%

IDM

10% VDS 10%

ID 0

VDD VDD VGS 90%

0 10%

AM01472v1

AM01473v1

DS9710 - Rev 4 page 7/12

STF18N60M2

Package information

4 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages,

depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product

status are available at: www.st.com. ECOPACK is an ST trademark.

4.1 TO-220FP package information

Figure 19. TO-220FP package outline

7012510_Rev_13_B

DS9710 - Rev 4 page 8/12

STF18N60M2

TO-220FP package information

Table 8. TO-220FP package mechanical data

mm

Dim.

Min. Typ. Max.

A 4.40 4.60

B 2.50 2.70

D 2.50 2.75

E 0.45 0.70

F 0.75 1.00

F1 1.15 1.70

F2 1.15 1.70

G 4.95 5.20

G1 2.40 2.70

H 10.00 10.40

L2 16.00

L3 28.60 30.60

L4 9.80 10.60

L5 2.90 3.60

L6 15.90 16.40

L7 9.00 9.30

Dia 3.00 3.20

DS9710 - Rev 4 page 9/12

STF18N60M2

Revision history

Table 9. Document revision history

Date Revision Changes

04-Jun-2013 1 First release.

– Added: note 2 in Table 2

– Modified: typical value for Ciss, Coss eq., Qg, Qgs, Qgd

05-Jun-2013 2

– Modified: Figure 10 and 11

– Minor text changes

– Modified: note 1 in Table 2

28-Feb-2014 3 – Rthj-case value in Table 3

– Minor text changes

Modified Figure 8. Normalized gate threshold voltage vs. temperature,

Figure 9. Normalized on-resistance vs temperature and Figure 11. Normalized

19-Jun-2019 4 V(BR)DSS vs temperature.

Minor text changes.

DS9710 - Rev 4 page 10/12

STF18N60M2

Contents

Contents

1 Electrical ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

2 Electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.1 Electrical characteristics (curves) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3 Test circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

4 Package information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

4.1 TO-220FP package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

DS9710 - Rev 4 page 11/12

STF18N60M2

IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST

products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST

products are sold pursuant to ST’s terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of

Purchasers’ products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service

names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2019 STMicroelectronics – All rights reserved

DS9710 - Rev 4 page 12/12

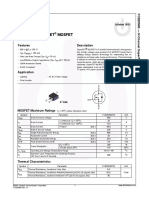

You might also like

- Lambda LQD Power Supply Repair and ModificationDocument1 pageLambda LQD Power Supply Repair and ModificationErasmo Franco SNo ratings yet

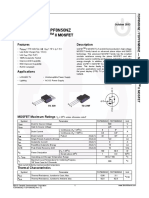

- N-Channel 650 V, 0.60 Ω Typ., 7 A Mdmesh M2 Power Mosfet In A To-220Fp PackageDocument12 pagesN-Channel 650 V, 0.60 Ω Typ., 7 A Mdmesh M2 Power Mosfet In A To-220Fp PackagejefjronNo ratings yet

- STF 13 NM 60 NDDocument12 pagesSTF 13 NM 60 NDlejojoel321No ratings yet

- STF 13 NM 60 NDocument12 pagesSTF 13 NM 60 Nrafaelmattos2015No ratings yet

- 20N60M2EP Mark STP20N60M2-EP 600V 13A FETDocument14 pages20N60M2EP Mark STP20N60M2-EP 600V 13A FETRuslanNo ratings yet

- std18nf03lDocument15 pagesstd18nf03lmhd.mousaNo ratings yet

- STD 17 NF 25Document15 pagesSTD 17 NF 25Sinon Amv'sNo ratings yet

- STF 3 NK 80 ZDocument12 pagesSTF 3 NK 80 ZGheorghe DavidNo ratings yet

- dm00128985 1798131Document13 pagesdm00128985 1798131Konstantin ИстинныйNo ratings yet

- MDP2N60/MDF2N60: N-Channel MOSFET 600V, 2.0A, 4.5Document8 pagesMDP2N60/MDF2N60: N-Channel MOSFET 600V, 2.0A, 4.5Erroz RosadiNo ratings yet

- Stp130N6F7: N-Channel 60 V, 4.2 Mω Typ., 80 A Stripfet™ F7 Power Mosfet In A To-220 PackageDocument12 pagesStp130N6F7: N-Channel 60 V, 4.2 Mω Typ., 80 A Stripfet™ F7 Power Mosfet In A To-220 PackageOsmir MonteiroNo ratings yet

- STB33N60DM2 STMicroelectronicsDocument20 pagesSTB33N60DM2 STMicroelectronicsMateus BelettiNo ratings yet

- Stn3Nf06L: N-Channel 60 V, 0.07 Ω Typ., 4 A Stripfet™ Ii Power Mosfet In A Sot-223 PackageDocument12 pagesStn3Nf06L: N-Channel 60 V, 0.07 Ω Typ., 4 A Stripfet™ Ii Power Mosfet In A Sot-223 Packageramesh sahukhalNo ratings yet

- STB12NM50T4, STP12NM50, STP12NM50FPDocument20 pagesSTB12NM50T4, STP12NM50, STP12NM50FPinformagicNo ratings yet

- Stmicroelectronics - SGST S A0007382382 1 1681241Document18 pagesStmicroelectronics - SGST S A0007382382 1 1681241MatNo ratings yet

- DatasheetDocument8 pagesDatasheetRegisk8 OliveiraNo ratings yet

- Datasheet PDFDocument15 pagesDatasheet PDFomar mijaresNo ratings yet

- STP80NF12Document12 pagesSTP80NF12vanuzalopeslopes1No ratings yet

- Stl36Dn6F7: Dual N-Channel 60 V, 23 Mω Typ., 33 A Stripfet™ F7 Power Mosfet In A Powerflat™ 5X6 Double Island PackageDocument16 pagesStl36Dn6F7: Dual N-Channel 60 V, 23 Mω Typ., 33 A Stripfet™ F7 Power Mosfet In A Powerflat™ 5X6 Double Island PackageKunal sawantNo ratings yet

- STP 16 NF 06 FPDocument14 pagesSTP 16 NF 06 FPjoverjover1No ratings yet

- stf13nm60n HDocument13 pagesstf13nm60n HMatheus Alves MendesNo ratings yet

- F10NK50Z STMicroelectronicsDocument13 pagesF10NK50Z STMicroelectronicsCandraBuanaNo ratings yet

- STD3N62K3, STF3N62K3, Stu3n62k3Document27 pagesSTD3N62K3, STF3N62K3, Stu3n62k3David Alberto Lotero AlvarezNo ratings yet

- STP 5 NK 100 ZDocument15 pagesSTP 5 NK 100 ZJimmy LinaresNo ratings yet

- N-Channel 650 V, 95 Mω Typ., 24 A Mdmesh™ M5 Power Mosfet In D²Pak PackageDocument17 pagesN-Channel 650 V, 95 Mω Typ., 24 A Mdmesh™ M5 Power Mosfet In D²Pak PackageErkanNo ratings yet

- STP 120 NF 10Document19 pagesSTP 120 NF 10Paun LiviuNo ratings yet

- Stb35Nf10 Stp35Nf10: N-Channel 100V - 0.030 - 40A - D Pak/To-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument14 pagesStb35Nf10 Stp35Nf10: N-Channel 100V - 0.030 - 40A - D Pak/To-220 Low Gate Charge Stripfet™ Ii Power MosfetRichardNo ratings yet

- STP62NS04Z: N-Channel Clamped 12.5 M, 62 A, TO-220 Fully Protected MESH OVERLAY™ Power MOSFETDocument12 pagesSTP62NS04Z: N-Channel Clamped 12.5 M, 62 A, TO-220 Fully Protected MESH OVERLAY™ Power MOSFETmartinNo ratings yet

- Fcb20N60: N-Channel Superfet MosfetDocument9 pagesFcb20N60: N-Channel Superfet MosfetEo GpNo ratings yet

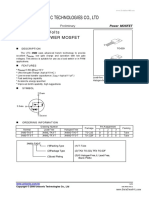

- 9N80 UnisonicTechnologiesDocument6 pages9N80 UnisonicTechnologiesJlavieraNo ratings yet

- N-Channel 600 V, 0.255 Ω Typ., 13 A Mdmesh M2 Power Mosfets In D Pak, I Pak, To-220 And To-247 PackagesDocument27 pagesN-Channel 600 V, 0.255 Ω Typ., 13 A Mdmesh M2 Power Mosfets In D Pak, I Pak, To-220 And To-247 PackagesTablet7 HomeNo ratings yet

- stl66dn3llh5Document15 pagesstl66dn3llh5mhd.mousaNo ratings yet

- MDF10N60G 1Document6 pagesMDF10N60G 1samvick103No ratings yet

- Std6N52K3: N-Channel 525 V, 1 Ω Typ., 6.5 A Mdmesh™ K3 Power Mosfet In Dpak PackageDocument18 pagesStd6N52K3: N-Channel 525 V, 1 Ω Typ., 6.5 A Mdmesh™ K3 Power Mosfet In Dpak PackageErkanNo ratings yet

- MDF7N60BDocument8 pagesMDF7N60BFreddyNo ratings yet

- 3N80Document6 pages3N80hectorsevillaNo ratings yet

- Moffet Stfu10nk60zDocument13 pagesMoffet Stfu10nk60zOmar ChirinoNo ratings yet

- STF 13 NK 50 ZDocument15 pagesSTF 13 NK 50 ZErkanNo ratings yet

- N-Channel 600 V, 0.108 Ω Typ., 26 A, Mdmesh M2 Power Mosfets In To ‑220Fp, I Pak, To-220 And To-247 PackagesDocument20 pagesN-Channel 600 V, 0.108 Ω Typ., 26 A, Mdmesh M2 Power Mosfets In To ‑220Fp, I Pak, To-220 And To-247 Packagesnio756No ratings yet

- stq1nk80zr ApDocument16 pagesstq1nk80zr ApPaun LiviuNo ratings yet

- STP 80 NF 10Document14 pagesSTP 80 NF 10Mateus BelettiNo ratings yet

- 30n06L InterfaceDocument8 pages30n06L Interfacepre freedaNo ratings yet

- P2HNC60FDocument9 pagesP2HNC60FEdmur MarianoNo ratings yet

- Data SheetDocument7 pagesData SheetAstronSatNo ratings yet

- Stp5Nk80Z Stp5Nk80Zfp: N-Channel 800V - 1.9 - 4.3A - To-220/To-220Fp Zener-Protected Supermesh™ Power MosfetDocument15 pagesStp5Nk80Z Stp5Nk80Zfp: N-Channel 800V - 1.9 - 4.3A - To-220/To-220Fp Zener-Protected Supermesh™ Power MosfetMarcilio AlmeidaNo ratings yet

- Fdp8N50Nz / Fdpf8N50Nz: N-Channel Unifet Ii MosfetDocument10 pagesFdp8N50Nz / Fdpf8N50Nz: N-Channel Unifet Ii MosfetsrasicNo ratings yet

- Stp40Nf10L: N-Channel 100V - 0.028 - 40A To-220 Low Gate Charge Stripfet™ Power MosfetDocument12 pagesStp40Nf10L: N-Channel 100V - 0.028 - 40A To-220 Low Gate Charge Stripfet™ Power MosfetKhairi SaidNo ratings yet

- IRF630 IRF630FP: N-Channel 200V - 0.35 - 9A TO-220/TO-220FP Mesh Overlay™ II Power MOSFETDocument14 pagesIRF630 IRF630FP: N-Channel 200V - 0.35 - 9A TO-220/TO-220FP Mesh Overlay™ II Power MOSFETBashir MtwaklNo ratings yet

- BLF 177Document16 pagesBLF 177Emilio EscalanteNo ratings yet

- Data Sheet: N-Channel Dual-Gate MOS-FETDocument8 pagesData Sheet: N-Channel Dual-Gate MOS-FETpenetroviskNo ratings yet

- STD 95 P 3 LLH 6 AgDocument16 pagesSTD 95 P 3 LLH 6 AgjkircsiNo ratings yet

- Stp9Nk65Z Stp9Nk65Zfp: N-Channel 650 V, 1 Ω, 6.4 A, To-220, To-220Fp Zener-Protected Supermesh™ Power MosfetDocument16 pagesStp9Nk65Z Stp9Nk65Zfp: N-Channel 650 V, 1 Ω, 6.4 A, To-220, To-220Fp Zener-Protected Supermesh™ Power MosfetAndyMahataraNo ratings yet

- SW2N60DC: N-Channel Enhanced Mode TO-252/TO-251 MOSFETDocument6 pagesSW2N60DC: N-Channel Enhanced Mode TO-252/TO-251 MOSFETdanielNo ratings yet

- Irf 634 BDocument8 pagesIrf 634 BAhmed ShagidullinNo ratings yet

- Fdb2532 - F085: N-Channel Powertrench Mosfet 150V, 79A, 16MDocument11 pagesFdb2532 - F085: N-Channel Powertrench Mosfet 150V, 79A, 16MSukandar TeaNo ratings yet

- STB 8 NM 60 DDocument13 pagesSTB 8 NM 60 DErkanNo ratings yet

- FCH25N60NDocument8 pagesFCH25N60Ngustavo gonzalezNo ratings yet

- STB 120 N 4 LF 6Document18 pagesSTB 120 N 4 LF 6Manuel QuirozNo ratings yet

- STB12NK80Z STP12NK80Z - STW12NK80ZDocument16 pagesSTB12NK80Z STP12NK80Z - STW12NK80ZMAKERNo ratings yet

- 8N65 PDFDocument8 pages8N65 PDFJose Luis CanterosNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Easychill E5Document22 pagesEasychill E5Erasmo Franco SNo ratings yet

- GXL WebDocument15 pagesGXL WebErasmo Franco SNo ratings yet

- Miniature Relays: Contact DataDocument12 pagesMiniature Relays: Contact DataErasmo Franco SNo ratings yet

- Tea 5170Document9 pagesTea 5170Erasmo Franco SNo ratings yet

- SPW17N80C3Document2 pagesSPW17N80C3Erasmo Franco SNo ratings yet

- MC1488Document8 pagesMC1488Erasmo Franco SNo ratings yet

- VXXX J Tr34 Tech-Spec 01-15Document7 pagesVXXX J Tr34 Tech-Spec 01-15Erasmo Franco SNo ratings yet

- RM84 / RM85 / RM87: Miniature Electromagnetic RelaysDocument2 pagesRM84 / RM85 / RM87: Miniature Electromagnetic RelaysErasmo Franco SNo ratings yet

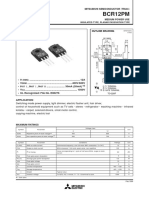

- Bcr12Pm: Mitsubishi Semiconductor TriacDocument5 pagesBcr12Pm: Mitsubishi Semiconductor TriacErasmo Franco SNo ratings yet

- SI-8201L SankenelectricDocument6 pagesSI-8201L SankenelectricErasmo Franco SNo ratings yet

- Coolmos Power Transistor: Please Note The New Package Dimensions Arccording To PCN 2009-134-ADocument11 pagesCoolmos Power Transistor: Please Note The New Package Dimensions Arccording To PCN 2009-134-AErasmo Franco SNo ratings yet

- Incremental Encoders: Hollow or End Shaft Max. Ø15 MM Resolution 5... 2048 PulsesDocument4 pagesIncremental Encoders: Hollow or End Shaft Max. Ø15 MM Resolution 5... 2048 PulsesErasmo Franco SNo ratings yet

- Microcut II Manual Rev498Document77 pagesMicrocut II Manual Rev498Erasmo Franco SNo ratings yet

- Datasheet - 2022-01-05T074219.435Document12 pagesDatasheet - 2022-01-05T074219.435Erasmo Franco SNo ratings yet

- N-Channel 0 V (D-S) Mosfet: Features Product SummaryDocument8 pagesN-Channel 0 V (D-S) Mosfet: Features Product SummaryErasmo Franco SNo ratings yet

- Lm2594, Lm2594Hv Simple Switcher Power Converter 150-Khz 0.5-A Step-Down Voltage RegulatorDocument41 pagesLm2594, Lm2594Hv Simple Switcher Power Converter 150-Khz 0.5-A Step-Down Voltage RegulatorErasmo Franco SNo ratings yet

- HCPL-2201, HCPL-2202, HCPL-2211, HCPL-2212, HCPL-2231, HCPL-2232, HCPL-0201, HCPL-0211, HCNW2201, HCNW2211Document22 pagesHCPL-2201, HCPL-2202, HCPL-2211, HCPL-2212, HCPL-2231, HCPL-2232, HCPL-0201, HCPL-0211, HCNW2201, HCNW2211Erasmo Franco SNo ratings yet