Professional Documents

Culture Documents

Abstract of Research For The Conference: Hassan Bin Qasim 2019-MS-EE-38

Abstract of Research For The Conference: Hassan Bin Qasim 2019-MS-EE-38

Uploaded by

Hassan Bin Qasim0 ratings0% found this document useful (0 votes)

22 views2 pagesOriginal Title

abstract

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

0 ratings0% found this document useful (0 votes)

22 views2 pagesAbstract of Research For The Conference: Hassan Bin Qasim 2019-MS-EE-38

Abstract of Research For The Conference: Hassan Bin Qasim 2019-MS-EE-38

Uploaded by

Hassan Bin QasimCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

You are on page 1of 2

Abstract of Research for the Conference

Hassan bin Qasim 2019-MS-EE-38

Abstract:

In this abstract, we have design three devices, a homo p-n, a hetero p-n, and, a Schottky

junction. We will use CdTe semiconductor materials to implement these devices. CdTe

devices have reached efficiencies of 22.1% due to continuing improvements in bulk material

properties, including minority carrier lifetime. Device modelling has helped guide these

device improvements by quantifying the impacts of material properties and different device

designs on device performance. One of the barriers to truly predictive device modelling is the

interdependence of these material properties. For example, interfaces become more critical as

bulk properties, particularly hole density and carrier lifetime, increase. We present device‐

modelling analyses that describe the effects of recombination at the interfaces and grain

boundaries as lifetime and doping of the CdTe layer change. The doping and lifetime should

be priorities for maximizing open‐circuit voltage (Voc) and efficiency improvements.

However, interface and grain boundary (GB) recombination become bottlenecks to device

performance at increased lifetime and doping levels. This work quantifies and discusses these

emerging challenges for next‐generation CdTe device efficiency. In our paper we are

following a research paper and doing simulation of CdTe solar cell on AFROS-HET software

and then we will compare our results with paper result

You might also like

- Assessment of Effective Stiffness Formulation of Concrete Coated Rigid Pipeline (ASME Paper)Document6 pagesAssessment of Effective Stiffness Formulation of Concrete Coated Rigid Pipeline (ASME Paper)bubbly_blu2No ratings yet

- !$if'ffi/l Ffi: IntermediateDocument1 page!$if'ffi/l Ffi: IntermediateHassan Bin QasimNo ratings yet

- Journal of Power Sources: L.A. Rom An-Ramírez, G. Apachitei, M. Faraji-Niri, M. Lain, W.D. Widanage, J. MarcoDocument11 pagesJournal of Power Sources: L.A. Rom An-Ramírez, G. Apachitei, M. Faraji-Niri, M. Lain, W.D. Widanage, J. MarcoMDRNo ratings yet

- Predicting Lifetime PCB IpcDocument30 pagesPredicting Lifetime PCB IpcJose LopezNo ratings yet

- Research Article: Experimental and Numerical Failure Analysis of Adhesive Composite JointsDocument10 pagesResearch Article: Experimental and Numerical Failure Analysis of Adhesive Composite Jointsmkiani2No ratings yet

- Impacts of Variations in Manufacturing Parameters On Performance of Lithium-Ion-BatteriesDocument9 pagesImpacts of Variations in Manufacturing Parameters On Performance of Lithium-Ion-BatteriesMDRNo ratings yet

- Composite Bolted Joints Analysis ProgramsDocument11 pagesComposite Bolted Joints Analysis ProgramschrisfaureNo ratings yet

- Microelectronics Reliability: P.F. Butzen, V. Dal Bem, A.I. Reis, R.P. RibasDocument5 pagesMicroelectronics Reliability: P.F. Butzen, V. Dal Bem, A.I. Reis, R.P. RibasAdip ChyNo ratings yet

- Literature Review of SupercapacitorDocument4 pagesLiterature Review of Supercapacitorafmzvadopepwrb100% (1)

- For Tensile Armour Wire Anchoring in A Flexible Pipe End FittingDocument8 pagesFor Tensile Armour Wire Anchoring in A Flexible Pipe End FittingMarcelo Varejão CasarinNo ratings yet

- Lee2022 Article ApproachesToSustainabilityInChDocument19 pagesLee2022 Article ApproachesToSustainabilityInChnamhuiNo ratings yet

- CERI Regina BulatovaDocument16 pagesCERI Regina Bulatovakinosraj kumaranNo ratings yet

- Lee 2015Document9 pagesLee 2015Doaa KamalNo ratings yet

- Injection-Molded Lightweight and High Electrical Conductivity Composites With Microcellular Structure and Hybrid FillersDocument22 pagesInjection-Molded Lightweight and High Electrical Conductivity Composites With Microcellular Structure and Hybrid Fillerstalán gybrNo ratings yet

- CdTe Solar Cells at The Threshold To 20% EfficiencyDocument5 pagesCdTe Solar Cells at The Threshold To 20% EfficiencyDemian Matus FuentesNo ratings yet

- SPE-194250-MS Optimized Coiled TubingDocument16 pagesSPE-194250-MS Optimized Coiled TubingbarcristianNo ratings yet

- LCA of Electricity Networks A ReviewDocument12 pagesLCA of Electricity Networks A ReviewAlvaro GonzálezNo ratings yet

- BioRes 07 2 B Popil Overview Edge Compression Buckling 1006Document30 pagesBioRes 07 2 B Popil Overview Edge Compression Buckling 1006SubtabNo ratings yet

- Dong2021 PDFDocument55 pagesDong2021 PDFmahmood majedNo ratings yet

- 1 s2.0 S2949821X23000844 MainDocument7 pages1 s2.0 S2949821X23000844 MainABDELKHALK ABOULOUARDNo ratings yet

- An Examination of Additive Manufacturing ProcessesDocument12 pagesAn Examination of Additive Manufacturing ProcessesShashank PhansikarNo ratings yet

- Shear Characterization of Adhesive Layers by Advanced Optical TechniquesDocument14 pagesShear Characterization of Adhesive Layers by Advanced Optical TechniquesyasminaNo ratings yet

- IETE D314ijarse PDFDocument10 pagesIETE D314ijarse PDFRàhuł MathiasNo ratings yet

- Gate All Around Fet: An Alternative of Finfet For Future Technology NodesDocument10 pagesGate All Around Fet: An Alternative of Finfet For Future Technology NodesRàhuł MathiasNo ratings yet

- Literature Review 2Document9 pagesLiterature Review 2K Bhavish V SuvarnaNo ratings yet

- Interfacial Aspects Ofc Arbon CompositesDocument69 pagesInterfacial Aspects Ofc Arbon CompositesDavid Frias BastarNo ratings yet

- TextureJet Metal Surface Preparation For BondingDocument8 pagesTextureJet Metal Surface Preparation For BondingAnonymous cgDfsNNo ratings yet

- Pipeline Damage Prediction by Det. Models and AIDocument10 pagesPipeline Damage Prediction by Det. Models and AIНикита ВязиковNo ratings yet

- Muhammad Athala Zakwan 1-IDocument5 pagesMuhammad Athala Zakwan 1-Iathala zakwanNo ratings yet

- Microwave Filter ThesisDocument5 pagesMicrowave Filter Thesisafktmeiehcakts100% (1)

- 2014 - Robust Optimization of Hydrogen NetworkDocument10 pages2014 - Robust Optimization of Hydrogen NetworkFSBollNo ratings yet

- SPE-143623-MS-Torque and Drag Software Model Comparison Impact On Application and Calibration of Field DataDocument11 pagesSPE-143623-MS-Torque and Drag Software Model Comparison Impact On Application and Calibration of Field DataHassaanAhmedNo ratings yet

- Analytical Model For Resistivity and Mean Free Path in On-Chip Interconnects With Rough SurfacesDocument11 pagesAnalytical Model For Resistivity and Mean Free Path in On-Chip Interconnects With Rough SurfacesSomesh DahiyaNo ratings yet

- Numerical and Experimental Study of Transparent Electrode Effect For Charge Transport Layer-Free Perovskite Solar CellsDocument18 pagesNumerical and Experimental Study of Transparent Electrode Effect For Charge Transport Layer-Free Perovskite Solar CellsJiji AttNo ratings yet

- Thesis About MSGDocument8 pagesThesis About MSGCustomPaperServiceFargo100% (2)

- Journal of Power Sources: Siddharth Gadkari, Sai Gu, Jhuma SadhukhanDocument11 pagesJournal of Power Sources: Siddharth Gadkari, Sai Gu, Jhuma SadhukhanAzka MufidNo ratings yet

- Dynamic Roughness APFDocument12 pagesDynamic Roughness APFJoaquinNo ratings yet

- Project Green Manufacturing With Resistance Spot WeldingDocument49 pagesProject Green Manufacturing With Resistance Spot Weldingguravshubham7777No ratings yet

- New Method To Measure The Adhesion Capability of Metallic Surface Under Shear Loading Using A Modified Arcan TestDocument31 pagesNew Method To Measure The Adhesion Capability of Metallic Surface Under Shear Loading Using A Modified Arcan TestMatt LABNo ratings yet

- Mechanical Properties of 3D Printed Architected Polmer Foams Under Large DeformationsDocument13 pagesMechanical Properties of 3D Printed Architected Polmer Foams Under Large DeformationsHumphrey Tarry NyokaNo ratings yet

- PROCEEDINGS Mjab PDFDocument8 pagesPROCEEDINGS Mjab PDFTatu KärkiNo ratings yet

- 2009 EMC Industrial Inverter Aime CN57Document2 pages2009 EMC Industrial Inverter Aime CN57Juan Gil RocaNo ratings yet

- 2009Document17 pages2009Ziyou LiNo ratings yet

- Additive Manufacturing DissertationDocument9 pagesAdditive Manufacturing DissertationWhereCanYouBuyResumePaperSingapore100% (1)

- Prem ConnectionDocument2 pagesPrem ConnectionJan Arild SkappelNo ratings yet

- Charc of 19.9 Per CZTS Solar CellDocument9 pagesCharc of 19.9 Per CZTS Solar CellVivek BelaNo ratings yet

- Fuel Cell PHD ThesisDocument5 pagesFuel Cell PHD Thesissbbftinbf100% (2)

- Damage Analysis of Composite-Aluminium Adhesively-Bonded Single-Lap JointseeeDocument9 pagesDamage Analysis of Composite-Aluminium Adhesively-Bonded Single-Lap JointseeeabiliovieiraNo ratings yet

- Analysis of Durability of High Performance Concrete Using Artificial Neural NetworksDocument8 pagesAnalysis of Durability of High Performance Concrete Using Artificial Neural NetworksBaneeIshaqueKNo ratings yet

- Ipc2012 90620Document17 pagesIpc2012 90620Marcelo Varejão CasarinNo ratings yet

- Literature Review On BatteriesDocument9 pagesLiterature Review On Batterieschrvzyukg100% (1)

- PHD Thesis Electricity MarketDocument6 pagesPHD Thesis Electricity Marketlisaandersonshreveport100% (2)

- Spot WeldingDocument15 pagesSpot WeldingLívia RodriguesNo ratings yet

- Ciardiello 2021 IOP Conf. Ser. Mater. Sci. Eng. 1038 012031Document13 pagesCiardiello 2021 IOP Conf. Ser. Mater. Sci. Eng. 1038 012031Paulo UtargNo ratings yet

- Sólyom Sándor, Balázs L GyörgyBond Behaviour FRPDocument18 pagesSólyom Sándor, Balázs L GyörgyBond Behaviour FRPSameerNo ratings yet

- Doctoral Thesis in Solid Mechanics (Impact of Paperboard Deformation and Damage Mechanisms On Packaging Perfomance)Document71 pagesDoctoral Thesis in Solid Mechanics (Impact of Paperboard Deformation and Damage Mechanisms On Packaging Perfomance)dnavaNo ratings yet

- Eccentric Block FailureDocument7 pagesEccentric Block FailureJohnprasannaNo ratings yet

- 008makino - Edited - NEWDocument19 pages008makino - Edited - NEWFilip Van den AbeeleNo ratings yet

- Life Cycle Assessment of Lithium-Air Cells Article Rev 20160503Document29 pagesLife Cycle Assessment of Lithium-Air Cells Article Rev 20160503Jorge CarrionNo ratings yet

- Fire Ge Call2Document7 pagesFire Ge Call2utsav mannuNo ratings yet

- Gallium Nitride-enabled High Frequency and High Efficiency Power ConversionFrom EverandGallium Nitride-enabled High Frequency and High Efficiency Power ConversionGaudenzio MeneghessoNo ratings yet

- TotkaDocument3 pagesTotkaHassan Bin QasimNo ratings yet

- Supplementary Components and System: Engr - Kashif IqbalDocument21 pagesSupplementary Components and System: Engr - Kashif IqbalHassan Bin QasimNo ratings yet

- UltrasonographyDocument3 pagesUltrasonographyHassan Bin QasimNo ratings yet

- Hassan Bin Qasim: ObjectiveDocument2 pagesHassan Bin Qasim: ObjectiveHassan Bin QasimNo ratings yet

- Hassan 3Document1 pageHassan 3Hassan Bin QasimNo ratings yet

- Hassan Bin Qasim: Bsc. Electronic Engineer +92-321-630-2447Document2 pagesHassan Bin Qasim: Bsc. Electronic Engineer +92-321-630-2447Hassan Bin QasimNo ratings yet

- Doc1 2Document2 pagesDoc1 2Hassan Bin QasimNo ratings yet

- Hassan Bin Qasim: Bsc. Electronic Engineer +92-321-635-5885Document3 pagesHassan Bin Qasim: Bsc. Electronic Engineer +92-321-635-5885Hassan Bin QasimNo ratings yet

- Book 1 TemplateDocument23 pagesBook 1 TemplateHassan Bin QasimNo ratings yet

- Computational Design of Hysteresis Free Perovskite Solar CellDocument12 pagesComputational Design of Hysteresis Free Perovskite Solar CellHassan Bin QasimNo ratings yet

- Hassan Bin Qasim: House No. 409 Shah Shams Road Wahdat Colony Multan Phone No: +92321-6302447, E-MailDocument2 pagesHassan Bin Qasim: House No. 409 Shah Shams Road Wahdat Colony Multan Phone No: +92321-6302447, E-MailHassan Bin QasimNo ratings yet

- !$if'ffi/l Ffi: IntermediateDocument1 page!$if'ffi/l Ffi: IntermediateHassan Bin QasimNo ratings yet

- Hassan 1Document1 pageHassan 1Hassan Bin QasimNo ratings yet

- Schedule Homework For 9th Class Mathematics: Unit Name Topics and ExercisesDocument1 pageSchedule Homework For 9th Class Mathematics: Unit Name Topics and ExercisesHassan Bin QasimNo ratings yet

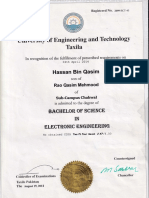

- Graduation DegreeDocument1 pageGraduation DegreeHassan Bin QasimNo ratings yet

- 010nawaqiz10 MagicDocument4 pages010nawaqiz10 MagicHassan Bin QasimNo ratings yet

- The Process of An Islamic RevolutionDocument2 pagesThe Process of An Islamic RevolutionHassan Bin QasimNo ratings yet

- Hassan Bin Qasim: ObjectiveDocument2 pagesHassan Bin Qasim: ObjectiveHassan Bin QasimNo ratings yet

- Concept of Intelligent Extraterrestrial Life in The Quran-2Document14 pagesConcept of Intelligent Extraterrestrial Life in The Quran-2Vahid ArvischNo ratings yet

- Design and Implementation of RCIED Jamming SystemDocument20 pagesDesign and Implementation of RCIED Jamming SystemHassan Bin QasimNo ratings yet

- Hassan Bin Qasim: ObjectiveDocument2 pagesHassan Bin Qasim: ObjectiveHassan Bin QasimNo ratings yet

- Yagi Antenna Design For Signal Phone Jammer: Y. Fitriyani, A.B. Mutiara, R. RefiantiDocument6 pagesYagi Antenna Design For Signal Phone Jammer: Y. Fitriyani, A.B. Mutiara, R. RefiantiHassan Bin QasimNo ratings yet

- Combined Entry Test For Admission in Engineering InstitutionsDocument2 pagesCombined Entry Test For Admission in Engineering InstitutionsHassan Bin QasimNo ratings yet