Professional Documents

Culture Documents

Ec0033-Asic Design-Model Qp-Vii Sem-Set2

Ec0033-Asic Design-Model Qp-Vii Sem-Set2

Uploaded by

skarthikpriyaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ec0033-Asic Design-Model Qp-Vii Sem-Set2

Ec0033-Asic Design-Model Qp-Vii Sem-Set2

Uploaded by

skarthikpriyaCopyright:

Available Formats

Reg. No.

D algorithm

SRM INSTITUTE OF SCIENCE AND TECHNOLOGY (OR)

Model Exam – Oct - 2019 b. What is fault modeling? Explain various types of faults.

Seventh Semester – Department of Electronics and Communication

Engineering 15 a. Apply KL algorithm for figure2 and find the minimum cut cost

asuume edge cost as 1

PEC0033 – ASIC Design (OR)

Duration: 3 Hrs Max. Marks: 100 b. With an example explain left edge channel routing algorithm and Lee

PART – A (10 X 2 = 20 Marks) maze routing

Answer ALL Questions

1. Size a 3 input NAND gate to achieve equal rise time and fall time

2. Design a XNOR gate using Transmission gates

3. Explain logic expander in Altera Max architecture

4. Draw a ONO and MIM Antifuse

5. List different types of Memory synthesis approach

6. What is logic optimization?

7. Draw the BIST Architecture and list various components associated.

8. Find the test vector for SA1 at the output of 2 input NOR gate

9. What are the objectives of partitioning?

10. What is the goal of global routing

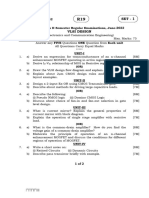

Figure1

PART – B (5 X 16= 80 Marks)

Answer ALL questions

11. a. Explain the various steps involved in ASIC Design

(OR)

b. Draw OAI321 and AOI22 logic cells and size it.

12. a. Draw and explain the features of XILINX XC5200 architecture

(OR)

b. Explain the features of ACTEL ACT interconnects

13 a. Illustrate various approaches of FSM synthesis

(OR) Figure2

b. Write short notes on various modes of simulation

14 a. Determine the Test vector for SA0 fault shown below in figure1

using

You might also like

- Ec0033-Asic Design-Model Qp-Vii Sem-Set1Document1 pageEc0033-Asic Design-Model Qp-Vii Sem-Set1skarthikpriyaNo ratings yet

- Ec0033-Asic Design-Model Qp-Vii SemDocument1 pageEc0033-Asic Design-Model Qp-Vii SemskarthikpriyaNo ratings yet

- 2008 Anna UniversityDocument1 page2008 Anna UniversitysasitsnNo ratings yet

- Ec 1401 Vlsi DesignDocument2 pagesEc 1401 Vlsi DesignsubhazNo ratings yet

- Ap7202-Asic and FpgaDocument12 pagesAp7202-Asic and FpgaMOTHI.R MEC-AP/ECENo ratings yet

- Time: 3 Hours Total Marks: 100: Printed Pages: 02 Sub Code:NEC703 Paper Id: 130718 Roll NoDocument2 pagesTime: 3 Hours Total Marks: 100: Printed Pages: 02 Sub Code:NEC703 Paper Id: 130718 Roll NoDeepanshi RuhelaNo ratings yet

- rr321202 Vlsi Systems DesignDocument4 pagesrr321202 Vlsi Systems DesignSRINIVASA RAO GANTANo ratings yet

- Time: 3 Hours Total Marks: 70: PD PLDocument1 pageTime: 3 Hours Total Marks: 70: PD PLDeepanshi RuhelaNo ratings yet

- VLSI DesignDocument7 pagesVLSI DesignVarun ThejNo ratings yet

- Department of Ece Model Examination Vl9261 - Asic Design: PART B - (5 × 16 80 Marks)Document2 pagesDepartment of Ece Model Examination Vl9261 - Asic Design: PART B - (5 × 16 80 Marks)Anandhi SrinivasanNo ratings yet

- Jntua University Previous Question Papers: Dept., of E.C.E, RCEWDocument4 pagesJntua University Previous Question Papers: Dept., of E.C.E, RCEWHarshini ANo ratings yet

- Question Paper Code:: Reg. No.Document3 pagesQuestion Paper Code:: Reg. No.Joshua DuffyNo ratings yet

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- Low Power VLSI 2022-23Document1 pageLow Power VLSI 2022-23souranshusNo ratings yet

- DLC Model IDocument2 pagesDLC Model IEEE DEPTNo ratings yet

- VLSI Question PaperDocument3 pagesVLSI Question Paper209X1A04D2 SHAIK ASMANo ratings yet

- Iii Ece VlsiDocument2 pagesIii Ece VlsiDelphin RoseNo ratings yet

- Cadcam Iat - 3 Question PaperDocument1 pageCadcam Iat - 3 Question PaperSelvaraj GNo ratings yet

- Vlsi QP 21,22Document11 pagesVlsi QP 21,22Arunitha ArulnathanNo ratings yet

- 15A04802 Low Power VLSI Circuits & SystemsDocument1 page15A04802 Low Power VLSI Circuits & SystemsMALLAVARAPU NARASAREDDYNo ratings yet

- Question Paper Code: X10348: Reg. NoDocument2 pagesQuestion Paper Code: X10348: Reg. NoJaikumar RajendranNo ratings yet

- VLSI DesignDocument1 pageVLSI DesignSurendar AviNo ratings yet

- 9A15502 Digital System DesignDocument4 pages9A15502 Digital System Designsivabharathamurthy100% (1)

- ASIC Design 2010 April (02 Ad)Document1 pageASIC Design 2010 April (02 Ad)Anand RajNo ratings yet

- Question Paper CodeDocument3 pagesQuestion Paper CodeDinesh SrinivasanNo ratings yet

- Rr311901 Digital Systems DesignDocument8 pagesRr311901 Digital Systems DesignSrinivasa Rao GNo ratings yet

- Previous Question PapersDocument4 pagesPrevious Question Papersshaker423No ratings yet

- Erts - Model 1Document3 pagesErts - Model 1Ece DeptNo ratings yet

- M.E. (VLSI & Embedded System) : Asic Design and Modelling (2008 Course)Document9 pagesM.E. (VLSI & Embedded System) : Asic Design and Modelling (2008 Course)Manu SeaNo ratings yet

- Model Exam Ocn 3Document2 pagesModel Exam Ocn 3Prabu KumarNo ratings yet

- Previous Year Question PaperDocument11 pagesPrevious Year Question PaperMinuNo ratings yet

- VLSIDesignDocument5 pagesVLSIDesignVenkatesh KolatiNo ratings yet

- EM506 VLSI ArchitectureDocument5 pagesEM506 VLSI ArchitecturePrakash Velayudham VNo ratings yet

- Rr410505 Vlsi Systems DesignDocument4 pagesRr410505 Vlsi Systems DesignSrinivasa Rao GNo ratings yet

- Tutdac 99Document2 pagesTutdac 99baburao_kodavatiNo ratings yet

- Vlsi Design June 2022Document8 pagesVlsi Design June 2022SivaGaneshGollaNo ratings yet

- Question Bank For Mid-2 r13 (Vlsi) .Document6 pagesQuestion Bank For Mid-2 r13 (Vlsi) .rppvchNo ratings yet

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Document8 pagesWWW - Manaresults.Co - In: (Electronics and Communication Engineering)Adhvay KrishnaNo ratings yet

- FPGA Based System DesignDocument2 pagesFPGA Based System Designammayi9845_930467904No ratings yet

- Cmos Dec 2019Document2 pagesCmos Dec 2019Prabhodh KulkarniNo ratings yet

- Previous Question PapersDocument11 pagesPrevious Question PapersShaik Sadhik BashaNo ratings yet

- JNTU Anantapur B.tech 2017 Third Year Second Sem R13 13A03601 CAD CAM FR 192Document1 pageJNTU Anantapur B.tech 2017 Third Year Second Sem R13 13A03601 CAD CAM FR 192Rammohan ReddyNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.Sharath ChandanNo ratings yet

- SEPTEMBERDocument3 pagesSEPTEMBERRocky BobeeNo ratings yet

- Low Power Vlsi Question PaperDocument2 pagesLow Power Vlsi Question Paperustadkrishna100% (3)

- Question Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodeDocument2 pagesQuestion Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodePrabu KumarNo ratings yet

- WWW - Manaresults.co - In: Vlsi DesignDocument2 pagesWWW - Manaresults.co - In: Vlsi DesignjagadeeshNo ratings yet

- Vlsi Model 4-QPDocument2 pagesVlsi Model 4-QPsanthoshNo ratings yet

- Q Paper 09ec61 May June 2012Document2 pagesQ Paper 09ec61 May June 2012Bhaskar MishraNo ratings yet

- Mohamed Sathak A J College of Engineering: Model Exam (Set 1)Document3 pagesMohamed Sathak A J College of Engineering: Model Exam (Set 1)formyphdNo ratings yet

- Advanced Digital VLSI Design (ECE 521) (Makeup) PDFDocument2 pagesAdvanced Digital VLSI Design (ECE 521) (Makeup) PDFRahul PinnamaneniNo ratings yet

- Ec 703 2019-20Document2 pagesEc 703 2019-202000520310061No ratings yet

- Mr3492 Esp Model QN PaperDocument3 pagesMr3492 Esp Model QN PaperKeerthana SahadevanNo ratings yet

- Analog Digital Apr2009Document2 pagesAnalog Digital Apr2009humtum_shri5736No ratings yet

- Embedded System Design PDFDocument37 pagesEmbedded System Design PDFLavanya R GowdaNo ratings yet

- Embedded System Design - Term-1Document2 pagesEmbedded System Design - Term-1Gokul SNo ratings yet

- Token Ring Technology ReportFrom EverandToken Ring Technology ReportNo ratings yet

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionFrom EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionNo ratings yet

- Bebop to the Boolean Boogie: An Unconventional Guide to ElectronicsFrom EverandBebop to the Boolean Boogie: An Unconventional Guide to ElectronicsRating: 4 out of 5 stars4/5 (3)

- Cpre 288 - Introduction To Embedded Systems: Instructors: Dr. Phillip JonesDocument89 pagesCpre 288 - Introduction To Embedded Systems: Instructors: Dr. Phillip JonesskarthikpriyaNo ratings yet

- NBA QP FORMAT - Cycle Test 01 - III Yr - EHOSDocument6 pagesNBA QP FORMAT - Cycle Test 01 - III Yr - EHOSskarthikpriyaNo ratings yet

- Gpio 2Document12 pagesGpio 2skarthikpriyaNo ratings yet

- Instructors: Dr. Phillip JonesDocument44 pagesInstructors: Dr. Phillip JonesskarthikpriyaNo ratings yet

- Short Channel Effects and ScalingDocument23 pagesShort Channel Effects and ScalingskarthikpriyaNo ratings yet

- SRM Institute of Science & Technology - Academic Curricula (2019 Part Time Regulations) 37Document2 pagesSRM Institute of Science & Technology - Academic Curricula (2019 Part Time Regulations) 37skarthikpriyaNo ratings yet

- M.E CSE Curriculum and Syllabus PDFDocument99 pagesM.E CSE Curriculum and Syllabus PDFskarthikpriyaNo ratings yet

- Cla1 - EhosDocument4 pagesCla1 - EhosskarthikpriyaNo ratings yet

- UML - Deployment Diagrams - Tutorialspoint PDFDocument3 pagesUML - Deployment Diagrams - Tutorialspoint PDFskarthikpriyaNo ratings yet

- 18CSC202J Set1Document1 page18CSC202J Set1skarthikpriyaNo ratings yet

- 18CSC202J Set2Document1 page18CSC202J Set2skarthikpriyaNo ratings yet

- CT3 QP-18EES101J BEEE - Set1Document2 pagesCT3 QP-18EES101J BEEE - Set1skarthikpriyaNo ratings yet

- Active and Collaborative LearningDocument4 pagesActive and Collaborative LearningskarthikpriyaNo ratings yet

- CDC Question TemplateDocument4 pagesCDC Question TemplateskarthikpriyaNo ratings yet

- Xilinx SDKDocument11 pagesXilinx SDKskarthikpriyaNo ratings yet

- UML - Component Diagrams - Tutorialspoint PDFDocument3 pagesUML - Component Diagrams - Tutorialspoint PDFskarthikpriyaNo ratings yet

- 8251 Material PDFDocument31 pages8251 Material PDFskarthikpriyaNo ratings yet

- Pre-Reading - 1Document24 pagesPre-Reading - 1skarthikpriyaNo ratings yet

- VLSI Technology Trends .: DR Usha Mehta Usha - Mehta@nirmauni - Ac.inDocument78 pagesVLSI Technology Trends .: DR Usha Mehta Usha - Mehta@nirmauni - Ac.inskarthikpriyaNo ratings yet

- Chip Design Flow and Hardware ModellingDocument39 pagesChip Design Flow and Hardware Modellingskarthikpriya100% (1)

- CT3 QP-18EES101J BEEE - Set2Document2 pagesCT3 QP-18EES101J BEEE - Set2skarthikpriyaNo ratings yet

- Ec0033-Asic Design-Model Qp-Vii SemDocument1 pageEc0033-Asic Design-Model Qp-Vii SemskarthikpriyaNo ratings yet

- Interactive Techniques: Instructor Action: LectureDocument24 pagesInteractive Techniques: Instructor Action: LectureskarthikpriyaNo ratings yet

- Ct3-Asic Set BDocument1 pageCt3-Asic Set BskarthikpriyaNo ratings yet

- Ec0033-Asic Design-Model Qp-Vii Sem-Set1Document1 pageEc0033-Asic Design-Model Qp-Vii Sem-Set1skarthikpriyaNo ratings yet

- Ct3-Asic Set ADocument1 pageCt3-Asic Set AskarthikpriyaNo ratings yet

- SRM Institute of Science and Technology CYCLE TEST - III April-2019 15EE232 - EECS PART - A (10 X 1 10 Marks)Document2 pagesSRM Institute of Science and Technology CYCLE TEST - III April-2019 15EE232 - EECS PART - A (10 X 1 10 Marks)skarthikpriyaNo ratings yet