Professional Documents

Culture Documents

88E6393X Development Board User Manual

88E6393X Development Board User Manual

Uploaded by

wxzcldw163.comCopyright:

Available Formats

You might also like

- Cambridge Audio Azur 851a Service ManualDocument75 pagesCambridge Audio Azur 851a Service ManualDavid NicolasNo ratings yet

- 4706 DS00 R BCM4706 Advance Data Sheet NDA ClearDocument62 pages4706 DS00 R BCM4706 Advance Data Sheet NDA Clearbb06412000No ratings yet

- Business Requirements For : Revision HistoryDocument16 pagesBusiness Requirements For : Revision HistoryVenkata Madhusudana Reddy BhumaNo ratings yet

- La C621P PDFDocument60 pagesLa C621P PDFJerzy LisowskiNo ratings yet

- Aspire Z1-612 SchematicDocument108 pagesAspire Z1-612 SchematicRakesh Singh100% (2)

- DS D3041-ADocument2 pagesDS D3041-AvagusdisarmNo ratings yet

- Microphone ConnectorsDocument49 pagesMicrophone ConnectorsAntonio José Ervilha Regalo100% (1)

- Change Request Form SAP Business OneDocument2 pagesChange Request Form SAP Business OneMarcin Orgacki100% (2)

- iOS 11 (2018)Document3 pagesiOS 11 (2018)jadi gini, nah gituNo ratings yet

- Marvell Phys Transceivers Alaska 88e151x Datasheet 2018 02 PDFDocument154 pagesMarvell Phys Transceivers Alaska 88e151x Datasheet 2018 02 PDFanhxcoNo ratings yet

- Intel Ethernet Connection I219 Reference Schematic Rev1 0Document1 pageIntel Ethernet Connection I219 Reference Schematic Rev1 0Смартфон СигмаNo ratings yet

- Intel (R) ME SW Installation GuideDocument31 pagesIntel (R) ME SW Installation Guidearvinarvind60No ratings yet

- ASM1053 Datasheet v0.5Document18 pagesASM1053 Datasheet v0.5Enrique PalacioNo ratings yet

- DAM00 DAM01 LA-F541P R20 - 3PH MB-20180328 Coffee Lake-HDocument75 pagesDAM00 DAM01 LA-F541P R20 - 3PH MB-20180328 Coffee Lake-HDude JonesNo ratings yet

- Marvell Phys Transceivers Alaska 88e1111 Technical Product Brief 2013 10Document56 pagesMarvell Phys Transceivers Alaska 88e1111 Technical Product Brief 2013 10Brijesh ShahNo ratings yet

- 88E1111 Datasheet: Integrated 10/100/1000 Ultra Gigabit Ethernet TransceiverDocument252 pages88E1111 Datasheet: Integrated 10/100/1000 Ultra Gigabit Ethernet TransceiverNicholas MoodyNo ratings yet

- 88E1111 SFP RefDsgn Schematics Rev 1 0newDocument3 pages88E1111 SFP RefDsgn Schematics Rev 1 0newKukla LossNo ratings yet

- Intel - Serial IO - Bring Up Guide and Release Note Rev1.0Document25 pagesIntel - Serial IO - Bring Up Guide and Release Note Rev1.0Nurfatini CheNo ratings yet

- 1 5MB FW Release Notes 7 1 52 1176 HFDocument60 pages1 5MB FW Release Notes 7 1 52 1176 HFEko Billy SetiawanNo ratings yet

- Intel Serial IO - Bring Up Guide and Release Note Rev1p0Document30 pagesIntel Serial IO - Bring Up Guide and Release Note Rev1p0gdfeiu dionwdnNo ratings yet

- Intel (R) MEBX User Guide PDFDocument57 pagesIntel (R) MEBX User Guide PDFBlubNo ratings yet

- DH67GD DH67BL TechProdSpecDocument92 pagesDH67GD DH67BL TechProdSpecjagan2003No ratings yet

- JMB585 PDFDocument10 pagesJMB585 PDFBono PrakosoNo ratings yet

- Rev: A: ECS ConfidentialDocument37 pagesRev: A: ECS ConfidentialEdgar Geovanny Varela MoralesNo ratings yet

- Intel Smart Connect Technology: Setup & Configuration GuideDocument44 pagesIntel Smart Connect Technology: Setup & Configuration GuideChhoemSovannNo ratings yet

- Intel (R) Serial IO - Bring Up Guide and Release Note Rev1p1Document25 pagesIntel (R) Serial IO - Bring Up Guide and Release Note Rev1p1YomaraNoemiPalmaAguirreNo ratings yet

- Coffee Lake H/S Platform System Memory Interface: Technical White PaperDocument51 pagesCoffee Lake H/S Platform System Memory Interface: Technical White PaperagxinNo ratings yet

- Intel (R) ME SW Installation GuideDocument36 pagesIntel (R) ME SW Installation GuideJesús Gildardo Mejía CortésNo ratings yet

- MB Manual Ga-z87x-Ud3h eDocument124 pagesMB Manual Ga-z87x-Ud3h ejazz240% (1)

- 1.5MB FW Bring Up Guide 8.1.0.1248 PVDocument131 pages1.5MB FW Bring Up Guide 8.1.0.1248 PVjorge bernalNo ratings yet

- MB Manual Ga-Z87 (h87) - Hd3 eDocument100 pagesMB Manual Ga-Z87 (h87) - Hd3 estarlaysNo ratings yet

- Manual Gigabyte Ga z87 d3hpDocument104 pagesManual Gigabyte Ga z87 d3hpslade3No ratings yet

- HX8398 PDFDocument293 pagesHX8398 PDFBayan MashrequiNo ratings yet

- VSCCommn - Bin Content 4.8.0Document14 pagesVSCCommn - Bin Content 4.8.0Uncle KnownNo ratings yet

- Fab A: Cpu: System Chipset: Main Memory: On Board DeviceDocument46 pagesFab A: Cpu: System Chipset: Main Memory: On Board DeviceFlavianoSilva100% (1)

- Dell Alienwarem 15 r2 Compal Edq51 La-H351p La-F552p La-F553p 1.0 (Xa00)Document109 pagesDell Alienwarem 15 r2 Compal Edq51 La-H351p La-F552p La-F553p 1.0 (Xa00)ml5801088No ratings yet

- Marvell Data SheetDocument4 pagesMarvell Data Sheetkrishnaec82No ratings yet

- JM20337 Datasheet v1.1Document15 pagesJM20337 Datasheet v1.1Mehmet DemirNo ratings yet

- Client BIOS 2012 CRB BIOS 98 Release Notes PDFDocument37 pagesClient BIOS 2012 CRB BIOS 98 Release Notes PDFUnfaithful AngelNo ratings yet

- Msi H81m-E33 MS-7817 Rev. 1.0Document32 pagesMsi H81m-E33 MS-7817 Rev. 1.0GudangNo ratings yet

- Intel Converged Security and Management Engine Software: Installation and Configuration GuideDocument34 pagesIntel Converged Security and Management Engine Software: Installation and Configuration GuideJailson Da SilvaNo ratings yet

- 3 - H5-Training Manual (LCD) - 080410Document37 pages3 - H5-Training Manual (LCD) - 080410Jorge Fernando de TivantaNo ratings yet

- Gigabyte Confidential Do Not Copy: Model Name: GA-TG965MP-RH-GWDocument36 pagesGigabyte Confidential Do Not Copy: Model Name: GA-TG965MP-RH-GWSjf NetNo ratings yet

- Acer Aspire One 522 AO522 - COMPAL LA-7072P - REV 1.0sec PDFDocument36 pagesAcer Aspire One 522 AO522 - COMPAL LA-7072P - REV 1.0sec PDFMcgregori AndradeNo ratings yet

- VUTEk ColorBurst 7.5 User ManualDocument172 pagesVUTEk ColorBurst 7.5 User ManualPaulo Alberto100% (1)

- Ds NV Quadro k1200 Feb15 NV Us HRDocument1 pageDs NV Quadro k1200 Feb15 NV Us HRJose PazNo ratings yet

- MB Manual Ga-G41mt-S2pt e PDFDocument40 pagesMB Manual Ga-G41mt-S2pt e PDFLeonel AtaramaNo ratings yet

- Toshiba 32av700e LCD TV SCHDocument44 pagesToshiba 32av700e LCD TV SCHMuhammad Ihsan100% (1)

- NES Famicom PinoutsDocument1 pageNES Famicom PinoutsgbyudbyNo ratings yet

- Manual Service 50UHD 9M32BDocument44 pagesManual Service 50UHD 9M32BOfelia GiménezNo ratings yet

- Dell/Compal Confidential: Schematic DocumentDocument7 pagesDell/Compal Confidential: Schematic Documentsantiago rodriguezNo ratings yet

- Acer Aspire 5742 Series-Gateway NV55C Series (PEW71 LA-6582P)Document48 pagesAcer Aspire 5742 Series-Gateway NV55C Series (PEW71 LA-6582P)Geoffrey M. Gitau0% (1)

- Ksj Ethercat Fpga Master 【Introduction】Document4 pagesKsj Ethercat Fpga Master 【Introduction】Andres LNo ratings yet

- BCM21331Document2 pagesBCM21331pavlodeNo ratings yet

- Sata Ide 2 ManualDocument10 pagesSata Ide 2 ManualSor MiNo ratings yet

- KB3930 ENEerDocument199 pagesKB3930 ENEerJuan Carlos Guerra MansoNo ratings yet

- Precision 5820 Tower Spec SheetDocument6 pagesPrecision 5820 Tower Spec Sheetbonsai todayNo ratings yet

- Lenovo Yoga 700-14isk Byg43 Nm-A601 Rev 1.0 PDFDocument46 pagesLenovo Yoga 700-14isk Byg43 Nm-A601 Rev 1.0 PDFA Meza BautiztaNo ratings yet

- BIOS 98 Release Notes PDFDocument37 pagesBIOS 98 Release Notes PDFliberthNo ratings yet

- Cable Schedule - ST OXD - RP Rev 1Document2 pagesCable Schedule - ST OXD - RP Rev 1mukesh_kht1No ratings yet

- Is Iec 60794 1 1 2001Document18 pagesIs Iec 60794 1 1 2001Anonymous P2Kij3LjHgNo ratings yet

- Sanyo Em-800t Ts SMDocument13 pagesSanyo Em-800t Ts SMNarci EdsonNo ratings yet

- Strugtwel Designers Consultants: Witfi z.4RxDocument2 pagesStrugtwel Designers Consultants: Witfi z.4RxSandesh JidewarNo ratings yet

- Theory of Automata RE 3Document13 pagesTheory of Automata RE 3Jaleed AbdullahNo ratings yet

- Beyond HDTV Technology: Srećko Kunić, Zoran ŠegoDocument5 pagesBeyond HDTV Technology: Srećko Kunić, Zoran ŠegoAntonioCastilloNo ratings yet

- 08 Power System Transients (KP)Document68 pages08 Power System Transients (KP)Prabu KumarNo ratings yet

- Java Web Services Using Apache Axis2Document24 pagesJava Web Services Using Apache Axis2kdorairajsgNo ratings yet

- 1 E1 - ESPIRITU Darwin James CDocument2 pages1 E1 - ESPIRITU Darwin James CJames tyler SmithNo ratings yet

- Linux - File PermissionDocument16 pagesLinux - File PermissionSatyajeet GaurNo ratings yet

- Computer Science Unit 1Document20 pagesComputer Science Unit 1arunNo ratings yet

- Database Design & ManagementDocument45 pagesDatabase Design & ManagementyohoNo ratings yet

- RHCSA Sa1 2 EXAM Questions (1) 1Document23 pagesRHCSA Sa1 2 EXAM Questions (1) 1hosnitmiNo ratings yet

- BiomguideDocument13 pagesBiomguideRajeshJosephAbrahamEdasseriathuNo ratings yet

- Blairstown OPRA FormDocument2 pagesBlairstown OPRA FormThe Citizens CampaignNo ratings yet

- Timeline Service v2.0 Reader Not Starting - HortonworksDocument3 pagesTimeline Service v2.0 Reader Not Starting - HortonworksMario SoaresNo ratings yet

- Rosen Integrity Solutions Managing The Integrity of Pipeline AssetsDocument9 pagesRosen Integrity Solutions Managing The Integrity of Pipeline AssetsBrandon Holder100% (1)

- Risk of Material Misstatement Worksheet - Overview General InstructionsDocument26 pagesRisk of Material Misstatement Worksheet - Overview General InstructionswellawalalasithNo ratings yet

- UtilitiesDocument569 pagesUtilitiesGaurav ShindeNo ratings yet

- 1.1 01 - Objective Mapping - Safety and Professionalism - A+ Chapter 1 PDFDocument2 pages1.1 01 - Objective Mapping - Safety and Professionalism - A+ Chapter 1 PDFFlippencioNo ratings yet

- Free Download Data Science Concepts and Practice Vijay Kotu Bala Deshpande Full Chapter PDFDocument51 pagesFree Download Data Science Concepts and Practice Vijay Kotu Bala Deshpande Full Chapter PDFanna.rather228100% (16)

- Heizer Om10 ModbDocument48 pagesHeizer Om10 ModbbsaNo ratings yet

- Akuvox E11R Datasheet - 20200220 - V2.2Document2 pagesAkuvox E11R Datasheet - 20200220 - V2.2hadiNo ratings yet

- Workshop Practice: Diploma of Associate EngineerDocument2 pagesWorkshop Practice: Diploma of Associate EngineerM Shumraiz SharifNo ratings yet

- Dual Axis Solar Panel ComponentsDocument11 pagesDual Axis Solar Panel ComponentsRaj Kothari MNo ratings yet

- CCIB Examination Paper Set-3: Read The Questions Properly and Then Answer .Marks Are Given For Each Correct StepDocument6 pagesCCIB Examination Paper Set-3: Read The Questions Properly and Then Answer .Marks Are Given For Each Correct StepNILANJANA PAHARINo ratings yet

- How To Create Position Hierarchy by Using ApisDocument6 pagesHow To Create Position Hierarchy by Using ApisrtagarraNo ratings yet

- HP P6000 Performance Advisor User Guide PDFDocument184 pagesHP P6000 Performance Advisor User Guide PDFADM HOSTCoNo ratings yet

- HB Acv2 Parallel enDocument156 pagesHB Acv2 Parallel enrobertoNo ratings yet

88E6393X Development Board User Manual

88E6393X Development Board User Manual

Uploaded by

wxzcldw163.comOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

88E6393X Development Board User Manual

88E6393X Development Board User Manual

Uploaded by

wxzcldw163.comCopyright:

Available Formats

User Manual

.

td

88E6393X Development Board

., L

User Manual

3ytp157jcr0i1tfe28kup6k0am0e4lviry3y-jr652rci * Maxvision Technology Co., Ltd. * UNDER NDA# 12165457

Co

gy

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

57 olo

1. Introduction

54 n

16 ch

The Marvell® 88E6393X, 88E6193X, and 88E6191X are a family of pin compatible devices that are single-chip

12 n Te

11-port Ethernet switches with eight 10/100/1000 PHY’s and three SERDES. The development board is intended

to provide a design example and facilitate the evaluation of this family of products.

A# sio

ND xvi

2. Overview

E R Ma

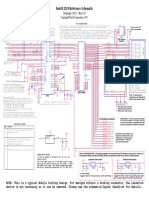

Refer to Figure 1 for the development board connector positions.

ND i *

, U 2rc

Figure 1: 88E6393X Development Board

AL 65

TI -jr

SMI AUX PORT

EN 3y

.

td

ID iry

5-12 VDC

USB2SMI

., L

NF e4lv

Port 0 Port 10 Port 9

Co

SERDES SERDES SERDES

COm0

g y

57 olo

LL 0a

VE p6k

54 n

16 ch

AR u

12 n Te

M 28k

A# sio

fe

1t

ND xvi

0i

cr

ER Ma

MDC_PHY

7j

MDIO_PHY

15

ND i *

, U 2rc

tp

3y

AL 65

TI -jr

EN 3y

ID iry

NF e4lv

COm0

LL 0a

VE p6k

AR u

M 28k

Port 0 RGMII Port 1 – Port 8 1000BASE-T integrated PHYs

tfe

88E1510 - MAGJACK

i1

r0

http://www.marvell.com

jc

7

Copyright © 2019 Marvell Confidential Doc. No. MV-L101220-10 Rev.--

15

January 16, 2019 Document Classification: Proprietary Information Page 1

tp

3y

.

td

., L

3ytp157jcr0i1tfe28kup6k0am0e4lviry3y-jr652rci * Maxvision Technology Co., Ltd. * UNDER NDA# 12165457

Co

88E6393X Development Board User Manual

gy

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

57 olo

Depending on the features required to support a given application, the same PCB design can support the

88E6393X, 88E6193X, or 88E6191X as the devices are pin compatible. Port 0 is configured in RGMII mode and

54 n

16 ch

connected to an 88E1510 transceiver. The internal PHY Polling unit will monitor the link state of the external

PHYs through the SMI PHY interface and configure the associated MAC in the switch for the correct operation

12 n Te

needed for a given link partner.

A# sio

3. Development Board Connectors and Switches

ND xvi

E R Ma

All the dip switches and SMA connectors are clearly labeled on the board. Refer to Table 1 through Table 4 for

switch and connector functions.

ND i *

Table 1: Connectors

, U 2rc

AL 65

Connector Connector Type Interface

Reference

TI -jr

Designator

EN 3y

.

td

Port 0 RGMII RJ-45 with Integrated 10BASE-T / 100BASE-TX / 1000BASE-T connection to

ID iry

., L

Magnetics 88E1510 via 3.3V RGMII interface.

NF e4lv

Ports 1 - 8 RJ-45 with Discrete Magnetics 10BASE-T / 100BASE-TX / 1000BASE-T connection to

Co

internal PHYs

COm0

y

Port 9 SERDES SFP+

g

Port 10 SERDES

57 olo

LL 0a

Port 0 SERDES SFP+ USXGMII, 10GBASE-R, 5GBASE-R, 2500BASE-

VE p6k

54 n

X,1000BASE-X, SGMII

16 ch

Note Port 0 can be used in RGMII mode or SERDES

AR u

12 n Te

Mode. By Default, Port 0 is configured in RGMII mode.

M 28k

Port 0 can be changed to SERDES mode by changing

C_MODE in port register 0x0

A# sio

fe

Aux SMI RJ-11 Used with the Marvell GUI to connect to customer board

1t

ND xvi

to assist with debugging or for an external CPU to

0i

manage the Switch. See Section 3.1 for more

cr

ER Ma

information.

7j

15

ND i *

When the USB interface is connected to a USB host,

, U 2rc

tp

This connector is connected to Channel 2 of on-board

3y

USB-2-SMI adaptor

AL 65

TI -jr

When the USB interface is not connected to a powered

EN 3y

host this connector is connected MDC_CPU and

ID iry

MDIO_CPU via relays.

SMI_PHY RJ-11 Connected to MDC_PHY and MDIO_PHY. This is used

NF e4lv

when an external PHY needs to be managed via the

switch.

COm0

USB USB Type B This interface is used to connect for the Marvell

Proprietary USB-2-SMI adaptor, it can be used with a PC

LL 0a

running Microsoft Windows or Linux Operating System.

VE p6k

The USB-2-SMI adaptor exposes two master SMI

AR u

busses. Channel 1 is connected to the 88E6393X

M 28k

Channel 2 is connected to the Aux SMI.

5-12 VDC Standard DC power connector Main power to the development board.

tfe

i1

r0

jc

7

Doc. No. MV-L101220-10 Rev.-- Confidential Copyright © 2019 Marvell

15

Page 2 Document Classification: Proprietary Information January 16, 2019

tp

3y

.

td

., L

3ytp157jcr0i1tfe28kup6k0am0e4lviry3y-jr652rci * Maxvision Technology Co., Ltd. * UNDER NDA# 12165457

Co

88E6393X Development Board User Manual

gy

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

57 olo

Table 2: Switch 3, Eight Position Dip Switch

54 n

Dip Switch Mode Mode Definition

16 ch

Position

12 n Te

POSITION [8:7] S_MODE[1:0] SMODE for Port 9 and Port 10.

Off = 1

A# sio

On = 0

ND xvi

The SMODE is set after the board is reset. The

mode of Port 9 and Port 10 is set together. These

E R Ma

can be changed by changing the C_MODE in port

Register 0x0 via the switch GUI.

ND i *

POSITION [6:5] ADDR[1:0]n

, U 2rc Configures SMI address of switch.

Off = 1

AL 65

On = 0

When SMI address = 0 The Board is configured in

TI -jr

Single chip Addressing mode

EN 3y

.

td

When Switch 6:5 are set to:

ID iry

., L

Off/Off = The device will be configured to address

NF e4lv

0x00 (Single chip Addressing Mode)

Co

Off/On = 0x01

On/Off = 0x02

COm0

g y

On/On = 0x03

57 olo

LL 0a

POSITION 4 Not Used

VE p6k

POSITION 3 LED_SEL Selects one of two preset LED modes.

54 n

16 ch

Off = LED Config = 0x3

AR u

12 n Te

On = LED Config = 0x2

M 28k

Refer to Table 6 and Table 7 for details.

LED modes can be changed with register access.

A# sio

fe

POSITION 2 SW-24P Configures device for three chip ring topologies for

1t

ND xvi

which Ports 9 and 10 are used to establish the ring.

0i

cr

Off = SW-24P is disabled

ER Ma

On = SW-24P is enabled

7j

15

ND i *

POSITION 1 FLOW Configures the internal PHYs to advertise Flow

, U 2rc

Control via PHY Page 0, Register 4 bit 10

tp

Off = Do not advertise Flow Control

3y

AL 65

On = Advertise Flow Control

TI -jr

EN 3y

Table 3: Switch 2, One Position Slide Switch

ID iry

Mode Mode Definition

NF e4lv

CPU_MGD CPU managed mode.

On = 1

COm0

Off = 0

LL 0a

When CPU managed is 1 after reset, all the internal PHYs will be in a

powered down state (Page 0, Register 0 bit 11 =1). The SERDES cores

VE p6k

will be in a Power-Down state (Device 4 register 0x1000=1). All ports will

be in a PortState = Disabled (Port Register Offset 0x4 bits 1:0 = b’11)

AR u

M 28k

tfe

i1

r0

jc

7

Copyright © 2019 Marvell Confidential Doc. No. MV-L101220-10 Rev.--

15

January 16, 2019 Document Classification: Proprietary Information Page 3

tp

3y

.

td

., L

3ytp157jcr0i1tfe28kup6k0am0e4lviry3y-jr652rci * Maxvision Technology Co., Ltd. * UNDER NDA# 12165457

Co

88E6393X Development Board User Manual

gy

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

57 olo

Table 4: SMA Connectors

54 n

Connector Connector Function

16 ch

GPIO9 - GPIO12 Multi-purpose pins that can be used for programable functions.

12 n Te

SE_SCLK 25 MHz Clock input from clock synchronous Ethernet clock source.

A# sio

3.1. I/O Interfaces

ND xvi

E R Ma

Auxiliary SMI

This board includes an Auxiliary SMI interface that can be connected to a customer board or a Management

ND i *

device. This allows the Marvell SwitchGUI to aid in debug and bring up of new designs using the device.

, U 2rc

AL 65

The port will operate in one of two modes depending on whether the development board is connected to a host

PC:

TI -jr

EN 3y

.

td

• If the development board is connected to a PC, Port 1 of the onboard USB-2-SMI adapter is connected

ID iry

., L

to the 88E6393X and Port 2 is connected to the AUX_SMI jack.

NF e4lv

Co

• If the development board’s USB Connector is not connected to a PC (i.e., no power), then the board

COm0

y

goes into USB Bypass mode and connects the AUX_SMI connector to the 88E6390X device’s

g

MDC_CPU/MDIO_CPU interface. This is to allow an external processor to manage the board modifying

57 olo

LL 0a

the board.

VE p6k

54 n

16 ch

The RJ-11 has the following pinout when used with the onboard USB-2-SMI adapter:

AR u

12 n Te

PIN Signal

M 28k

2 MDIO

A# sio

fe

3, 4 Signal Ground

1t

5 MDC ND xvi

0i

cr

ER Ma

When in USB Bypass mode the connector is configured as:

7j

PIN Signal

15

ND i *

2 MDC

, U 2rc

tp

3, 4 Signal Ground

5 MDIO

3y

AL 65

TI -jr

WARNING: While managing the board in USB Bypass mode, do not connect the USB cable.

EN 3y

Connecting the USB cable will connect the USB-2-SMI adapter to the external management device and

ID iry

may damage one or both devices.

NF e4lv

The Auxiliary SMI interface uses 3.3V I/O. Please use care when connecting to another board to ensure

that its corresponding MDC/MDIO interface also uses 3.3V I/O. The Auxiliary SMI connection is

COm0

accessed via SMI Port 2.

LL 0a

PHY SMI RJ-11

VE p6k

PHY SMI connector can be used to connect an external PHY MDC_PHY and MDIO_PHY. If the PHY has a

AR u

standard IEEE defined Clause 22 register interface it can be managed by the PPU. If the PHY has a non-

M 28k

standard register interface, it can be managed by firmware running on the Internal Management processer (IMP)

or a CPU.

tfe

i1

r0

jc

7

Doc. No. MV-L101220-10 Rev.-- Confidential Copyright © 2019 Marvell

15

Page 4 Document Classification: Proprietary Information January 16, 2019

tp

3y

.

td

., L

3ytp157jcr0i1tfe28kup6k0am0e4lviry3y-jr652rci * Maxvision Technology Co., Ltd. * UNDER NDA# 12165457

Co

88E6393X Development Board User Manual

gy

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

57 olo

4. Cables

54 n

16 ch

One or more cables are required in order to use the development board. A listing of the appropriate cable for

12 n Te

each connector type is indicated in Table 5.

A# sio

Table 5: 88E6320/88E6321 Development Board Cables

ND xvi

Connector Type Cable

RJ-45 Straight, Category 5 (CAT5), Unshielded Twisted Pair (UTP), with RJ-45 plug

E R Ma

ends

Power DC power, 5V, positive polarity supplied to the center pin

ND i *

USB slave port USB 2.0 A/B cables

, U 2rc

AL 65

TI -jr

EN 3y

.

td

ID iry

., L

NF e4lv

Co

COm0

g y

57 olo

LL 0a

VE p6k

54 n

16 ch

AR u

12 n Te

M 28k

A# sio

fe

1t

ND xvi

0i

cr

ER Ma

7j

15

ND i *

, U 2rc

tp

3y

AL 65

TI -jr

EN 3y

ID iry

NF e4lv

COm0

LL 0a

VE p6k

AR u

M 28k

tfe

i1

r0

7 jc

Copyright © 2019 Marvell Confidential Doc. No. MV-L101220-10 Rev.--

15

January 16, 2019 Document Classification: Proprietary Information Page 5

tp

3y

.

td

., L

3ytp157jcr0i1tfe28kup6k0am0e4lviry3y-jr652rci * Maxvision Technology Co., Ltd. * UNDER NDA# 12165457

Co

88E6393X Development Board User Manual

gy

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

57 olo

5. Switches and LEDs

54 n

16 ch

5.1. Power and Fuses

12 n Te

Power is supplied to the development board via the DC power jack, J3. A 5V, 3.0A minimum, DC power supply

is required. LED D30 indicates power is present at the power jack. A 5A fuse (F1) links the power jack and the

A# sio

on-board 5V power net.

ND xvi

NOTE: if F1 is blown, LED D30 will not illuminate even if power is present at J3.

E R Ma

5.2. LEDs

ND i *

, U 2rc

The 88E6390X switch features 20 LED’s and has user configurable LED modes. The two default modes are

configured by hardware configuration (LED_SEL). Table 6 and Table 7 show the default behavior of each LED

AL 65

based on the settings of SW11 [2:1].

TI -jr

EN 3y

.

td

Table 6: SW11 [1] = [OFF] (LED Config = 0x3)

ID iry

., L

C0_LED C1_LED C2_LED C3_LED

NF e4lv

Co

R0_LED Port 1 Link/Activity Port 1 Gig Link Port 2 Link/Activity Port 2 Gig Link

R1_LED Port 3 Link/Activity Port 3 Gig Link Port 4 Link/Activity Port 4 Gig Link

COm0

y

R2_LED Port 5 Link/Activity Port 5 Gig Link Port 6 Link/Activity Port 6 Gig Link

g

57 olo

R3_LED Port 7 Link/Activity Port 7 Gig Link Port 8 Link/Activity Port 8 Gig Link

LL 0a

R4_LED Special LED 1 Special LED 4 Special LED 2 Special LED 3

VE p6k

54 n

LAN Link/Activity PTP Activity WAN Link/Activity CPU Link/Activity

16 ch

AR u

12 n Te

M 28k

Table 7: SW11 [1] = [ON] (LED Config = 0x2)

A# sio

fe

C0_LED C1_LED C2_LED C3_LED

1t

R0_LED Port 1 Gig Port 1 10/100 ND xvi

Port 2 Gig Port 2 10/100

0i

Link/Activity Link/Activity Link/Activity Link/Activity

cr

ER Ma

R1_LED Port 3 Gig Port 3 10/100 Port 4 Gig Port 4 10/100

7j

Link/Activity Link/Activity Link/Activity Link/Activity

15

ND i *

R2_LED Port 5 Gig Port 5 10/100 Port 6 Gig Port 6 10/100

, U 2rc

tp

Link/Activity Link/Activity Link/Activity Link/Activity

3y

R3_LED Port 7 Gig Port 7 10/100 Port 8 Gig Port 8 10/100

AL 65

Link/Activity Link/Activity Link/Activity Link/Activity

TI -jr

R4_LED Special LED 3 Special LED 2 Special LED 4 Special LED 1

EN 3y

CPU Link/Activity WAN Link/Activity PTP Activity LAN Link/Activity

ID iry

NF e4lv

INTn LED

The INTn LED is connected to the INTn signal. The LED will be turned on when there is an un-serviced interrupt.

COm0

By default, the INTn LED will light up after the board is reset. This indicates the EEDone interrupt has been

posted and is cleared as soon. The EE_DONE interrupt can be cleared by reading Global 2 Offset 0x13.

LL 0a

VE p6k

SERDES LEDs

AR u

Each SFP+ cage has an LED which indicates that there is a module inserted.

M 28k

tfe

i1

r0

jc

7

Doc. No. MV-L101220-10 Rev.-- Confidential Copyright © 2019 Marvell

15

Page 6 Document Classification: Proprietary Information January 16, 2019

tp

3y

.

td

., L

3ytp157jcr0i1tfe28kup6k0am0e4lviry3y-jr652rci * Maxvision Technology Co., Ltd. * UNDER NDA# 12165457

Co

88E6393X Development Board User Manual

gy

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

57 olo

6. EEPROM

54 n

16 ch

The development board has an on-board socket labeled U5 can accommodate a 2-wire serial Electrically

12 n Te

Erasable Programmable Memory (EEPROM). The EEPROM can be used to load an operating image into the

Internal Management processor. Supported EEPROM families include: 24C64, 24C128, 24C256, 24C512.

A# sio

Similar devices from different manufacturers may also be used. The Marvell IMPGui is the only supported

method for developing EEPROM code. Most CPU managed applications do not require an EEPROM image.

ND xvi

E R Ma

Another EEPROM labeled U16 is used for the USB circuitry. Do not change the contents of this EEPROM as the

USB circuitry will not function properly unless otherwise instructed.

ND i *

, U 2rc

This chip is capable of programming the EEPROM via switch registers. Please see the GUI users’ guide and the

Functional Specification for more information about programming the EEPROM.

AL 65

TI -jr

7. Software tools

EN 3y

.

td

ID iry

., L

The board can be managed from a standard Windows 7 or Windows 10 PC via the USB-2-SMI adaptor. The

NF e4lv

Co

following tools are available from extranet.marvell.com:

COm0

g y

Table 8: Marvell Switching Tools

57 olo

LL 0a

Tool Description Extranet Folder

VE p6k

54 n

SwitchGUI A graphical user interface that be

16 ch

My Products Switching Link Street

used to access switch registers Data

AR u

12 n Te

M 28k

Structures and counters SOHO Switch Family SwitchGUI

IMPGui Integrated Development Environment

A# sio

fe

My Products Switching Link Street

for EEPROM code and operating

1t

images ND xvi

SOHO Switch Family Gigabit Ethernet

0i

UMSD_MCLI A command line interface built over

cr

Switches 88E6393X/88E6193X/88E6191X

ER Ma

UMSD driver package

7j

UMSD An OS independent driver package (Amethyst) Software

15

ND i *

used for configurating the switch and

, U 2rc

tp

accessing data structures.

3y

AL 65

TI -jr

EN 3y

ID iry

NF e4lv

COm0

LL 0a

VE p6k

AR u

M 28k

tfe

i1

r0

jc

7

Copyright © 2019 Marvell Confidential Doc. No. MV-L101220-10 Rev.--

15

January 16, 2019 Document Classification: Proprietary Information Page 7

tp

3y

.

td

., L

3ytp157jcr0i1tfe28kup6k0am0e4lviry3y-jr652rci * Maxvision Technology Co., Ltd. * UNDER NDA# 12165457

Co

88E6393X Development Board User Manual

gy

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

57 olo

54 n

16 ch

12 n Te

A# sio

ND xvi

E R Ma

ND i *

, U 2rc

AL 65

TI -jr

EN 3y

.

td

ID iry

., L

NF e4lv

Co

COm0

g y

57 olo

LL 0a

VE p6k

54 n

16 ch

AR u

12 n Te

M 28k

A# sio

fe

1t

ND xvi

0i

cr

ER Ma

7j

15

ND i *

, U 2rc

tp

3y

AL 65

TI -jr

EN 3y

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the

express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any kind, expressed or implied,

ID iry

with regard to any information contained in this document, including, but not limited to, the implied warranties of merchantability or fitness for any particular purpose. Further, Marvell does

not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document.

NF e4lv

Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use Marvell products in

these types of equipment or applications.

With respect to the products described herein, the user or recipient, in the absence of appropriate U.S. government authorization, agrees:

1) Not to re-export or release any such information consisting of technology, software or source code controlled for national security reasons by the U.S. Export Control Regulations

COm0

("EAR"), to a national of EAR Country Groups D:1 or E:2;

2) Not to export the direct product of such technology or such software, to EAR Country Groups D:1 or E:2, if such technology or software and direct products thereof are controlled for

LL 0a

national security reasons by the EAR; and,

3) In the case of technology controlled for national security reasons under the EAR where the direct product of the technology is a complete plant or component of a plant, not to export to

VE p6k

EAR Country Groups D:1 or E:2 the direct product of the plant or major component thereof, if such direct product is controlled for national security reasons by the EAR, or is subject to

controls under the U.S. Munitions List ("USML").

At all times hereunder, the recipient of any such information agrees that they shall be deemed to have manually signed this document in connection with their receipt of any such

AR u

information.

M 28k

Copyright © 2019. Marvell International Ltd. All rights reserved. Marvell and the Marvell logo are registered trademarks of Marvell. For a more complete listing of Marvell trademarks, visit

www.marvell.com.

Patent(s) Pending - Products identified in this document may be covered by one or more Marvell patents and/or patent applications.

tfe

i1

r0

7 jc

Doc. No. MV-L101220-10 Rev.-- Confidential Copyright © 2019 Marvell

15

Page 8 Document Classification: Proprietary Information January 16, 2019

tp

3y

You might also like

- Cambridge Audio Azur 851a Service ManualDocument75 pagesCambridge Audio Azur 851a Service ManualDavid NicolasNo ratings yet

- 4706 DS00 R BCM4706 Advance Data Sheet NDA ClearDocument62 pages4706 DS00 R BCM4706 Advance Data Sheet NDA Clearbb06412000No ratings yet

- Business Requirements For : Revision HistoryDocument16 pagesBusiness Requirements For : Revision HistoryVenkata Madhusudana Reddy BhumaNo ratings yet

- La C621P PDFDocument60 pagesLa C621P PDFJerzy LisowskiNo ratings yet

- Aspire Z1-612 SchematicDocument108 pagesAspire Z1-612 SchematicRakesh Singh100% (2)

- DS D3041-ADocument2 pagesDS D3041-AvagusdisarmNo ratings yet

- Microphone ConnectorsDocument49 pagesMicrophone ConnectorsAntonio José Ervilha Regalo100% (1)

- Change Request Form SAP Business OneDocument2 pagesChange Request Form SAP Business OneMarcin Orgacki100% (2)

- iOS 11 (2018)Document3 pagesiOS 11 (2018)jadi gini, nah gituNo ratings yet

- Marvell Phys Transceivers Alaska 88e151x Datasheet 2018 02 PDFDocument154 pagesMarvell Phys Transceivers Alaska 88e151x Datasheet 2018 02 PDFanhxcoNo ratings yet

- Intel Ethernet Connection I219 Reference Schematic Rev1 0Document1 pageIntel Ethernet Connection I219 Reference Schematic Rev1 0Смартфон СигмаNo ratings yet

- Intel (R) ME SW Installation GuideDocument31 pagesIntel (R) ME SW Installation Guidearvinarvind60No ratings yet

- ASM1053 Datasheet v0.5Document18 pagesASM1053 Datasheet v0.5Enrique PalacioNo ratings yet

- DAM00 DAM01 LA-F541P R20 - 3PH MB-20180328 Coffee Lake-HDocument75 pagesDAM00 DAM01 LA-F541P R20 - 3PH MB-20180328 Coffee Lake-HDude JonesNo ratings yet

- Marvell Phys Transceivers Alaska 88e1111 Technical Product Brief 2013 10Document56 pagesMarvell Phys Transceivers Alaska 88e1111 Technical Product Brief 2013 10Brijesh ShahNo ratings yet

- 88E1111 Datasheet: Integrated 10/100/1000 Ultra Gigabit Ethernet TransceiverDocument252 pages88E1111 Datasheet: Integrated 10/100/1000 Ultra Gigabit Ethernet TransceiverNicholas MoodyNo ratings yet

- 88E1111 SFP RefDsgn Schematics Rev 1 0newDocument3 pages88E1111 SFP RefDsgn Schematics Rev 1 0newKukla LossNo ratings yet

- Intel - Serial IO - Bring Up Guide and Release Note Rev1.0Document25 pagesIntel - Serial IO - Bring Up Guide and Release Note Rev1.0Nurfatini CheNo ratings yet

- 1 5MB FW Release Notes 7 1 52 1176 HFDocument60 pages1 5MB FW Release Notes 7 1 52 1176 HFEko Billy SetiawanNo ratings yet

- Intel Serial IO - Bring Up Guide and Release Note Rev1p0Document30 pagesIntel Serial IO - Bring Up Guide and Release Note Rev1p0gdfeiu dionwdnNo ratings yet

- Intel (R) MEBX User Guide PDFDocument57 pagesIntel (R) MEBX User Guide PDFBlubNo ratings yet

- DH67GD DH67BL TechProdSpecDocument92 pagesDH67GD DH67BL TechProdSpecjagan2003No ratings yet

- JMB585 PDFDocument10 pagesJMB585 PDFBono PrakosoNo ratings yet

- Rev: A: ECS ConfidentialDocument37 pagesRev: A: ECS ConfidentialEdgar Geovanny Varela MoralesNo ratings yet

- Intel Smart Connect Technology: Setup & Configuration GuideDocument44 pagesIntel Smart Connect Technology: Setup & Configuration GuideChhoemSovannNo ratings yet

- Intel (R) Serial IO - Bring Up Guide and Release Note Rev1p1Document25 pagesIntel (R) Serial IO - Bring Up Guide and Release Note Rev1p1YomaraNoemiPalmaAguirreNo ratings yet

- Coffee Lake H/S Platform System Memory Interface: Technical White PaperDocument51 pagesCoffee Lake H/S Platform System Memory Interface: Technical White PaperagxinNo ratings yet

- Intel (R) ME SW Installation GuideDocument36 pagesIntel (R) ME SW Installation GuideJesús Gildardo Mejía CortésNo ratings yet

- MB Manual Ga-z87x-Ud3h eDocument124 pagesMB Manual Ga-z87x-Ud3h ejazz240% (1)

- 1.5MB FW Bring Up Guide 8.1.0.1248 PVDocument131 pages1.5MB FW Bring Up Guide 8.1.0.1248 PVjorge bernalNo ratings yet

- MB Manual Ga-Z87 (h87) - Hd3 eDocument100 pagesMB Manual Ga-Z87 (h87) - Hd3 estarlaysNo ratings yet

- Manual Gigabyte Ga z87 d3hpDocument104 pagesManual Gigabyte Ga z87 d3hpslade3No ratings yet

- HX8398 PDFDocument293 pagesHX8398 PDFBayan MashrequiNo ratings yet

- VSCCommn - Bin Content 4.8.0Document14 pagesVSCCommn - Bin Content 4.8.0Uncle KnownNo ratings yet

- Fab A: Cpu: System Chipset: Main Memory: On Board DeviceDocument46 pagesFab A: Cpu: System Chipset: Main Memory: On Board DeviceFlavianoSilva100% (1)

- Dell Alienwarem 15 r2 Compal Edq51 La-H351p La-F552p La-F553p 1.0 (Xa00)Document109 pagesDell Alienwarem 15 r2 Compal Edq51 La-H351p La-F552p La-F553p 1.0 (Xa00)ml5801088No ratings yet

- Marvell Data SheetDocument4 pagesMarvell Data Sheetkrishnaec82No ratings yet

- JM20337 Datasheet v1.1Document15 pagesJM20337 Datasheet v1.1Mehmet DemirNo ratings yet

- Client BIOS 2012 CRB BIOS 98 Release Notes PDFDocument37 pagesClient BIOS 2012 CRB BIOS 98 Release Notes PDFUnfaithful AngelNo ratings yet

- Msi H81m-E33 MS-7817 Rev. 1.0Document32 pagesMsi H81m-E33 MS-7817 Rev. 1.0GudangNo ratings yet

- Intel Converged Security and Management Engine Software: Installation and Configuration GuideDocument34 pagesIntel Converged Security and Management Engine Software: Installation and Configuration GuideJailson Da SilvaNo ratings yet

- 3 - H5-Training Manual (LCD) - 080410Document37 pages3 - H5-Training Manual (LCD) - 080410Jorge Fernando de TivantaNo ratings yet

- Gigabyte Confidential Do Not Copy: Model Name: GA-TG965MP-RH-GWDocument36 pagesGigabyte Confidential Do Not Copy: Model Name: GA-TG965MP-RH-GWSjf NetNo ratings yet

- Acer Aspire One 522 AO522 - COMPAL LA-7072P - REV 1.0sec PDFDocument36 pagesAcer Aspire One 522 AO522 - COMPAL LA-7072P - REV 1.0sec PDFMcgregori AndradeNo ratings yet

- VUTEk ColorBurst 7.5 User ManualDocument172 pagesVUTEk ColorBurst 7.5 User ManualPaulo Alberto100% (1)

- Ds NV Quadro k1200 Feb15 NV Us HRDocument1 pageDs NV Quadro k1200 Feb15 NV Us HRJose PazNo ratings yet

- MB Manual Ga-G41mt-S2pt e PDFDocument40 pagesMB Manual Ga-G41mt-S2pt e PDFLeonel AtaramaNo ratings yet

- Toshiba 32av700e LCD TV SCHDocument44 pagesToshiba 32av700e LCD TV SCHMuhammad Ihsan100% (1)

- NES Famicom PinoutsDocument1 pageNES Famicom PinoutsgbyudbyNo ratings yet

- Manual Service 50UHD 9M32BDocument44 pagesManual Service 50UHD 9M32BOfelia GiménezNo ratings yet

- Dell/Compal Confidential: Schematic DocumentDocument7 pagesDell/Compal Confidential: Schematic Documentsantiago rodriguezNo ratings yet

- Acer Aspire 5742 Series-Gateway NV55C Series (PEW71 LA-6582P)Document48 pagesAcer Aspire 5742 Series-Gateway NV55C Series (PEW71 LA-6582P)Geoffrey M. Gitau0% (1)

- Ksj Ethercat Fpga Master 【Introduction】Document4 pagesKsj Ethercat Fpga Master 【Introduction】Andres LNo ratings yet

- BCM21331Document2 pagesBCM21331pavlodeNo ratings yet

- Sata Ide 2 ManualDocument10 pagesSata Ide 2 ManualSor MiNo ratings yet

- KB3930 ENEerDocument199 pagesKB3930 ENEerJuan Carlos Guerra MansoNo ratings yet

- Precision 5820 Tower Spec SheetDocument6 pagesPrecision 5820 Tower Spec Sheetbonsai todayNo ratings yet

- Lenovo Yoga 700-14isk Byg43 Nm-A601 Rev 1.0 PDFDocument46 pagesLenovo Yoga 700-14isk Byg43 Nm-A601 Rev 1.0 PDFA Meza BautiztaNo ratings yet

- BIOS 98 Release Notes PDFDocument37 pagesBIOS 98 Release Notes PDFliberthNo ratings yet

- Cable Schedule - ST OXD - RP Rev 1Document2 pagesCable Schedule - ST OXD - RP Rev 1mukesh_kht1No ratings yet

- Is Iec 60794 1 1 2001Document18 pagesIs Iec 60794 1 1 2001Anonymous P2Kij3LjHgNo ratings yet

- Sanyo Em-800t Ts SMDocument13 pagesSanyo Em-800t Ts SMNarci EdsonNo ratings yet

- Strugtwel Designers Consultants: Witfi z.4RxDocument2 pagesStrugtwel Designers Consultants: Witfi z.4RxSandesh JidewarNo ratings yet

- Theory of Automata RE 3Document13 pagesTheory of Automata RE 3Jaleed AbdullahNo ratings yet

- Beyond HDTV Technology: Srećko Kunić, Zoran ŠegoDocument5 pagesBeyond HDTV Technology: Srećko Kunić, Zoran ŠegoAntonioCastilloNo ratings yet

- 08 Power System Transients (KP)Document68 pages08 Power System Transients (KP)Prabu KumarNo ratings yet

- Java Web Services Using Apache Axis2Document24 pagesJava Web Services Using Apache Axis2kdorairajsgNo ratings yet

- 1 E1 - ESPIRITU Darwin James CDocument2 pages1 E1 - ESPIRITU Darwin James CJames tyler SmithNo ratings yet

- Linux - File PermissionDocument16 pagesLinux - File PermissionSatyajeet GaurNo ratings yet

- Computer Science Unit 1Document20 pagesComputer Science Unit 1arunNo ratings yet

- Database Design & ManagementDocument45 pagesDatabase Design & ManagementyohoNo ratings yet

- RHCSA Sa1 2 EXAM Questions (1) 1Document23 pagesRHCSA Sa1 2 EXAM Questions (1) 1hosnitmiNo ratings yet

- BiomguideDocument13 pagesBiomguideRajeshJosephAbrahamEdasseriathuNo ratings yet

- Blairstown OPRA FormDocument2 pagesBlairstown OPRA FormThe Citizens CampaignNo ratings yet

- Timeline Service v2.0 Reader Not Starting - HortonworksDocument3 pagesTimeline Service v2.0 Reader Not Starting - HortonworksMario SoaresNo ratings yet

- Rosen Integrity Solutions Managing The Integrity of Pipeline AssetsDocument9 pagesRosen Integrity Solutions Managing The Integrity of Pipeline AssetsBrandon Holder100% (1)

- Risk of Material Misstatement Worksheet - Overview General InstructionsDocument26 pagesRisk of Material Misstatement Worksheet - Overview General InstructionswellawalalasithNo ratings yet

- UtilitiesDocument569 pagesUtilitiesGaurav ShindeNo ratings yet

- 1.1 01 - Objective Mapping - Safety and Professionalism - A+ Chapter 1 PDFDocument2 pages1.1 01 - Objective Mapping - Safety and Professionalism - A+ Chapter 1 PDFFlippencioNo ratings yet

- Free Download Data Science Concepts and Practice Vijay Kotu Bala Deshpande Full Chapter PDFDocument51 pagesFree Download Data Science Concepts and Practice Vijay Kotu Bala Deshpande Full Chapter PDFanna.rather228100% (16)

- Heizer Om10 ModbDocument48 pagesHeizer Om10 ModbbsaNo ratings yet

- Akuvox E11R Datasheet - 20200220 - V2.2Document2 pagesAkuvox E11R Datasheet - 20200220 - V2.2hadiNo ratings yet

- Workshop Practice: Diploma of Associate EngineerDocument2 pagesWorkshop Practice: Diploma of Associate EngineerM Shumraiz SharifNo ratings yet

- Dual Axis Solar Panel ComponentsDocument11 pagesDual Axis Solar Panel ComponentsRaj Kothari MNo ratings yet

- CCIB Examination Paper Set-3: Read The Questions Properly and Then Answer .Marks Are Given For Each Correct StepDocument6 pagesCCIB Examination Paper Set-3: Read The Questions Properly and Then Answer .Marks Are Given For Each Correct StepNILANJANA PAHARINo ratings yet

- How To Create Position Hierarchy by Using ApisDocument6 pagesHow To Create Position Hierarchy by Using ApisrtagarraNo ratings yet

- HP P6000 Performance Advisor User Guide PDFDocument184 pagesHP P6000 Performance Advisor User Guide PDFADM HOSTCoNo ratings yet

- HB Acv2 Parallel enDocument156 pagesHB Acv2 Parallel enrobertoNo ratings yet