Professional Documents

Culture Documents

AIC Project PDF

AIC Project PDF

Uploaded by

uam22Copyright:

Available Formats

You might also like

- ECE 534 Project 1 F19Document6 pagesECE 534 Project 1 F19JAY CHHEDANo ratings yet

- OI For UT of Laminations-BasicDocument8 pagesOI For UT of Laminations-Basicperogami100% (1)

- ALSi User Guide v4 5Document72 pagesALSi User Guide v4 5cardiacanesthesiaNo ratings yet

- Design Project: (Due: Friday, December 8, 2006, 5pm PT)Document6 pagesDesign Project: (Due: Friday, December 8, 2006, 5pm PT)Ibrahim MuhammedNo ratings yet

- Aic Lab Cadence 11 Folded v02Document9 pagesAic Lab Cadence 11 Folded v02Hagar IlbheryNo ratings yet

- Frequency Response of A CMOS Common-Source Amplifier: Experiment # 5Document10 pagesFrequency Response of A CMOS Common-Source Amplifier: Experiment # 5Md. Sadique SheikhNo ratings yet

- ADVD Analog Assignment - 2023ssDocument36 pagesADVD Analog Assignment - 2023ssNimit JainNo ratings yet

- Final Exam CMPE 650: NameDocument10 pagesFinal Exam CMPE 650: NameFritzie LuayonNo ratings yet

- MAX5072/3 Switching Power Supply Clock ConfigurationDocument13 pagesMAX5072/3 Switching Power Supply Clock ConfigurationJc Jayamanikandan BNo ratings yet

- Lab 5 Multisim TutorialDocument9 pagesLab 5 Multisim TutorialMuhammad UbaidNo ratings yet

- Digital-to-Analogue Conversion: PHY 406F - Microprocessor Interfacing TechniquesDocument14 pagesDigital-to-Analogue Conversion: PHY 406F - Microprocessor Interfacing TechniquesMalou Ruiz DenolanNo ratings yet

- Aic Lab Cadence MM 07 gmID v01Document8 pagesAic Lab Cadence MM 07 gmID v01احمد علىNo ratings yet

- (ECEN 4797 and ECEN 5797) Two-Transistor Forward Converter: Modeling, Design and SimulationsDocument2 pages(ECEN 4797 and ECEN 5797) Two-Transistor Forward Converter: Modeling, Design and SimulationsMaharshiGohelNo ratings yet

- Unipolar To Bipolar Analog Voltage ConversionDocument20 pagesUnipolar To Bipolar Analog Voltage ConversionGautam MonipatroNo ratings yet

- DESG - CabDocument6 pagesDESG - CabJAY PARIKHNo ratings yet

- You Should Try To MinimizeDocument5 pagesYou Should Try To MinimizeSunwoo LeeNo ratings yet

- Land Use Services DepartmentDocument20 pagesLand Use Services DepartmentJesusSQANo ratings yet

- Lab 4 A Folded-Cascode Operational AmplifierDocument6 pagesLab 4 A Folded-Cascode Operational AmplifierJatinKumarNo ratings yet

- DAC AnalysisDocument19 pagesDAC Analysisమురళీధర్ ఆది ఆంధ్రుడుNo ratings yet

- Flyback Converter Design ThesisDocument8 pagesFlyback Converter Design Thesisleanneuhlsterlingheights100% (2)

- Inter Grating AdcDocument6 pagesInter Grating AdcthắngNo ratings yet

- Theory: Lab Session 07 Light Dimmer CircuitDocument3 pagesTheory: Lab Session 07 Light Dimmer CircuitAqeel HaiderNo ratings yet

- LM240WU7 SLA1 NDS CAS Ver 1 (1) (1) .0 090403Document34 pagesLM240WU7 SLA1 NDS CAS Ver 1 (1) (1) .0 090403jaygheezyNo ratings yet

- Understanding Integrating ADC AN1041Document7 pagesUnderstanding Integrating ADC AN1041dileepank14No ratings yet

- A 10b 100MS S 1.13mW SAR ADC With Binary-Scaled Error CompensationDocument3 pagesA 10b 100MS S 1.13mW SAR ADC With Binary-Scaled Error Compensation陳昀顥No ratings yet

- Understanding Integrating ADCsDocument5 pagesUnderstanding Integrating ADCsjulioNo ratings yet

- Ee414 The4Document1 pageEe414 The4Asif SiddiqueNo ratings yet

- A New, Low-Cost, Sampled-Data, 10-Bit CMOS A/D ConverterDocument6 pagesA New, Low-Cost, Sampled-Data, 10-Bit CMOS A/D Converteralgnben1746No ratings yet

- Analog Assignment ADVDDocument24 pagesAnalog Assignment ADVDRajeevDuttNo ratings yet

- Chapter 6 - Cmos Operational AmplifiersDocument79 pagesChapter 6 - Cmos Operational AmplifierssanjayorcaNo ratings yet

- CIS Final ProjectDocument4 pagesCIS Final Project王柏勛No ratings yet

- Design of Low Power 4-Bit Flash ADC Based On Standard Cells: Marcel Siadjine Njinowa, Hung Tien Bui François-Raymond BoyerDocument4 pagesDesign of Low Power 4-Bit Flash ADC Based On Standard Cells: Marcel Siadjine Njinowa, Hung Tien Bui François-Raymond BoyerSunil PandeyNo ratings yet

- Massachusetts Institute of Technology Department of Electrical Engineering and Computer ScienceDocument7 pagesMassachusetts Institute of Technology Department of Electrical Engineering and Computer ScienceFernando Sánchez HernándezNo ratings yet

- Transformer Less Power Supply For MicrocontrollersDocument11 pagesTransformer Less Power Supply For MicrocontrollersSentimental SagNo ratings yet

- 2020 IC Design Contest: Full-Custom CategoryDocument6 pages2020 IC Design Contest: Full-Custom CategoryE94086018陳寧文No ratings yet

- Digital LC Meter Version 2Document3 pagesDigital LC Meter Version 2geraldino250No ratings yet

- LDO Basics - Capacitor vs. Capacitance - Power Management - Technical Articles - TI E2E Support ForumsDocument5 pagesLDO Basics - Capacitor vs. Capacitance - Power Management - Technical Articles - TI E2E Support Forumstheodoros tzouralasNo ratings yet

- LDO Basics - Capacitor vs. Capacitance - Power Management - Technical Articles - TI E2E Support ForumsDocument5 pagesLDO Basics - Capacitor vs. Capacitance - Power Management - Technical Articles - TI E2E Support Forumstheodoros tzouralasNo ratings yet

- Ee141 HW5 2Document3 pagesEe141 HW5 2Vidhya DsNo ratings yet

- Low Power ThesisDocument6 pagesLow Power Thesistiffanybarbermobile100% (2)

- TN4602 PDFDocument3 pagesTN4602 PDFMarcel BlinduNo ratings yet

- SMPSBuckDesign 031809Document17 pagesSMPSBuckDesign 031809shaheerdurraniNo ratings yet

- 06 Wireless ReportDocument17 pages06 Wireless ReportshastryNo ratings yet

- A Basic Guide To The AC Specifications of ADCsDocument28 pagesA Basic Guide To The AC Specifications of ADCsuser123phcNo ratings yet

- 1 IECON-2020 Analytical Loss Equations For Three Level Active Neutral Point Clamped ConvertersDocument6 pages1 IECON-2020 Analytical Loss Equations For Three Level Active Neutral Point Clamped Convertersraghbendrat3884No ratings yet

- DGD2005 App NoteDocument9 pagesDGD2005 App NotecharlesNo ratings yet

- Fully-Differential High-Speed and High-Precision Operational Amplifier DesignsDocument9 pagesFully-Differential High-Speed and High-Precision Operational Amplifier DesignskimjimNo ratings yet

- Buck Boost ConverterDocument17 pagesBuck Boost Converteramohdzah100% (2)

- Group 9 Panilag TabucalDocument26 pagesGroup 9 Panilag Tabucalallenpanilag24No ratings yet

- Power Electronics Lab Manual With Orcad Pspice 10.5Document36 pagesPower Electronics Lab Manual With Orcad Pspice 10.5Muhammad Ahtisham Asif100% (2)

- Chapter06-2UP (4 23 02)Document79 pagesChapter06-2UP (4 23 02)Nelor Jane Robles LagunaNo ratings yet

- Durabrand Bh2004d One ChipDocument27 pagesDurabrand Bh2004d One ChipAlejo Alex CondeNo ratings yet

- 93004diDocument8 pages93004dirogererfredererNo ratings yet

- File 4Document6 pagesFile 4احمد علىNo ratings yet

- G107A Student Project 2Document14 pagesG107A Student Project 2Charlotte WilkinsonNo ratings yet

- Geo CleaningDocument34 pagesGeo CleaningNanaNo ratings yet

- Auto Power Factor Correction PresentationDocument22 pagesAuto Power Factor Correction PresentationAsad AsifNo ratings yet

- Cmb16D-Qc DMX: 16 Channel DC ControllerDocument10 pagesCmb16D-Qc DMX: 16 Channel DC ControllerFranklin SilvaNo ratings yet

- 8-Bit Digital To Analog Converter (DAC)Document5 pages8-Bit Digital To Analog Converter (DAC)Yaman GargNo ratings yet

- Digital LED Thermometer with Microcontroller AVR ATtiny13From EverandDigital LED Thermometer with Microcontroller AVR ATtiny13Rating: 5 out of 5 stars5/5 (1)

- TI - SensitivityDocument48 pagesTI - Sensitivityuam22No ratings yet

- t2004 Digital ConverterDocument102 pagest2004 Digital Converteruam22No ratings yet

- Measurement Literature ReviewDocument20 pagesMeasurement Literature Reviewuam22No ratings yet

- An Analytical Equation For The Oscillation Frequency of High-Frequency Ring OscillatorsDocument5 pagesAn Analytical Equation For The Oscillation Frequency of High-Frequency Ring Oscillatorsuam22No ratings yet

- CMOS Phase Frequency Detector For High Speed Applications: Masuri - Othman@mimos - MyDocument4 pagesCMOS Phase Frequency Detector For High Speed Applications: Masuri - Othman@mimos - Myuam22No ratings yet

- TOEFL PBT BookDocument93 pagesTOEFL PBT Bookaqua_6978% (9)

- An Improved Fast Acquisition Phase Frequency Detector For High Speed Phase-Locked LoopsDocument9 pagesAn Improved Fast Acquisition Phase Frequency Detector For High Speed Phase-Locked Loopsuam22No ratings yet

- Behavioral Modeling of PLL Using Verilog-ADocument3 pagesBehavioral Modeling of PLL Using Verilog-Auam22No ratings yet

- Znosko-Borovsky - How Not To Play Chess PDFDocument60 pagesZnosko-Borovsky - How Not To Play Chess PDFuam22No ratings yet

- SC AC Simulation PDFDocument5 pagesSC AC Simulation PDFuam22No ratings yet

- The Experimental GenerationDocument15 pagesThe Experimental Generationuam22No ratings yet

- Escala de Do Mayor para Ukelele. Ejercicios Rítmicos PDFDocument2 pagesEscala de Do Mayor para Ukelele. Ejercicios Rítmicos PDFuam22No ratings yet

- Lect 08 Latch FFDocument34 pagesLect 08 Latch FFuam22No ratings yet

- CMP 2019Document5 pagesCMP 2019uam22No ratings yet

- EE115C Tutorial 5Document37 pagesEE115C Tutorial 5uam22No ratings yet

- Guidelines For Printing in Cadence: 1) Printing Files From The Terminal (Shell Console or Command Line)Document2 pagesGuidelines For Printing in Cadence: 1) Printing Files From The Terminal (Shell Console or Command Line)uam22No ratings yet

- Bennet04 - RF and AMSDocument14 pagesBennet04 - RF and AMSuam22No ratings yet

- Hardface Hc-ODocument1 pageHardface Hc-OTirath TmsNo ratings yet

- Cloudera JDBC Driver For Apache Hive Install Guide PDFDocument111 pagesCloudera JDBC Driver For Apache Hive Install Guide PDFprasannnaNo ratings yet

- 1Document9 pages1Kavinhariharasudhan SankaralingamNo ratings yet

- Efecto Hall New TechDocument3 pagesEfecto Hall New Techmanue_saldarriaga2No ratings yet

- Mitsubishi Melservo MR JEDocument346 pagesMitsubishi Melservo MR JEpankaj mankar100% (1)

- Nota Sobre Aplciacion L100eDocument26 pagesNota Sobre Aplciacion L100eFabiana De la HozNo ratings yet

- Delremo-Version 2.0: The Power Behind CompetitivenessDocument4 pagesDelremo-Version 2.0: The Power Behind CompetitivenessBharat KumarNo ratings yet

- Chapter Cyber SecDocument30 pagesChapter Cyber SecNoura btNo ratings yet

- Coex C1000 PTZ Marine Camera Station: Data SheetDocument2 pagesCoex C1000 PTZ Marine Camera Station: Data Sheetrahmanu wiyonoNo ratings yet

- Nikran NS Smart BoatsDocument17 pagesNikran NS Smart BoatssilvioNo ratings yet

- Plate 1Document8 pagesPlate 1Mark PalisocNo ratings yet

- CD 4071 e CD 4081Document9 pagesCD 4071 e CD 4081Loganh NiassiNo ratings yet

- Java Programming Lab SyllabusDocument2 pagesJava Programming Lab SyllabusAnnie GargNo ratings yet

- Micom P127Document13 pagesMicom P127Mohyedin Ganjian aboukheiliNo ratings yet

- Si Entro Inst en Acces CardDocument132 pagesSi Entro Inst en Acces CarddaniNo ratings yet

- Migrate VMs Faster With A New Dell EMC PowerEdge MX SolutionDocument16 pagesMigrate VMs Faster With A New Dell EMC PowerEdge MX SolutionPrincipled TechnologiesNo ratings yet

- LM4051-N Precision Micropower Shunt Voltage Reference: 1 Features 3 DescriptionDocument20 pagesLM4051-N Precision Micropower Shunt Voltage Reference: 1 Features 3 Descriptiondjahid abdullohNo ratings yet

- Jeanette Carlsson An Assessment of Social Media ModelsDocument32 pagesJeanette Carlsson An Assessment of Social Media ModelsCao YajingNo ratings yet

- Samsung HT d4550 enDocument80 pagesSamsung HT d4550 enJános KáldiNo ratings yet

- Uputstvo - Capelec CAP3600Document69 pagesUputstvo - Capelec CAP3600Samir ČičakNo ratings yet

- General Letter: Updated Product Identity For Cat® Hydraulic Mining Shovels (Models 6015B - 6090 FS)Document2 pagesGeneral Letter: Updated Product Identity For Cat® Hydraulic Mining Shovels (Models 6015B - 6090 FS)Juan Carlos Inga Vasquez0% (1)

- Schottky, !. Barrier (,1, .. T .Rir., ., ,,, Hot Carrier Power Rectifiers RECTI FI ER&F's:j$r . ,. .,, .Document4 pagesSchottky, !. Barrier (,1, .. T .Rir., ., ,,, Hot Carrier Power Rectifiers RECTI FI ER&F's:j$r . ,. .,, .gdiliogNo ratings yet

- Products Catalog 13-07-2020 3Document71 pagesProducts Catalog 13-07-2020 3me46951No ratings yet

- Chapter 6 Case StudiesDocument12 pagesChapter 6 Case StudiesXyzNo ratings yet

- Ieee 32 1972 PDFDocument36 pagesIeee 32 1972 PDFSirish ShresthaNo ratings yet

- Functional Safety SyllabusDocument4 pagesFunctional Safety SyllabusramkrishnaNo ratings yet

- EVE GooglecloudDocument14 pagesEVE GooglecloudAnousone XomphouNo ratings yet

- TF6420 TC3 Database Server enDocument409 pagesTF6420 TC3 Database Server enmaadidNo ratings yet

AIC Project PDF

AIC Project PDF

Uploaded by

uam22Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

AIC Project PDF

AIC Project PDF

Uploaded by

uam22Copyright:

Available Formats

EE214 Autumn 06/07

B. Murmann Page 1 of 6

DESIGN PROJECT

(Due: Friday, December 8, 2006, 5pm PT)

1. Overview

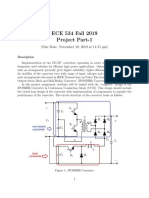

You are to design a fully differential OTA for a switched capacitor circuit application.

Figure 1 shows a model of the overall circuit in the relevant phase of operation. The

following target specifications apply:

Parameter Specification

Technology EE214 0.35µm CMOS, Nominal Corner

Operating Temperature 25°C

VDD 3V

Power Dissipation Minimize

CL ≥ 2pF

Cs ≥ 4pF

Cf 0.5·Cs

Current Mirror Ratios1 ≤ 20

Pole/Zero cancellation and left half

Forbidden

plane zeros

CMFB Circuit Ideal, as in homework 6

Single ideal current source of arbitrary value, with

Reference Current

positive node tied to VDD or negative node tied to GND

Dynamic Range 86dB

Settling Time2 ≤10ns

Static Settling Error ≤0.1%

Dynamic Settling Error ≤0.05%

Cf

CL

Cs

+ -

Vsd Vid Vod

- +

Cs

CL

Cf

Figure 1

1

Diode connected devices cannot “drive” more than the specified number of same-size unit devices.

2

Measured for a differential input step that transitions from 0V at t=0 to the maximum input voltage of the

circuit in 0.5ns. The maximum input corresponds to the maximum output voltage used in the dynamic

range calculation, divided by the closed loop gain.

Last modified 11/6/2006 11:07:00 AM

EE214 Autumn 06/07

B. Murmann Page 2 of 6

Key choices to be made in this design problem include:

o Amplifier topology

o Output signal range

o Input and output common mode levels

o Device sizes and bias currents

In addition to the design at nominal specifications indicated above, you will conclude this project

by running two additional sets of simulations at “worst case” process and temperature corners –

“fast” devices operated at 0°C, and “slow” devices at 125°C. For simplicity in this short project,

you are not required to meet the specifications at these conditions. The purpose of this addition is

to give you a feel for the impact of temperature and process variations. In practice, you would

overdesign your circuit such that the given specs are met across all corners and conditions.

You may work on this project alone or in teams of two. Each team must submit one copy of the

deliverables specified below. You are encouraged to discuss the design problem with other teams,

but your design must be unique. Under no circumstances should you exchange computer files

with other teams; this would constitute a gross violation of the honor code.

2. Suggested Design Flow

As you might find out, this problem has many more degrees of freedom than any problem you

have dealt with so far. Hence, we suggest that you organize your time and work e.g. as follows

a) Read this entire handout thoroughly.

b) Find a project partner (if you haven’t already done so).

c) Download the starter file project_example.zip or copy the files available in

/usr/class/ee214/project/ into your working directory. Examine and understand the

included files, run the various included simulations on the provided example circuit.

d) Familiarize yourself with the design example presented in lecture 20. Try to duplicate the

results and/or modify the specs to meet some of the requirements of this project (e.g.

dynamic range).

e) Pay special attention to lectures 18-23; this material will provide you with the last few

pieces of information needed to complete this assignment.

f) Decide about the circuit architecture and begin the design. In the spirit of the design

example presented in class, develop a spreadsheet or Matlab script that allows you to

optimize your design iteratively without repetitive “Spice monkeying”. You may want to

begin with a small-signal based design (as done in class), and later include transient

settling considerations.

g) Begin to write your project report (see below) at least several days before the deadline.

Your grade will strongly depend on the quality of your write-up, and not just the achieved

power dissipation.

Finally, and this is important: DON’T WAIT UNTIL THE LAST MINUTE TO START. This

project involves a great deal of just plain old labor; it takes significant amounts of time to

determine suitable design choices, run all the necessary simulations and document your work.

Also, the instructional computers and printers have been known to slow down and even go down

Last modified 11/6/2006 11:07:00 AM

EE214 Autumn 06/07

B. Murmann Page 3 of 6

at the worst possible times, to say nothing of license availability problems. We will be largely

unsympathetic to pleas for extensions arising from such problems.

3. Deliverables

a) Electronic Submission of Circuit Netlist

You are required to submit an electronic copy of your final design netlist. Details regarding this

submission and subtleties of file formatting will be communicated to you in a separate handout.

b) Project Report

You are required to prepare a hardcopy report with the following format (a hand-written report is

just fine). In case you decide to submit a computer generated report, make sure to use font sizes

greater than 10. Be sure to follow the format instructions below EXACTLY:

Page 0: Cover Page

Page 1: Outline of your design, justifications of key design decisions; comparison with

alternatives.

Page 2: Schematic diagram of final design, with component values and bias currents clearly

labeled. Show component values right next to the components, and currents next to the branches

(i.e., absolutely, positively do not make us refer to a look-up table). Annotate all transistors with

the chosen gm/ID value.

Pages 3-5: Calculation of key design parameters, such as transconductances, bias currents, etc.

Be sure to include a calculation of the circuit’s settling time. Compare hand calculated values

with final HSpice values in a table and discuss discrepancies. Make sure to include the total

power dissipation of your design (calculation and HSpice). This is one of the most important

sections of your report! The lowest power designs will not automatically score the highest grades.

The methodology you used to justify your design choices and component values is far more

important (see section on point distribution below).

Page 6: Bode plot of T(jω), phase and magnitude. Clearly annotate the achieved low frequency

loop gain, the loop crossover frequency and the phase margin.

Page 7: Plots the simulated settling transient of Vod (no zoom, show the entire waveform). In a

separate subplot, show the % error of the differential output voltage relative to the ideal output

voltage. Zoom into the relevant region of the settling, i.e. clearly demonstrate that your design

settles within spec. Annotate the achieved settling time and static settling error. For simplicity, we

use the error at t=30ns as an estimate of the static settling error.

Page 8: Plot the common mode output voltage versus time during transient settling of the circuit.

In separate subplots each, also show the differential output current of the OTA, and the

differential input to the OTA (Vid in Figure 1).

Page 9: Plot of the noise power spectral density at the OTA output (Vod) and noise integral.

Annotate the total integrated noise value and the achieved dynamic range.

Page 10: Output range. Simulation plot showing the differential open loop DC gain Vod/Vid of the

amplifier. Mark the differential output voltage at which the gain has dropped by 30%. This value

should be larger than the peak output voltage used in your dynamic range calculation.

Page 11-12: Results of corner simulations. Tabulate your circuit’s performance for the slow/hot

and fast/cold corner. Include settling time, static error, and any other parameter that you find

noteworthy. Include the %-changes with respect to nominal conditions in your table. In case the

Last modified 11/6/2006 11:07:00 AM

EE214 Autumn 06/07

B. Murmann Page 4 of 6

circuit is non-functional in these corners, investigate and explain the problem (no need to fix the

circuit). Include selected interesting plots documenting corner performance and/or issues.

Page 13: Comments and Conclusion. Here, you can convey issues you may have had, or things

you’ve learned/not learned in this project.

4. HSpice Testbench

We will use the testbench provided as part of the starter files to evaluate your design in HSpice.

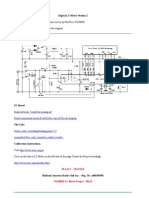

The testbench is illustrated schematically in Figure 2 below. The 10gig helper resistors are

needed to properly initialize capacitor charges in the operating point of the circuit (Note that in

practice, this will be accomplished using dedicated switches in the final switched capacitor

circuit).

CL

10gig

Cs Cf

Vsp Vom

Differential

Y Looptest

X

Vsm Vop

Cs Cf

10gig

CL

Vsc Vsp

Vsd Diffdrive Vsm Vop Vod

Vom Diffsense Voc

s

Figure 2

The testbench file contains the proper simulation setup to carry out the following analyses needed

in this project:

o Loop gain AC simulation. Sets Vsd=0V and activates the ac sources in the Differential

Looptest block to find the circuit’s loop gain vs. frequency.

o Noise simulation.

Last modified 11/6/2006 11:07:00 AM

EE214 Autumn 06/07

B. Murmann Page 5 of 6

o Transient simulation. Applies the specified input transient step. The amplitude is determined

by a parameter set in your submitted netlist (see example design netlist).

o Open-loop DC gain simulation. Applies a (small) DC-sweep to Vsd. Note that this DC

simulation will be unaffected by the presence of all capacitors and the Differential Looptest

block.

Note: The testbench will run properly with HSpice version 2004 or later (e.g. the 2006 version

setup for this course. This is due to the RUNLVL option (see application note in handouts/spice

section on eeclass) that we’re using to improve transient accuracy and simulation time.

5. Grading

1. Design Flow and Insight 20 points

2. Documentation 10 points

3. Specs and Practicality 10 points

4. Discussion/documentation of corner performance 5 points

5. Power Dissipation 15 points

Aspect Excellent Not that great… Poor

1. Design Flow Well structured, Well structured, Unclear how

clear and but unjustified design point was

reasonable decisions reached

decisions

CMFB Proper design No mention of Unstable

based on stability

stability considerations,

constraints randomly chosen

CMFB

transconductance

Discrepancies between Well explained No discussion of

hand analysis and and/or within discrepancies

simulations reasonable and potential

bounds sources

Misconceptions None Minor Not clear if

students

understand their

design

Creativity Tried Basic design

something

“new” and

interesting, e.g.

based on a

literature search

2. Schematics & Clearly labeled Somewhat Unreadable

annotation unclear schematics

Plots Clear, good Somewhat Some plots

zoom and sloppy, e.g. no missing or

annotation zoom, no labels. unreadable.

Last modified 11/6/2006 11:07:00 AM

EE214 Autumn 06/07

B. Murmann Page 6 of 6

3. Design All satisfied Somewhat Impractical

constraints/Practicality impractical, e.g. design, e.g. pole

violating M- zero cancellation

factors, tail

current source in

triode region, …

Netlist Simulated OK Not functional

Specs All met and 1 specification More

results agree barely not met, specifications

with our sim results agree with missed or design

our sim does not work

4. Corner performance Well Not clear if

documented, all corner

issues simulations were

explained run, inconsistent

data without

proper

interpretation

5. Power dissipation Computed based on ranking (0…15 points)

Last modified 11/6/2006 11:07:00 AM

You might also like

- ECE 534 Project 1 F19Document6 pagesECE 534 Project 1 F19JAY CHHEDANo ratings yet

- OI For UT of Laminations-BasicDocument8 pagesOI For UT of Laminations-Basicperogami100% (1)

- ALSi User Guide v4 5Document72 pagesALSi User Guide v4 5cardiacanesthesiaNo ratings yet

- Design Project: (Due: Friday, December 8, 2006, 5pm PT)Document6 pagesDesign Project: (Due: Friday, December 8, 2006, 5pm PT)Ibrahim MuhammedNo ratings yet

- Aic Lab Cadence 11 Folded v02Document9 pagesAic Lab Cadence 11 Folded v02Hagar IlbheryNo ratings yet

- Frequency Response of A CMOS Common-Source Amplifier: Experiment # 5Document10 pagesFrequency Response of A CMOS Common-Source Amplifier: Experiment # 5Md. Sadique SheikhNo ratings yet

- ADVD Analog Assignment - 2023ssDocument36 pagesADVD Analog Assignment - 2023ssNimit JainNo ratings yet

- Final Exam CMPE 650: NameDocument10 pagesFinal Exam CMPE 650: NameFritzie LuayonNo ratings yet

- MAX5072/3 Switching Power Supply Clock ConfigurationDocument13 pagesMAX5072/3 Switching Power Supply Clock ConfigurationJc Jayamanikandan BNo ratings yet

- Lab 5 Multisim TutorialDocument9 pagesLab 5 Multisim TutorialMuhammad UbaidNo ratings yet

- Digital-to-Analogue Conversion: PHY 406F - Microprocessor Interfacing TechniquesDocument14 pagesDigital-to-Analogue Conversion: PHY 406F - Microprocessor Interfacing TechniquesMalou Ruiz DenolanNo ratings yet

- Aic Lab Cadence MM 07 gmID v01Document8 pagesAic Lab Cadence MM 07 gmID v01احمد علىNo ratings yet

- (ECEN 4797 and ECEN 5797) Two-Transistor Forward Converter: Modeling, Design and SimulationsDocument2 pages(ECEN 4797 and ECEN 5797) Two-Transistor Forward Converter: Modeling, Design and SimulationsMaharshiGohelNo ratings yet

- Unipolar To Bipolar Analog Voltage ConversionDocument20 pagesUnipolar To Bipolar Analog Voltage ConversionGautam MonipatroNo ratings yet

- DESG - CabDocument6 pagesDESG - CabJAY PARIKHNo ratings yet

- You Should Try To MinimizeDocument5 pagesYou Should Try To MinimizeSunwoo LeeNo ratings yet

- Land Use Services DepartmentDocument20 pagesLand Use Services DepartmentJesusSQANo ratings yet

- Lab 4 A Folded-Cascode Operational AmplifierDocument6 pagesLab 4 A Folded-Cascode Operational AmplifierJatinKumarNo ratings yet

- DAC AnalysisDocument19 pagesDAC Analysisమురళీధర్ ఆది ఆంధ్రుడుNo ratings yet

- Flyback Converter Design ThesisDocument8 pagesFlyback Converter Design Thesisleanneuhlsterlingheights100% (2)

- Inter Grating AdcDocument6 pagesInter Grating AdcthắngNo ratings yet

- Theory: Lab Session 07 Light Dimmer CircuitDocument3 pagesTheory: Lab Session 07 Light Dimmer CircuitAqeel HaiderNo ratings yet

- LM240WU7 SLA1 NDS CAS Ver 1 (1) (1) .0 090403Document34 pagesLM240WU7 SLA1 NDS CAS Ver 1 (1) (1) .0 090403jaygheezyNo ratings yet

- Understanding Integrating ADC AN1041Document7 pagesUnderstanding Integrating ADC AN1041dileepank14No ratings yet

- A 10b 100MS S 1.13mW SAR ADC With Binary-Scaled Error CompensationDocument3 pagesA 10b 100MS S 1.13mW SAR ADC With Binary-Scaled Error Compensation陳昀顥No ratings yet

- Understanding Integrating ADCsDocument5 pagesUnderstanding Integrating ADCsjulioNo ratings yet

- Ee414 The4Document1 pageEe414 The4Asif SiddiqueNo ratings yet

- A New, Low-Cost, Sampled-Data, 10-Bit CMOS A/D ConverterDocument6 pagesA New, Low-Cost, Sampled-Data, 10-Bit CMOS A/D Converteralgnben1746No ratings yet

- Analog Assignment ADVDDocument24 pagesAnalog Assignment ADVDRajeevDuttNo ratings yet

- Chapter 6 - Cmos Operational AmplifiersDocument79 pagesChapter 6 - Cmos Operational AmplifierssanjayorcaNo ratings yet

- CIS Final ProjectDocument4 pagesCIS Final Project王柏勛No ratings yet

- Design of Low Power 4-Bit Flash ADC Based On Standard Cells: Marcel Siadjine Njinowa, Hung Tien Bui François-Raymond BoyerDocument4 pagesDesign of Low Power 4-Bit Flash ADC Based On Standard Cells: Marcel Siadjine Njinowa, Hung Tien Bui François-Raymond BoyerSunil PandeyNo ratings yet

- Massachusetts Institute of Technology Department of Electrical Engineering and Computer ScienceDocument7 pagesMassachusetts Institute of Technology Department of Electrical Engineering and Computer ScienceFernando Sánchez HernándezNo ratings yet

- Transformer Less Power Supply For MicrocontrollersDocument11 pagesTransformer Less Power Supply For MicrocontrollersSentimental SagNo ratings yet

- 2020 IC Design Contest: Full-Custom CategoryDocument6 pages2020 IC Design Contest: Full-Custom CategoryE94086018陳寧文No ratings yet

- Digital LC Meter Version 2Document3 pagesDigital LC Meter Version 2geraldino250No ratings yet

- LDO Basics - Capacitor vs. Capacitance - Power Management - Technical Articles - TI E2E Support ForumsDocument5 pagesLDO Basics - Capacitor vs. Capacitance - Power Management - Technical Articles - TI E2E Support Forumstheodoros tzouralasNo ratings yet

- LDO Basics - Capacitor vs. Capacitance - Power Management - Technical Articles - TI E2E Support ForumsDocument5 pagesLDO Basics - Capacitor vs. Capacitance - Power Management - Technical Articles - TI E2E Support Forumstheodoros tzouralasNo ratings yet

- Ee141 HW5 2Document3 pagesEe141 HW5 2Vidhya DsNo ratings yet

- Low Power ThesisDocument6 pagesLow Power Thesistiffanybarbermobile100% (2)

- TN4602 PDFDocument3 pagesTN4602 PDFMarcel BlinduNo ratings yet

- SMPSBuckDesign 031809Document17 pagesSMPSBuckDesign 031809shaheerdurraniNo ratings yet

- 06 Wireless ReportDocument17 pages06 Wireless ReportshastryNo ratings yet

- A Basic Guide To The AC Specifications of ADCsDocument28 pagesA Basic Guide To The AC Specifications of ADCsuser123phcNo ratings yet

- 1 IECON-2020 Analytical Loss Equations For Three Level Active Neutral Point Clamped ConvertersDocument6 pages1 IECON-2020 Analytical Loss Equations For Three Level Active Neutral Point Clamped Convertersraghbendrat3884No ratings yet

- DGD2005 App NoteDocument9 pagesDGD2005 App NotecharlesNo ratings yet

- Fully-Differential High-Speed and High-Precision Operational Amplifier DesignsDocument9 pagesFully-Differential High-Speed and High-Precision Operational Amplifier DesignskimjimNo ratings yet

- Buck Boost ConverterDocument17 pagesBuck Boost Converteramohdzah100% (2)

- Group 9 Panilag TabucalDocument26 pagesGroup 9 Panilag Tabucalallenpanilag24No ratings yet

- Power Electronics Lab Manual With Orcad Pspice 10.5Document36 pagesPower Electronics Lab Manual With Orcad Pspice 10.5Muhammad Ahtisham Asif100% (2)

- Chapter06-2UP (4 23 02)Document79 pagesChapter06-2UP (4 23 02)Nelor Jane Robles LagunaNo ratings yet

- Durabrand Bh2004d One ChipDocument27 pagesDurabrand Bh2004d One ChipAlejo Alex CondeNo ratings yet

- 93004diDocument8 pages93004dirogererfredererNo ratings yet

- File 4Document6 pagesFile 4احمد علىNo ratings yet

- G107A Student Project 2Document14 pagesG107A Student Project 2Charlotte WilkinsonNo ratings yet

- Geo CleaningDocument34 pagesGeo CleaningNanaNo ratings yet

- Auto Power Factor Correction PresentationDocument22 pagesAuto Power Factor Correction PresentationAsad AsifNo ratings yet

- Cmb16D-Qc DMX: 16 Channel DC ControllerDocument10 pagesCmb16D-Qc DMX: 16 Channel DC ControllerFranklin SilvaNo ratings yet

- 8-Bit Digital To Analog Converter (DAC)Document5 pages8-Bit Digital To Analog Converter (DAC)Yaman GargNo ratings yet

- Digital LED Thermometer with Microcontroller AVR ATtiny13From EverandDigital LED Thermometer with Microcontroller AVR ATtiny13Rating: 5 out of 5 stars5/5 (1)

- TI - SensitivityDocument48 pagesTI - Sensitivityuam22No ratings yet

- t2004 Digital ConverterDocument102 pagest2004 Digital Converteruam22No ratings yet

- Measurement Literature ReviewDocument20 pagesMeasurement Literature Reviewuam22No ratings yet

- An Analytical Equation For The Oscillation Frequency of High-Frequency Ring OscillatorsDocument5 pagesAn Analytical Equation For The Oscillation Frequency of High-Frequency Ring Oscillatorsuam22No ratings yet

- CMOS Phase Frequency Detector For High Speed Applications: Masuri - Othman@mimos - MyDocument4 pagesCMOS Phase Frequency Detector For High Speed Applications: Masuri - Othman@mimos - Myuam22No ratings yet

- TOEFL PBT BookDocument93 pagesTOEFL PBT Bookaqua_6978% (9)

- An Improved Fast Acquisition Phase Frequency Detector For High Speed Phase-Locked LoopsDocument9 pagesAn Improved Fast Acquisition Phase Frequency Detector For High Speed Phase-Locked Loopsuam22No ratings yet

- Behavioral Modeling of PLL Using Verilog-ADocument3 pagesBehavioral Modeling of PLL Using Verilog-Auam22No ratings yet

- Znosko-Borovsky - How Not To Play Chess PDFDocument60 pagesZnosko-Borovsky - How Not To Play Chess PDFuam22No ratings yet

- SC AC Simulation PDFDocument5 pagesSC AC Simulation PDFuam22No ratings yet

- The Experimental GenerationDocument15 pagesThe Experimental Generationuam22No ratings yet

- Escala de Do Mayor para Ukelele. Ejercicios Rítmicos PDFDocument2 pagesEscala de Do Mayor para Ukelele. Ejercicios Rítmicos PDFuam22No ratings yet

- Lect 08 Latch FFDocument34 pagesLect 08 Latch FFuam22No ratings yet

- CMP 2019Document5 pagesCMP 2019uam22No ratings yet

- EE115C Tutorial 5Document37 pagesEE115C Tutorial 5uam22No ratings yet

- Guidelines For Printing in Cadence: 1) Printing Files From The Terminal (Shell Console or Command Line)Document2 pagesGuidelines For Printing in Cadence: 1) Printing Files From The Terminal (Shell Console or Command Line)uam22No ratings yet

- Bennet04 - RF and AMSDocument14 pagesBennet04 - RF and AMSuam22No ratings yet

- Hardface Hc-ODocument1 pageHardface Hc-OTirath TmsNo ratings yet

- Cloudera JDBC Driver For Apache Hive Install Guide PDFDocument111 pagesCloudera JDBC Driver For Apache Hive Install Guide PDFprasannnaNo ratings yet

- 1Document9 pages1Kavinhariharasudhan SankaralingamNo ratings yet

- Efecto Hall New TechDocument3 pagesEfecto Hall New Techmanue_saldarriaga2No ratings yet

- Mitsubishi Melservo MR JEDocument346 pagesMitsubishi Melservo MR JEpankaj mankar100% (1)

- Nota Sobre Aplciacion L100eDocument26 pagesNota Sobre Aplciacion L100eFabiana De la HozNo ratings yet

- Delremo-Version 2.0: The Power Behind CompetitivenessDocument4 pagesDelremo-Version 2.0: The Power Behind CompetitivenessBharat KumarNo ratings yet

- Chapter Cyber SecDocument30 pagesChapter Cyber SecNoura btNo ratings yet

- Coex C1000 PTZ Marine Camera Station: Data SheetDocument2 pagesCoex C1000 PTZ Marine Camera Station: Data Sheetrahmanu wiyonoNo ratings yet

- Nikran NS Smart BoatsDocument17 pagesNikran NS Smart BoatssilvioNo ratings yet

- Plate 1Document8 pagesPlate 1Mark PalisocNo ratings yet

- CD 4071 e CD 4081Document9 pagesCD 4071 e CD 4081Loganh NiassiNo ratings yet

- Java Programming Lab SyllabusDocument2 pagesJava Programming Lab SyllabusAnnie GargNo ratings yet

- Micom P127Document13 pagesMicom P127Mohyedin Ganjian aboukheiliNo ratings yet

- Si Entro Inst en Acces CardDocument132 pagesSi Entro Inst en Acces CarddaniNo ratings yet

- Migrate VMs Faster With A New Dell EMC PowerEdge MX SolutionDocument16 pagesMigrate VMs Faster With A New Dell EMC PowerEdge MX SolutionPrincipled TechnologiesNo ratings yet

- LM4051-N Precision Micropower Shunt Voltage Reference: 1 Features 3 DescriptionDocument20 pagesLM4051-N Precision Micropower Shunt Voltage Reference: 1 Features 3 Descriptiondjahid abdullohNo ratings yet

- Jeanette Carlsson An Assessment of Social Media ModelsDocument32 pagesJeanette Carlsson An Assessment of Social Media ModelsCao YajingNo ratings yet

- Samsung HT d4550 enDocument80 pagesSamsung HT d4550 enJános KáldiNo ratings yet

- Uputstvo - Capelec CAP3600Document69 pagesUputstvo - Capelec CAP3600Samir ČičakNo ratings yet

- General Letter: Updated Product Identity For Cat® Hydraulic Mining Shovels (Models 6015B - 6090 FS)Document2 pagesGeneral Letter: Updated Product Identity For Cat® Hydraulic Mining Shovels (Models 6015B - 6090 FS)Juan Carlos Inga Vasquez0% (1)

- Schottky, !. Barrier (,1, .. T .Rir., ., ,,, Hot Carrier Power Rectifiers RECTI FI ER&F's:j$r . ,. .,, .Document4 pagesSchottky, !. Barrier (,1, .. T .Rir., ., ,,, Hot Carrier Power Rectifiers RECTI FI ER&F's:j$r . ,. .,, .gdiliogNo ratings yet

- Products Catalog 13-07-2020 3Document71 pagesProducts Catalog 13-07-2020 3me46951No ratings yet

- Chapter 6 Case StudiesDocument12 pagesChapter 6 Case StudiesXyzNo ratings yet

- Ieee 32 1972 PDFDocument36 pagesIeee 32 1972 PDFSirish ShresthaNo ratings yet

- Functional Safety SyllabusDocument4 pagesFunctional Safety SyllabusramkrishnaNo ratings yet

- EVE GooglecloudDocument14 pagesEVE GooglecloudAnousone XomphouNo ratings yet

- TF6420 TC3 Database Server enDocument409 pagesTF6420 TC3 Database Server enmaadidNo ratings yet