Professional Documents

Culture Documents

EE457 Homework#4: Problem 1

EE457 Homework#4: Problem 1

Uploaded by

ottoporCopyright:

Available Formats

You might also like

- HW 5Document1 pageHW 5ottoporNo ratings yet

- Layout Solns 3Document12 pagesLayout Solns 3VIKRAM KUMARNo ratings yet

- Board Exam ProblemsDocument120 pagesBoard Exam ProblemsLanz de la Cruz83% (6)

- HW 5Document1 pageHW 5ottoporNo ratings yet

- Parasitic Extractions in Electric VLSIDocument4 pagesParasitic Extractions in Electric VLSIottoporNo ratings yet

- Digital Integrated CircuitDocument33 pagesDigital Integrated CircuitottoporNo ratings yet

- Tutorial Exercises 0: The Basics: E1001 Electronic Circuits Prof P BayvelDocument7 pagesTutorial Exercises 0: The Basics: E1001 Electronic Circuits Prof P BayvelraihanserajNo ratings yet

- Materials ScienceDocument45 pagesMaterials ScienceSantosh Rai0% (1)

- Materials ScienceDocument41 pagesMaterials ScienceNagasowjanyaJonnalagaddaNo ratings yet

- VLSI Design Assignment ProblemsDocument2 pagesVLSI Design Assignment ProblemsBhavani BhagyasreeNo ratings yet

- Namma Kalvi 12th Physics First Mid Term Model Question Paper EM 221034Document14 pagesNamma Kalvi 12th Physics First Mid Term Model Question Paper EM 221034pearlynNo ratings yet

- Faculty of Engineering Electronic and Computer EngineeringDocument4 pagesFaculty of Engineering Electronic and Computer EngineeringSamuelNo ratings yet

- EE 1 Probset 1Document2 pagesEE 1 Probset 1Clint Charles P. BrutasNo ratings yet

- Compilations of Board Exam Problem1 PDFDocument65 pagesCompilations of Board Exam Problem1 PDFJevan Calaque100% (1)

- 2015 ExamDocument2 pages2015 ExamshyyhongNo ratings yet

- Assignement 1Document2 pagesAssignement 1jacksonNo ratings yet

- Design of RCC Structural Elements July 2016 (2010 Scheme)Document2 pagesDesign of RCC Structural Elements July 2016 (2010 Scheme)Sandeep DevikereMathNo ratings yet

- Amos 2012Document4 pagesAmos 2012prk74No ratings yet

- Me 3403 Mechanics of Solids Exam 1 Fall 2016Document9 pagesMe 3403 Mechanics of Solids Exam 1 Fall 2016Jake OakenfoldNo ratings yet

- Etc - Ei-Ii Final Exam Paper - 2020 - 21Document3 pagesEtc - Ei-Ii Final Exam Paper - 2020 - 21ARYA RAJPUTNo ratings yet

- Thapar University: B. Tech. (111 Semester)Document2 pagesThapar University: B. Tech. (111 Semester)auro auroNo ratings yet

- Tsu m18 Practice Problems Smat1Document2 pagesTsu m18 Practice Problems Smat1Mark Lester ValdozNo ratings yet

- Kee101t Ee Aktu QP-2020-21Document14 pagesKee101t Ee Aktu QP-2020-21Sudhir ChandNo ratings yet

- Hallmark Engineering Classes: "Please Check Whether You Have Got The Right Question Paper."Document2 pagesHallmark Engineering Classes: "Please Check Whether You Have Got The Right Question Paper."Yash DhabaliaNo ratings yet

- Exercises ResistanceDocument5 pagesExercises ResistanceAldren IbarrondoNo ratings yet

- Engineering Academy: Civil Engineering ESE Conventional Revision TEST - IDocument8 pagesEngineering Academy: Civil Engineering ESE Conventional Revision TEST - Isaxenaarpita41No ratings yet

- Tut4 PDFDocument3 pagesTut4 PDFGregorNo ratings yet

- Sample Midterm 1Document8 pagesSample Midterm 1Ryan GittensNo ratings yet

- 9A01301 Mechanics of SolidsDocument4 pages9A01301 Mechanics of SolidssivabharathamurthyNo ratings yet

- Physics: Max - Marks: 66: 10 A × 10 A × 10 A × 10 A ×Document8 pagesPhysics: Max - Marks: 66: 10 A × 10 A × 10 A × 10 A ×K R I S HNo ratings yet

- Physics Mdr1 Fm4Document5 pagesPhysics Mdr1 Fm4Nassrah JumaNo ratings yet

- EEE 455Document13 pagesEEE 455fahim0110ahmedNo ratings yet

- 1 Basic Principles of ElectricityDocument4 pages1 Basic Principles of Electricitydabs_orangejuiceNo ratings yet

- E - C Etj - .::B) : '/' '"Dem09-Dd - (A) Con. T? .14-09. 0As/C3 - O - /JL-S 'Document2 pagesE - C Etj - .::B) : '/' '"Dem09-Dd - (A) Con. T? .14-09. 0As/C3 - O - /JL-S 'aniket-mhatre-164No ratings yet

- CE 8601 Internal 2 Answerkey 2021Document10 pagesCE 8601 Internal 2 Answerkey 2021ci_balaNo ratings yet

- model qp -XII -PHYSICSDocument6 pagesmodel qp -XII -PHYSICSganbuphysics80No ratings yet

- Chapter 14 Magnetic Field - QDocument6 pagesChapter 14 Magnetic Field - QhinchosyNo ratings yet

- Module Taxation 2Document1 pageModule Taxation 2RyanCallejaNo ratings yet

- CH 5Document53 pagesCH 5sameer60% (5)

- HW 5 UpdatedDocument1 pageHW 5 UpdatedottoporNo ratings yet

- 2020 10 28SupplementaryCE201CE201 I Ktu QbankDocument3 pages2020 10 28SupplementaryCE201CE201 I Ktu Qbankprasidh msNo ratings yet

- Power AppartusDocument3 pagesPower AppartusRajkumarJhapteNo ratings yet

- P Side N SideDocument3 pagesP Side N SideAahan JainNo ratings yet

- Assign#1Document2 pagesAssign#1vineet mishraNo ratings yet

- EE3012 Oct2013Document4 pagesEE3012 Oct2013Amazing ElectricalNo ratings yet

- Btech 1 Sem Basic Electrical Engineering Kee 101 2018 19Document4 pagesBtech 1 Sem Basic Electrical Engineering Kee 101 2018 19Viraj RuhelaNo ratings yet

- Csec E&ET TestDocument5 pagesCsec E&ET TestkesnaNo ratings yet

- Q2 Attempt Any Two Questions: (2x10 20)Document2 pagesQ2 Attempt Any Two Questions: (2x10 20)maniram7No ratings yet

- Semester-1 - Chemistry Stream - Mid+end PaperDocument15 pagesSemester-1 - Chemistry Stream - Mid+end PaperGopiNo ratings yet

- LPVD 2018Document2 pagesLPVD 2018Aniruddh AndeNo ratings yet

- C C192023 Pages:2: Answer Any Two Full Questions, Each Carries 15 MarksDocument2 pagesC C192023 Pages:2: Answer Any Two Full Questions, Each Carries 15 MarksFayaz aliNo ratings yet

- Current Electricity ExerciseDocument36 pagesCurrent Electricity ExerciseBeena JayNo ratings yet

- LPVD 2019Document3 pagesLPVD 2019Aniruddh AndeNo ratings yet

- IES 1988 Question PaperpdfDocument8 pagesIES 1988 Question Paperpdfh9emanth4No ratings yet

- 9A02502 Transmission of Electric PowerDocument6 pages9A02502 Transmission of Electric PowersivabharathamurthyNo ratings yet

- 12 Physics (Theory)Document6 pages12 Physics (Theory)Bhaswati SurNo ratings yet

- Assign SemiconDocument6 pagesAssign SemiconChaztan RajNo ratings yet

- HPSC Panchayati Raj Conventional Paper 2023Document11 pagesHPSC Panchayati Raj Conventional Paper 2023vikram SinghNo ratings yet

- Vacuum Nanoelectronic Devices: Novel Electron Sources and ApplicationsFrom EverandVacuum Nanoelectronic Devices: Novel Electron Sources and ApplicationsNo ratings yet

- Home Depot Sweepstakes USDocument5 pagesHome Depot Sweepstakes USottoporNo ratings yet

- Jetro Ny Flyer - 46Document12 pagesJetro Ny Flyer - 46ottoporNo ratings yet

- Lucid Financing ULFJVDDocument3 pagesLucid Financing ULFJVDottoporNo ratings yet

- Fisker MY23 Price Reductions FINAL 3-US-ENDocument4 pagesFisker MY23 Price Reductions FINAL 3-US-ENottoporNo ratings yet

- Homework #6 (Optional HW) EE457: Due Date: May 2, 2016Document2 pagesHomework #6 (Optional HW) EE457: Due Date: May 2, 2016ottoporNo ratings yet

- HW 5 UpdatedDocument1 pageHW 5 UpdatedottoporNo ratings yet

- HW 5Document15 pagesHW 5ottoporNo ratings yet

- H S C I: I T (I T) : Ardware Ecurity For Yber Nfrastructure Nternet of Hings ODocument47 pagesH S C I: I T (I T) : Ardware Ecurity For Yber Nfrastructure Nternet of Hings OottoporNo ratings yet

- Guide To Setup The Environment For CAD Tools and Install CAD ToolsDocument13 pagesGuide To Setup The Environment For CAD Tools and Install CAD ToolsottoporNo ratings yet

- Graphene Supercapacitors: The Race To The Future - Efficient Power Storage ManagementDocument7 pagesGraphene Supercapacitors: The Race To The Future - Efficient Power Storage ManagementottoporNo ratings yet

- Digital Integrated Circuits Cont'dDocument30 pagesDigital Integrated Circuits Cont'dottoporNo ratings yet

- The City College of New York: Networking & Security MIS G 2030Document23 pagesThe City College of New York: Networking & Security MIS G 2030ottoporNo ratings yet

- Take Home Exam 3: OptimizationDocument45 pagesTake Home Exam 3: OptimizationottoporNo ratings yet

EE457 Homework#4: Problem 1

EE457 Homework#4: Problem 1

Uploaded by

ottoporOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

EE457 Homework#4: Problem 1

EE457 Homework#4: Problem 1

Uploaded by

ottoporCopyright:

Available Formats

EE457

Homework#4

Due April 11, 2016

Note:

Read Chapters 4&5.

100 points maximum, 20 points per problem.

Problem 1:

You should watch other videos as needed. Watch Videos #10, 11, 12, and 13. Write some key salient features

about these videos. A few sentences are fine.

Problem 2:

(a) Compute resistance of a copper interconnect where the thickness t = 2x10-4cm. length L=4mm and the

width W=800x10-6cm. Be careful with corners.

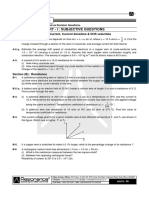

(b) Using the same sheet resistance, Rs, from part (a), find the resistance of the following layout metal

trace by calculating straight and corner squares.

155um

50um

5um

45um

30um

Problem 3:

(A)Calculate line capacitance of a chip interconnect that sits on top of silicon dioxide layer on a silicon

substrate. The interconnect is a copper trace where the thickness t = 2x10-4cm. length L=4mm and the

width W=800x10-6cm. The thickness of the silicon dioxide is 200 Angstroms. Note: 1Angstrom = 10-10m.

(B)Compute the fringe capacitance of part (A).

Problem 4

a) Using Electric, draw the schematic of F AB CD .

b) Using Euler’s path, find the optimum input permutation.

c) Layout in Electric. Run DRC check.

d) Extract the layout.

e) Do SPICE transient analysis of the layout. Put A=0, B=1, C=1 and D shown below.

0 5ns 10ns 20ns 25ns 35ns 45ns time

Timing Diagram for D Input

Problem 5:

For a TG circuit shown in class with 3 TG’s, calculate the final voltage, Vf, if your initial states were A=1, B=0,

C=0 and final states changed to A=1, B=1, C=1. The output capacitor is initially uncharged. Now change states

from previous A=1, B=1, C=1 to A=0, B=0, C=1. Find the final voltage at Vf.

You might also like

- HW 5Document1 pageHW 5ottoporNo ratings yet

- Layout Solns 3Document12 pagesLayout Solns 3VIKRAM KUMARNo ratings yet

- Board Exam ProblemsDocument120 pagesBoard Exam ProblemsLanz de la Cruz83% (6)

- HW 5Document1 pageHW 5ottoporNo ratings yet

- Parasitic Extractions in Electric VLSIDocument4 pagesParasitic Extractions in Electric VLSIottoporNo ratings yet

- Digital Integrated CircuitDocument33 pagesDigital Integrated CircuitottoporNo ratings yet

- Tutorial Exercises 0: The Basics: E1001 Electronic Circuits Prof P BayvelDocument7 pagesTutorial Exercises 0: The Basics: E1001 Electronic Circuits Prof P BayvelraihanserajNo ratings yet

- Materials ScienceDocument45 pagesMaterials ScienceSantosh Rai0% (1)

- Materials ScienceDocument41 pagesMaterials ScienceNagasowjanyaJonnalagaddaNo ratings yet

- VLSI Design Assignment ProblemsDocument2 pagesVLSI Design Assignment ProblemsBhavani BhagyasreeNo ratings yet

- Namma Kalvi 12th Physics First Mid Term Model Question Paper EM 221034Document14 pagesNamma Kalvi 12th Physics First Mid Term Model Question Paper EM 221034pearlynNo ratings yet

- Faculty of Engineering Electronic and Computer EngineeringDocument4 pagesFaculty of Engineering Electronic and Computer EngineeringSamuelNo ratings yet

- EE 1 Probset 1Document2 pagesEE 1 Probset 1Clint Charles P. BrutasNo ratings yet

- Compilations of Board Exam Problem1 PDFDocument65 pagesCompilations of Board Exam Problem1 PDFJevan Calaque100% (1)

- 2015 ExamDocument2 pages2015 ExamshyyhongNo ratings yet

- Assignement 1Document2 pagesAssignement 1jacksonNo ratings yet

- Design of RCC Structural Elements July 2016 (2010 Scheme)Document2 pagesDesign of RCC Structural Elements July 2016 (2010 Scheme)Sandeep DevikereMathNo ratings yet

- Amos 2012Document4 pagesAmos 2012prk74No ratings yet

- Me 3403 Mechanics of Solids Exam 1 Fall 2016Document9 pagesMe 3403 Mechanics of Solids Exam 1 Fall 2016Jake OakenfoldNo ratings yet

- Etc - Ei-Ii Final Exam Paper - 2020 - 21Document3 pagesEtc - Ei-Ii Final Exam Paper - 2020 - 21ARYA RAJPUTNo ratings yet

- Thapar University: B. Tech. (111 Semester)Document2 pagesThapar University: B. Tech. (111 Semester)auro auroNo ratings yet

- Tsu m18 Practice Problems Smat1Document2 pagesTsu m18 Practice Problems Smat1Mark Lester ValdozNo ratings yet

- Kee101t Ee Aktu QP-2020-21Document14 pagesKee101t Ee Aktu QP-2020-21Sudhir ChandNo ratings yet

- Hallmark Engineering Classes: "Please Check Whether You Have Got The Right Question Paper."Document2 pagesHallmark Engineering Classes: "Please Check Whether You Have Got The Right Question Paper."Yash DhabaliaNo ratings yet

- Exercises ResistanceDocument5 pagesExercises ResistanceAldren IbarrondoNo ratings yet

- Engineering Academy: Civil Engineering ESE Conventional Revision TEST - IDocument8 pagesEngineering Academy: Civil Engineering ESE Conventional Revision TEST - Isaxenaarpita41No ratings yet

- Tut4 PDFDocument3 pagesTut4 PDFGregorNo ratings yet

- Sample Midterm 1Document8 pagesSample Midterm 1Ryan GittensNo ratings yet

- 9A01301 Mechanics of SolidsDocument4 pages9A01301 Mechanics of SolidssivabharathamurthyNo ratings yet

- Physics: Max - Marks: 66: 10 A × 10 A × 10 A × 10 A ×Document8 pagesPhysics: Max - Marks: 66: 10 A × 10 A × 10 A × 10 A ×K R I S HNo ratings yet

- Physics Mdr1 Fm4Document5 pagesPhysics Mdr1 Fm4Nassrah JumaNo ratings yet

- EEE 455Document13 pagesEEE 455fahim0110ahmedNo ratings yet

- 1 Basic Principles of ElectricityDocument4 pages1 Basic Principles of Electricitydabs_orangejuiceNo ratings yet

- E - C Etj - .::B) : '/' '"Dem09-Dd - (A) Con. T? .14-09. 0As/C3 - O - /JL-S 'Document2 pagesE - C Etj - .::B) : '/' '"Dem09-Dd - (A) Con. T? .14-09. 0As/C3 - O - /JL-S 'aniket-mhatre-164No ratings yet

- CE 8601 Internal 2 Answerkey 2021Document10 pagesCE 8601 Internal 2 Answerkey 2021ci_balaNo ratings yet

- model qp -XII -PHYSICSDocument6 pagesmodel qp -XII -PHYSICSganbuphysics80No ratings yet

- Chapter 14 Magnetic Field - QDocument6 pagesChapter 14 Magnetic Field - QhinchosyNo ratings yet

- Module Taxation 2Document1 pageModule Taxation 2RyanCallejaNo ratings yet

- CH 5Document53 pagesCH 5sameer60% (5)

- HW 5 UpdatedDocument1 pageHW 5 UpdatedottoporNo ratings yet

- 2020 10 28SupplementaryCE201CE201 I Ktu QbankDocument3 pages2020 10 28SupplementaryCE201CE201 I Ktu Qbankprasidh msNo ratings yet

- Power AppartusDocument3 pagesPower AppartusRajkumarJhapteNo ratings yet

- P Side N SideDocument3 pagesP Side N SideAahan JainNo ratings yet

- Assign#1Document2 pagesAssign#1vineet mishraNo ratings yet

- EE3012 Oct2013Document4 pagesEE3012 Oct2013Amazing ElectricalNo ratings yet

- Btech 1 Sem Basic Electrical Engineering Kee 101 2018 19Document4 pagesBtech 1 Sem Basic Electrical Engineering Kee 101 2018 19Viraj RuhelaNo ratings yet

- Csec E&ET TestDocument5 pagesCsec E&ET TestkesnaNo ratings yet

- Q2 Attempt Any Two Questions: (2x10 20)Document2 pagesQ2 Attempt Any Two Questions: (2x10 20)maniram7No ratings yet

- Semester-1 - Chemistry Stream - Mid+end PaperDocument15 pagesSemester-1 - Chemistry Stream - Mid+end PaperGopiNo ratings yet

- LPVD 2018Document2 pagesLPVD 2018Aniruddh AndeNo ratings yet

- C C192023 Pages:2: Answer Any Two Full Questions, Each Carries 15 MarksDocument2 pagesC C192023 Pages:2: Answer Any Two Full Questions, Each Carries 15 MarksFayaz aliNo ratings yet

- Current Electricity ExerciseDocument36 pagesCurrent Electricity ExerciseBeena JayNo ratings yet

- LPVD 2019Document3 pagesLPVD 2019Aniruddh AndeNo ratings yet

- IES 1988 Question PaperpdfDocument8 pagesIES 1988 Question Paperpdfh9emanth4No ratings yet

- 9A02502 Transmission of Electric PowerDocument6 pages9A02502 Transmission of Electric PowersivabharathamurthyNo ratings yet

- 12 Physics (Theory)Document6 pages12 Physics (Theory)Bhaswati SurNo ratings yet

- Assign SemiconDocument6 pagesAssign SemiconChaztan RajNo ratings yet

- HPSC Panchayati Raj Conventional Paper 2023Document11 pagesHPSC Panchayati Raj Conventional Paper 2023vikram SinghNo ratings yet

- Vacuum Nanoelectronic Devices: Novel Electron Sources and ApplicationsFrom EverandVacuum Nanoelectronic Devices: Novel Electron Sources and ApplicationsNo ratings yet

- Home Depot Sweepstakes USDocument5 pagesHome Depot Sweepstakes USottoporNo ratings yet

- Jetro Ny Flyer - 46Document12 pagesJetro Ny Flyer - 46ottoporNo ratings yet

- Lucid Financing ULFJVDDocument3 pagesLucid Financing ULFJVDottoporNo ratings yet

- Fisker MY23 Price Reductions FINAL 3-US-ENDocument4 pagesFisker MY23 Price Reductions FINAL 3-US-ENottoporNo ratings yet

- Homework #6 (Optional HW) EE457: Due Date: May 2, 2016Document2 pagesHomework #6 (Optional HW) EE457: Due Date: May 2, 2016ottoporNo ratings yet

- HW 5 UpdatedDocument1 pageHW 5 UpdatedottoporNo ratings yet

- HW 5Document15 pagesHW 5ottoporNo ratings yet

- H S C I: I T (I T) : Ardware Ecurity For Yber Nfrastructure Nternet of Hings ODocument47 pagesH S C I: I T (I T) : Ardware Ecurity For Yber Nfrastructure Nternet of Hings OottoporNo ratings yet

- Guide To Setup The Environment For CAD Tools and Install CAD ToolsDocument13 pagesGuide To Setup The Environment For CAD Tools and Install CAD ToolsottoporNo ratings yet

- Graphene Supercapacitors: The Race To The Future - Efficient Power Storage ManagementDocument7 pagesGraphene Supercapacitors: The Race To The Future - Efficient Power Storage ManagementottoporNo ratings yet

- Digital Integrated Circuits Cont'dDocument30 pagesDigital Integrated Circuits Cont'dottoporNo ratings yet

- The City College of New York: Networking & Security MIS G 2030Document23 pagesThe City College of New York: Networking & Security MIS G 2030ottoporNo ratings yet

- Take Home Exam 3: OptimizationDocument45 pagesTake Home Exam 3: OptimizationottoporNo ratings yet