Professional Documents

Culture Documents

Fun Work (Bonus Points - Group Assignment) : GM GM

Fun Work (Bonus Points - Group Assignment) : GM GM

Uploaded by

uzair ahmadCopyright:

Available Formats

You might also like

- Solucion Problemas de Practica Sadiku PDFDocument14 pagesSolucion Problemas de Practica Sadiku PDFCristian Arevalo Briceño33% (3)

- Optical Con Field Assembly - Technical Info v1.0Document14 pagesOptical Con Field Assembly - Technical Info v1.0Mariano AcostaNo ratings yet

- 2-Attenuation-Limited Fiber LengthDocument3 pages2-Attenuation-Limited Fiber LengthrafatelecomNo ratings yet

- smf28 PDFDocument4 pagessmf28 PDFRODRIGUEZDIAZJJNo ratings yet

- OM4 Fiber - The Next Generation of Multimode: Tony Irujo - Sales Engineer OFSDocument47 pagesOM4 Fiber - The Next Generation of Multimode: Tony Irujo - Sales Engineer OFSgryglewskiaNo ratings yet

- Corning® LEAF® Optical Fiber: Product InformationDocument0 pagesCorning® LEAF® Optical Fiber: Product Informationhcdung18No ratings yet

- Tech. Specification 48fiber Armoured Single Sheath (8tube)Document7 pagesTech. Specification 48fiber Armoured Single Sheath (8tube)Zaman MuhammadNo ratings yet

- PigtailDocument4 pagesPigtailachraf conceptionNo ratings yet

- Hobby Electronics 1978 11 S OCR Vol 1 No 1Document74 pagesHobby Electronics 1978 11 S OCR Vol 1 No 1Annamária ApátiNo ratings yet

- Om4 MM 24 Fiber MTP Female To MTP Female 5m Fiber Optic Patch Cable Data Sheet 242018Document3 pagesOm4 MM 24 Fiber MTP Female To MTP Female 5m Fiber Optic Patch Cable Data Sheet 242018GLsun MallNo ratings yet

- FSC DSF Spool 030c Pdf4Document37 pagesFSC DSF Spool 030c Pdf4Ragu pathiNo ratings yet

- Sip Design and Verification Using AdsDocument34 pagesSip Design and Verification Using AdsMaria Lavinia IordacheNo ratings yet

- Link Design: DR Tahmina AjmalDocument36 pagesLink Design: DR Tahmina Ajmalaamirsaleem54No ratings yet

- LEAF Optical Fiber PDFDocument2 pagesLEAF Optical Fiber PDFShewan Alam SuhreedNo ratings yet

- LS Fiber Optics enDocument48 pagesLS Fiber Optics enboopelectraNo ratings yet

- MTRJ Patch Cable Spec SheetDocument2 pagesMTRJ Patch Cable Spec SheetMohan KNo ratings yet

- Fiber Optic Cable ProductsDocument48 pagesFiber Optic Cable ProductsUdriste DanielNo ratings yet

- Corning SMF-28e Optical Fiber Product InformationDocument4 pagesCorning SMF-28e Optical Fiber Product InformationCompengtech DeptNo ratings yet

- smf28 PDFDocument4 pagessmf28 PDFNahed Ep KhaledNo ratings yet

- Die Manufacturing NewDocument37 pagesDie Manufacturing NewaramacataNo ratings yet

- Om4 MM 24 Fiber MTP Female To MTP Female 2m Fiber Optic Patch Cable Data Sheet 242022Document3 pagesOm4 MM 24 Fiber MTP Female To MTP Female 2m Fiber Optic Patch Cable Data Sheet 242022GLsun MallNo ratings yet

- FOC Link DesignDocument10 pagesFOC Link DesignMilica DrajicNo ratings yet

- CMOS Tech Loose ModDocument17 pagesCMOS Tech Loose ModAjay YadavNo ratings yet

- AMD 45nm Press Presentation 2Document11 pagesAMD 45nm Press Presentation 2Jānis BalgalvisNo ratings yet

- Ufiber Gpon - Designing A Gpon Network: Notes & RequirementsDocument10 pagesUfiber Gpon - Designing A Gpon Network: Notes & RequirementsHeooo GamingNo ratings yet

- Corning SMF-28e Photonic Fiber: Extreme Precision For Demanding OEM ApplicationsDocument4 pagesCorning SMF-28e Photonic Fiber: Extreme Precision For Demanding OEM ApplicationsCHRISTIAN LEZAMA CUELLAR,No ratings yet

- Family - Fiber Optic Patch Cords: MT Mpo/Mtp/MtDocument2 pagesFamily - Fiber Optic Patch Cords: MT Mpo/Mtp/MtMohan KNo ratings yet

- Optical Fiber PigtailDocument2 pagesOptical Fiber PigtailSunny LinNo ratings yet

- OPGW Technical SpecificationDocument56 pagesOPGW Technical SpecificationbinodeNo ratings yet

- SM LightDocument4 pagesSM LighttocviNo ratings yet

- OPGWDocument74 pagesOPGWAnonymous 3y4Z5cUNo ratings yet

- Práctica 1 Módulo 2Document7 pagesPráctica 1 Módulo 2DARCELY ALEJANDRA CANTO DE LA CRUZNo ratings yet

- Cisco CFP2DCO Data SheetDocument8 pagesCisco CFP2DCO Data Sheetd00h0vNyNo ratings yet

- A DQ BN 2y 6-288 E9Document2 pagesA DQ BN 2y 6-288 E9Ade DwinantoNo ratings yet

- FTTH Accessories PDFDocument10 pagesFTTH Accessories PDFdannyalcivarNo ratings yet

- Design of Optical Digital Transmission SystemsDocument51 pagesDesign of Optical Digital Transmission SystemsSimrandeep SinghNo ratings yet

- FO - Technical ParametersDocument3 pagesFO - Technical ParametersReinaldo Sciliano juniorNo ratings yet

- Ixfiber Catalogue 2011Document14 pagesIxfiber Catalogue 2011Patrice CrochetNo ratings yet

- GOHNDocument5 pagesGOHNNadeem HaddadNo ratings yet

- CD and PMD TestDocument4 pagesCD and PMD TestSheik Mohamed AliNo ratings yet

- CS Optical Patch Cable Data Sheet by JTOPTICSDocument7 pagesCS Optical Patch Cable Data Sheet by JTOPTICSJayani Technologies LtdNo ratings yet

- FTTH-OR20 Series Optical ReceiverDocument3 pagesFTTH-OR20 Series Optical Receivermende7No ratings yet

- Texto Que Encontre Por AhiDocument4 pagesTexto Que Encontre Por AhiExerseNo ratings yet

- Scaling PDFDocument72 pagesScaling PDFMayank SinghNo ratings yet

- ITU-T G.652.D SpecsDocument2 pagesITU-T G.652.D SpecsroomforsquaresNo ratings yet

- FO-ESC250D: Mechanical Fiber Optic Connector-Fiber Pre-Embeded TechDocument1 pageFO-ESC250D: Mechanical Fiber Optic Connector-Fiber Pre-Embeded TechDilmer Javier Puel CruzNo ratings yet

- Cisco DWDM OverviewDocument87 pagesCisco DWDM OverviewRishi NandwanaNo ratings yet

- Draka G 652D ESMF - AmericasDocument2 pagesDraka G 652D ESMF - AmericasLuis Gonzalo Tarazona CubaNo ratings yet

- IL2225 L10 ManufacturingDocument29 pagesIL2225 L10 ManufacturingJordi AltayóNo ratings yet

- CTC-Continuously Transposed ConductorDocument7 pagesCTC-Continuously Transposed ConductorSAGARNo ratings yet

- Fibra OpticaDocument2 pagesFibra OpticaJORGE ALOR RODRIGUEZNo ratings yet

- Ref10 06259481Document3 pagesRef10 06259481Rajendra ChikkanagoudaNo ratings yet

- OPGW SpecDocument28 pagesOPGW SpecvikasmikkuNo ratings yet

- 10 Christian Schillab-FlukeDocument35 pages10 Christian Schillab-FlukeberrezegNo ratings yet

- DWDM 101 - Introduction To DWDM 2Document107 pagesDWDM 101 - Introduction To DWDM 2Đỗ Quang Huy0% (1)

- DVB-S2 at Incospec SeminarDocument54 pagesDVB-S2 at Incospec SeminarpabloNo ratings yet

- Parameter Kabel Fiber OptikDocument3 pagesParameter Kabel Fiber OptikDaud MaulanaNo ratings yet

- 5g Fronthaul Passive WDM SytemDocument2 pages5g Fronthaul Passive WDM SytemDavoodNo ratings yet

- The Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsFrom EverandThe Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsSylvain ClercNo ratings yet

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDFrom EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDNo ratings yet

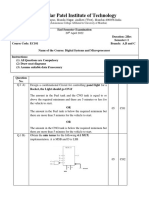

- CamScanner 11-07-2022 17.10Document7 pagesCamScanner 11-07-2022 17.10uzair ahmadNo ratings yet

- T4answers PDFDocument3 pagesT4answers PDFuzair ahmadNo ratings yet

- HW2 SolDocument7 pagesHW2 Soluzair ahmadNo ratings yet

- EE537-Spring 2020 Digital Integrated Circuit Design Instructor: Engr. Dr. Nasir MohyuddinDocument2 pagesEE537-Spring 2020 Digital Integrated Circuit Design Instructor: Engr. Dr. Nasir Mohyuddinuzair ahmadNo ratings yet

- T 2 AnswersDocument2 pagesT 2 Answersuzair ahmadNo ratings yet

- Scanned by CamscannerDocument10 pagesScanned by Camscanneruzair ahmadNo ratings yet

- HW1 SolDocument4 pagesHW1 Soluzair ahmadNo ratings yet

- CVDocument4 pagesCVuzair ahmadNo ratings yet

- HW#08 Analog and Discrete Electronics EE539, SPRING 2020 Submitted By: Muhammad Jawad Shakil STUDENT ID: 20I-1316Document10 pagesHW#08 Analog and Discrete Electronics EE539, SPRING 2020 Submitted By: Muhammad Jawad Shakil STUDENT ID: 20I-1316uzair ahmadNo ratings yet

- TESCO Junior Engineer TestDocument20 pagesTESCO Junior Engineer Testuzair ahmad100% (1)

- Lab Report - 5: Submitted ToDocument5 pagesLab Report - 5: Submitted ToSaif UR RahmanNo ratings yet

- P2003EVG: P-Channel Logic Level Enhancement Mode MOSFETDocument5 pagesP2003EVG: P-Channel Logic Level Enhancement Mode MOSFETWyllyam BarbosaNo ratings yet

- Dual, 8-Bit, Voltage-Output Serial DAC in 8-Pin SO PackageDocument12 pagesDual, 8-Bit, Voltage-Output Serial DAC in 8-Pin SO PackagemvpgmNo ratings yet

- 8051 ArchitectureDocument37 pages8051 ArchitectureALNo ratings yet

- ArduinoDocument14 pagesArduinowmarasigan2610No ratings yet

- Fire Alarm SystemDocument15 pagesFire Alarm SystemnNo ratings yet

- 7 Segment LCDDocument6 pages7 Segment LCDCharawut MasukNo ratings yet

- EASA Mod 5 BK 1 Digital TechDocument79 pagesEASA Mod 5 BK 1 Digital TechaviNo ratings yet

- Vlsi Lab Manual: Department of Information TechnologyDocument135 pagesVlsi Lab Manual: Department of Information TechnologyVijay MythryNo ratings yet

- LM387ANDocument4 pagesLM387ANEl HackerNo ratings yet

- Chapter 17 Differential AmplifiersDocument20 pagesChapter 17 Differential AmplifiersAngelicaNo ratings yet

- Instrumentation AmplifierDocument4 pagesInstrumentation Amplifierjassisc100% (1)

- AN 1059 High CMR Isolation Amplifier For Current SensingDocument9 pagesAN 1059 High CMR Isolation Amplifier For Current Sensing조용규No ratings yet

- 7series SCMDocument623 pages7series SCMyogeee2No ratings yet

- CRT2820 CX-3007Document22 pagesCRT2820 CX-3007Voja ElektronikNo ratings yet

- UHF Digital/Analog Mobile Transceiver Service Manual: Vertex Standard LMR, IncDocument31 pagesUHF Digital/Analog Mobile Transceiver Service Manual: Vertex Standard LMR, IncIng Marco Antonio Hernandez LimaNo ratings yet

- International Training Workshop On FPGA Design For Scientific Instrumentation and Computing 11 - 22 November 2013Document89 pagesInternational Training Workshop On FPGA Design For Scientific Instrumentation and Computing 11 - 22 November 2013saverfimNo ratings yet

- Lab - 7 - Common Emitter AmplifiersDocument6 pagesLab - 7 - Common Emitter AmplifiersAhmed ChNo ratings yet

- DST Tmpm370fydfg-Tde en 21751Document498 pagesDST Tmpm370fydfg-Tde en 21751trân văn tuấnNo ratings yet

- Smartphone Repair CourseDocument14 pagesSmartphone Repair CourseKirsty Joy Bacali50% (2)

- Datasheet PDFDocument38 pagesDatasheet PDFDinh Thuong CaoNo ratings yet

- DSM 2022 EseDocument4 pagesDSM 2022 EsenarendraNo ratings yet

- ch8 12eDocument103 pagesch8 12eareej.fatima1298No ratings yet

- SCH 13Document1 pageSCH 13Roiser DelgadoNo ratings yet

- A 2.4-Ghz Monolithic Fractional-Synthesizer With Robust Phase-Switching Prescaler and Loop Capacitance MultiplierDocument9 pagesA 2.4-Ghz Monolithic Fractional-Synthesizer With Robust Phase-Switching Prescaler and Loop Capacitance MultiplierSampoornaGonellaNo ratings yet

- TTL ProbeDocument2 pagesTTL ProbeSaadNo ratings yet

- Prez1 PDFDocument49 pagesPrez1 PDFDusan SimijonovicNo ratings yet

- Channel Adaptive ADC and TDC For 28 Gb/s PAM-4 Digital ReceiverDocument4 pagesChannel Adaptive ADC and TDC For 28 Gb/s PAM-4 Digital Receiverranickng1No ratings yet

Fun Work (Bonus Points - Group Assignment) : GM GM

Fun Work (Bonus Points - Group Assignment) : GM GM

Uploaded by

uzair ahmadOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Fun Work (Bonus Points - Group Assignment) : GM GM

Fun Work (Bonus Points - Group Assignment) : GM GM

Uploaded by

uzair ahmadCopyright:

Available Formats

Fun Work (Bonus Points – Group Assignment)

Q2: In the university we do the manufacturing through chip brokers. MOSIS, CMP France, and Euro Practice

are three well-known brokers. Here is the Problem, you are a small research group in the company and you have

designed a new kind of the operational amplifier such has the better GBW product and noise performance

compared to all the existing designs.

You want to manufacture few dozen ICs to test your design. Since this is an op-amp and ft of all the

technologies nodes below 350 nm are enough to support this design. You need the ¼ mm 2 of the area for this

CMOS opamp.

Please go through the above three websites and find out that what is the most low cost CMOS technology

node to test this circuit. Please be careful about the minimum area you can order.

What type of the package you will select for this operational amplifier and why? Please also add the cost of

10 packaged dies.

Calculate the total cost you need to tapeout the designed opamp?

{Learning Outcome: Types and Details of the Technologies uses and different coding attached to the process}

Per opamp will require 0.25mm2 .So, for prototying and will be delivered 40 pieces

Foundary Price Minmum area Packaging CostGrand Total

(Euro) (Euro)

Price for Area ≤ Minimum Cost 4500+750=5250

CMP ST Microelectronics ST 65nm 4,500 3 22,500+

5mm2 with minimum

[(Area-5) x 250 + (10 x 49)

CMOS065 charge of 1.25mm2

3,750] 6 including seal-ring. = 740

~1 million pkr

For simplicity I am using 65nm process.

Package:

As in opamp the pin count is low that why QFN is a preferable packaging for IC’s.

QFN is also better for heat due to its metal contacts.

Speed is also a prominent factor in opamp and QFN packaging can handle the speed we require.

QFN is very cost effective and reliable for long use.

It is available in Surface Mount topology.

Total Cost:

Approximately 5500 Euros including shipping cost for 3 dozen IC’s

Q3: We will use the 65nm CMOS from TSMC for your future tape out? What is the ft and fmax of the 65nm

CMOS and what is the Vdd value? Also what is the gm of the minimum size transistor for certain Id.

TSMC 65nm process parameters

Vdd rated =1.2V

gmn= 0.93mA/v for Id=1mA, kn=440uA/V for 65nmos

gmp= 0.53uA/v for Id=1mA, kp=140uA/V for 65nmos

ft =360GHZ fmax=420GHZ

You might also like

- Solucion Problemas de Practica Sadiku PDFDocument14 pagesSolucion Problemas de Practica Sadiku PDFCristian Arevalo Briceño33% (3)

- Optical Con Field Assembly - Technical Info v1.0Document14 pagesOptical Con Field Assembly - Technical Info v1.0Mariano AcostaNo ratings yet

- 2-Attenuation-Limited Fiber LengthDocument3 pages2-Attenuation-Limited Fiber LengthrafatelecomNo ratings yet

- smf28 PDFDocument4 pagessmf28 PDFRODRIGUEZDIAZJJNo ratings yet

- OM4 Fiber - The Next Generation of Multimode: Tony Irujo - Sales Engineer OFSDocument47 pagesOM4 Fiber - The Next Generation of Multimode: Tony Irujo - Sales Engineer OFSgryglewskiaNo ratings yet

- Corning® LEAF® Optical Fiber: Product InformationDocument0 pagesCorning® LEAF® Optical Fiber: Product Informationhcdung18No ratings yet

- Tech. Specification 48fiber Armoured Single Sheath (8tube)Document7 pagesTech. Specification 48fiber Armoured Single Sheath (8tube)Zaman MuhammadNo ratings yet

- PigtailDocument4 pagesPigtailachraf conceptionNo ratings yet

- Hobby Electronics 1978 11 S OCR Vol 1 No 1Document74 pagesHobby Electronics 1978 11 S OCR Vol 1 No 1Annamária ApátiNo ratings yet

- Om4 MM 24 Fiber MTP Female To MTP Female 5m Fiber Optic Patch Cable Data Sheet 242018Document3 pagesOm4 MM 24 Fiber MTP Female To MTP Female 5m Fiber Optic Patch Cable Data Sheet 242018GLsun MallNo ratings yet

- FSC DSF Spool 030c Pdf4Document37 pagesFSC DSF Spool 030c Pdf4Ragu pathiNo ratings yet

- Sip Design and Verification Using AdsDocument34 pagesSip Design and Verification Using AdsMaria Lavinia IordacheNo ratings yet

- Link Design: DR Tahmina AjmalDocument36 pagesLink Design: DR Tahmina Ajmalaamirsaleem54No ratings yet

- LEAF Optical Fiber PDFDocument2 pagesLEAF Optical Fiber PDFShewan Alam SuhreedNo ratings yet

- LS Fiber Optics enDocument48 pagesLS Fiber Optics enboopelectraNo ratings yet

- MTRJ Patch Cable Spec SheetDocument2 pagesMTRJ Patch Cable Spec SheetMohan KNo ratings yet

- Fiber Optic Cable ProductsDocument48 pagesFiber Optic Cable ProductsUdriste DanielNo ratings yet

- Corning SMF-28e Optical Fiber Product InformationDocument4 pagesCorning SMF-28e Optical Fiber Product InformationCompengtech DeptNo ratings yet

- smf28 PDFDocument4 pagessmf28 PDFNahed Ep KhaledNo ratings yet

- Die Manufacturing NewDocument37 pagesDie Manufacturing NewaramacataNo ratings yet

- Om4 MM 24 Fiber MTP Female To MTP Female 2m Fiber Optic Patch Cable Data Sheet 242022Document3 pagesOm4 MM 24 Fiber MTP Female To MTP Female 2m Fiber Optic Patch Cable Data Sheet 242022GLsun MallNo ratings yet

- FOC Link DesignDocument10 pagesFOC Link DesignMilica DrajicNo ratings yet

- CMOS Tech Loose ModDocument17 pagesCMOS Tech Loose ModAjay YadavNo ratings yet

- AMD 45nm Press Presentation 2Document11 pagesAMD 45nm Press Presentation 2Jānis BalgalvisNo ratings yet

- Ufiber Gpon - Designing A Gpon Network: Notes & RequirementsDocument10 pagesUfiber Gpon - Designing A Gpon Network: Notes & RequirementsHeooo GamingNo ratings yet

- Corning SMF-28e Photonic Fiber: Extreme Precision For Demanding OEM ApplicationsDocument4 pagesCorning SMF-28e Photonic Fiber: Extreme Precision For Demanding OEM ApplicationsCHRISTIAN LEZAMA CUELLAR,No ratings yet

- Family - Fiber Optic Patch Cords: MT Mpo/Mtp/MtDocument2 pagesFamily - Fiber Optic Patch Cords: MT Mpo/Mtp/MtMohan KNo ratings yet

- Optical Fiber PigtailDocument2 pagesOptical Fiber PigtailSunny LinNo ratings yet

- OPGW Technical SpecificationDocument56 pagesOPGW Technical SpecificationbinodeNo ratings yet

- SM LightDocument4 pagesSM LighttocviNo ratings yet

- OPGWDocument74 pagesOPGWAnonymous 3y4Z5cUNo ratings yet

- Práctica 1 Módulo 2Document7 pagesPráctica 1 Módulo 2DARCELY ALEJANDRA CANTO DE LA CRUZNo ratings yet

- Cisco CFP2DCO Data SheetDocument8 pagesCisco CFP2DCO Data Sheetd00h0vNyNo ratings yet

- A DQ BN 2y 6-288 E9Document2 pagesA DQ BN 2y 6-288 E9Ade DwinantoNo ratings yet

- FTTH Accessories PDFDocument10 pagesFTTH Accessories PDFdannyalcivarNo ratings yet

- Design of Optical Digital Transmission SystemsDocument51 pagesDesign of Optical Digital Transmission SystemsSimrandeep SinghNo ratings yet

- FO - Technical ParametersDocument3 pagesFO - Technical ParametersReinaldo Sciliano juniorNo ratings yet

- Ixfiber Catalogue 2011Document14 pagesIxfiber Catalogue 2011Patrice CrochetNo ratings yet

- GOHNDocument5 pagesGOHNNadeem HaddadNo ratings yet

- CD and PMD TestDocument4 pagesCD and PMD TestSheik Mohamed AliNo ratings yet

- CS Optical Patch Cable Data Sheet by JTOPTICSDocument7 pagesCS Optical Patch Cable Data Sheet by JTOPTICSJayani Technologies LtdNo ratings yet

- FTTH-OR20 Series Optical ReceiverDocument3 pagesFTTH-OR20 Series Optical Receivermende7No ratings yet

- Texto Que Encontre Por AhiDocument4 pagesTexto Que Encontre Por AhiExerseNo ratings yet

- Scaling PDFDocument72 pagesScaling PDFMayank SinghNo ratings yet

- ITU-T G.652.D SpecsDocument2 pagesITU-T G.652.D SpecsroomforsquaresNo ratings yet

- FO-ESC250D: Mechanical Fiber Optic Connector-Fiber Pre-Embeded TechDocument1 pageFO-ESC250D: Mechanical Fiber Optic Connector-Fiber Pre-Embeded TechDilmer Javier Puel CruzNo ratings yet

- Cisco DWDM OverviewDocument87 pagesCisco DWDM OverviewRishi NandwanaNo ratings yet

- Draka G 652D ESMF - AmericasDocument2 pagesDraka G 652D ESMF - AmericasLuis Gonzalo Tarazona CubaNo ratings yet

- IL2225 L10 ManufacturingDocument29 pagesIL2225 L10 ManufacturingJordi AltayóNo ratings yet

- CTC-Continuously Transposed ConductorDocument7 pagesCTC-Continuously Transposed ConductorSAGARNo ratings yet

- Fibra OpticaDocument2 pagesFibra OpticaJORGE ALOR RODRIGUEZNo ratings yet

- Ref10 06259481Document3 pagesRef10 06259481Rajendra ChikkanagoudaNo ratings yet

- OPGW SpecDocument28 pagesOPGW SpecvikasmikkuNo ratings yet

- 10 Christian Schillab-FlukeDocument35 pages10 Christian Schillab-FlukeberrezegNo ratings yet

- DWDM 101 - Introduction To DWDM 2Document107 pagesDWDM 101 - Introduction To DWDM 2Đỗ Quang Huy0% (1)

- DVB-S2 at Incospec SeminarDocument54 pagesDVB-S2 at Incospec SeminarpabloNo ratings yet

- Parameter Kabel Fiber OptikDocument3 pagesParameter Kabel Fiber OptikDaud MaulanaNo ratings yet

- 5g Fronthaul Passive WDM SytemDocument2 pages5g Fronthaul Passive WDM SytemDavoodNo ratings yet

- The Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsFrom EverandThe Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsSylvain ClercNo ratings yet

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDFrom EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDNo ratings yet

- CamScanner 11-07-2022 17.10Document7 pagesCamScanner 11-07-2022 17.10uzair ahmadNo ratings yet

- T4answers PDFDocument3 pagesT4answers PDFuzair ahmadNo ratings yet

- HW2 SolDocument7 pagesHW2 Soluzair ahmadNo ratings yet

- EE537-Spring 2020 Digital Integrated Circuit Design Instructor: Engr. Dr. Nasir MohyuddinDocument2 pagesEE537-Spring 2020 Digital Integrated Circuit Design Instructor: Engr. Dr. Nasir Mohyuddinuzair ahmadNo ratings yet

- T 2 AnswersDocument2 pagesT 2 Answersuzair ahmadNo ratings yet

- Scanned by CamscannerDocument10 pagesScanned by Camscanneruzair ahmadNo ratings yet

- HW1 SolDocument4 pagesHW1 Soluzair ahmadNo ratings yet

- CVDocument4 pagesCVuzair ahmadNo ratings yet

- HW#08 Analog and Discrete Electronics EE539, SPRING 2020 Submitted By: Muhammad Jawad Shakil STUDENT ID: 20I-1316Document10 pagesHW#08 Analog and Discrete Electronics EE539, SPRING 2020 Submitted By: Muhammad Jawad Shakil STUDENT ID: 20I-1316uzair ahmadNo ratings yet

- TESCO Junior Engineer TestDocument20 pagesTESCO Junior Engineer Testuzair ahmad100% (1)

- Lab Report - 5: Submitted ToDocument5 pagesLab Report - 5: Submitted ToSaif UR RahmanNo ratings yet

- P2003EVG: P-Channel Logic Level Enhancement Mode MOSFETDocument5 pagesP2003EVG: P-Channel Logic Level Enhancement Mode MOSFETWyllyam BarbosaNo ratings yet

- Dual, 8-Bit, Voltage-Output Serial DAC in 8-Pin SO PackageDocument12 pagesDual, 8-Bit, Voltage-Output Serial DAC in 8-Pin SO PackagemvpgmNo ratings yet

- 8051 ArchitectureDocument37 pages8051 ArchitectureALNo ratings yet

- ArduinoDocument14 pagesArduinowmarasigan2610No ratings yet

- Fire Alarm SystemDocument15 pagesFire Alarm SystemnNo ratings yet

- 7 Segment LCDDocument6 pages7 Segment LCDCharawut MasukNo ratings yet

- EASA Mod 5 BK 1 Digital TechDocument79 pagesEASA Mod 5 BK 1 Digital TechaviNo ratings yet

- Vlsi Lab Manual: Department of Information TechnologyDocument135 pagesVlsi Lab Manual: Department of Information TechnologyVijay MythryNo ratings yet

- LM387ANDocument4 pagesLM387ANEl HackerNo ratings yet

- Chapter 17 Differential AmplifiersDocument20 pagesChapter 17 Differential AmplifiersAngelicaNo ratings yet

- Instrumentation AmplifierDocument4 pagesInstrumentation Amplifierjassisc100% (1)

- AN 1059 High CMR Isolation Amplifier For Current SensingDocument9 pagesAN 1059 High CMR Isolation Amplifier For Current Sensing조용규No ratings yet

- 7series SCMDocument623 pages7series SCMyogeee2No ratings yet

- CRT2820 CX-3007Document22 pagesCRT2820 CX-3007Voja ElektronikNo ratings yet

- UHF Digital/Analog Mobile Transceiver Service Manual: Vertex Standard LMR, IncDocument31 pagesUHF Digital/Analog Mobile Transceiver Service Manual: Vertex Standard LMR, IncIng Marco Antonio Hernandez LimaNo ratings yet

- International Training Workshop On FPGA Design For Scientific Instrumentation and Computing 11 - 22 November 2013Document89 pagesInternational Training Workshop On FPGA Design For Scientific Instrumentation and Computing 11 - 22 November 2013saverfimNo ratings yet

- Lab - 7 - Common Emitter AmplifiersDocument6 pagesLab - 7 - Common Emitter AmplifiersAhmed ChNo ratings yet

- DST Tmpm370fydfg-Tde en 21751Document498 pagesDST Tmpm370fydfg-Tde en 21751trân văn tuấnNo ratings yet

- Smartphone Repair CourseDocument14 pagesSmartphone Repair CourseKirsty Joy Bacali50% (2)

- Datasheet PDFDocument38 pagesDatasheet PDFDinh Thuong CaoNo ratings yet

- DSM 2022 EseDocument4 pagesDSM 2022 EsenarendraNo ratings yet

- ch8 12eDocument103 pagesch8 12eareej.fatima1298No ratings yet

- SCH 13Document1 pageSCH 13Roiser DelgadoNo ratings yet

- A 2.4-Ghz Monolithic Fractional-Synthesizer With Robust Phase-Switching Prescaler and Loop Capacitance MultiplierDocument9 pagesA 2.4-Ghz Monolithic Fractional-Synthesizer With Robust Phase-Switching Prescaler and Loop Capacitance MultiplierSampoornaGonellaNo ratings yet

- TTL ProbeDocument2 pagesTTL ProbeSaadNo ratings yet

- Prez1 PDFDocument49 pagesPrez1 PDFDusan SimijonovicNo ratings yet

- Channel Adaptive ADC and TDC For 28 Gb/s PAM-4 Digital ReceiverDocument4 pagesChannel Adaptive ADC and TDC For 28 Gb/s PAM-4 Digital Receiverranickng1No ratings yet