Professional Documents

Culture Documents

Verification of Universal Memory Controller With Memory Using System Verilog

Verification of Universal Memory Controller With Memory Using System Verilog

Uploaded by

IJRASETPublicationsCopyright:

Available Formats

You might also like

- Reflective Competency Statement 2Document1 pageReflective Competency Statement 2api-24090731375% (4)

- Curtain Dahlberg 5th Edition 2016Document73 pagesCurtain Dahlberg 5th Edition 2016Mónica Morales Garcia100% (1)

- Chapter Eight: Influence Tactics of LeadersDocument28 pagesChapter Eight: Influence Tactics of LeadersMCINo ratings yet

- Understanding The Post Industrial City: Metropolis, URBAN RENEWAL AND PUBLIC SPACEDocument15 pagesUnderstanding The Post Industrial City: Metropolis, URBAN RENEWAL AND PUBLIC SPACEPop MadalinaNo ratings yet

- Verification of Dual Port RAM Using System Verilog and UVM: A ReviewDocument6 pagesVerification of Dual Port RAM Using System Verilog and UVM: A ReviewIJRASETPublicationsNo ratings yet

- Research PaperDocument5 pagesResearch PaperVaibhavNo ratings yet

- RTL Design of Cisc Cpu Ip CoreDocument8 pagesRTL Design of Cisc Cpu Ip CoreIJRASETPublicationsNo ratings yet

- Implementation of Automatic College/Industry Bell System Using Visual Studio &ATMEGA 16 MicrocontrollerDocument7 pagesImplementation of Automatic College/Industry Bell System Using Visual Studio &ATMEGA 16 MicrocontrollerIJRASETPublicationsNo ratings yet

- Line Follower and Bluetooth Controlled RobotDocument11 pagesLine Follower and Bluetooth Controlled RobotIJRASETPublicationsNo ratings yet

- VerificationEnvironmentofDualPortRAM AReviewDocument7 pagesVerificationEnvironmentofDualPortRAM AReviewBC RNo ratings yet

- IOT-ques Bank (Sol)Document41 pagesIOT-ques Bank (Sol)Hrithik SahuNo ratings yet

- Arduino Based Congestion Control System For AmbulanceDocument10 pagesArduino Based Congestion Control System For AmbulanceIJRASETPublicationsNo ratings yet

- Arduino-Based Embedded System ModuleDocument8 pagesArduino-Based Embedded System ModuleIJRASETPublicationsNo ratings yet

- The Electricity Billing System Over IOTDocument7 pagesThe Electricity Billing System Over IOTIJRASETPublicationsNo ratings yet

- Ijet V4i3p95 PDFDocument8 pagesIjet V4i3p95 PDFInternational Journal of Engineering and TechniquesNo ratings yet

- A Unified UVM Architecture For Flash-Based MemoryDocument4 pagesA Unified UVM Architecture For Flash-Based MemoryUsha KrishnaNo ratings yet

- Embedded Systems (All Units)Document250 pagesEmbedded Systems (All Units)ezhiltham0% (2)

- Designand Verificationof Dual Port RAMusing System Verilog MethodologyDocument7 pagesDesignand Verificationof Dual Port RAMusing System Verilog MethodologySACHIN SINGHNo ratings yet

- Smart Car Parking System Using Arduino UNODocument8 pagesSmart Car Parking System Using Arduino UNOIJRASETPublicationsNo ratings yet

- Smart Parking System Using Machine Learning and Internet of ThingsDocument9 pagesSmart Parking System Using Machine Learning and Internet of ThingsIJRASETPublicationsNo ratings yet

- Embedded Trainer BoardDocument5 pagesEmbedded Trainer BoardSolomon AkpanNo ratings yet

- Password Protected Electronic Lock System For Smart Home SecurityDocument6 pagesPassword Protected Electronic Lock System For Smart Home SecurityRiya ShettyNo ratings yet

- Electronics 13 00120 With CoverDocument15 pagesElectronics 13 00120 With CoverSRIRAAM VSNo ratings yet

- Designand Verificationof Dual Port RAMusing System Verilog MethodologyDocument7 pagesDesignand Verificationof Dual Port RAMusing System Verilog MethodologyB Chakradhar ReddyNo ratings yet

- Designing of Telecommand System Using System On Chip Soc For Spacecraft Control ApplicationsDocument11 pagesDesigning of Telecommand System Using System On Chip Soc For Spacecraft Control ApplicationsIAEME PublicationNo ratings yet

- CPE 352 Computer ArchitectureDocument4 pagesCPE 352 Computer ArchitectureIBITAYO TOLUWALASENo ratings yet

- Design and Implementation of Energy-Efficient Floating Point MFCC Extraction Architecture For Speech Recognition SystemsDocument11 pagesDesign and Implementation of Energy-Efficient Floating Point MFCC Extraction Architecture For Speech Recognition SystemsIJRASETPublicationsNo ratings yet

- Implementation of PLC Based Automated CNG Tank For Chuter Assembly LineDocument9 pagesImplementation of PLC Based Automated CNG Tank For Chuter Assembly LineIJRASETPublicationsNo ratings yet

- 8284 ManualDocument82 pages8284 ManualTecer Tecer50% (2)

- Study On Transformation To Universal Verification MethodologyDocument5 pagesStudy On Transformation To Universal Verification MethodologyIJRASETPublicationsNo ratings yet

- IoT Based Smart Factory Over The CloudDocument6 pagesIoT Based Smart Factory Over The CloudIJRASETPublicationsNo ratings yet

- Designing of A 16 Bit Microprocessor's Functional Units - CPU, ALU and RAMDocument5 pagesDesigning of A 16 Bit Microprocessor's Functional Units - CPU, ALU and RAMijaertNo ratings yet

- Battery Management System To Find Accurate TimingDocument9 pagesBattery Management System To Find Accurate TimingIJRASETPublicationsNo ratings yet

- Design and Analysis of Automatic ForkliftDocument6 pagesDesign and Analysis of Automatic ForkliftIJRASETPublicationsNo ratings yet

- SoC NotesDocument22 pagesSoC Notesabha mauryaNo ratings yet

- Re Engineering Traditional Learning Model With Outcome Based Learning Curve Using Embedded Training LaboratoryDocument11 pagesRe Engineering Traditional Learning Model With Outcome Based Learning Curve Using Embedded Training LaboratoryEditor IJTSRDNo ratings yet

- Fail-Proof Over The Air Firmware Upgrade For Embedded Systems PDFDocument80 pagesFail-Proof Over The Air Firmware Upgrade For Embedded Systems PDFi_am_in02No ratings yet

- 1st Review Report - Smart Distribution SystemDocument54 pages1st Review Report - Smart Distribution SystemretechNo ratings yet

- Smart Armed Robot For Military Application: Bachelor of Technology IN Electronics and Communication EngineeringDocument46 pagesSmart Armed Robot For Military Application: Bachelor of Technology IN Electronics and Communication EngineeringTimothy AbrahamNo ratings yet

- Smart HelmetDocument5 pagesSmart HelmetIJARSCT JournalNo ratings yet

- Chapter 1 PDFDocument127 pagesChapter 1 PDFAhmed Al-MasoodiNo ratings yet

- An Introductionto Functional Verificationof I2 CDocument6 pagesAn Introductionto Functional Verificationof I2 CAtharva VazeNo ratings yet

- Embedded SystemDocument30 pagesEmbedded Systemajas777BNo ratings yet

- 10 Embedded SystemsDocument74 pages10 Embedded SystemsFarumaNo ratings yet

- Voice Controlled Robot Vehicle Using ArduinoDocument8 pagesVoice Controlled Robot Vehicle Using ArduinoIJRASETPublicationsNo ratings yet

- Microprocessor Exp 1Document4 pagesMicroprocessor Exp 1Marc Daniel YbañezNo ratings yet

- Automatic Door Access Control System Based On Facial Recognition Using ESP32-CAMDocument7 pagesAutomatic Door Access Control System Based On Facial Recognition Using ESP32-CAMIJRASETPublicationsNo ratings yet

- Module 4 Living in The IT EraDocument8 pagesModule 4 Living in The IT ErakvelezNo ratings yet

- Internet Controlled DroneDocument7 pagesInternet Controlled DroneIJRASETPublicationsNo ratings yet

- Development of Verification Environment For I2C Controller Using System Verilog and UVMDocument9 pagesDevelopment of Verification Environment For I2C Controller Using System Verilog and UVMMeghana VeggalamNo ratings yet

- 2017 OpenCPUDocument6 pages2017 OpenCPUNgô Đức ViệtNo ratings yet

- An Analytical Search For Efficient Microcontroller-On Board Computer For Veltech-NanoSatDocument5 pagesAn Analytical Search For Efficient Microcontroller-On Board Computer For Veltech-NanoSatprabhu kumarNo ratings yet

- Proposal of A Reliable Embedded Circuit To Control A Stepper Motor Using Microblaze Soft-Core ProcessorDocument11 pagesProposal of A Reliable Embedded Circuit To Control A Stepper Motor Using Microblaze Soft-Core ProcessorIJRES teamNo ratings yet

- Result Paper On IOT Based Induction Motor Speed Control and Parameter MonitoringDocument8 pagesResult Paper On IOT Based Induction Motor Speed Control and Parameter MonitoringIJRASETPublicationsNo ratings yet

- 10 2348 Ijset06150601Document3 pages10 2348 Ijset06150601satyendraNo ratings yet

- Main ReportDocument46 pagesMain Reportkrish4allindians100% (3)

- Auto Intensity Control of Street LightDocument53 pagesAuto Intensity Control of Street LightNikhith ReddyNo ratings yet

- Module 1 (Part 1)Document103 pagesModule 1 (Part 1)SAATHVIK SHEKARNo ratings yet

- Mini Project DocumentationDocument43 pagesMini Project Documentationmgitecetech100% (6)

- Bioelex Pr5Document28 pagesBioelex Pr5Eagle CoolNo ratings yet

- Testbench Development and Verification of Memory Controller: Aparajita Lenka, G. ShashibhushanDocument5 pagesTestbench Development and Verification of Memory Controller: Aparajita Lenka, G. ShashibhushanscribdresNo ratings yet

- Test SocDocument133 pagesTest SocjeevithaNo ratings yet

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipFrom EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNo ratings yet

- Digital Electronics, Computer Architecture and Microprocessor Design PrinciplesFrom EverandDigital Electronics, Computer Architecture and Microprocessor Design PrinciplesNo ratings yet

- Design and Analysis of Fixed-Segment Carrier at Carbon Thrust BearingDocument10 pagesDesign and Analysis of Fixed-Segment Carrier at Carbon Thrust BearingIJRASETPublicationsNo ratings yet

- Study and Analysis of Non-Newtonian Fluid Speed BumpDocument8 pagesStudy and Analysis of Non-Newtonian Fluid Speed BumpIJRASETPublicationsNo ratings yet

- Survey On Different Morphology Detection TechniquesDocument5 pagesSurvey On Different Morphology Detection TechniquesIJRASETPublicationsNo ratings yet

- Adsorption Study On Waste Water Characteristics by Using Natural Bio-AdsorbentsDocument6 pagesAdsorption Study On Waste Water Characteristics by Using Natural Bio-AdsorbentsIJRASETPublicationsNo ratings yet

- Study and Analysis of Non-Newtonian Fluid Speed BumpDocument8 pagesStudy and Analysis of Non-Newtonian Fluid Speed BumpIJRASETPublicationsNo ratings yet

- IoT-Based Smart Medicine DispenserDocument8 pagesIoT-Based Smart Medicine DispenserIJRASETPublications100% (1)

- IoT Based Safety System For BAJA VehicleDocument7 pagesIoT Based Safety System For BAJA VehicleIJRASETPublicationsNo ratings yet

- Se of Optimism Software To Observe Effect of Different Sources in Optical FiberDocument7 pagesSe of Optimism Software To Observe Effect of Different Sources in Optical FiberIJRASETPublicationsNo ratings yet

- Air Conditioning Heat Load Analysis of A CabinDocument9 pagesAir Conditioning Heat Load Analysis of A CabinIJRASETPublicationsNo ratings yet

- BIM Data Analysis and Visualization WorkflowDocument7 pagesBIM Data Analysis and Visualization WorkflowIJRASETPublicationsNo ratings yet

- Advanced Wireless Multipurpose Mine Detection RobotDocument7 pagesAdvanced Wireless Multipurpose Mine Detection RobotIJRASETPublicationsNo ratings yet

- Role of Artificial Intelligence in Emotion RecognitionDocument5 pagesRole of Artificial Intelligence in Emotion RecognitionIJRASETPublicationsNo ratings yet

- Survey On Battery Explosion Detection SystemDocument7 pagesSurvey On Battery Explosion Detection SystemIJRASETPublicationsNo ratings yet

- Design and Analysis of Components in Off-Road VehicleDocument23 pagesDesign and Analysis of Components in Off-Road VehicleIJRASETPublicationsNo ratings yet

- A Review On Speech Emotion Classification Using Linear Predictive Coding and Neural NetworksDocument5 pagesA Review On Speech Emotion Classification Using Linear Predictive Coding and Neural NetworksIJRASETPublicationsNo ratings yet

- Structural Analysis of The Performance of The Diagrid System With and Without Shear WallDocument13 pagesStructural Analysis of The Performance of The Diagrid System With and Without Shear WallIJRASETPublicationsNo ratings yet

- 11 V May 2023Document34 pages11 V May 2023IJRASETPublicationsNo ratings yet

- Topology Optimisation of PistonDocument8 pagesTopology Optimisation of PistonIJRASETPublicationsNo ratings yet

- Controlled Hand Gestures Using Python and OpenCVDocument7 pagesControlled Hand Gestures Using Python and OpenCVIJRASETPublicationsNo ratings yet

- Real Time Human Body Posture Analysis Using Deep LearningDocument7 pagesReal Time Human Body Posture Analysis Using Deep LearningIJRASETPublications100% (1)

- TNP Portal Using Web Development and Machine LearningDocument9 pagesTNP Portal Using Web Development and Machine LearningIJRASETPublicationsNo ratings yet

- Skill Verification System Using Blockchain SkillVioDocument6 pagesSkill Verification System Using Blockchain SkillVioIJRASETPublicationsNo ratings yet

- Smart Parking System Using MERN StackDocument6 pagesSmart Parking System Using MERN StackIJRASETPublicationsNo ratings yet

- Design and Analysis of Fixed Brake Caliper Using Additive ManufacturingDocument9 pagesDesign and Analysis of Fixed Brake Caliper Using Additive ManufacturingIJRASETPublicationsNo ratings yet

- Credit Card Fraud Detection Using Machine Learning and BlockchainDocument9 pagesCredit Card Fraud Detection Using Machine Learning and BlockchainIJRASETPublications100% (1)

- Image Detection and Real Time Object DetectionDocument8 pagesImage Detection and Real Time Object DetectionIJRASETPublicationsNo ratings yet

- Pneumonia Detection Using X-Rays by Deep LearningDocument6 pagesPneumonia Detection Using X-Rays by Deep LearningIJRASETPublicationsNo ratings yet

- Fund Future Empowering The CrowdfundingDocument6 pagesFund Future Empowering The CrowdfundingIJRASETPublicationsNo ratings yet

- Comparative in Vivo Study On Quality Analysis On Bisacodyl of Different BrandsDocument17 pagesComparative in Vivo Study On Quality Analysis On Bisacodyl of Different BrandsIJRASETPublicationsNo ratings yet

- CryptoDrive A Decentralized Car Sharing SystemDocument9 pagesCryptoDrive A Decentralized Car Sharing SystemIJRASETPublications100% (1)

- Philip B. Magtaan, Rcrim, Mscrim, CSP: LecturerDocument13 pagesPhilip B. Magtaan, Rcrim, Mscrim, CSP: LecturerPhilip MagtaanNo ratings yet

- Lexical and Grammatical Peculiarities of Scientific-Technical TextsDocument39 pagesLexical and Grammatical Peculiarities of Scientific-Technical TextsLyudmila Anastasjeva67% (3)

- Basketball Lesson Plans June 5Document31 pagesBasketball Lesson Plans June 5Stephen GimoteaNo ratings yet

- Gumstix Launches Raspberry Pi CM4 Series and Free ManufacturingDocument3 pagesGumstix Launches Raspberry Pi CM4 Series and Free ManufacturingPR.comNo ratings yet

- Balaji ResumeDocument3 pagesBalaji ResumeNaveen KumarNo ratings yet

- PHNLChartsDocument52 pagesPHNLChartsBagasNo ratings yet

- Best Practices and Strategies For High Speed Rail EnergyDocument98 pagesBest Practices and Strategies For High Speed Rail Energythuy giangNo ratings yet

- Describe The Fundamentals of The Doctrine of Binding PrecedentDocument3 pagesDescribe The Fundamentals of The Doctrine of Binding PrecedentSaadat Bin SiddiqueNo ratings yet

- MBA PESTEL - Bajaj RE60 - The Branding Challenge of Disruptive Innovation PESTEL - PEST AnalysisDocument8 pagesMBA PESTEL - Bajaj RE60 - The Branding Challenge of Disruptive Innovation PESTEL - PEST AnalysisNaunihal KumarNo ratings yet

- Effect of Urbanization On Hydrological Response in Case of Gondar City 1Document3 pagesEffect of Urbanization On Hydrological Response in Case of Gondar City 1cher bisetegnNo ratings yet

- Political Discourse Analysis: Group 10 The MembersDocument27 pagesPolitical Discourse Analysis: Group 10 The MembersAdhe AgnityNo ratings yet

- Mountaineering CourseDocument4 pagesMountaineering CourseEvelyn MedinaNo ratings yet

- 3-HOW CAN THE STRATEGY CHANGE-p.27-OKDocument27 pages3-HOW CAN THE STRATEGY CHANGE-p.27-OKari wibowoNo ratings yet

- Havelock North Primary School CharterDocument37 pagesHavelock North Primary School CharterJoshua WoodhamNo ratings yet

- Running Head: Whistle Blowing: Assignment 4 1Document4 pagesRunning Head: Whistle Blowing: Assignment 4 1highness149No ratings yet

- Safety Officer - ROLES & RESPONSIBILITIESDocument19 pagesSafety Officer - ROLES & RESPONSIBILITIESrashmi_shantikumar69% (29)

- Report On Most and Least Learned Skills SECOND QUARTER, S.Y. 2020-2021Document2 pagesReport On Most and Least Learned Skills SECOND QUARTER, S.Y. 2020-2021Crisanta CañeteNo ratings yet

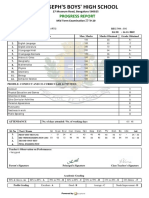

- ST Joseph'S Boys' High School: Progress ReportDocument1 pageST Joseph'S Boys' High School: Progress Reportvanessa martisNo ratings yet

- AIA-Four Levels of Evidence-Based PracticeDocument2 pagesAIA-Four Levels of Evidence-Based PracticeMatt KriseNo ratings yet

- Homeroom Guidance: Siyahan Nga Bahin - Modyul 2: An Akon GintikanganDocument10 pagesHomeroom Guidance: Siyahan Nga Bahin - Modyul 2: An Akon GintikangansaraiNo ratings yet

- Commission On Higher Education Baao Community College: InterpretationDocument40 pagesCommission On Higher Education Baao Community College: InterpretationAvegail MantesNo ratings yet

- Appolo Study Centre: TNPSC Group I Preliminary 2019 Test Batch Postal TrainingDocument10 pagesAppolo Study Centre: TNPSC Group I Preliminary 2019 Test Batch Postal TrainingvijaythealmightyNo ratings yet

- en The Effect of Packaging Satisfaction andDocument9 pagesen The Effect of Packaging Satisfaction andJanet MuisNo ratings yet

- Impact of Government Policies and EthicsDocument24 pagesImpact of Government Policies and EthicsGunveen AbrolNo ratings yet

- Organizational Knowledge Creation Theory: Evolutionary Paths and Future AdvancesDocument30 pagesOrganizational Knowledge Creation Theory: Evolutionary Paths and Future AdvancesPutri DewintariNo ratings yet

- Enhanced ground proximity warning system (EGPWS) : Kirilchev Vladislav ЛЭ (С) -19Document13 pagesEnhanced ground proximity warning system (EGPWS) : Kirilchev Vladislav ЛЭ (С) -19Мария Попелющенко100% (1)

Verification of Universal Memory Controller With Memory Using System Verilog

Verification of Universal Memory Controller With Memory Using System Verilog

Uploaded by

IJRASETPublicationsOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Verification of Universal Memory Controller With Memory Using System Verilog

Verification of Universal Memory Controller With Memory Using System Verilog

Uploaded by

IJRASETPublicationsCopyright:

Available Formats

8 VII July 2020

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429

Volume 8 Issue VII July 2020- Available at www.ijraset.com

Verification of Universal Memory Controller with

Memory using System Verilog

S P Vignesh1, Dr. Radhakrishna Rao2

1

Student, Dept of ECE, P.E.S. College of Engineering Mandya,

2

Professor & Head of the Department, Dept of ECE, P.E.S. College of Engineering Mandya

Abstract: Functional verification mainly based on coverage driven constraint. The universal memory controller is aiming

to advance the performance of the prevailing memory controllers through a complete integration of the all memory in

addition of providing novel features. It mainly serves as one amongst the basic important feature that’s lagging in most of

memory controller that is power being consumed. The aim of the paper is to validate the design and to generate regression

test cases in the test-bench in order to obtain 100% functional coverage using System Verilog (SV) and a typical code

coverage.

Keywords: WISHBONE, SDRAM, FLASH

I. INTRODUCTION

For any electronic device memory plays a major role in reading and writing data into it. For any data to be written or read into

memory it requires a prominent element known as memory controller. The very important aspect of memory controllers is to equip

reasonable interface and protocol between the host and the memories to efficiently handle data, maximize transfer speed, data

integrity and information retention. For SoC(system on chip) having multiple memory many memory controllers may have to

accessed for individual memory, Which will add on space in SoC. This design mainly overcome the problem confronted by existing

memory controller by addition of novel features. This reduces power being consumed by the design. So, henceforth the design

controlling multiple memories to be verified by generating the test cases.

II. UNIVERSAL MEMORY CONTROLLER

Fig. 1 Proposed Interface Of The Universal Memory Controller

As it can be seen in the Fig-1 the processor connects the controller through wishbone interface and memory module linked to the

UMC(universal memory controller). These communicate

when memory requires a signal for particular operations and when request is generated by processor

A. Wishbone Interface

The wishbone interface is a portable IP(intellectual property) core, it is mainly used in semiconductor IP for flexible design

methodology. Wishbone mainly possess great features like reusability, portability and trustworthiness for the system. This is can be done

by creating a common interface amidst IP cores this results in faster time-to-market for the end user.

Fig. 2 WISHBONE Interface Block

It supports a 32bit bus width and does not support other bus width. The wishbone interface performs very simple decoding of

wishbone signals wb_write_go represent a write cycle, while wb_read_go indicates a read cycle, wb_first denotes the initial transfer

of a possible burst, and wb_wait clearly depicts wait state insertion on the wishbone bus.

©IJRASET: All Rights are Reserved 621

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429

Volume 8 Issue VII July 2020- Available at www.ijraset.com

B. Universal Memory Controller (UMC)

The memory controller is a digital circuit which manage the flow of data going to and from the main memory. A memory controller

can be a individual chip or integrated into another chip, such as being incorporated on the same die or as an core part of

a microprocessor; in the other case, it is usually called an Integrated Memory Controller (IMC). A memory controller may also be

termed as Memory Chip Controller (MCC) or a Memory Controller Unit (MCU).

The Memory Controller becomes prominent due to following features

1) 8 chip selects, each uniquely programmable

2) Burst transfer and Burst termination

3) Supports RMW(Read Modify Write) cycles

4) Dynamic bus sizing for reading from Asynchronous devices

5) Default boot sequence support

6) Supports power down mode

7) Up to 8*64MB memory size

UMC is sited amidst wishbone and memory module. These blocks are interlinked by wishbone interface, memory interface to the

UMC.

C. Memory Modules

A memory module is a printed circuit board on which memory integrated circuits are mounted.

Various memory of which universal memory controller is verified are:

1) Flash Memory

2) Synchronous Dynamic Random Access Memory

III. VERIFICATION OF UMC

The process of evaluating correctness of design and to avoid surprises at a later time, to avoid a re-spin of the chip, to enter the

market on time with good quality the verification plays a key role.

In the process of verification, modules are verified by driving the correct and an error input, in both cases need to observe the design

whether it is behaving as expected,.

In verification, the exactness of the design under test (DUT) are mainly determined by creating testbench environment

Below is the functionality of the Testbench/Verification environment,

1) Generate stimulus

2) Apply stimulus to the DUT

3) Capture the response

4) Check for the correctness

5) Measure progress against the overall verification goals

Environment contain a generator (gen), Bus Functional Module (BFM), monitor, reference module, coverage, checker and

scoreboard

Fig. 3 Testbench environment of wishbone protocol

In Fig 4 Testbench environment of wishbone protocol depicts while in the creation of environment first we start with the top module,

followed by creation of generator, bus functional module, monitor, checker, reference module, and interface

©IJRASET: All Rights are Reserved 622

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429

Volume 8 Issue VII July 2020- Available at www.ijraset.com

IV. MEMORY INTERFACE TO UMC

A. SDRAM Module

Synchronous Dynamic Random Access Memory(SDRAM) are quicker than Asynchronous DRAM.As it is synchronous in nature

changes in clock along with input side causes changes in output. SDRAM memory comprise of four banks, due to which transaction

of data happens faster than any other memories

Fig . 4: Interface of SDRAM with Memory Controller

Fig 4:Pin diagram of memory controller and SDRAM both blocks are interfaced by memory interface shown in figure.

The data from memory controller is written to the memory of SDRAM in one address location and from same address location data is

read back to the memory controller.

Fig. 4 SDRAM Read and Write

B. FLASH Module

Flash module is a non-volatile memory chip that can only be erased electrically and by reprogramming it. These are mainly

accessed whenever the data needs to be stored for a longer interval of time.

Fig -7: Interface of FLASH with Memory Controller

©IJRASET: All Rights are Reserved 623

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429

Volume 8 Issue VII July 2020- Available at www.ijraset.com

Fig. 8 Flash Read and Write

C. Functional Coverage

Functional coverage is code that observes execution of a test plan. As such, it is code we write to track whether important values,

sets of values, or sequences of values that corresponds to design or interface requirements, features or boundary conditions has been

exercised.

Functional coverage is important to any verification approach since it is one of the factors used to determine when testing is done.

Specifically ,100%functional coverage indicates that all items in the test plan have been tested

Fig. 9 Functional coverage report

D. Code Coverage

Code coverage tracks what lines of code or expressions in the code have been exercised. Normally there may be cases in which case

statement or extra undocumented features in the design may not have not have exercised in normal hardware operation. So in order

to either remove or exercise untested feature. So henceforth along with functional coverage its very important to make use of code

coverage

Fig. 10 Code coverage report

©IJRASET: All Rights are Reserved 624

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429

Volume 8 Issue VII July 2020- Available at www.ijraset.com

V. CONCLUSIONS

Memory is the integral part of any processer, comprising of various memory present on SoC. Instead of accessing multiple memory

controller for different memory an individual or one memory controller been used called Universal Memory Controller(UMC). In this

thesis, various memories possessing different characteristics is been verified. Waveform suggest that data being sent through wishbone

and retrieved back to be same and multiple characteristics is been verified . Along with-it functional coverage of 100% is obtained which

indicates all functionality of design is verified followed with its code coverage is done to verify all the cases are taken into account .

REFERENCES

[1] Khaled Salah Alexandria University Mentor Graphics “Implementation and Verification of A Generic Universal Memory Controller Based On UVM”

International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS), 978-1-4799-1999-4©2015 IEEE

[2] Jagadeesha Kolour, Nagendra Reddy, Venkata Siva Reddy3“Design Verification of Universal Memory Controller IP Core (UMC) using System Verilog

Architecture” International Research Journal of Engineering and Technology (IRJET), e-ISSN: 2395-0056 Volume: 06 Issue: 05 | May 2019

[3] Sharada Pattar, Mrs. Rashmi S Bhaskarn “Verification of Universal Memory Controller” International Research Journal of Engineering and Technology

(IRJET), e-ISSN: 2395 -0056 Volume: 04 Issue: 05 | May -2017

[4] Memory Controller IP Core by Rudolf Usselmann ,January21,2002

[5] Aparajita Lenka,G Shashibhushan “Development and Verification Of Memory Controller”

[6] A Reconfigurable Real-Time SDRAM Controller for Mixed Time-Criticality Systems 978-1-4799-1417-3/13/$31.00

©2013 IEEE

[7] A Novel AHB Based SDRAM Memory Controller International journal of research in Computer and Communication Technology, Vol4, Issue 6, June-2015J.

www.ijrcct.org

[8] MohdWajid,Shahank SB, ”Architecture for Faster RAM Controller Design with Inbuilt Memory”, IEEE ,2010 ARM, AMBA Specification Rev.2.0, 1999.

“Memory Controllers for Real-Time Embedded systems” Benny Akesson

[9] “Memory Controller Architectures: A comparative Study” 978-1-4799-35253/13/$31.00 ©2013 IEEE

©IJRASET: All Rights are Reserved 625

You might also like

- Reflective Competency Statement 2Document1 pageReflective Competency Statement 2api-24090731375% (4)

- Curtain Dahlberg 5th Edition 2016Document73 pagesCurtain Dahlberg 5th Edition 2016Mónica Morales Garcia100% (1)

- Chapter Eight: Influence Tactics of LeadersDocument28 pagesChapter Eight: Influence Tactics of LeadersMCINo ratings yet

- Understanding The Post Industrial City: Metropolis, URBAN RENEWAL AND PUBLIC SPACEDocument15 pagesUnderstanding The Post Industrial City: Metropolis, URBAN RENEWAL AND PUBLIC SPACEPop MadalinaNo ratings yet

- Verification of Dual Port RAM Using System Verilog and UVM: A ReviewDocument6 pagesVerification of Dual Port RAM Using System Verilog and UVM: A ReviewIJRASETPublicationsNo ratings yet

- Research PaperDocument5 pagesResearch PaperVaibhavNo ratings yet

- RTL Design of Cisc Cpu Ip CoreDocument8 pagesRTL Design of Cisc Cpu Ip CoreIJRASETPublicationsNo ratings yet

- Implementation of Automatic College/Industry Bell System Using Visual Studio &ATMEGA 16 MicrocontrollerDocument7 pagesImplementation of Automatic College/Industry Bell System Using Visual Studio &ATMEGA 16 MicrocontrollerIJRASETPublicationsNo ratings yet

- Line Follower and Bluetooth Controlled RobotDocument11 pagesLine Follower and Bluetooth Controlled RobotIJRASETPublicationsNo ratings yet

- VerificationEnvironmentofDualPortRAM AReviewDocument7 pagesVerificationEnvironmentofDualPortRAM AReviewBC RNo ratings yet

- IOT-ques Bank (Sol)Document41 pagesIOT-ques Bank (Sol)Hrithik SahuNo ratings yet

- Arduino Based Congestion Control System For AmbulanceDocument10 pagesArduino Based Congestion Control System For AmbulanceIJRASETPublicationsNo ratings yet

- Arduino-Based Embedded System ModuleDocument8 pagesArduino-Based Embedded System ModuleIJRASETPublicationsNo ratings yet

- The Electricity Billing System Over IOTDocument7 pagesThe Electricity Billing System Over IOTIJRASETPublicationsNo ratings yet

- Ijet V4i3p95 PDFDocument8 pagesIjet V4i3p95 PDFInternational Journal of Engineering and TechniquesNo ratings yet

- A Unified UVM Architecture For Flash-Based MemoryDocument4 pagesA Unified UVM Architecture For Flash-Based MemoryUsha KrishnaNo ratings yet

- Embedded Systems (All Units)Document250 pagesEmbedded Systems (All Units)ezhiltham0% (2)

- Designand Verificationof Dual Port RAMusing System Verilog MethodologyDocument7 pagesDesignand Verificationof Dual Port RAMusing System Verilog MethodologySACHIN SINGHNo ratings yet

- Smart Car Parking System Using Arduino UNODocument8 pagesSmart Car Parking System Using Arduino UNOIJRASETPublicationsNo ratings yet

- Smart Parking System Using Machine Learning and Internet of ThingsDocument9 pagesSmart Parking System Using Machine Learning and Internet of ThingsIJRASETPublicationsNo ratings yet

- Embedded Trainer BoardDocument5 pagesEmbedded Trainer BoardSolomon AkpanNo ratings yet

- Password Protected Electronic Lock System For Smart Home SecurityDocument6 pagesPassword Protected Electronic Lock System For Smart Home SecurityRiya ShettyNo ratings yet

- Electronics 13 00120 With CoverDocument15 pagesElectronics 13 00120 With CoverSRIRAAM VSNo ratings yet

- Designand Verificationof Dual Port RAMusing System Verilog MethodologyDocument7 pagesDesignand Verificationof Dual Port RAMusing System Verilog MethodologyB Chakradhar ReddyNo ratings yet

- Designing of Telecommand System Using System On Chip Soc For Spacecraft Control ApplicationsDocument11 pagesDesigning of Telecommand System Using System On Chip Soc For Spacecraft Control ApplicationsIAEME PublicationNo ratings yet

- CPE 352 Computer ArchitectureDocument4 pagesCPE 352 Computer ArchitectureIBITAYO TOLUWALASENo ratings yet

- Design and Implementation of Energy-Efficient Floating Point MFCC Extraction Architecture For Speech Recognition SystemsDocument11 pagesDesign and Implementation of Energy-Efficient Floating Point MFCC Extraction Architecture For Speech Recognition SystemsIJRASETPublicationsNo ratings yet

- Implementation of PLC Based Automated CNG Tank For Chuter Assembly LineDocument9 pagesImplementation of PLC Based Automated CNG Tank For Chuter Assembly LineIJRASETPublicationsNo ratings yet

- 8284 ManualDocument82 pages8284 ManualTecer Tecer50% (2)

- Study On Transformation To Universal Verification MethodologyDocument5 pagesStudy On Transformation To Universal Verification MethodologyIJRASETPublicationsNo ratings yet

- IoT Based Smart Factory Over The CloudDocument6 pagesIoT Based Smart Factory Over The CloudIJRASETPublicationsNo ratings yet

- Designing of A 16 Bit Microprocessor's Functional Units - CPU, ALU and RAMDocument5 pagesDesigning of A 16 Bit Microprocessor's Functional Units - CPU, ALU and RAMijaertNo ratings yet

- Battery Management System To Find Accurate TimingDocument9 pagesBattery Management System To Find Accurate TimingIJRASETPublicationsNo ratings yet

- Design and Analysis of Automatic ForkliftDocument6 pagesDesign and Analysis of Automatic ForkliftIJRASETPublicationsNo ratings yet

- SoC NotesDocument22 pagesSoC Notesabha mauryaNo ratings yet

- Re Engineering Traditional Learning Model With Outcome Based Learning Curve Using Embedded Training LaboratoryDocument11 pagesRe Engineering Traditional Learning Model With Outcome Based Learning Curve Using Embedded Training LaboratoryEditor IJTSRDNo ratings yet

- Fail-Proof Over The Air Firmware Upgrade For Embedded Systems PDFDocument80 pagesFail-Proof Over The Air Firmware Upgrade For Embedded Systems PDFi_am_in02No ratings yet

- 1st Review Report - Smart Distribution SystemDocument54 pages1st Review Report - Smart Distribution SystemretechNo ratings yet

- Smart Armed Robot For Military Application: Bachelor of Technology IN Electronics and Communication EngineeringDocument46 pagesSmart Armed Robot For Military Application: Bachelor of Technology IN Electronics and Communication EngineeringTimothy AbrahamNo ratings yet

- Smart HelmetDocument5 pagesSmart HelmetIJARSCT JournalNo ratings yet

- Chapter 1 PDFDocument127 pagesChapter 1 PDFAhmed Al-MasoodiNo ratings yet

- An Introductionto Functional Verificationof I2 CDocument6 pagesAn Introductionto Functional Verificationof I2 CAtharva VazeNo ratings yet

- Embedded SystemDocument30 pagesEmbedded Systemajas777BNo ratings yet

- 10 Embedded SystemsDocument74 pages10 Embedded SystemsFarumaNo ratings yet

- Voice Controlled Robot Vehicle Using ArduinoDocument8 pagesVoice Controlled Robot Vehicle Using ArduinoIJRASETPublicationsNo ratings yet

- Microprocessor Exp 1Document4 pagesMicroprocessor Exp 1Marc Daniel YbañezNo ratings yet

- Automatic Door Access Control System Based On Facial Recognition Using ESP32-CAMDocument7 pagesAutomatic Door Access Control System Based On Facial Recognition Using ESP32-CAMIJRASETPublicationsNo ratings yet

- Module 4 Living in The IT EraDocument8 pagesModule 4 Living in The IT ErakvelezNo ratings yet

- Internet Controlled DroneDocument7 pagesInternet Controlled DroneIJRASETPublicationsNo ratings yet

- Development of Verification Environment For I2C Controller Using System Verilog and UVMDocument9 pagesDevelopment of Verification Environment For I2C Controller Using System Verilog and UVMMeghana VeggalamNo ratings yet

- 2017 OpenCPUDocument6 pages2017 OpenCPUNgô Đức ViệtNo ratings yet

- An Analytical Search For Efficient Microcontroller-On Board Computer For Veltech-NanoSatDocument5 pagesAn Analytical Search For Efficient Microcontroller-On Board Computer For Veltech-NanoSatprabhu kumarNo ratings yet

- Proposal of A Reliable Embedded Circuit To Control A Stepper Motor Using Microblaze Soft-Core ProcessorDocument11 pagesProposal of A Reliable Embedded Circuit To Control A Stepper Motor Using Microblaze Soft-Core ProcessorIJRES teamNo ratings yet

- Result Paper On IOT Based Induction Motor Speed Control and Parameter MonitoringDocument8 pagesResult Paper On IOT Based Induction Motor Speed Control and Parameter MonitoringIJRASETPublicationsNo ratings yet

- 10 2348 Ijset06150601Document3 pages10 2348 Ijset06150601satyendraNo ratings yet

- Main ReportDocument46 pagesMain Reportkrish4allindians100% (3)

- Auto Intensity Control of Street LightDocument53 pagesAuto Intensity Control of Street LightNikhith ReddyNo ratings yet

- Module 1 (Part 1)Document103 pagesModule 1 (Part 1)SAATHVIK SHEKARNo ratings yet

- Mini Project DocumentationDocument43 pagesMini Project Documentationmgitecetech100% (6)

- Bioelex Pr5Document28 pagesBioelex Pr5Eagle CoolNo ratings yet

- Testbench Development and Verification of Memory Controller: Aparajita Lenka, G. ShashibhushanDocument5 pagesTestbench Development and Verification of Memory Controller: Aparajita Lenka, G. ShashibhushanscribdresNo ratings yet

- Test SocDocument133 pagesTest SocjeevithaNo ratings yet

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipFrom EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNo ratings yet

- Digital Electronics, Computer Architecture and Microprocessor Design PrinciplesFrom EverandDigital Electronics, Computer Architecture and Microprocessor Design PrinciplesNo ratings yet

- Design and Analysis of Fixed-Segment Carrier at Carbon Thrust BearingDocument10 pagesDesign and Analysis of Fixed-Segment Carrier at Carbon Thrust BearingIJRASETPublicationsNo ratings yet

- Study and Analysis of Non-Newtonian Fluid Speed BumpDocument8 pagesStudy and Analysis of Non-Newtonian Fluid Speed BumpIJRASETPublicationsNo ratings yet

- Survey On Different Morphology Detection TechniquesDocument5 pagesSurvey On Different Morphology Detection TechniquesIJRASETPublicationsNo ratings yet

- Adsorption Study On Waste Water Characteristics by Using Natural Bio-AdsorbentsDocument6 pagesAdsorption Study On Waste Water Characteristics by Using Natural Bio-AdsorbentsIJRASETPublicationsNo ratings yet

- Study and Analysis of Non-Newtonian Fluid Speed BumpDocument8 pagesStudy and Analysis of Non-Newtonian Fluid Speed BumpIJRASETPublicationsNo ratings yet

- IoT-Based Smart Medicine DispenserDocument8 pagesIoT-Based Smart Medicine DispenserIJRASETPublications100% (1)

- IoT Based Safety System For BAJA VehicleDocument7 pagesIoT Based Safety System For BAJA VehicleIJRASETPublicationsNo ratings yet

- Se of Optimism Software To Observe Effect of Different Sources in Optical FiberDocument7 pagesSe of Optimism Software To Observe Effect of Different Sources in Optical FiberIJRASETPublicationsNo ratings yet

- Air Conditioning Heat Load Analysis of A CabinDocument9 pagesAir Conditioning Heat Load Analysis of A CabinIJRASETPublicationsNo ratings yet

- BIM Data Analysis and Visualization WorkflowDocument7 pagesBIM Data Analysis and Visualization WorkflowIJRASETPublicationsNo ratings yet

- Advanced Wireless Multipurpose Mine Detection RobotDocument7 pagesAdvanced Wireless Multipurpose Mine Detection RobotIJRASETPublicationsNo ratings yet

- Role of Artificial Intelligence in Emotion RecognitionDocument5 pagesRole of Artificial Intelligence in Emotion RecognitionIJRASETPublicationsNo ratings yet

- Survey On Battery Explosion Detection SystemDocument7 pagesSurvey On Battery Explosion Detection SystemIJRASETPublicationsNo ratings yet

- Design and Analysis of Components in Off-Road VehicleDocument23 pagesDesign and Analysis of Components in Off-Road VehicleIJRASETPublicationsNo ratings yet

- A Review On Speech Emotion Classification Using Linear Predictive Coding and Neural NetworksDocument5 pagesA Review On Speech Emotion Classification Using Linear Predictive Coding and Neural NetworksIJRASETPublicationsNo ratings yet

- Structural Analysis of The Performance of The Diagrid System With and Without Shear WallDocument13 pagesStructural Analysis of The Performance of The Diagrid System With and Without Shear WallIJRASETPublicationsNo ratings yet

- 11 V May 2023Document34 pages11 V May 2023IJRASETPublicationsNo ratings yet

- Topology Optimisation of PistonDocument8 pagesTopology Optimisation of PistonIJRASETPublicationsNo ratings yet

- Controlled Hand Gestures Using Python and OpenCVDocument7 pagesControlled Hand Gestures Using Python and OpenCVIJRASETPublicationsNo ratings yet

- Real Time Human Body Posture Analysis Using Deep LearningDocument7 pagesReal Time Human Body Posture Analysis Using Deep LearningIJRASETPublications100% (1)

- TNP Portal Using Web Development and Machine LearningDocument9 pagesTNP Portal Using Web Development and Machine LearningIJRASETPublicationsNo ratings yet

- Skill Verification System Using Blockchain SkillVioDocument6 pagesSkill Verification System Using Blockchain SkillVioIJRASETPublicationsNo ratings yet

- Smart Parking System Using MERN StackDocument6 pagesSmart Parking System Using MERN StackIJRASETPublicationsNo ratings yet

- Design and Analysis of Fixed Brake Caliper Using Additive ManufacturingDocument9 pagesDesign and Analysis of Fixed Brake Caliper Using Additive ManufacturingIJRASETPublicationsNo ratings yet

- Credit Card Fraud Detection Using Machine Learning and BlockchainDocument9 pagesCredit Card Fraud Detection Using Machine Learning and BlockchainIJRASETPublications100% (1)

- Image Detection and Real Time Object DetectionDocument8 pagesImage Detection and Real Time Object DetectionIJRASETPublicationsNo ratings yet

- Pneumonia Detection Using X-Rays by Deep LearningDocument6 pagesPneumonia Detection Using X-Rays by Deep LearningIJRASETPublicationsNo ratings yet

- Fund Future Empowering The CrowdfundingDocument6 pagesFund Future Empowering The CrowdfundingIJRASETPublicationsNo ratings yet

- Comparative in Vivo Study On Quality Analysis On Bisacodyl of Different BrandsDocument17 pagesComparative in Vivo Study On Quality Analysis On Bisacodyl of Different BrandsIJRASETPublicationsNo ratings yet

- CryptoDrive A Decentralized Car Sharing SystemDocument9 pagesCryptoDrive A Decentralized Car Sharing SystemIJRASETPublications100% (1)

- Philip B. Magtaan, Rcrim, Mscrim, CSP: LecturerDocument13 pagesPhilip B. Magtaan, Rcrim, Mscrim, CSP: LecturerPhilip MagtaanNo ratings yet

- Lexical and Grammatical Peculiarities of Scientific-Technical TextsDocument39 pagesLexical and Grammatical Peculiarities of Scientific-Technical TextsLyudmila Anastasjeva67% (3)

- Basketball Lesson Plans June 5Document31 pagesBasketball Lesson Plans June 5Stephen GimoteaNo ratings yet

- Gumstix Launches Raspberry Pi CM4 Series and Free ManufacturingDocument3 pagesGumstix Launches Raspberry Pi CM4 Series and Free ManufacturingPR.comNo ratings yet

- Balaji ResumeDocument3 pagesBalaji ResumeNaveen KumarNo ratings yet

- PHNLChartsDocument52 pagesPHNLChartsBagasNo ratings yet

- Best Practices and Strategies For High Speed Rail EnergyDocument98 pagesBest Practices and Strategies For High Speed Rail Energythuy giangNo ratings yet

- Describe The Fundamentals of The Doctrine of Binding PrecedentDocument3 pagesDescribe The Fundamentals of The Doctrine of Binding PrecedentSaadat Bin SiddiqueNo ratings yet

- MBA PESTEL - Bajaj RE60 - The Branding Challenge of Disruptive Innovation PESTEL - PEST AnalysisDocument8 pagesMBA PESTEL - Bajaj RE60 - The Branding Challenge of Disruptive Innovation PESTEL - PEST AnalysisNaunihal KumarNo ratings yet

- Effect of Urbanization On Hydrological Response in Case of Gondar City 1Document3 pagesEffect of Urbanization On Hydrological Response in Case of Gondar City 1cher bisetegnNo ratings yet

- Political Discourse Analysis: Group 10 The MembersDocument27 pagesPolitical Discourse Analysis: Group 10 The MembersAdhe AgnityNo ratings yet

- Mountaineering CourseDocument4 pagesMountaineering CourseEvelyn MedinaNo ratings yet

- 3-HOW CAN THE STRATEGY CHANGE-p.27-OKDocument27 pages3-HOW CAN THE STRATEGY CHANGE-p.27-OKari wibowoNo ratings yet

- Havelock North Primary School CharterDocument37 pagesHavelock North Primary School CharterJoshua WoodhamNo ratings yet

- Running Head: Whistle Blowing: Assignment 4 1Document4 pagesRunning Head: Whistle Blowing: Assignment 4 1highness149No ratings yet

- Safety Officer - ROLES & RESPONSIBILITIESDocument19 pagesSafety Officer - ROLES & RESPONSIBILITIESrashmi_shantikumar69% (29)

- Report On Most and Least Learned Skills SECOND QUARTER, S.Y. 2020-2021Document2 pagesReport On Most and Least Learned Skills SECOND QUARTER, S.Y. 2020-2021Crisanta CañeteNo ratings yet

- ST Joseph'S Boys' High School: Progress ReportDocument1 pageST Joseph'S Boys' High School: Progress Reportvanessa martisNo ratings yet

- AIA-Four Levels of Evidence-Based PracticeDocument2 pagesAIA-Four Levels of Evidence-Based PracticeMatt KriseNo ratings yet

- Homeroom Guidance: Siyahan Nga Bahin - Modyul 2: An Akon GintikanganDocument10 pagesHomeroom Guidance: Siyahan Nga Bahin - Modyul 2: An Akon GintikangansaraiNo ratings yet

- Commission On Higher Education Baao Community College: InterpretationDocument40 pagesCommission On Higher Education Baao Community College: InterpretationAvegail MantesNo ratings yet

- Appolo Study Centre: TNPSC Group I Preliminary 2019 Test Batch Postal TrainingDocument10 pagesAppolo Study Centre: TNPSC Group I Preliminary 2019 Test Batch Postal TrainingvijaythealmightyNo ratings yet

- en The Effect of Packaging Satisfaction andDocument9 pagesen The Effect of Packaging Satisfaction andJanet MuisNo ratings yet

- Impact of Government Policies and EthicsDocument24 pagesImpact of Government Policies and EthicsGunveen AbrolNo ratings yet

- Organizational Knowledge Creation Theory: Evolutionary Paths and Future AdvancesDocument30 pagesOrganizational Knowledge Creation Theory: Evolutionary Paths and Future AdvancesPutri DewintariNo ratings yet

- Enhanced ground proximity warning system (EGPWS) : Kirilchev Vladislav ЛЭ (С) -19Document13 pagesEnhanced ground proximity warning system (EGPWS) : Kirilchev Vladislav ЛЭ (С) -19Мария Попелющенко100% (1)