Professional Documents

Culture Documents

Application Note: EMC Design Guide F MC-8L Family

Application Note: EMC Design Guide F MC-8L Family

Uploaded by

Mr CdtOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Application Note: EMC Design Guide F MC-8L Family

Application Note: EMC Design Guide F MC-8L Family

Uploaded by

Mr CdtCopyright:

Available Formats

Fujitsu Microelectronics Europe MCU-AN-389024-E-V11

Application Note

EMC Design Guide

F2MC-8L Family

© Fujitsu Mikroelektronik GmbH, Microcontroller Application Group

History

04th Jul 02 NFL V1.0 Initial draft

18th Jul. 02 NFl V1.1 Description DeCap added

MCU-AN-389024-E-V11 -1- © Fujitsu Microelectronics Europe GmbH

Warranty and Disclaimer

To the maximum extent permitted by applicable law, Fujitsu Mikroelektronik GmbH restricts its warranties and

its liability for all products delivered free of charge (eg. software include or header files, application examples,

application Notes, target boards, evaluation boards, engineering samples of IC’s etc.), its performance and any

consequential damages, on the use of the Product in accordance with (i) the terms of the License Agreement and

the Sale and Purchase Agreement under which agreements the Product has been delivered, (ii) the technical

descriptions and (iii) all accompanying written materials. In addition, to the maximum extent permitted by

applicable law, Fujitsu Mikroelektronik GmbH disclaims all warranties and liabilities for the performance of the

Product and any consequential damages in cases of unauthorised decompiling and/or reverse engineering and/or

disassembling. Note, all these products are intended and must only be used in an evaluation laboratory

environment.

1. Fujitsu Mikroelektronik GmbH warrants that the Product will perform substantially in accordance with

the accompanying written materials for a period of 90 days form the date of receipt by the customer.

Concerning the hardware components of the Product, Fujitsu Mikroelektronik GmbH warrants that the

Product will be free from defects in material and workmanship under use and service as specified in the

accompanying written materials for a duration of 1 year from the date of receipt by the customer.

2. Should a Product turn out to be defect, Fujitsu Mikroelektronik GmbH´s entire liability and the

customer’s exclusive remedy shall be, at Fujitsu Mikroelektronik GmbH´s sole discretion, either return

of the purchase price and the license fee, or replacement of the Product or parts thereof, if the Product is

returned to Fujitsu Mikroelektronik GmbH in original packing and without further defects resulting

from the customer’s use or the transport. However, this warranty is excluded if the defect has resulted

from an accident not attributable to Fujitsu Mikroelektronik GmbH, or abuse or misapplication

attributable to the customer or any other third party not relating to Fujitsu Mikroelektronik GmbH.

3. To the maximum extent permitted by applicable law Fujitsu Mikroelektronik GmbH disclaims all other

warranties, whether expressed or implied, in particular, but not limited to, warranties of merchantability

and fitness for a particular purpose for which the Product is not designated.

4. To the maximum extent permitted by applicable law, Fujitsu Mikroelektronik GmbH´s and its suppliers´

liability is restricted to intention and gross negligence.

NO LIABILITY FOR CONSEQUENTIAL DAMAGES

To the maximum extent permitted by applicable law, in no event shall Fujitsu Mikroelektronik

GmbH and its suppliers be liable for any damages whatsoever (including but without limitation,

consequential and/or indirect damages for personal injury, assets of substantial value, loss of

profits, interruption of business operation, loss of information, or any other monetary or

pecuniary loss) arising from the use of the Product.

Should one of the above stipulations be or become invalid and/or unenforceable, the remaining stipulations shall

stay in full effect.

© Fujitsu Microelectronics Europe GmbH -2- MCU-AN-389024-E-V11

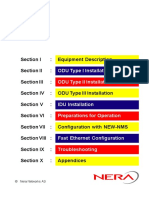

Table of Contents:

1 INTRODUCTION 4

2 RULES TO CREATE A GOOD LAYOUT 4

3 CRYSTAL OSCILLATOR CIRCUIT 5

4 POWER SUPPLY ROUTING 6

5 NOISE REDUCTION FOR GENERAL IO PINS 9

6 FUNCTION OF CERTAIN MCU PINS 9

7 EMI MEASUREMENT FOR F2MC-8L FAMILY 10

7.1 Measurement setup 10

7.2 Measurement procedure 10

7.3 Measurements 10

7.4 Blank check 11

7.5 Noise measurements on VCC 11

MCU-AN-389024-E-V111 -3- © Fujitsu Microelectronics Europe GmbH

1 Introduction

In the following description, the EMC design guide of 8-bit Fujitsu microcontroller will be

discussed. It describes how external power supply should be connected to the Vcc and Vss

pins and offers some suggestions. An overview of internal supply of MCU is made as well to

have a better understanding of the design. The EMI measurements in the following described

tests are just example measurements. The measured emissions are no data, which are

specified in the DS of the microcontroller series.

During the last designs the EMI of the Fujitsu F2MC-8L microcontroller series could be

reduced step by step. The PLL multiplier circuit allows the usage of low crystal frequency to

reduce high-frequency noise from the oscillator circuit.

The clock tree is mostly the cause of the noise. Therefore the driver capability of clock

buffers is optimised and for one big buffer are used several small clock buffers.

The integration of On-chip bypass capacitors reduces the noise ripple on the internal power

supply net so that the broadband noise on the IO pins is improved.

The following description is based on the MB89530 series, but the same situation exists for

all current devices of the F2MC-8L family, with or without an external bus interface.

2 Rules to create a good Layout

1. Use max. trace-width and min. length to connect VSS and VDD :C-pins to decoupling

capacitors (DeCap)

2. Don’t use stub line to connect the DeCap to :C-pins, let flows the noise current direct

through pads of DeCap

3. Use close ground plane direct below MCU package as shield

4. Use different ground systems for analogue, digital, power-driver and connector

ground

5. Avoid loop current in the ground system, check for ground loops.

6. Use a star point ground below MCU for analogue and digital ground, use a second

star point ground below 5V regulator for MCU, power-driver and connector ground

7. Don't create signal loop on the PCB, minimize trace length

8. Partitioned system into analogue, digital and power-driver section

9. Place series resistor or RC-block for the IO-circuit nearby MCU-pin to reduce the

noise on the signal line.

10. Use a capacitor for each connector pin to reduce the noise of external lines, place this

capacitor close to connector pin

© Fujitsu Microelectronics Europe GmbH -4- MCU-AN-389024-E-V11

3 Crystal Oscillator Circuit

Figure 1 shows the oscillator for the 8-bit family. For best performance, the PCB layout of this

circuit should cover only a very small area. For the layout is recommended a PCB with two or

more layers. Make sure to provide bypass capacitors via shortest distance from X0, X1 pins,

crystal oscillator, and ground lines. The lines of the oscillation circuit should not cross lines of

other circuits.

X0 X1

Microcontroller

Oscillator

Figure 1: Principle of the Oscillator circuit

It is necessary to avoid coupling noise into the power supply (pin 81/84) of the clock circuit.

The crystal oscillator has to be connected with short lines to X0/X1 and Vss. Note that pin X1

is the output of inverter. Particularly this track should have a short length.

Decoupling capacitor C B on

the back side of the PCB

Decoupling capacitor C B on

the back side of the PCB Via to ground island Via to system Vcc

and system ground CB

CB

Vss Vcc Vss Vcc

X0 X1 X0 X1 Single ground island

on the back side

Connection to Connection to

C1 C2

ground layer ground layer

SMD

Via to ground island

on the back side Quartz Crystal

Quartz

Quartz Crystal package C1 C2

Crystal has to be grounded

Connection to

ground layer

a) Layout example for a leaded quartz crystal b) Layout example for a SMD quartz crystal

worse layout design, because C1 and C2 better layout design, because C1 and C2

are wrong connected to VSS are connected to Vss and than after with

the system ground

Figure 2: Layout example for oscillator circuit

MCU-AN-389024-E-V111 -5- © Fujitsu Microelectronics Europe GmbH

4 Power supply routing

One topic our noise reduction technology is the bypass capacitors. By placing of modules

inside the chip, it is possible to connect a bypass capacitor with low impedance where power

supply lines are short, effectively reducing the noise to very low flow levels. These bypass

capacitors are place into power supply of IO and logic.

I/O-PORT

ROM

Vcc

Vss

CPU

RAM

SCI / TIMER / etc.

A/D+D/A

AVcc AVss

Figure 3: Structure of power supply for MCU core and IO-Port

VCC VCC VCC

:C :C

:C

DeCap DeCap DeCap

GND

GND GND

a) VCC and GND lead to supply b) GND lead noise to system GND c) GND lead noise to System GND

noise current flows not via noise current flows partly via noise current flows partly via

DeCap, DeCap has not effect DeCap, DeCap has hardly effect DeCap, DeCap has hardly effect

VCC

:C VCC

:C VCC

:C

DeCap

DeCap DeCap

GND

GND

GND

GND

d) VCC and GND lead to supply e) GND is not short connected to f) DeCap correct connected to :C

noise current flows not via DeCap. between GND and and power supply.

DeCap, DeCap has not effect DeCap flows a loop current high speed current will be

DeCap has hardly effect supported from DeCap

Figure 4: The exactly use of the DeCap (decoupling capacitor)

© Fujitsu Microelectronics Europe GmbH -6- MCU-AN-389024-E-V11

The high-speed current (di/dt) will be supported from the decoupling capacitor only.

Therefore use traces with max. width and min. length between Vss/Vcc pin and DeCap.

After DeCap use thin traces to route the trace to the power supply system.

use EMC filter for short length

:C-supply max. width

:C

high Z low Z

VCC

C

GND

Figure 5: The noise current flows return over the ground line

The exactly use of decoupling capacitors for the Vcc and Vss pins is the basis to reduce the

noise, but also the return way between load and MCU ground is not neglect.

high-Z min. length min. length

low-Z

choking coil max. width max. width

VCC

:C HVCC

I supply

clock

unit

C & IO-driver

C

VSS HVSS

core

I slow I fast I crossbar I return

dt/di

R C Load

I load

Figure 6: The noise current flows return over the ground line

To ensure an efficient decoupling of the power supply, two capacitors should be placed close

on each Vcc pin. The values of both capacitors should have a relationship of about 1:100.

Typical values are e.g. 100nF (XR7) and 1nF (COG). The accurate value is depended on the

application board, e.g. impedance of PCB or the length of supply lines. However, all of the

DeCaps on the PCB should have the same value.

Lboard Lboard

VDD

IC1 IC2 ICn

DeCap C1

DeCap C2

DeCap Cn

Cboard

f

GND

Figure 7: The use of several values of DeCaps lead to undefined resonance frequencies,

that’s why all DeCaps should have the same value.

MCU-AN-389024-E-V111 -7- © Fujitsu Microelectronics Europe GmbH

For 2-layer boards should be used a closed ground plane (located directly below the MCU).

The Vcc supplies should be taken from the bottom layer.

For 4-layer boards should be used the inside layers for GND and Vcc supplies. In this case,

both layers form additional capacitor (broadband behaviour) for the power supply.

Figure 8 shows a layout example for the connection of powers supply on the MCU.

This method of Vcc connection reduces the loop of the Vcc lines around the MCU, thus

reducing noise emission. A variation of this circuit may be needed, if separate filtered supply

voltages are routed to the A/D supplies (pin AVCC/AVSS).

Connection to star point and noise

power supply filter for Decoupling capacitor C B on

Vcc and ground the back side of the PCB

Vcc

on the back side

ground plan

below package

on the top side

CB

CB

LB

Via to ground island

and system ground

Decoupling capacitor C B on

the back side of the PCB

AVcc

CB

AVR

AVss

X0A

X1A Via to ground island

and system ground

C1

32kHz

C2

C1

Rs

Via to ground island

Single ground island on the back side

on the back side C2

Quartz

Crystal

Vss

X0

X1

2

Figure 8: F MC-8L family with main- and subclock,

recommended layout for multiple layers PCB

Note: All decoupling capacitors on the Vcc pins should have the same value.

These capacitors should be placed close to the Vcc pin. The Vcc/Vss current should flows

through the pad of the capacitor.

© Fujitsu Microelectronics Europe GmbH -8- MCU-AN-389024-E-V11

5 Noise reduction for general IO pins

To reduce noise, make sure to connect the Vss or Vcc with smoothed power supply, because

the noise on the power supply will also distributed via IO-pin, which is configured as static

low or high output. Figure 9 shows an example to reduce the noise on output lines.

:C :C

IO-Port IO-Port

Noise

length of trace length of trace

Figure 9: Place the series resistor close to IO pin because so will be reduced the noise

of output

Note: To reduce noise, make sure to connect unused input pins to Vss or Vcc (Use pull-down

or pull-up resistor, please check the DS of the microcontroller series).

Also, especially if CMOS Logic is used, floating gates could generate problems regarding high

input currents and latch up.

6 Function of certain MCU pins

Pin name Function

VDD Main supply for IO buffer and MCU core

VSS Main supply for IO buffer and MCU core

close to crystal oscillator

AVCC Power supply for the A/D converter

AVR Reference voltage input for the A/D converter

AVSS Power supply for the A/D converter

X0 Oscillator input, if not used so shall be connected with

X0A pull-up or pull-down resistor (see please DS)

X1 Oscillator output, the crystal and bypass capacitor

X1A must be connected via shortest distance with X1 pin,

if not used so shall be open

MCU-AN-389024-E-V111 -9- © Fujitsu Microelectronics Europe GmbH

7 EMI Measurement for F2MC-8L family

7.1 Measurement setup

Figure 10: Set-up for noise measurement on power supply

7.2 Measurement procedure

- RF- voltage, measured on VCC power supply by BI mode RUN

- RF- voltage, measured on VCC power supply by BI mode RESET

7.3 Measurements

Sample: MB89538A, MB89538AL, MB89535A

Measurement condition: Ta = 25 deg.C

Power supply: Vcc = 5.0V / 3.0V

Crystal: 8MHz (FAR)

Frequency range: 0MHz to 120MHz, BW: 120kHz

© Fujitsu Microelectronics Europe GmbH - 10 - MCU-AN-389024-E-V11

7.4 Blank check

Figure 11: Noise measured on VCC power supply, blank check

7.5 Noise measurements on VCC

Figure 12: MB89538A - Noise measured on VCC power supply, BI-mode RUN

MCU-AN-389024-E-V111 - 11 - © Fujitsu Microelectronics Europe GmbH

Figure 13: MB89538AL - Noise measured on VCC power supply, BI-mode RUN

Figure 14: MB89535A - Noise measured on VCC power supply, BI-mode RUN

© Fujitsu Microelectronics Europe GmbH - 12 - MCU-AN-389024-E-V11

You might also like

- PHILIPS HTL2110, HTL2112, HTL2196 Service ManualDocument49 pagesPHILIPS HTL2110, HTL2112, HTL2196 Service ManualMohamad Hafiz Md TahirNo ratings yet

- Sharp AQUOS LC - (32/40/46/52) LE700UN Service ManualDocument156 pagesSharp AQUOS LC - (32/40/46/52) LE700UN Service Manualvobios78% (32)

- Introduction to Power System ProtectionFrom EverandIntroduction to Power System ProtectionRating: 4 out of 5 stars4/5 (2)

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- SIFANG CSC-103 V1.41 Line PTT User Manual ENUDocument7 pagesSIFANG CSC-103 V1.41 Line PTT User Manual ENURaúlEmirGutiérrezLópezNo ratings yet

- BFT LIBRA Control PanelDocument10 pagesBFT LIBRA Control PanelAADAFFAFASASNo ratings yet

- DAVR Series Automatic Voltage Regulator Users ManualDocument20 pagesDAVR Series Automatic Voltage Regulator Users ManualriyantoNo ratings yet

- ITYS-E 6-10kVA MSMITYTWXX31-GB 00Document24 pagesITYS-E 6-10kVA MSMITYTWXX31-GB 00Anuradhe ThilakarathnaNo ratings yet

- S3 Radio-Remote-Control Scanreco 20120503Document14 pagesS3 Radio-Remote-Control Scanreco 20120503tsdcn100% (1)

- Model No. SA-AKX12LM-K - PanasonicDocument108 pagesModel No. SA-AKX12LM-K - PanasonicSimon MariñoNo ratings yet

- NSX BL24Document31 pagesNSX BL24Alfredo Smith MurrayNo ratings yet

- Vestel - Chassis - 17mb11 2 SERV BOLDocument71 pagesVestel - Chassis - 17mb11 2 SERV BOLsinfo338No ratings yet

- 14315Document35 pages14315suresh_geraldNo ratings yet

- zITYS MSDocument24 pageszITYS MSAnuradhe ThilakarathnaNo ratings yet

- Designing-an-RF-Remote-Control-WPDocument7 pagesDesigning-an-RF-Remote-Control-WPmamonicanamocaNo ratings yet

- Bts 3000Document19 pagesBts 3000Braham DevNo ratings yet

- Datasheet PS S9014 CDocument7 pagesDatasheet PS S9014 CLiliana Araujo AbdalaNo ratings yet

- Manual SA-MAX500 Manual de Servicio PDFDocument133 pagesManual SA-MAX500 Manual de Servicio PDFAbel GaunaNo ratings yet

- Electrical BOQ TOWER-1Document53 pagesElectrical BOQ TOWER-1Sudheer Vojjala100% (1)

- OPTRIS CT ManualDocument58 pagesOPTRIS CT ManualrbucholzNo ratings yet

- Apple m8536 TFT LCDDocument28 pagesApple m8536 TFT LCDDaniel Avecilla100% (1)

- Retrofitting A Telematics Control Unit With Bluetooth Technology TCU B841405 E9xDocument6 pagesRetrofitting A Telematics Control Unit With Bluetooth Technology TCU B841405 E9xnmaiorNo ratings yet

- MC44BC380Document10 pagesMC44BC380judas_priest_12345No ratings yet

- Aiwa+Nsx t929lh CX Nt929Document43 pagesAiwa+Nsx t929lh CX Nt929caririnetworkNo ratings yet

- Tcd650bx Service ManulDocument79 pagesTcd650bx Service ManulcvijovicNo ratings yet

- VHF Marine Transceiver: S-14720XZ-C1 Apr. 2011Document27 pagesVHF Marine Transceiver: S-14720XZ-C1 Apr. 2011song_trangNo ratings yet

- Akira CT21TF9 CH 3Y01 (Z LA8633xx) - TrybDocument13 pagesAkira CT21TF9 CH 3Y01 (Z LA8633xx) - TrybDaniel AvecillaNo ratings yet

- NERA CityLink - User Manual - 2 PDFDocument375 pagesNERA CityLink - User Manual - 2 PDFRiky Fitriadi50% (2)

- Service Manual: Model #: VIZIO VW46L FHDTV10A - MT5382 - AUODocument22 pagesService Manual: Model #: VIZIO VW46L FHDTV10A - MT5382 - AUObud31202000No ratings yet

- Newtec Mod 2080Document120 pagesNewtec Mod 2080jean27000100% (2)

- 【b】30240301001287 使用说明书 储能三相 sun (25 50) k sg01hp3 - 221103 - 190919Document53 pages【b】30240301001287 使用说明书 储能三相 sun (25 50) k sg01hp3 - 221103 - 190919Mohammed Abdullah AwadhNo ratings yet

- 【b】30240301001287 使用说明书 储能三相 sun (25 50) k sg01hp3 - 240311 - 201912Document52 pages【b】30240301001287 使用说明书 储能三相 sun (25 50) k sg01hp3 - 240311 - 201912Alexis ArayaNo ratings yet

- Av02 0891en - Ds - Acpl m60l - 2017 03 03 1827568Document15 pagesAv02 0891en - Ds - Acpl m60l - 2017 03 03 1827568mikeguo76No ratings yet

- Noblex: SERVICE MANUAL Colour TelevisionDocument29 pagesNoblex: SERVICE MANUAL Colour Televisionjose4445No ratings yet

- 1MRK504161-BEN A en Product Guide Transformer Protection RET650 2.1Document68 pages1MRK504161-BEN A en Product Guide Transformer Protection RET650 2.1osmpotNo ratings yet

- Solis Manual S6-EH3P (3-10) K-H EUR V1.3 (20230818)Document56 pagesSolis Manual S6-EH3P (3-10) K-H EUR V1.3 (20230818)vicmarcamNo ratings yet

- Datasheet - 8BVI - 1 - HWS - E - 039 ACOPOS MULTI 0-901-37-385-4Document14 pagesDatasheet - 8BVI - 1 - HWS - E - 039 ACOPOS MULTI 0-901-37-385-4fernandocushwakeNo ratings yet

- JVC Lt17c50bu LCD TV PDFDocument12 pagesJVC Lt17c50bu LCD TV PDFMicro EmissionNo ratings yet

- JVC LCD Lt-19db1buDocument64 pagesJVC LCD Lt-19db1bungoclinhdtddNo ratings yet

- JVC LCD Lt-26dc1bhDocument78 pagesJVC LCD Lt-26dc1bhngoclinhdtddNo ratings yet

- JVC LCD Lt-26de1bj - BuDocument83 pagesJVC LCD Lt-26de1bj - BungoclinhdtddNo ratings yet

- User Manual: Manufactured by ItalyDocument66 pagesUser Manual: Manufactured by ItalyRaul Angel Perez AbadNo ratings yet

- Elenberg 1402,2108,21F08,29F08 Service ManualDocument85 pagesElenberg 1402,2108,21F08,29F08 Service ManualalexanderNo ratings yet

- BlueOptics BO32J13210D 10GBASE-LR X2 Transceiver 1310nm 10 Kilometer Singlemode SC-Duplex 10 GigabitDocument9 pagesBlueOptics BO32J13210D 10GBASE-LR X2 Transceiver 1310nm 10 Kilometer Singlemode SC-Duplex 10 GigabitCBO GmbHNo ratings yet

- PLF-77TD Servive ManualDocument29 pagesPLF-77TD Servive Manualapi-3711045100% (1)

- Zone Selective Interlocking On Instantaneous (I-ZSI) PDFDocument7 pagesZone Selective Interlocking On Instantaneous (I-ZSI) PDFjumpingjack229No ratings yet

- Panasonic Sa-Akx77lm-K SMDocument104 pagesPanasonic Sa-Akx77lm-K SMLesther GonzálezNo ratings yet

- Assembling The Arduino Diecimila Compatible Freeduino Board USBDocument8 pagesAssembling The Arduino Diecimila Compatible Freeduino Board USBMC. Rene Solis R.No ratings yet

- JVC LCD Lt-26db1buDocument65 pagesJVC LCD Lt-26db1bungoclinhdtddNo ratings yet

- XZone Service Manual 1.2Document20 pagesXZone Service Manual 1.2Abraham BongòNo ratings yet

- AA104VC08 MitsubishiDocument23 pagesAA104VC08 MitsubishiJosé AdelinoNo ratings yet

- JVC AV-21M315 - M335-Service - Manual PDFDocument32 pagesJVC AV-21M315 - M335-Service - Manual PDFkilol0No ratings yet

- Sony Icf-Cd815 Ver.1.0Document36 pagesSony Icf-Cd815 Ver.1.0elvergajojoNo ratings yet

- Automated Optical Inspection: Advancements in Computer Vision TechnologyFrom EverandAutomated Optical Inspection: Advancements in Computer Vision TechnologyNo ratings yet

- The Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsFrom EverandThe Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsSylvain ClercNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- The Importance of Capacitance: Issue 2, January 2005Document12 pagesThe Importance of Capacitance: Issue 2, January 2005Mr CdtNo ratings yet

- Recommended Reading: Issue 4, May 2005Document10 pagesRecommended Reading: Issue 4, May 2005Mr CdtNo ratings yet

- DAC2009 - User - Track - Session - 1.1 - STMicroelectronics - 0Document35 pagesDAC2009 - User - Track - Session - 1.1 - STMicroelectronics - 0Mr CdtNo ratings yet

- Issue 5, August 2005: in This Issue Tips and TricksDocument8 pagesIssue 5, August 2005: in This Issue Tips and TricksMr CdtNo ratings yet

- Issue 3, March 2005: Rodger RicheyDocument12 pagesIssue 3, March 2005: Rodger RicheyMr CdtNo ratings yet

- Enc Inverter: Shenzhen Encom Electric Technologies Co., LTDDocument16 pagesEnc Inverter: Shenzhen Encom Electric Technologies Co., LTDMr CdtNo ratings yet

- EMC Design Guidelines For Microcontroller Board Layout: Never Stop ThinkingDocument63 pagesEMC Design Guidelines For Microcontroller Board Layout: Never Stop ThinkingMr CdtNo ratings yet

- Interfacing Microchip'S Mcp3201 Analog-To-Digital Converter To The Picmicro MicrocontrollerDocument21 pagesInterfacing Microchip'S Mcp3201 Analog-To-Digital Converter To The Picmicro MicrocontrollerMaxi NozikovskyNo ratings yet

- Visvesvaraya Technological University: "Nano Robotics Embed Technologies"Document34 pagesVisvesvaraya Technological University: "Nano Robotics Embed Technologies"pradip pokharelNo ratings yet

- ADC Measurement DetailDocument9 pagesADC Measurement DetailMuhammad SiddiqueNo ratings yet

- Sensorbased Control of Three Phase Brushless DC Motor PDFDocument8 pagesSensorbased Control of Three Phase Brushless DC Motor PDFmike_helplineNo ratings yet

- TMPM374FWUG ProductIntroductionGuide en 20150331Document60 pagesTMPM374FWUG ProductIntroductionGuide en 20150331Elton Ribeiro100% (1)

- Fault Detection and Protection of Transformer by Using MicrocontrollerDocument8 pagesFault Detection and Protection of Transformer by Using MicrocontrollerVelu SamyNo ratings yet

- Introduction To ADC TestingDocument78 pagesIntroduction To ADC Testingsanjeevss_200-No ratings yet

- GSM Based 3 Phase Distribution Transformer Monitoring and ControlDocument8 pagesGSM Based 3 Phase Distribution Transformer Monitoring and ControlSharath AppuNo ratings yet

- Understanding Jitter and Phase NoiseDocument265 pagesUnderstanding Jitter and Phase Noiseelias ayoubNo ratings yet

- Direct RF ConvertionDocument9 pagesDirect RF ConvertionpabloNo ratings yet

- 09 Welding Machine TD 355Document1 page09 Welding Machine TD 355LucioNo ratings yet

- TSW1405 EvmDocument31 pagesTSW1405 Evmchandan1993No ratings yet

- TI Application Note For NIBP MeassureDocument20 pagesTI Application Note For NIBP MeassureHoang Anh TuanNo ratings yet

- Control de Campo Orientado MicrochipDocument28 pagesControl de Campo Orientado MicrochipguanitouNo ratings yet

- Solid Rocket Motor Static Fire Test Stand Optimization - Load CeDocument96 pagesSolid Rocket Motor Static Fire Test Stand Optimization - Load CeS DMNo ratings yet

- Crack The Code Teacher FolioDocument126 pagesCrack The Code Teacher Foliosnooze101No ratings yet

- Design and Implementation of Sigma Delta Modulators (ΣΔM) for Class D Audio Amplifiers Using Differential PairsDocument85 pagesDesign and Implementation of Sigma Delta Modulators (ΣΔM) for Class D Audio Amplifiers Using Differential PairsPreeti Bobde100% (1)

- RF Transceiver Architectures For W-CDMADocument10 pagesRF Transceiver Architectures For W-CDMABình PhạmNo ratings yet

- TI Maximizing SNRDocument58 pagesTI Maximizing SNRdhfsi7496No ratings yet

- Analog Isolation D AmpDocument7 pagesAnalog Isolation D AmpDirceu Rodrigues JrNo ratings yet

- Mod1 Exam - 108Document8 pagesMod1 Exam - 108Vivien VilladelreyNo ratings yet

- Smart-Sensor Report 1Document26 pagesSmart-Sensor Report 1AR CreationNo ratings yet

- P60 Agile P16x: Technical ManualDocument552 pagesP60 Agile P16x: Technical ManualGowtham ArumugamNo ratings yet

- ADC Noise Figure - An Often MisunderstoodDocument9 pagesADC Noise Figure - An Often MisunderstoodelvagojpNo ratings yet

- 8086 - Interfacing Analog To Digital Converters (ADC)Document22 pages8086 - Interfacing Analog To Digital Converters (ADC)PARIJAAT B MITRANo ratings yet

- MPC5643LDocument136 pagesMPC5643LNavya SreeNo ratings yet

- Sensors 18 03445 PDFDocument23 pagesSensors 18 03445 PDFadfasfdafssafNo ratings yet