Professional Documents

Culture Documents

0 ratings0% found this document useful (0 votes)

60 viewsP-Channel Logic Level Enhancement Mode MOSFET: Product Summary

P-Channel Logic Level Enhancement Mode MOSFET: Product Summary

Uploaded by

Xavier PortocarreroThe document summarizes a P-channel logic level enhancement mode MOSFET. Some key specifications include:

- Maximum drain-source voltage of -40V

- On-resistance as low as 40mΩ at a gate-source voltage of -10V

- Continuous drain current rating of -21A

- TO-252 surface mount package

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You might also like

- Newnes Electronics Engineers Pocket BookFrom EverandNewnes Electronics Engineers Pocket BookRating: 4.5 out of 5 stars4.5/5 (4)

- P1504edg UnikcDocument6 pagesP1504edg UnikcLuiz Gustavo VolpatoNo ratings yet

- UNIKCP3004BDDocument7 pagesUNIKCP3004BDgorgor1No ratings yet

- P-Channel Enhancement Mode MOSFET: Product SummaryDocument5 pagesP-Channel Enhancement Mode MOSFET: Product SummaryAhmad Syafii LeongNo ratings yet

- P06p03lcga UnikcDocument5 pagesP06p03lcga UnikcTaller 62No ratings yet

- Pz0703ek Unikc PDFDocument6 pagesPz0703ek Unikc PDFSergio GalliNo ratings yet

- P0603BDL: N-Channel Enhancement Mode MOSFETDocument5 pagesP0603BDL: N-Channel Enhancement Mode MOSFETLuisa GonzalezNo ratings yet

- Mosfet P0603BDLDocument5 pagesMosfet P0603BDLErmand WindNo ratings yet

- 1,7 2,5de20VGS 21 45mRDS 040VDS 20 70A 16 42W TO-252 P2504BDGDocument5 pages1,7 2,5de20VGS 21 45mRDS 040VDS 20 70A 16 42W TO-252 P2504BDGJoacir Marques MartinsNo ratings yet

- P-Channel Enhancement Mode MOSFET: Product SummaryDocument5 pagesP-Channel Enhancement Mode MOSFET: Product Summarymarlon corpuzNo ratings yet

- P0903BDL: N-Channel Enhancement Mode MOSFETDocument5 pagesP0903BDL: N-Channel Enhancement Mode MOSFETDiego AzevedoNo ratings yet

- P45N02LDG: N-Channel Enhancement Mode MOSFETDocument5 pagesP45N02LDG: N-Channel Enhancement Mode MOSFETserrano.flia.coNo ratings yet

- P2003EVG: P-Channel Logic Level Enhancement Mode MOSFETDocument5 pagesP2003EVG: P-Channel Logic Level Enhancement Mode MOSFETWyllyam BarbosaNo ratings yet

- P0603BDG N Chanel-MosfetDocument5 pagesP0603BDG N Chanel-MosfetathusNo ratings yet

- P1003EVG: P-Channel Enhancement Mode MOSFETDocument5 pagesP1003EVG: P-Channel Enhancement Mode MOSFETAnkit ShuklaNo ratings yet

- P 6010 DTFGDocument5 pagesP 6010 DTFGJohnsan DrummerNo ratings yet

- P0603BDDocument5 pagesP0603BDCarlosBayonaMontenegroNo ratings yet

- P0903BDG UnikcDocument5 pagesP0903BDG UnikcEdgar CatalanoNo ratings yet

- Nikos 903BDG DatasheetDocument5 pagesNikos 903BDG DatasheetTankard_grNo ratings yet

- P0903BDG: N-Channel Enhancement Mode MOSFETDocument5 pagesP0903BDG: N-Channel Enhancement Mode MOSFETJohnny Alberto Caicedo NiñoNo ratings yet

- Pv507ba UnikcDocument8 pagesPv507ba UnikcDoddy PrasetyaNo ratings yet

- TD422BL UnikcDocument5 pagesTD422BL UnikcandreasmonNo ratings yet

- P1703BDG UnikcDocument5 pagesP1703BDG UnikcDavid SuarezNo ratings yet

- Aoc 712s5 LCD Monitor Service ManualDocument5 pagesAoc 712s5 LCD Monitor Service Manualdomador1624No ratings yet

- N-Channel Enhancement Mode MOSFET: Product SummaryDocument4 pagesN-Channel Enhancement Mode MOSFET: Product SummaryGislaine Sousa CamposNo ratings yet

- Dual N-Channel Enhancement Mode MOSFET: Product SummaryDocument5 pagesDual N-Channel Enhancement Mode MOSFET: Product SummaryMelissa MelissaNo ratings yet

- Mosfet Doble Tipo N Pd1503yvs-UnikcDocument8 pagesMosfet Doble Tipo N Pd1503yvs-UnikcJuan PerezNo ratings yet

- DataSheet - PA410BDDocument8 pagesDataSheet - PA410BDastartngNo ratings yet

- P0903bea Laptop Primo de Miguel Perdomo PDFDocument6 pagesP0903bea Laptop Primo de Miguel Perdomo PDFLuis Luis GarciaNo ratings yet

- Pe610sa ReemplazoDocument8 pagesPe610sa ReemplazoDavid Enrique Rivero CahuichNo ratings yet

- P0903BEA: N-Channel Enhancement Mode MOSFETDocument7 pagesP0903BEA: N-Channel Enhancement Mode MOSFETAndre PinhoNo ratings yet

- TD 304 BHDocument5 pagesTD 304 BHGrady SharpeNo ratings yet

- P2003BDG: N-Channel Logic Level Enhancement Mode MOSFETDocument5 pagesP2003BDG: N-Channel Logic Level Enhancement Mode MOSFETRexer AnthonyNo ratings yet

- P2003BDG: N-Channel Logic Level Enhancement Mode MOSFETDocument5 pagesP2003BDG: N-Channel Logic Level Enhancement Mode MOSFETRexer AnthonyNo ratings yet

- P0803BDG Unikc PDFDocument5 pagesP0803BDG Unikc PDFSantiago DiosdadoNo ratings yet

- P0803BDG UnikcDocument5 pagesP0803BDG UnikcSantiago DiosdadoNo ratings yet

- N-Channel Enhancement Mode MOSFET: Product SummaryDocument5 pagesN-Channel Enhancement Mode MOSFET: Product SummaryMotorola E5 PlusNo ratings yet

- A06N03N Excelliance MOSDocument6 pagesA06N03N Excelliance MOSLeonardo FerreiraNo ratings yet

- 1Document5 pages1bahmanNo ratings yet

- Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument5 pagesNiko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorJulio Rafael GamboaNo ratings yet

- P0903BDA: N-Channel Enhancement Mode MOSFETDocument5 pagesP0903BDA: N-Channel Enhancement Mode MOSFETMax Assistência TécnicaNo ratings yet

- P5506BDG UnikcDocument5 pagesP5506BDG UnikcYessenia PerezNo ratings yet

- NIKO-Semicon-PA102FMG C133607Document5 pagesNIKO-Semicon-PA102FMG C133607Taller 62No ratings yet

- P75N02LDG: N-Channel Enhancement Mode MOSFETDocument5 pagesP75N02LDG: N-Channel Enhancement Mode MOSFETAriel Rodrigo MuñozNo ratings yet

- Pa102fdg Mos PDocument5 pagesPa102fdg Mos PValentinNo ratings yet

- B20P03 To-252Document6 pagesB20P03 To-252freddyNo ratings yet

- Emb 03 N 03 HRDocument6 pagesEmb 03 N 03 HRChiapin LeeNo ratings yet

- P8008HVA: Dual N-Channel Enhancement Mode MOSFETDocument5 pagesP8008HVA: Dual N-Channel Enhancement Mode MOSFETEsther AsturiasNo ratings yet

- P1260ATF: N-Channel Enhancement Mode MOSFETDocument5 pagesP1260ATF: N-Channel Enhancement Mode MOSFETGioVoTamNo ratings yet

- EMB07N03HRDocument6 pagesEMB07N03HRChiapin LeeNo ratings yet

- EMB20P03VDocument5 pagesEMB20P03Vk10sergaNo ratings yet

- Pa 110 BdaDocument8 pagesPa 110 BdaIvan Arturo Barrientos PreciadoNo ratings yet

- EMB12P03VDocument5 pagesEMB12P03VBình NguyễnNo ratings yet

- P0903BK UnikcDocument5 pagesP0903BK UnikcAmilcar SilvaNo ratings yet

- Data Sheet PA102FDGDocument5 pagesData Sheet PA102FDGSlagalicaSlagalicaNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsRating: 5 out of 5 stars5/5 (1)

- Modulation - WikipediaDocument8 pagesModulation - WikipediaMubashir AliNo ratings yet

- R9DS IntroductionDocument4 pagesR9DS IntroductionMauricio Hernandez SolanoNo ratings yet

- LogDocument9 pagesLogStojan ManojlovicNo ratings yet

- Aspire 8951 Service Guide 20110330Document260 pagesAspire 8951 Service Guide 20110330BDMasterNo ratings yet

- Lge 42LV4400 PDFDocument137 pagesLge 42LV4400 PDFtran nhat namNo ratings yet

- Bist For Xilinx 4000 and Spartan Series Fpgas: A Case Study: Charles E. Stroud Keshia N. Leach, and Thomas A. SlaughterDocument10 pagesBist For Xilinx 4000 and Spartan Series Fpgas: A Case Study: Charles E. Stroud Keshia N. Leach, and Thomas A. Slaughtersumit.raj.iiit5613No ratings yet

- Trigem Micro-Atx Motherboard Hardware Document: CognacDocument16 pagesTrigem Micro-Atx Motherboard Hardware Document: CognacSteve MartinNo ratings yet

- Types of Storage DeviceDocument26 pagesTypes of Storage DeviceHarry ValeteNo ratings yet

- Audiovox Avp7280 - 7200Document52 pagesAudiovox Avp7280 - 7200Justin WilliamsNo ratings yet

- MouseDocument20 pagesMouseFroylan01No ratings yet

- Solaredge Grid Tie InverterDocument2 pagesSolaredge Grid Tie InverterMayur HiwarkarNo ratings yet

- Led Display PDFDocument12 pagesLed Display PDFIrwin DarmansyahNo ratings yet

- E81am33 - R0 - MD Supply Sections With Fieldbus ControlDocument38 pagesE81am33 - R0 - MD Supply Sections With Fieldbus ControlFarshad MahmoudiNo ratings yet

- EC Gate 2016 SET 1 PDFDocument16 pagesEC Gate 2016 SET 1 PDFGanesh KumarNo ratings yet

- Electrical Part ListDocument10 pagesElectrical Part ListTony SalvianoNo ratings yet

- PB Ir3555 PDFDocument1 pagePB Ir3555 PDFTieMuZhenNo ratings yet

- Datasheet CS141 enDocument9 pagesDatasheet CS141 enPeter PeterNo ratings yet

- Experiment#7 To Study The Operation of Direct Coupled Two Stage AmplifierDocument3 pagesExperiment#7 To Study The Operation of Direct Coupled Two Stage AmplifierZbNo ratings yet

- EA 400 EA 400: EA 400 Series Hydrographic Single Beam Echo Sounders EA 400 Series Hydrographic Single Beam Echo SoundersDocument1 pageEA 400 EA 400: EA 400 Series Hydrographic Single Beam Echo Sounders EA 400 Series Hydrographic Single Beam Echo SoundersrcmmazNo ratings yet

- Datasheet LTC1286 FsDocument25 pagesDatasheet LTC1286 FsRamonNo ratings yet

- Silicon NPN Triple Diffused Planar Transistor: (High Voltage and High Speed Switchihg Transistor)Document1 pageSilicon NPN Triple Diffused Planar Transistor: (High Voltage and High Speed Switchihg Transistor)Bernardo RatiaNo ratings yet

- Sony Mdsje440+640 Manual PDFDocument60 pagesSony Mdsje440+640 Manual PDFhkaruvathilNo ratings yet

- Seminar On HDL's and HVL'sDocument25 pagesSeminar On HDL's and HVL'sharishkashaNo ratings yet

- PLC Law 2016 EditionDocument10 pagesPLC Law 2016 Editionmelin2000No ratings yet

- Antenna Specifications: Electrical PropertiesDocument2 pagesAntenna Specifications: Electrical Propertiesmapat99No ratings yet

- Instalation ManualDocument9 pagesInstalation Manualjoseluisrosglz1678No ratings yet

- SPDT Relay Switch Circuit Using TriacDocument4 pagesSPDT Relay Switch Circuit Using TriacΔημητριος ΣταθηςNo ratings yet

- 27011054-Wall Mount Antenna Datasheet (HADA-07091827-N-586-O) Datasheet PDFDocument1 page27011054-Wall Mount Antenna Datasheet (HADA-07091827-N-586-O) Datasheet PDFСергей МирошниченкоNo ratings yet

- UPF & Special Cells Used For Power Planning - VLSI - Physical Design For FreshersDocument4 pagesUPF & Special Cells Used For Power Planning - VLSI - Physical Design For FreshersRA NDYNo ratings yet

- Easy To Build WIFI 2.4GHz Yagi Antenna PDFDocument12 pagesEasy To Build WIFI 2.4GHz Yagi Antenna PDFPeter FrankNo ratings yet

P-Channel Logic Level Enhancement Mode MOSFET: Product Summary

P-Channel Logic Level Enhancement Mode MOSFET: Product Summary

Uploaded by

Xavier Portocarrero0 ratings0% found this document useful (0 votes)

60 views5 pagesThe document summarizes a P-channel logic level enhancement mode MOSFET. Some key specifications include:

- Maximum drain-source voltage of -40V

- On-resistance as low as 40mΩ at a gate-source voltage of -10V

- Continuous drain current rating of -21A

- TO-252 surface mount package

Original Description:

Fet

Original Title

p4004ed

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThe document summarizes a P-channel logic level enhancement mode MOSFET. Some key specifications include:

- Maximum drain-source voltage of -40V

- On-resistance as low as 40mΩ at a gate-source voltage of -10V

- Continuous drain current rating of -21A

- TO-252 surface mount package

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

60 views5 pagesP-Channel Logic Level Enhancement Mode MOSFET: Product Summary

P-Channel Logic Level Enhancement Mode MOSFET: Product Summary

Uploaded by

Xavier PortocarreroThe document summarizes a P-channel logic level enhancement mode MOSFET. Some key specifications include:

- Maximum drain-source voltage of -40V

- On-resistance as low as 40mΩ at a gate-source voltage of -10V

- Continuous drain current rating of -21A

- TO-252 surface mount package

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 5

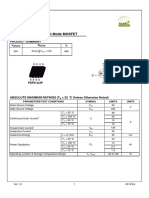

P4004ED

P-Channel Logic Level Enhancement Mode MOSFET

PRODUCT SUMMARY

V(BR)DSS RDS(ON) ID

-40V 40mΩ @VGS = -10V -21A

TO-252

ABSOLUTE MAXIMUM RATINGS (TA = 25 °C Unless Otherwise Noted)

PARAMETERS/TEST CONDITIONS SYMBOL LIMITS UNITS

Drain-Source Voltage VDS -40 V

Gate-Source Voltage VGS ±20 V

TC= 25 °C -21

Continuous Drain Current ID

TC= 70 °C -17

1

A

Pulsed Drain Current IDM -70

Avalanche Current IAS -27

2 EAS

Avalanche Energy L = 0.1mH 36 mJ

TC= 25 °C 30

Power Dissipation PD W

TC= 70°C 20

Junction & Storage Temperature Range Tj, Tstg -55 to 150 °C

THERMAL RESISTANCE RATINGS

THERMAL RESISTANCE SYMBOL TYPICAL MAXIMUM UNITS

Junction-to-Case RqJC 4.1

°C / W

Junction-to-Ambient RqJA 40

1

Pulse width limited by maximum junction temperature.

2

VDD = -20V . Starting TJ = 25°C.

REV 1.0 1 2014/5/13

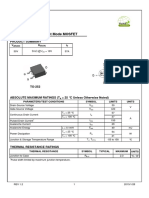

P4004ED

P-Channel Logic Level Enhancement Mode MOSFET

ELECTRICAL CHARACTERISTICS (TJ = 25 °C, Unless Otherwise Noted)

LIMITS

PARAMETER SYMBOL TEST CONDITIONS UNITS

MIN TYP MAX

STATIC

Drain-Source Breakdown V(BR)DSS VGS = 0V, ID = -250mA -40

Voltage V

Gate Threshold Voltage VGS(th) VDS = VGS, ID = -250mA -2.0 -2.5 -3

Gate-Body Leakage IGSS VDS = 0V, VGS = ±20V ±250 nA

VDS =-32V, VGS = 0V 1

Zero Gate Voltage Drain Current IDSS mA

VDS =-30V, VGS = 0V, TJ = 125°C 10

On-State Drain Current1 ID(ON) VDS = -5V, VGS = -10V -70 A

VGS =-5V, ID =-8A 65 73

Drain-Source On-State

RDS(ON) VGS = -7V, ID = -8A 35 50 mΩ

Resistance1

VGS =-10V, ID =-10A 30 40

1 gfs VDS = -10V, ID = -10A

Forward Transconductance 20 S

DYNAMIC

Input Capacitance Ciss 1090

Output Capacitance Coss VGS = 0V, VDS = -20V, f = 1MHz 175 pF

Reverse Transfer Capacitance Crss 91

Qg(VGS = -10V) 17

Total Gate Charge2

Qg(VGS =-4.5V) VDS =0.5V(BR)DSS, 8.5

nC

Gate-Source Charge 2 Qgs ID = -18A 5.5

Gate-Drain Charge2 Qgd 3

Gate Resistance Rg VGS = 0V, VDS = 0V, f = 1MHz 4.95 Ω

2 td(on)

Turn-On Delay Time 6

Rise Time 2 tr @

VDS =-20V ,RL = 2Ω,ID -10A, 16

2 VGS=-10V,RGS=6Ω nS

Turn-Off Delay Time td(off) 26

Fall Time2 tf 10

SOURCE-DRAIN DIODE RATINGS AND CHARACTERISTICS (TJ = 25 °C)

Continuous Current IS -21 A

1 VSD IF = -1A, VGS = 0V

Forward Voltage -1 V

Reverse Recovery Time trr 15.5 nS

IF = -10A, dlF/dt = 100A / μS

Reverse Recovery Charge Qrr 7.9 nC

1

Pulse test : Pulse Width 300 msec, Duty Cycle 2%.

2

Independent of operating temperature.

REV 1.0 2 2014/5/13

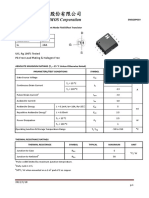

P4004ED

P-Channel Logic Level Enhancement Mode MOSFET

REV 1.0 3 2014/5/13

P4004ED

P-Channel Logic Level Enhancement Mode MOSFET

REV 1.0 4 2014/5/13

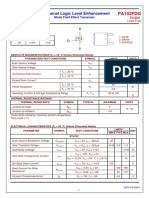

P4004ED

P-Channel Logic Level Enhancement Mode MOSFET

*因为各家封装模具不同而外观略有所差异,不影响电性及Layout。

REV 1.0 5 2014/5/13

You might also like

- Newnes Electronics Engineers Pocket BookFrom EverandNewnes Electronics Engineers Pocket BookRating: 4.5 out of 5 stars4.5/5 (4)

- P1504edg UnikcDocument6 pagesP1504edg UnikcLuiz Gustavo VolpatoNo ratings yet

- UNIKCP3004BDDocument7 pagesUNIKCP3004BDgorgor1No ratings yet

- P-Channel Enhancement Mode MOSFET: Product SummaryDocument5 pagesP-Channel Enhancement Mode MOSFET: Product SummaryAhmad Syafii LeongNo ratings yet

- P06p03lcga UnikcDocument5 pagesP06p03lcga UnikcTaller 62No ratings yet

- Pz0703ek Unikc PDFDocument6 pagesPz0703ek Unikc PDFSergio GalliNo ratings yet

- P0603BDL: N-Channel Enhancement Mode MOSFETDocument5 pagesP0603BDL: N-Channel Enhancement Mode MOSFETLuisa GonzalezNo ratings yet

- Mosfet P0603BDLDocument5 pagesMosfet P0603BDLErmand WindNo ratings yet

- 1,7 2,5de20VGS 21 45mRDS 040VDS 20 70A 16 42W TO-252 P2504BDGDocument5 pages1,7 2,5de20VGS 21 45mRDS 040VDS 20 70A 16 42W TO-252 P2504BDGJoacir Marques MartinsNo ratings yet

- P-Channel Enhancement Mode MOSFET: Product SummaryDocument5 pagesP-Channel Enhancement Mode MOSFET: Product Summarymarlon corpuzNo ratings yet

- P0903BDL: N-Channel Enhancement Mode MOSFETDocument5 pagesP0903BDL: N-Channel Enhancement Mode MOSFETDiego AzevedoNo ratings yet

- P45N02LDG: N-Channel Enhancement Mode MOSFETDocument5 pagesP45N02LDG: N-Channel Enhancement Mode MOSFETserrano.flia.coNo ratings yet

- P2003EVG: P-Channel Logic Level Enhancement Mode MOSFETDocument5 pagesP2003EVG: P-Channel Logic Level Enhancement Mode MOSFETWyllyam BarbosaNo ratings yet

- P0603BDG N Chanel-MosfetDocument5 pagesP0603BDG N Chanel-MosfetathusNo ratings yet

- P1003EVG: P-Channel Enhancement Mode MOSFETDocument5 pagesP1003EVG: P-Channel Enhancement Mode MOSFETAnkit ShuklaNo ratings yet

- P 6010 DTFGDocument5 pagesP 6010 DTFGJohnsan DrummerNo ratings yet

- P0603BDDocument5 pagesP0603BDCarlosBayonaMontenegroNo ratings yet

- P0903BDG UnikcDocument5 pagesP0903BDG UnikcEdgar CatalanoNo ratings yet

- Nikos 903BDG DatasheetDocument5 pagesNikos 903BDG DatasheetTankard_grNo ratings yet

- P0903BDG: N-Channel Enhancement Mode MOSFETDocument5 pagesP0903BDG: N-Channel Enhancement Mode MOSFETJohnny Alberto Caicedo NiñoNo ratings yet

- Pv507ba UnikcDocument8 pagesPv507ba UnikcDoddy PrasetyaNo ratings yet

- TD422BL UnikcDocument5 pagesTD422BL UnikcandreasmonNo ratings yet

- P1703BDG UnikcDocument5 pagesP1703BDG UnikcDavid SuarezNo ratings yet

- Aoc 712s5 LCD Monitor Service ManualDocument5 pagesAoc 712s5 LCD Monitor Service Manualdomador1624No ratings yet

- N-Channel Enhancement Mode MOSFET: Product SummaryDocument4 pagesN-Channel Enhancement Mode MOSFET: Product SummaryGislaine Sousa CamposNo ratings yet

- Dual N-Channel Enhancement Mode MOSFET: Product SummaryDocument5 pagesDual N-Channel Enhancement Mode MOSFET: Product SummaryMelissa MelissaNo ratings yet

- Mosfet Doble Tipo N Pd1503yvs-UnikcDocument8 pagesMosfet Doble Tipo N Pd1503yvs-UnikcJuan PerezNo ratings yet

- DataSheet - PA410BDDocument8 pagesDataSheet - PA410BDastartngNo ratings yet

- P0903bea Laptop Primo de Miguel Perdomo PDFDocument6 pagesP0903bea Laptop Primo de Miguel Perdomo PDFLuis Luis GarciaNo ratings yet

- Pe610sa ReemplazoDocument8 pagesPe610sa ReemplazoDavid Enrique Rivero CahuichNo ratings yet

- P0903BEA: N-Channel Enhancement Mode MOSFETDocument7 pagesP0903BEA: N-Channel Enhancement Mode MOSFETAndre PinhoNo ratings yet

- TD 304 BHDocument5 pagesTD 304 BHGrady SharpeNo ratings yet

- P2003BDG: N-Channel Logic Level Enhancement Mode MOSFETDocument5 pagesP2003BDG: N-Channel Logic Level Enhancement Mode MOSFETRexer AnthonyNo ratings yet

- P2003BDG: N-Channel Logic Level Enhancement Mode MOSFETDocument5 pagesP2003BDG: N-Channel Logic Level Enhancement Mode MOSFETRexer AnthonyNo ratings yet

- P0803BDG Unikc PDFDocument5 pagesP0803BDG Unikc PDFSantiago DiosdadoNo ratings yet

- P0803BDG UnikcDocument5 pagesP0803BDG UnikcSantiago DiosdadoNo ratings yet

- N-Channel Enhancement Mode MOSFET: Product SummaryDocument5 pagesN-Channel Enhancement Mode MOSFET: Product SummaryMotorola E5 PlusNo ratings yet

- A06N03N Excelliance MOSDocument6 pagesA06N03N Excelliance MOSLeonardo FerreiraNo ratings yet

- 1Document5 pages1bahmanNo ratings yet

- Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument5 pagesNiko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorJulio Rafael GamboaNo ratings yet

- P0903BDA: N-Channel Enhancement Mode MOSFETDocument5 pagesP0903BDA: N-Channel Enhancement Mode MOSFETMax Assistência TécnicaNo ratings yet

- P5506BDG UnikcDocument5 pagesP5506BDG UnikcYessenia PerezNo ratings yet

- NIKO-Semicon-PA102FMG C133607Document5 pagesNIKO-Semicon-PA102FMG C133607Taller 62No ratings yet

- P75N02LDG: N-Channel Enhancement Mode MOSFETDocument5 pagesP75N02LDG: N-Channel Enhancement Mode MOSFETAriel Rodrigo MuñozNo ratings yet

- Pa102fdg Mos PDocument5 pagesPa102fdg Mos PValentinNo ratings yet

- B20P03 To-252Document6 pagesB20P03 To-252freddyNo ratings yet

- Emb 03 N 03 HRDocument6 pagesEmb 03 N 03 HRChiapin LeeNo ratings yet

- P8008HVA: Dual N-Channel Enhancement Mode MOSFETDocument5 pagesP8008HVA: Dual N-Channel Enhancement Mode MOSFETEsther AsturiasNo ratings yet

- P1260ATF: N-Channel Enhancement Mode MOSFETDocument5 pagesP1260ATF: N-Channel Enhancement Mode MOSFETGioVoTamNo ratings yet

- EMB07N03HRDocument6 pagesEMB07N03HRChiapin LeeNo ratings yet

- EMB20P03VDocument5 pagesEMB20P03Vk10sergaNo ratings yet

- Pa 110 BdaDocument8 pagesPa 110 BdaIvan Arturo Barrientos PreciadoNo ratings yet

- EMB12P03VDocument5 pagesEMB12P03VBình NguyễnNo ratings yet

- P0903BK UnikcDocument5 pagesP0903BK UnikcAmilcar SilvaNo ratings yet

- Data Sheet PA102FDGDocument5 pagesData Sheet PA102FDGSlagalicaSlagalicaNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsRating: 5 out of 5 stars5/5 (1)

- Modulation - WikipediaDocument8 pagesModulation - WikipediaMubashir AliNo ratings yet

- R9DS IntroductionDocument4 pagesR9DS IntroductionMauricio Hernandez SolanoNo ratings yet

- LogDocument9 pagesLogStojan ManojlovicNo ratings yet

- Aspire 8951 Service Guide 20110330Document260 pagesAspire 8951 Service Guide 20110330BDMasterNo ratings yet

- Lge 42LV4400 PDFDocument137 pagesLge 42LV4400 PDFtran nhat namNo ratings yet

- Bist For Xilinx 4000 and Spartan Series Fpgas: A Case Study: Charles E. Stroud Keshia N. Leach, and Thomas A. SlaughterDocument10 pagesBist For Xilinx 4000 and Spartan Series Fpgas: A Case Study: Charles E. Stroud Keshia N. Leach, and Thomas A. Slaughtersumit.raj.iiit5613No ratings yet

- Trigem Micro-Atx Motherboard Hardware Document: CognacDocument16 pagesTrigem Micro-Atx Motherboard Hardware Document: CognacSteve MartinNo ratings yet

- Types of Storage DeviceDocument26 pagesTypes of Storage DeviceHarry ValeteNo ratings yet

- Audiovox Avp7280 - 7200Document52 pagesAudiovox Avp7280 - 7200Justin WilliamsNo ratings yet

- MouseDocument20 pagesMouseFroylan01No ratings yet

- Solaredge Grid Tie InverterDocument2 pagesSolaredge Grid Tie InverterMayur HiwarkarNo ratings yet

- Led Display PDFDocument12 pagesLed Display PDFIrwin DarmansyahNo ratings yet

- E81am33 - R0 - MD Supply Sections With Fieldbus ControlDocument38 pagesE81am33 - R0 - MD Supply Sections With Fieldbus ControlFarshad MahmoudiNo ratings yet

- EC Gate 2016 SET 1 PDFDocument16 pagesEC Gate 2016 SET 1 PDFGanesh KumarNo ratings yet

- Electrical Part ListDocument10 pagesElectrical Part ListTony SalvianoNo ratings yet

- PB Ir3555 PDFDocument1 pagePB Ir3555 PDFTieMuZhenNo ratings yet

- Datasheet CS141 enDocument9 pagesDatasheet CS141 enPeter PeterNo ratings yet

- Experiment#7 To Study The Operation of Direct Coupled Two Stage AmplifierDocument3 pagesExperiment#7 To Study The Operation of Direct Coupled Two Stage AmplifierZbNo ratings yet

- EA 400 EA 400: EA 400 Series Hydrographic Single Beam Echo Sounders EA 400 Series Hydrographic Single Beam Echo SoundersDocument1 pageEA 400 EA 400: EA 400 Series Hydrographic Single Beam Echo Sounders EA 400 Series Hydrographic Single Beam Echo SoundersrcmmazNo ratings yet

- Datasheet LTC1286 FsDocument25 pagesDatasheet LTC1286 FsRamonNo ratings yet

- Silicon NPN Triple Diffused Planar Transistor: (High Voltage and High Speed Switchihg Transistor)Document1 pageSilicon NPN Triple Diffused Planar Transistor: (High Voltage and High Speed Switchihg Transistor)Bernardo RatiaNo ratings yet

- Sony Mdsje440+640 Manual PDFDocument60 pagesSony Mdsje440+640 Manual PDFhkaruvathilNo ratings yet

- Seminar On HDL's and HVL'sDocument25 pagesSeminar On HDL's and HVL'sharishkashaNo ratings yet

- PLC Law 2016 EditionDocument10 pagesPLC Law 2016 Editionmelin2000No ratings yet

- Antenna Specifications: Electrical PropertiesDocument2 pagesAntenna Specifications: Electrical Propertiesmapat99No ratings yet

- Instalation ManualDocument9 pagesInstalation Manualjoseluisrosglz1678No ratings yet

- SPDT Relay Switch Circuit Using TriacDocument4 pagesSPDT Relay Switch Circuit Using TriacΔημητριος ΣταθηςNo ratings yet

- 27011054-Wall Mount Antenna Datasheet (HADA-07091827-N-586-O) Datasheet PDFDocument1 page27011054-Wall Mount Antenna Datasheet (HADA-07091827-N-586-O) Datasheet PDFСергей МирошниченкоNo ratings yet

- UPF & Special Cells Used For Power Planning - VLSI - Physical Design For FreshersDocument4 pagesUPF & Special Cells Used For Power Planning - VLSI - Physical Design For FreshersRA NDYNo ratings yet

- Easy To Build WIFI 2.4GHz Yagi Antenna PDFDocument12 pagesEasy To Build WIFI 2.4GHz Yagi Antenna PDFPeter FrankNo ratings yet