Professional Documents

Culture Documents

Dual Monostable Multivibrators With Schmitt-Trigger Inputs SN54/74LS221

Dual Monostable Multivibrators With Schmitt-Trigger Inputs SN54/74LS221

Uploaded by

parsa mahvisOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Dual Monostable Multivibrators With Schmitt-Trigger Inputs SN54/74LS221

Dual Monostable Multivibrators With Schmitt-Trigger Inputs SN54/74LS221

Uploaded by

parsa mahvisCopyright:

Available Formats

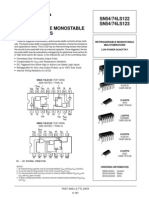

SN54/74LS221

DUAL MONOSTABLE

MULTIVIBRATORS

WITH SCHMITT-TRIGGER INPUTS

Each multivibrator of the LS221 features a negative-transition-triggered DUAL MONOSTABLE

input and a positive-transition-triggered input either of which can be used as MULTIVIBRATORS

an inhibit input. WITH SCHMITT-TRIGGER INPUTS

Pulse triggering occurs at a voltage level and is not related to the transition

time of the input pulse. Schmitt-trigger input circuitry for B input allows LOW POWER SCHOTTKY

jitter-free triggering for inputs as slow as 1 volt / second, providing the circuit

with excellent noise immunity. A high immunity to VCC noise is also provided

by internal latching circuitry.

Once triggered, the outputs are independent of further transitions of the

inputs and are a function of the timing components. The output pulses can be J SUFFIX

terminated by the overriding clear. Input pulse width may be of any duration CERAMIC

relative to the output pulse width. Output pulse width may be varied from 35 CASE 620-09

16

nanoseconds to a maximum of 70 s by choosing appropriate timing 1

components. With Rext = 2.0 kΩ and Cext = 0, a typical output pulse of 30

nanoseconds is achieved. Output rise and fall times are independent of pulse

length.

Pulse width stability is achieved through internal compensation and is

N SUFFIX

virtually independent of VCC and temperature. In most applications, pulse PLASTIC

stability will only be limited by the accuracy of external timing components. CASE 648-08

16

Jitter-free operation is maintained over the full temperature and VCC ranges

for greater than six decades of timing capacitance (10 pF to 10 µF), and 1

greater than one decade of timing resistance (2.0 to 70 kΩ for the

SN54LS221, and 2.0 to 100 kΩ for the SN74LS221). Pulse width is defined

by the relationship: tw(out) = CextRext ln 2.0 ≈ 0.7 Cext Rext; where tW is in ns D SUFFIX

SOIC

if Cext is in pF and Rext is in kΩ . If pulse cutoff is not critical, capacitance up 16

CASE 751B-03

to 1000 µF and resistance as low as 1.4 kΩ may be used. The range of 1

jitter-free pulse widths is extended if VCC is 5.0 V and 25°C temperature.

• SN54LS221 and SN74LS221 is a Dual Highly Stable One-Shot ORDERING INFORMATION

• Overriding Clear Terminates Output Pulse

SN54LSXXXJ Ceramic

• Pin Out is Identical to SN54 / 74LS123

SN74LSXXXN Plastic

SN74LSXXXD SOIC

FUNCTION TABLE

(TOP VIEW)

(EACH MONOSTABLE)

1 Rext/ 1 2

INPUTS OUTPUTS

VCC Cext Cext 1Q 2Q CLR 2B 2A

CLEAR A B Q Q

16 15 14 13 12 11 10 9

L X X L H

Q VCC X H X L H

Q X X L L H

CLR Rext H L °

CLR

Q + H ± H

Q

*° L H

Cext R/C *See operational notes — Pulse Trigger Modes

1 2 3 4 5 6 7 8

1A 1B 1 1Q 2Q 2 2 Rext/ GND TYPICAL MAXIMUM

CLR Cext Cext TYPE POWER OUTPUT PULSE

positive logic: Low input to clear resets Q low and DISSIPATION LENGTH

positive logic: Q high regardless of dc levels at A SN54LS221 23 mW 49 s

positive logic: or B inputs. SN74LS221 23 mW 70 s

FAST AND LS TTL DATA

5-1

SN54/74LS221

OPERATIONAL NOTES

Once in the pulse trigger mode, the output pulse width is Clear Mode: If the clear input is held low, irregardless of

determined by tW = RextCextIn2, as long as Rext and Cext are the previous output state and other input

within their minimum and maximum valves and the duty cycle states, the Q output is low.

is less than 50%. This pulse width is essentially independent

of VCC and temperature variations. Output pulse widths varies Inhibit Mode: If either the A input is high or the B input is

typically no more than ±0.5% from device to device. low, once the Q output goes low, it cannot be

retriggered by other inputs.

If the duty cycle, defined as being 100 • tW where T is the

input T Pulse Trigger

period of the input pulse, rises above 50%, the output pulse

Mode: A transition of the A or B inputs as indicated

width will become shorter. If the duty cycle varies between

in the functional truth table will trigger the Q

low and high valves, this causes the output pulse width to

output to go high for a duration determined

vary in length, or jitter. To reduce jitter to a minimum, Rext

by the tW equation described above; Q will

should be as large as possible. (Jitter is independent of Cext).

go low for a corresponding length of time.

With Rext = 100K, jitter is not appreciable until the duty cycle

approaches 90%. The Clear input may also be used to trigger

Although the LS221 is pin-for-pin compatible with the an output pulse, but special logic precondi-

LS123, it should be remembered that they are not functionally tioning on the A or B inputs must be done as

identical. The LS123 is retriggerable so that the output is follows:

dependent upon the input transitions once it is high. This is not

Following any output triggering action

the case for the LS221. Also note that it is recommended to

using the A or B inputs, the A input must

externally ground the LS123 Cext pin. However, this cannot be

be set high OR the B input must be set

done on the LS221.

low to allow Clear to be used as a trigger.

The SN54LS/74LS221 is a dual, monolithic, non-retrigger-

Inputs should then be set up per the truth

able, high-stability one shot. The output pulse width, tW can be

table (without triggering the output) to

varied over 9 decades of timing by proper selection of the

allow Clear to be used a trigger for the

external timing components, Rext and Cext.

output pulse.

Pulse triggering occurs at a voltage level and is, therefore,

independent of the input slew rate. Although all three inputs If the Clear pin is routinely being used to

have this Schmitt-trigger effect, only the B input should be trigger the output pulse, the A or B inputs

used for very long transition triggers (≥1.0 µV/s). High must be toggled as described above

immunity to VCC noise (typically 1.5 V) is achieved by internal before and between each Clear trigger

latching circuitry. However, standard VCC bypassing is event.

strongly recommended.

The LS221 has four basic modes of operation. Once triggered, as long as the output

remains high, all input transitions (except

overriding Clear) are ignored.

Overriding

Clear Mode: If the Q output is high, it may be forced low

by bringing the clear input low.

FAST AND LS TTL DATA

5-2

SN54/74LS221

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

VCC Supply Voltage 54 4.5 5.0 5.5 V

74 4.75 5.0 5.25

TA Operating Ambient Temperature Range 54 – 55 25 125 °C

74 0 25 70

IOH Output Current — High 54, 74 – 0.4 mA

IOL Output Current — Low 54 4.0 mA

74 8.0

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Limits

S b l

Symbol P

Parameter Min Typ Max U i

Unit T

Test C

Conditions

di i

Positive-Going Threshold

VT+ 1.0 2.0 V VCC = MIN

Voltage at C Input

Negative-Going

g g Threshold 54 0.7 0.8 V

VT

T– VCC = MIN

Voltage at C Input 74 0.7 0.8 V

Positive-Going Threshold

VT+ 1.0 2.0 V VCC = MIN

Voltage at B Input

Negative-Going

g g Threshold 54 0.7 0.9 V

VT

T– VCC = MIN

Voltage at B Input 74 0.8 0.9 V

Guaranteed Input HIGH Voltage for

VIH Input HIGH Voltage 2.0 V

A Input

54 0.7 Guaranteed Input

p LOW Voltage

g for

VIL Input LOW Voltage V

74 0.8 A Input

VIK Input Clamp Voltage – 1.5 V VCC = MIN, IIN = – 18 mA

54 2.5 3.4 V

VOH Output HIGH Voltage VCC = MIN

MIN, IOH = MAX

74 2.7 3.4 V

54 0.25 0.4 V IOL = 4.0 mA

VOL Output LOW Voltage VCC = MIN

74 0.35 0.5 V IOL = 8.0 mA

20 µA VCC = MAX, VIN = 2.7 V

IIH Input HIGH Current

0.1 mA VCC = MAX, VIN = 7.0 V

Input LOW Current

Input A – 0.4

IIL mA VCC = MAX, VIN = 0.4 V

Input B – 0.8

Clear – 0.8

IOS Short Circuit Current (Note 1) – 20 – 100 mA VCC = MAX

Power Supply Current

ICC Quiescent 4.7 11 mA VCC = MAX

Triggered 19 27

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

FAST AND LS TTL DATA

5-3

SN54/74LS221

AC CHARACTERISTICS (VCC = 5.0 V, TA = 25°C)

Limits

From To

S b l

Symbol (Input) (Output) Min Typ Max U i

Unit T

Test C

Conditions

di i

A Q 45 70

tPLH ns

B Q 35 55

A Q 50 80

tPHL ns Cext = 80 pF,

pF 20Ω

F Rext = 2.0

B Q 40 65

tPHL Clear Q 35 55 ns CL = 15 p

pF,

F,

tPLH Clear Q 44 65 ns See Figure 1

70 120 150 Cext = 80 pF, Rext = 2.0 Ω

20 47 70 ns Cext = 0, Rext = 2.0 kΩ

tW(out) A or B Q or Q

600 670 750 Cext = 100 pF, Rext = 10 kΩ

6.0 6.9 7.5 ms Cext = 1.0 µF, Rext = 10 kΩ

AC SETUP REQUIREMENTS (VCC = 5.0 V, TA = 25°C)

Limits

S b l

Symbol P

Parameter Min Typ Max U i

Unit

Rate of Rise or Fall of Input Pulse

d /d

dv/dt Schmitt, B 1.0 V/s

Logic Input, A 1.0 V/µs

Input Pulse Width

tW A or B, tW(in) 40 ns

Clear, tW (clear) 40

ts Clear-Inactive-State Setup Time 15 ns

54 1.4 70

Rext External Timing Resistance kΩ

74 1.4 100

Cext External Timing Capacitance 0 1000 µF

Output Duty Cycle

RT = 2.0 kΩ 50 %

RT = MAX Rext 90

FAST AND LS TTL DATA

5-4

SN54/74LS221

AC WAVEFORMS

tW(in)

B INPUT 3V

1.3 V

0V

≥60 ns

3V

CLEAR

0V

tPLH tPHL

VOH

Q OUTPUT

VOL

tPHL tPLH

VOH

Q OUTPUT

VOL

A INPUT IS LOW.

TRIGGER FROM B, THEN CLEAR — CONDITION 1

3V

B INPUT

0V

≥ 60 ns

3V

1.3 V

CLEAR 0V

VOH

Q OUTPUT

VOL

A INPUT IS LOW.

TRIGGER FROM B, THEN CLEAR — CONDITION 2

3V

B INPUT

ts 0V

≥ 50 ns ≥0

3V

CLEAR

0V

TRIGGERED

VOH

Q OUTPUT

VOL

NOT TRIGGERED tW(out)

A INPUT IS LOW.

CLEAR OVERRIDING B, THEN TRIGGER FROM B

3V

B INPUT

0V

≥ 50 ns ≥ 50 ns

3V

CLEAR 1.3 V

0V

VOH

Q OUTPUT

VOL

A INPUT IS LOW.

TRIGGERING FROM POSITIVE TRANSITION OF CLEAR

Figure 1

FAST AND LS TTL DATA

5-5

You might also like

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- A Practical Guide To Free-Energy' Devices - PJKbookDocument14 pagesA Practical Guide To Free-Energy' Devices - PJKbookBharat Mumbaikar100% (2)

- Minor Project Automatic Room Light ControllerDocument32 pagesMinor Project Automatic Room Light ControllerSarita Yadav100% (1)

- Flip Flop JK 7473Document11 pagesFlip Flop JK 7473Tatyantoro AndrastoNo ratings yet

- Data Sheet: 74HC/HCT221Document16 pagesData Sheet: 74HC/HCT221MUHAMMAD SISWANTORONo ratings yet

- HC4538ADocument14 pagesHC4538AnatanaelNo ratings yet

- M54HC221/221A M74HC221/221A: Dual Monostable MultivibratorDocument14 pagesM54HC221/221A M74HC221/221A: Dual Monostable MultivibratornooorNo ratings yet

- Sn74hc76 J-K Flip FlopDocument11 pagesSn74hc76 J-K Flip Flopcarlos tito torresNo ratings yet

- Data Sheet: 74HC/HCT273Document9 pagesData Sheet: 74HC/HCT273Edson CostaNo ratings yet

- 74LS122 Datasheet PDFDocument12 pages74LS122 Datasheet PDFYudhi TaokaenoiNo ratings yet

- Dual Monostable (LS Series)Document8 pagesDual Monostable (LS Series)Pandarinath ParachiNo ratings yet

- 74HC4538Document16 pages74HC4538ceco conevNo ratings yet

- 74HC123Document17 pages74HC123birricaNo ratings yet

- 74 HC 76Document12 pages74 HC 76agus satyaNo ratings yet

- Integrated CircuitsDocument7 pagesIntegrated Circuitssexan8No ratings yet

- 74 Ls 121Document10 pages74 Ls 121krlossnNo ratings yet

- M54HC123/123A M74HC123/123A: Dual Retriggerable Monostable MultivibratorDocument14 pagesM54HC123/123A M74HC123/123A: Dual Retriggerable Monostable MultivibratornooorNo ratings yet

- 74LVC273Document15 pages74LVC273ly7123No ratings yet

- 74HC HCT109 CNV 2Document10 pages74HC HCT109 CNV 2MUHAMMAD SISWANTORONo ratings yet

- SN54273, SN54LS273, SN74273, SN74LS273 Octal D-Type Flip-Flop With ClearDocument6 pagesSN54273, SN54LS273, SN74273, SN74LS273 Octal D-Type Flip-Flop With Clearvictor manuelNo ratings yet

- SN54273, SN54LS273, SN74273, SN74LS273 Octal D-Type Flip-Flop With ClearDocument8 pagesSN54273, SN54LS273, SN74273, SN74LS273 Octal D-Type Flip-Flop With Clearsas999333No ratings yet

- M54HC74 M74HC74: Dual D Type Flip Flop With Preset and ClearDocument11 pagesM54HC74 M74HC74: Dual D Type Flip Flop With Preset and ClearnooorNo ratings yet

- 74HC HCT390 CNV 2Document8 pages74HC HCT390 CNV 2joaquin espalterNo ratings yet

- SN 65 Lvelt 23Document17 pagesSN 65 Lvelt 23邹昊芃No ratings yet

- 74112Document12 pages74112Luis Rey Martínez RodríguezNo ratings yet

- M54HC107 M74HC107: Dual J-K Flip Flop With ClearDocument11 pagesM54HC107 M74HC107: Dual J-K Flip Flop With ClearnooorNo ratings yet

- DatasheetDocument19 pagesDatasheetСтанислав ИвановNo ratings yet

- Datasheet CD54HC107Document18 pagesDatasheet CD54HC107correoradioflyNo ratings yet

- Ren 8516 DST 20150612Document17 pagesRen 8516 DST 20150612JoséNo ratings yet

- CD 54 HC 221Document28 pagesCD 54 HC 221Nerza ElectronicsNo ratings yet

- CD54HC73, CD74HC73, CD74HCT73: Features DescriptionDocument12 pagesCD54HC73, CD74HC73, CD74HCT73: Features DescriptionacotfasNo ratings yet

- Lec 11 Sequential Logic CircuitsDocument49 pagesLec 11 Sequential Logic CircuitsDeependra NigamNo ratings yet

- 74HC112 (Flip Flop J-K)Document9 pages74HC112 (Flip Flop J-K)Oscar Zabaleta LaverdeNo ratings yet

- CD14538BMS IntersilDocument9 pagesCD14538BMS IntersildinhdtdNo ratings yet

- Semiconductor Technical Data: L SuffixDocument10 pagesSemiconductor Technical Data: L Suffixtarek proNo ratings yet

- Ic4 74HC4538Document13 pagesIc4 74HC4538elio.oyarzun4375No ratings yet

- Dual J-K Flip Flop With Preset and Clear: Order CodesDocument11 pagesDual J-K Flip Flop With Preset and Clear: Order CodesAtzin SanchezNo ratings yet

- MC10198 Monostable Multivibrator: CDIP-16 L Suffix CASE 620Document12 pagesMC10198 Monostable Multivibrator: CDIP-16 L Suffix CASE 620MarceloCobaNo ratings yet

- 74HC4053Document18 pages74HC4053Alvaro MedinaNo ratings yet

- MM74HC574 3-STATE Octal D-Type Edge-Triggered Flip-Flop: General Description FeaturesDocument8 pagesMM74HC574 3-STATE Octal D-Type Edge-Triggered Flip-Flop: General Description Featureskumar_santosh1989100% (1)

- SN 74 Alvch 16374Document18 pagesSN 74 Alvch 16374SuBaRu GTNo ratings yet

- Diode-Transistor Logic (DTL) : University of Connecticut 56Document32 pagesDiode-Transistor Logic (DTL) : University of Connecticut 56Amrendra Kumar MishraNo ratings yet

- M54HC273 M74HC273: Octal D Type Flip Flop With ClearDocument11 pagesM54HC273 M74HC273: Octal D Type Flip Flop With ClearnooorNo ratings yet

- Diode-Transistor Logic (DTL)Document32 pagesDiode-Transistor Logic (DTL)rejishkpkdNo ratings yet

- CMOS General Purpose Timer: Description Pin ConfigurationDocument10 pagesCMOS General Purpose Timer: Description Pin ConfigurationNagappan NagaNo ratings yet

- Obsolete Product(s) - Obsolete Product(s) Obsolete Product(s) - Obsolete Product(s)Document10 pagesObsolete Product(s) - Obsolete Product(s) Obsolete Product(s) - Obsolete Product(s)abu talha priyontoNo ratings yet

- MC14027B Dual J-K Flip-Flop: FeaturesDocument6 pagesMC14027B Dual J-K Flip-Flop: Featuresmarcos cordovaNo ratings yet

- Data Sheet: 74LVC1GX04Document16 pagesData Sheet: 74LVC1GX04AmirNo ratings yet

- Sensors: Read Chapter 2 of TextbookDocument102 pagesSensors: Read Chapter 2 of TextbookJanelle Gil MallariNo ratings yet

- LMX2322Document14 pagesLMX2322Igo_MichelNo ratings yet

- 74HC244Document8 pages74HC244vijayNo ratings yet

- D D D D D D: Description/ordering InformationDocument17 pagesD D D D D D: Description/ordering InformationBryan David Caceres DuarteNo ratings yet

- D D D D D: TL714C High-Speed Differential ComparatorDocument13 pagesD D D D D: TL714C High-Speed Differential ComparatorRabah AmidiNo ratings yet

- Data Sheet: 74AHC373 74AHCT373Document21 pagesData Sheet: 74AHC373 74AHCT373quasemanobrasNo ratings yet

- Contek - TA31002Document5 pagesContek - TA31002Wah yonoNo ratings yet

- High-Performance Silicon-Gate CMOS: Semiconductor Technical DataDocument6 pagesHigh-Performance Silicon-Gate CMOS: Semiconductor Technical DataMuhammad Rizwan Haider DurraniNo ratings yet

- 74HC595Document10 pages74HC595frickytoNo ratings yet

- 1-Of-8 Decoder/Demultiplexer: SL74HC138Document5 pages1-Of-8 Decoder/Demultiplexer: SL74HC138Dimano ManoNo ratings yet

- M54HC30 M74HC30: 8 Input Nand GateDocument9 pagesM54HC30 M74HC30: 8 Input Nand GatenooorNo ratings yet

- Vdocuments - MX Edn Design Ideas 2002Document198 pagesVdocuments - MX Edn Design Ideas 2002ciccioNo ratings yet

- High-Performance Silicon-Gate CMOS: Semiconductor Technical DataDocument6 pagesHigh-Performance Silicon-Gate CMOS: Semiconductor Technical DataAmirNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Ch8 1 - 19 48 50Document19 pagesCh8 1 - 19 48 50parsa mahvisNo ratings yet

- New Doc 2023-06-18 230407 - 230619 - 195859Document1 pageNew Doc 2023-06-18 230407 - 230619 - 195859parsa mahvisNo ratings yet

- Tn-Relays: Slim Polarized RelayDocument4 pagesTn-Relays: Slim Polarized Relayparsa mahvisNo ratings yet

- Upc 451Document4 pagesUpc 451parsa mahvisNo ratings yet

- Voltage Variable Phase ShifterDocument1 pageVoltage Variable Phase Shifterparsa mahvisNo ratings yet

- BA679/BA679S: RF PIN DiodesDocument4 pagesBA679/BA679S: RF PIN Diodesparsa mahvisNo ratings yet

- Vishay Semiconductors: FeaturesDocument4 pagesVishay Semiconductors: Featuresparsa mahvisNo ratings yet

- Education Apps and WebsitesDocument1 pageEducation Apps and Websitesparsa mahvisNo ratings yet

- Ballast-Lamp Technology Update: Fluorescent Lamp Starting and Operating TechnologiesDocument2 pagesBallast-Lamp Technology Update: Fluorescent Lamp Starting and Operating Technologiesparsa mahvisNo ratings yet

- A Low-Cost Surface Mount PIN Diode Attenuator: Application Note 1048Document6 pagesA Low-Cost Surface Mount PIN Diode Attenuator: Application Note 1048parsa mahvisNo ratings yet

- Gu Photomos (Aqv21, Aqv214H) : Controls Low-Level Input Signals. Controls Load Voltage 60V To 600V. FeaturesDocument4 pagesGu Photomos (Aqv21, Aqv214H) : Controls Low-Level Input Signals. Controls Load Voltage 60V To 600V. Featuresparsa mahvisNo ratings yet

- Drive Technologies: Brushless Motor DrivesDocument2 pagesDrive Technologies: Brushless Motor Drivesparsa mahvisNo ratings yet

- 1N5822 1 PDFDocument2 pages1N5822 1 PDFparsa mahvisNo ratings yet

- Version 2004-05-04: Dimensions / Maße in MM 1 B 2 E 3 CDocument3 pagesVersion 2004-05-04: Dimensions / Maße in MM 1 B 2 E 3 Cparsa mahvisNo ratings yet

- Ticket 4740656Document4 pagesTicket 4740656parsa mahvisNo ratings yet

- 30 CPQ 150Document5 pages30 CPQ 150parsa mahvisNo ratings yet

- B.SC Electronics and CommunicationDocument75 pagesB.SC Electronics and CommunicationAayan KNo ratings yet

- EC6411 C&SI Lab ManualDocument114 pagesEC6411 C&SI Lab ManualRajNo ratings yet

- A Solar Powered Smart Helmet With MultifeaturesDocument6 pagesA Solar Powered Smart Helmet With MultifeaturesInternational Journal of Engineering Inventions (IJEI)No ratings yet

- Amplifier and OscillatorsDocument102 pagesAmplifier and OscillatorsKapil ChoudharyNo ratings yet

- J. Flanagan - Laringe ArtificialDocument10 pagesJ. Flanagan - Laringe ArtificialLicio Bruno Ramos de AraújoNo ratings yet

- Project Report Fire AlarmDocument9 pagesProject Report Fire AlarmAYUSH PATELNo ratings yet

- EWA Final ReportDocument304 pagesEWA Final ReportgeniunetNo ratings yet

- EC-II SyllabusDocument1 pageEC-II SyllabusThiyagarajan VelayuthamNo ratings yet

- JNTU Jawaharlal Nehru Technological University R18 B.TECH EIE II Year SyllabusDocument29 pagesJNTU Jawaharlal Nehru Technological University R18 B.TECH EIE II Year SyllabuskiranpatruduNo ratings yet

- Lab Manual LicDocument66 pagesLab Manual LicUppum Mulakam FansNo ratings yet

- GATE 2018 - Previous Solutions & Video Lectures For FREE - Previous GATE Questions On Operational Amplifiers & Differential Amplifiers - II (2001 - Till Date)Document51 pagesGATE 2018 - Previous Solutions & Video Lectures For FREE - Previous GATE Questions On Operational Amplifiers & Differential Amplifiers - II (2001 - Till Date)Nitin MauryaNo ratings yet

- Analog Electronics LAB ManualDocument52 pagesAnalog Electronics LAB ManualPrahlad ReddyNo ratings yet

- Institute of Aeronautical Engineering (Autonomous) : Electronics and Communication EngineeringDocument32 pagesInstitute of Aeronautical Engineering (Autonomous) : Electronics and Communication EngineeringMano Har100% (1)

- Important Questions BEEMDocument5 pagesImportant Questions BEEMVIJAY VIDHYA SAGAR SNo ratings yet

- ExperimentDocument28 pagesExperimentGitesh NagarNo ratings yet

- 4.49 TYBSc Physics PDFDocument18 pages4.49 TYBSc Physics PDFrafiqsNo ratings yet

- Synopsis: OF Minor Project ON Electronic DoorbellDocument6 pagesSynopsis: OF Minor Project ON Electronic DoorbellomenderNo ratings yet

- Bistable Multivibrator Design PDFDocument20 pagesBistable Multivibrator Design PDFOmkar Thakur100% (1)

- Datasheet HEF74106BPDocument7 pagesDatasheet HEF74106BPBetsabeNo ratings yet

- Mini Mani 3 PDFDocument33 pagesMini Mani 3 PDFvishnu pillaiNo ratings yet

- Electronics and Communication EngineeringDocument552 pagesElectronics and Communication EngineeringShylu SamNo ratings yet

- The 555 OscillatorDocument8 pagesThe 555 OscillatorWaqas034No ratings yet

- Unit-V Blocking Oscillators and Time Base Generators Two Marks Question & AnswerDocument3 pagesUnit-V Blocking Oscillators and Time Base Generators Two Marks Question & AnswerJayed Ahmed LaskarNo ratings yet

- Ha17741 HiDocument18 pagesHa17741 HiBurin SapsiriNo ratings yet

- ADEDocument10 pagesADEashwinishettytpNo ratings yet

- Chapter-I Literature Survey: Department of EceDocument25 pagesChapter-I Literature Survey: Department of EceAnusha RudrarapuNo ratings yet

- Astable MultivibratorDocument4 pagesAstable MultivibratorDa100% (1)

- MX907Document3 pagesMX907João Manuel LopesNo ratings yet