Professional Documents

Culture Documents

Digital Design Course Syllabus

Digital Design Course Syllabus

Uploaded by

Dahlia ZamoraCopyright:

Available Formats

You might also like

- Métodos numéricos aplicados a Ingeniería: Casos de estudio usando MATLABFrom EverandMétodos numéricos aplicados a Ingeniería: Casos de estudio usando MATLABRating: 5 out of 5 stars5/5 (1)

- VLSI Interview QuestionsDocument11 pagesVLSI Interview QuestionsmibNo ratings yet

- L6 Bios Setup ConfigurationsDocument25 pagesL6 Bios Setup ConfigurationsFrancia VillagonzaloNo ratings yet

- PLC Lab ReportDocument11 pagesPLC Lab Reportdonatchange50% (2)

- Course Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentDocument6 pagesCourse Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentAbdullah SohailNo ratings yet

- CSE 231 Outline - 3Document3 pagesCSE 231 Outline - 3Emam Hossain Pial 1831170042No ratings yet

- Study Plan EE-221 Digital Logic DesignDocument5 pagesStudy Plan EE-221 Digital Logic Designnauman yasinNo ratings yet

- DLD_CS128L_CIS-Spring 24Document6 pagesDLD_CS128L_CIS-Spring 24Faisal YazdanieNo ratings yet

- Curriculum details of Y-3 T-1Document29 pagesCurriculum details of Y-3 T-1Mr. KamaruzzamanNo ratings yet

- Course Plan Digital ElectronicsDocument14 pagesCourse Plan Digital ElectronicsChakradhar AdupaNo ratings yet

- EE 421-Digital System Design-Dr. Shahid Masud-Updated PDFDocument4 pagesEE 421-Digital System Design-Dr. Shahid Masud-Updated PDFUbaid UmarNo ratings yet

- Updated DLD - Course OutlineDocument8 pagesUpdated DLD - Course OutlineabsarNo ratings yet

- Gs Ee118Document9 pagesGs Ee118Tomas PirirNo ratings yet

- 241 CSM-4 - Digital Logic - Lab Manual - Course Specification - 1Document48 pages241 CSM-4 - Digital Logic - Lab Manual - Course Specification - 1ahmedNo ratings yet

- Updated Course Outline EE 221 - Digital - Logic - Design - Spring - 2023Document9 pagesUpdated Course Outline EE 221 - Digital - Logic - Design - Spring - 2023Laiqa AliNo ratings yet

- CDF DLD TheoryDocument4 pagesCDF DLD TheoryMuhammad Fayyaz Khan AP Electronics ABTNo ratings yet

- Fall 2023 ELEC 205 (01) Syllabus 08 09 2023Document3 pagesFall 2023 ELEC 205 (01) Syllabus 08 09 2023caggllayan47No ratings yet

- Pre-Requisites: Course Objectives:: KLS's Gogte Institute of Technology, Udyambag, BelagaviDocument4 pagesPre-Requisites: Course Objectives:: KLS's Gogte Institute of Technology, Udyambag, BelagavianjanbsNo ratings yet

- Cmpe224 CS Fall2010-2011Document3 pagesCmpe224 CS Fall2010-2011MICHAEL K. E. DonkorNo ratings yet

- DE Course Plan2020Document10 pagesDE Course Plan2020Charu PathakNo ratings yet

- DLD Course OulineDocument2 pagesDLD Course OulineSarangNo ratings yet

- Syllabus DLD Fall 2020-2021Document2 pagesSyllabus DLD Fall 2020-2021Mahmoud Alshar'eNo ratings yet

- Logic Design Lab Lesson PlanDocument28 pagesLogic Design Lab Lesson PlanchaitanyaNo ratings yet

- 241 CSM-4 - Digital Logic-Course SpecificationDocument7 pages241 CSM-4 - Digital Logic-Course SpecificationahmedNo ratings yet

- Cmpe223 Sylabi AbetDocument3 pagesCmpe223 Sylabi AbetStrt SandyNo ratings yet

- 0 Course IntroductionDocument28 pages0 Course IntroductionKhai Hua MinhNo ratings yet

- Bits PilaniDocument3 pagesBits PilaniasdmddamcNo ratings yet

- DDE 1313 Digital Electronics 1 LODocument6 pagesDDE 1313 Digital Electronics 1 LOAhmad FadzlyNo ratings yet

- First Course in VHDL Modeling and Fpga Synthesis of Digital SystemsDocument30 pagesFirst Course in VHDL Modeling and Fpga Synthesis of Digital Systemshuy2910 dangdangNo ratings yet

- Course Plan DLD-2020Document16 pagesCourse Plan DLD-2020Muhammad AsadNo ratings yet

- Elc 218Document4 pagesElc 218ghostreamNo ratings yet

- CENG250-Syllabus-Summer 2021Document3 pagesCENG250-Syllabus-Summer 2021medo.miso.2000No ratings yet

- CS EE 220-Digital Logic Circuits-Jahangir Ikram-Adeel Pasha-Wala SaadehDocument3 pagesCS EE 220-Digital Logic Circuits-Jahangir Ikram-Adeel Pasha-Wala Saadehfarhan mukhtiarNo ratings yet

- DLD Theory F23Document4 pagesDLD Theory F23Imran Ahmad AhmadNo ratings yet

- Course Information Sheet: Syllabus: Unit Details HoursDocument47 pagesCourse Information Sheet: Syllabus: Unit Details HoursHarshith BejjamNo ratings yet

- Outline 3861 f19 Rev1Document3 pagesOutline 3861 f19 Rev1vigneshwar RNo ratings yet

- ELEC 1411 Syllabus 03-04Document2 pagesELEC 1411 Syllabus 03-04ardagecimli70No ratings yet

- DLD EXP 1 and 2Document20 pagesDLD EXP 1 and 2Muhammad UsmanNo ratings yet

- Syllabus-CEN-COE-424-AS (1-7)Document4 pagesSyllabus-CEN-COE-424-AS (1-7)Omar AboelfadlNo ratings yet

- Vlsi FinalDocument4 pagesVlsi FinalAbhinav KumarNo ratings yet

- DDDocument3 pagesDDJAY JANAK MANEKNo ratings yet

- Lab MANUAL - EDLD - July2022Document68 pagesLab MANUAL - EDLD - July2022darshanpote005No ratings yet

- B.tech Cse VTR Uge2021 de SyllabusDocument4 pagesB.tech Cse VTR Uge2021 de SyllabusBOLLIGARLA MOHAN SAI AKASH,CSE2021 Vel Tech, ChennaiNo ratings yet

- Code EEL204 Digital Electronics LAB Category L T P CreditDocument2 pagesCode EEL204 Digital Electronics LAB Category L T P CreditabhilashNo ratings yet

- Digital Logic Design TheoryDocument7 pagesDigital Logic Design TheoryPRABHU GNo ratings yet

- CS 114 Fundamentals of Programming - Fall 2019 - Zunera - FinalDocument4 pagesCS 114 Fundamentals of Programming - Fall 2019 - Zunera - FinalTalha AnwarNo ratings yet

- CS2031 Digital Logic Design OBE AdnanDocument4 pagesCS2031 Digital Logic Design OBE Adnanseemialvi6No ratings yet

- Teaching VLSI Design To Today's Students: Session 2532Document11 pagesTeaching VLSI Design To Today's Students: Session 2532aswinjohnNo ratings yet

- EE221-E Lecture 1 Fall 2016Document10 pagesEE221-E Lecture 1 Fall 2016sayed Tamir janNo ratings yet

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Document3 pagesCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Deepti MishraNo ratings yet

- De Course File 2013-14Document75 pagesDe Course File 2013-14ragvshahNo ratings yet

- ECE3362 Syllabus Fall 2014Document3 pagesECE3362 Syllabus Fall 2014Gershom BenjaminNo ratings yet

- Digital Logic Design: Tanzilur Rahman (TNR) Assistant Professor North South UniversityDocument16 pagesDigital Logic Design: Tanzilur Rahman (TNR) Assistant Professor North South UniversityMohammad Olid AfzalNo ratings yet

- EEE20001 Unit Outline Semester 2 2023Document12 pagesEEE20001 Unit Outline Semester 2 2023MKNo ratings yet

- Digital Communication SystemsDocument4 pagesDigital Communication SystemsMarina KhanNo ratings yet

- Bubt Eee-304 Lab Manual - Edited 25-12-21 v2Document73 pagesBubt Eee-304 Lab Manual - Edited 25-12-21 v2Md. Arif Hasan MasumNo ratings yet

- Ece 2003Document3 pagesEce 2003gokulNo ratings yet

- Syllabus: (Tentative) Bachelor of Technology (B. Tech.) Data Science and Artificial Intelligence (DSAI)Document53 pagesSyllabus: (Tentative) Bachelor of Technology (B. Tech.) Data Science and Artificial Intelligence (DSAI)Mohit KulhariNo ratings yet

- Ece F215 Digital Design - HandoutDocument3 pagesEce F215 Digital Design - HandoutRishiNo ratings yet

- 3rd, 5th, 7th Course OutlineDocument55 pages3rd, 5th, 7th Course OutlineSamiullah IlyasNo ratings yet

- Digital Technics 1 VM N A E'Document2 pagesDigital Technics 1 VM N A E'Zsolt KovácsNo ratings yet

- DPSD Course File Up PDFDocument365 pagesDPSD Course File Up PDFVINOD DNo ratings yet

- Schaum’s Outline of Computer Graphics 2/EFrom EverandSchaum’s Outline of Computer Graphics 2/ERating: 3.5 out of 5 stars3.5/5 (6)

- TABLE OF SPECIFICATIONS (Revised 2019) : A Ur Ora P Ioneer S M Emorial OllegeDocument1 pageTABLE OF SPECIFICATIONS (Revised 2019) : A Ur Ora P Ioneer S M Emorial OllegeDahlia Zamora100% (1)

- Learning Module Plumbing Junior High School Grade 7: A Urora P Ioneers M Emorial OllegeDocument1 pageLearning Module Plumbing Junior High School Grade 7: A Urora P Ioneers M Emorial OllegeDahlia ZamoraNo ratings yet

- Aurora Pioneers Memorial College: Curriculum MapDocument8 pagesAurora Pioneers Memorial College: Curriculum MapDahlia ZamoraNo ratings yet

- CIDAM NeedlecraftDocument13 pagesCIDAM NeedlecraftDahlia ZamoraNo ratings yet

- Tle 9 ModuleDocument5 pagesTle 9 ModuleAl Lhea Bandayanon MoralesNo ratings yet

- 1st Lecture DLDDocument13 pages1st Lecture DLDsibgha ziaNo ratings yet

- ABPROG User's ManualDocument35 pagesABPROG User's ManualMiguel VegaNo ratings yet

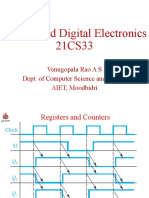

- Analog and Digital Electronics 21CS33: Venugopala Rao A S Dept. of Computer Science and Design AIET, MoodbidriDocument40 pagesAnalog and Digital Electronics 21CS33: Venugopala Rao A S Dept. of Computer Science and Design AIET, MoodbidrivenuraoNo ratings yet

- Coa Lecture Unit 3 PipeliningDocument95 pagesCoa Lecture Unit 3 PipeliningSumathy JayaramNo ratings yet

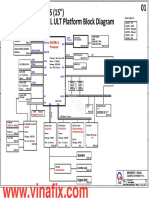

- Lenovo Ideapad La9911p g505 Laptop SchematicsDocument48 pagesLenovo Ideapad La9911p g505 Laptop SchematicsDimaTurcanNo ratings yet

- LVM Mirror Walking - Flash Read PreferredDocument15 pagesLVM Mirror Walking - Flash Read Preferredliew99No ratings yet

- Wistron jv50-cp RSB SchematicsDocument68 pagesWistron jv50-cp RSB SchematicsАлекс ХомичNo ratings yet

- Arm Program ModelDocument4 pagesArm Program ModelvlkumashankardeekshithNo ratings yet

- Static Timing Analysis: - RoshanDocument60 pagesStatic Timing Analysis: - Roshanmani krishna yakkatiNo ratings yet

- Convert Gray Code 101011 Into Its Binary Equivalent. Gray Code: 1 0 1 0 1 1 Binary Code: 1 1 0 0 1 0Document23 pagesConvert Gray Code 101011 Into Its Binary Equivalent. Gray Code: 1 0 1 0 1 1 Binary Code: 1 1 0 0 1 0khadarbasha.n nNo ratings yet

- Desktop Motherboard Service Training-Chip Level: (30 Days 24 Hrs Time) 720 Hrs / (30 Days 1.30 Hrs 45 HRS)Document7 pagesDesktop Motherboard Service Training-Chip Level: (30 Days 24 Hrs Time) 720 Hrs / (30 Days 1.30 Hrs 45 HRS)Rozitarmizi MohammadNo ratings yet

- ch3 1Document48 pagesch3 1Narayanan Ram100% (1)

- Ocr As and A Level Computer Science Heathcote R S Annas ArchiveDocument384 pagesOcr As and A Level Computer Science Heathcote R S Annas Archivemc5279185No ratings yet

- Vsphere 6.7 Configuration - MaximumsDocument13 pagesVsphere 6.7 Configuration - MaximumsRegginaNo ratings yet

- MBL 01Document8 pagesMBL 01Adis LagunaNo ratings yet

- Timing DiagramDocument35 pagesTiming DiagramNew worldNo ratings yet

- Arduino Mega 2560Document3 pagesArduino Mega 2560Wilfredo Aliaga JuárezNo ratings yet

- CST202 Computer Organization and Architecture June 2022Document2 pagesCST202 Computer Organization and Architecture June 2022Abhinav SNo ratings yet

- Microelectronics II 考古題 Part II: 劉昱賢 Yu-Sian LiuDocument25 pagesMicroelectronics II 考古題 Part II: 劉昱賢 Yu-Sian Liu安王No ratings yet

- DH61WW TechProdSpec06 PDFDocument86 pagesDH61WW TechProdSpec06 PDFFelipe Raul Chumpitaz GuevaraNo ratings yet

- Device Tree Tut - Power - ePAPR - APPROVED - v1.1 PDFDocument108 pagesDevice Tree Tut - Power - ePAPR - APPROVED - v1.1 PDFafdgtdsghfNo ratings yet

- HP Pavilion Presario Series PTGDDocument5 pagesHP Pavilion Presario Series PTGDgeorgilaNo ratings yet

- G34a SKL U n16s 20160105 SMTDocument47 pagesG34a SKL U n16s 20160105 SMTAntonio MartiniNo ratings yet

- Digital Circuit Work Book F1Document33 pagesDigital Circuit Work Book F1swaransh patelNo ratings yet

- Instruction Manual: C650 Bay ControllerDocument284 pagesInstruction Manual: C650 Bay Controllernguyen rinNo ratings yet

- Advanced Microprocessor & Microcontroller Lab Manual PDFDocument22 pagesAdvanced Microprocessor & Microcontroller Lab Manual PDFtariq76No ratings yet

Digital Design Course Syllabus

Digital Design Course Syllabus

Uploaded by

Dahlia ZamoraOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Design Course Syllabus

Digital Design Course Syllabus

Uploaded by

Dahlia ZamoraCopyright:

Available Formats

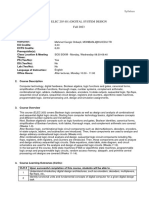

DIGITAL DESIGN COURSE SYLLABUS

COURSE TITLE: Digital Design (EGR3331)

(15 weeks lectures, 4 tutorials and 2 class projects)

TEXTBOOK: Charles H.Roth,Jr, "Fundamentals of Logic Design",ISBN 0-534-37804-8

INSTRUCTOR: Dr. A.Doumar

Office: Room 113, Building 7

Phone: Ext. 2154

e-mail: A.Doumar@aui.ma

OFFICE HOURS: MWF: 09:00-10:00, 16:00-18:00 OR BY APPOINTMENT

COURSE DESCRIPTION:

This course presents the introductory concepts that are needed in order to design digital systems.

Classical methods, including Boolean algebra, combinational and sequential logic design methods.

Additionally this course will present an introduction of the Hardware description language (VHDL)

and introduce students to design combinational and sequential circuits using VHDL and simulators.

INTENDED LEARNING OUTCOMES:

On successful completion of this course student should be able to design the basic logic functions,

simplification of expressions, Karnaugh maps,, flip flops, simple sequential systems, fan-out, propagation

delay, speed, power consumption of logic families. Programmable Logic Devices: architecture and

programming using VHDL. Implementing a simple MSI functions using VHDL : multiplexers, decoders,

registers and counters.

ABSENTEEISM:

The University's official attendance policy is stated as: "class attendance is compulsory for all students.

A student exceeding three unexcused absences may be dropped form the course and assigned the grade

of "F"... Any absentee must present a valid excuse to the instructor, and would hold responsible for all

assignments, quizzes and examinations held during their absence".

TESTS:

Two exams will be given during the semester; their dates will be announced in class.

A comprehensive final examination will be held at the end of the semester as scheduled by the University.

QUIZZES:

Quizzes may be assigned by the professor if it is deemed necessary.

Home work will be assigned from the textbook.

GRADING POLICIES:

The course grade will be determined from the percentage of the students' earned grades over the total

possible points. The percentiles for the different course assignments are:

Term exam 20%

Project 20%

Final Exam 40%

Quizzes/Homeworks 20%

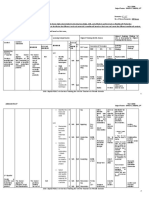

Course Calendar

EGR 3331 Course Outline/Schedule

WEEK Topic REFERENCECHAPTERS

1 Introduction, Logic Gates 2

2 Boolean Algebra, Logic Gates 2, 3

3 Boolean Algebra, Logic Gates 2, 3

4 Simplification/Karnaugh maps 5, 6

5 Simplification/Karnaugh maps 5, 6

6 Combinational Logic Design 8, 9

7 Introdution Logic Design using VHDL 8, 9, 10

8 Flip-Flops, Sequential Logic Design 11, 12

9 Spring break

10 Flip-Flops, Sequential Logic Design (counters) 11, 12

11 Flip-Flops, Sequential Logic Design (registers) 12, 13, 14

12 Other examples of sequential design 16, 17, 20

Class Project1--Design of a simple market

13 Lecture notes

clock

14 Class Project 2--Design of Trafic light controller Lecture notes

15 FINAL EXAM

Recommended books

Authors Titles, edition Publisher Year ISBN Cost Code

J F Wakerly Digital Design Prentice Hall 2000 0130825999 」37 C

Th. L. Floyd Digital Fundamentals Prentice Hall 2003 0130464112 」50 C

Codes : A = compulsory ; B = strongly recommended ; C = recommended ; D = wider reading

Study times

Type Details

Lectures and tutorials 45 hours

Tutorial Sheets 10 hours

Review and consolidation of course material 30 hours

Final revision and examination 15 hours

These times are an estimate of the work required by a typical student. There will be variations between

individuals, but you will run the risk of failure if you spend significantly less time on this course than these

guidelines suggest.

You might also like

- Métodos numéricos aplicados a Ingeniería: Casos de estudio usando MATLABFrom EverandMétodos numéricos aplicados a Ingeniería: Casos de estudio usando MATLABRating: 5 out of 5 stars5/5 (1)

- VLSI Interview QuestionsDocument11 pagesVLSI Interview QuestionsmibNo ratings yet

- L6 Bios Setup ConfigurationsDocument25 pagesL6 Bios Setup ConfigurationsFrancia VillagonzaloNo ratings yet

- PLC Lab ReportDocument11 pagesPLC Lab Reportdonatchange50% (2)

- Course Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentDocument6 pagesCourse Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentAbdullah SohailNo ratings yet

- CSE 231 Outline - 3Document3 pagesCSE 231 Outline - 3Emam Hossain Pial 1831170042No ratings yet

- Study Plan EE-221 Digital Logic DesignDocument5 pagesStudy Plan EE-221 Digital Logic Designnauman yasinNo ratings yet

- DLD_CS128L_CIS-Spring 24Document6 pagesDLD_CS128L_CIS-Spring 24Faisal YazdanieNo ratings yet

- Curriculum details of Y-3 T-1Document29 pagesCurriculum details of Y-3 T-1Mr. KamaruzzamanNo ratings yet

- Course Plan Digital ElectronicsDocument14 pagesCourse Plan Digital ElectronicsChakradhar AdupaNo ratings yet

- EE 421-Digital System Design-Dr. Shahid Masud-Updated PDFDocument4 pagesEE 421-Digital System Design-Dr. Shahid Masud-Updated PDFUbaid UmarNo ratings yet

- Updated DLD - Course OutlineDocument8 pagesUpdated DLD - Course OutlineabsarNo ratings yet

- Gs Ee118Document9 pagesGs Ee118Tomas PirirNo ratings yet

- 241 CSM-4 - Digital Logic - Lab Manual - Course Specification - 1Document48 pages241 CSM-4 - Digital Logic - Lab Manual - Course Specification - 1ahmedNo ratings yet

- Updated Course Outline EE 221 - Digital - Logic - Design - Spring - 2023Document9 pagesUpdated Course Outline EE 221 - Digital - Logic - Design - Spring - 2023Laiqa AliNo ratings yet

- CDF DLD TheoryDocument4 pagesCDF DLD TheoryMuhammad Fayyaz Khan AP Electronics ABTNo ratings yet

- Fall 2023 ELEC 205 (01) Syllabus 08 09 2023Document3 pagesFall 2023 ELEC 205 (01) Syllabus 08 09 2023caggllayan47No ratings yet

- Pre-Requisites: Course Objectives:: KLS's Gogte Institute of Technology, Udyambag, BelagaviDocument4 pagesPre-Requisites: Course Objectives:: KLS's Gogte Institute of Technology, Udyambag, BelagavianjanbsNo ratings yet

- Cmpe224 CS Fall2010-2011Document3 pagesCmpe224 CS Fall2010-2011MICHAEL K. E. DonkorNo ratings yet

- DE Course Plan2020Document10 pagesDE Course Plan2020Charu PathakNo ratings yet

- DLD Course OulineDocument2 pagesDLD Course OulineSarangNo ratings yet

- Syllabus DLD Fall 2020-2021Document2 pagesSyllabus DLD Fall 2020-2021Mahmoud Alshar'eNo ratings yet

- Logic Design Lab Lesson PlanDocument28 pagesLogic Design Lab Lesson PlanchaitanyaNo ratings yet

- 241 CSM-4 - Digital Logic-Course SpecificationDocument7 pages241 CSM-4 - Digital Logic-Course SpecificationahmedNo ratings yet

- Cmpe223 Sylabi AbetDocument3 pagesCmpe223 Sylabi AbetStrt SandyNo ratings yet

- 0 Course IntroductionDocument28 pages0 Course IntroductionKhai Hua MinhNo ratings yet

- Bits PilaniDocument3 pagesBits PilaniasdmddamcNo ratings yet

- DDE 1313 Digital Electronics 1 LODocument6 pagesDDE 1313 Digital Electronics 1 LOAhmad FadzlyNo ratings yet

- First Course in VHDL Modeling and Fpga Synthesis of Digital SystemsDocument30 pagesFirst Course in VHDL Modeling and Fpga Synthesis of Digital Systemshuy2910 dangdangNo ratings yet

- Course Plan DLD-2020Document16 pagesCourse Plan DLD-2020Muhammad AsadNo ratings yet

- Elc 218Document4 pagesElc 218ghostreamNo ratings yet

- CENG250-Syllabus-Summer 2021Document3 pagesCENG250-Syllabus-Summer 2021medo.miso.2000No ratings yet

- CS EE 220-Digital Logic Circuits-Jahangir Ikram-Adeel Pasha-Wala SaadehDocument3 pagesCS EE 220-Digital Logic Circuits-Jahangir Ikram-Adeel Pasha-Wala Saadehfarhan mukhtiarNo ratings yet

- DLD Theory F23Document4 pagesDLD Theory F23Imran Ahmad AhmadNo ratings yet

- Course Information Sheet: Syllabus: Unit Details HoursDocument47 pagesCourse Information Sheet: Syllabus: Unit Details HoursHarshith BejjamNo ratings yet

- Outline 3861 f19 Rev1Document3 pagesOutline 3861 f19 Rev1vigneshwar RNo ratings yet

- ELEC 1411 Syllabus 03-04Document2 pagesELEC 1411 Syllabus 03-04ardagecimli70No ratings yet

- DLD EXP 1 and 2Document20 pagesDLD EXP 1 and 2Muhammad UsmanNo ratings yet

- Syllabus-CEN-COE-424-AS (1-7)Document4 pagesSyllabus-CEN-COE-424-AS (1-7)Omar AboelfadlNo ratings yet

- Vlsi FinalDocument4 pagesVlsi FinalAbhinav KumarNo ratings yet

- DDDocument3 pagesDDJAY JANAK MANEKNo ratings yet

- Lab MANUAL - EDLD - July2022Document68 pagesLab MANUAL - EDLD - July2022darshanpote005No ratings yet

- B.tech Cse VTR Uge2021 de SyllabusDocument4 pagesB.tech Cse VTR Uge2021 de SyllabusBOLLIGARLA MOHAN SAI AKASH,CSE2021 Vel Tech, ChennaiNo ratings yet

- Code EEL204 Digital Electronics LAB Category L T P CreditDocument2 pagesCode EEL204 Digital Electronics LAB Category L T P CreditabhilashNo ratings yet

- Digital Logic Design TheoryDocument7 pagesDigital Logic Design TheoryPRABHU GNo ratings yet

- CS 114 Fundamentals of Programming - Fall 2019 - Zunera - FinalDocument4 pagesCS 114 Fundamentals of Programming - Fall 2019 - Zunera - FinalTalha AnwarNo ratings yet

- CS2031 Digital Logic Design OBE AdnanDocument4 pagesCS2031 Digital Logic Design OBE Adnanseemialvi6No ratings yet

- Teaching VLSI Design To Today's Students: Session 2532Document11 pagesTeaching VLSI Design To Today's Students: Session 2532aswinjohnNo ratings yet

- EE221-E Lecture 1 Fall 2016Document10 pagesEE221-E Lecture 1 Fall 2016sayed Tamir janNo ratings yet

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Document3 pagesCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Deepti MishraNo ratings yet

- De Course File 2013-14Document75 pagesDe Course File 2013-14ragvshahNo ratings yet

- ECE3362 Syllabus Fall 2014Document3 pagesECE3362 Syllabus Fall 2014Gershom BenjaminNo ratings yet

- Digital Logic Design: Tanzilur Rahman (TNR) Assistant Professor North South UniversityDocument16 pagesDigital Logic Design: Tanzilur Rahman (TNR) Assistant Professor North South UniversityMohammad Olid AfzalNo ratings yet

- EEE20001 Unit Outline Semester 2 2023Document12 pagesEEE20001 Unit Outline Semester 2 2023MKNo ratings yet

- Digital Communication SystemsDocument4 pagesDigital Communication SystemsMarina KhanNo ratings yet

- Bubt Eee-304 Lab Manual - Edited 25-12-21 v2Document73 pagesBubt Eee-304 Lab Manual - Edited 25-12-21 v2Md. Arif Hasan MasumNo ratings yet

- Ece 2003Document3 pagesEce 2003gokulNo ratings yet

- Syllabus: (Tentative) Bachelor of Technology (B. Tech.) Data Science and Artificial Intelligence (DSAI)Document53 pagesSyllabus: (Tentative) Bachelor of Technology (B. Tech.) Data Science and Artificial Intelligence (DSAI)Mohit KulhariNo ratings yet

- Ece F215 Digital Design - HandoutDocument3 pagesEce F215 Digital Design - HandoutRishiNo ratings yet

- 3rd, 5th, 7th Course OutlineDocument55 pages3rd, 5th, 7th Course OutlineSamiullah IlyasNo ratings yet

- Digital Technics 1 VM N A E'Document2 pagesDigital Technics 1 VM N A E'Zsolt KovácsNo ratings yet

- DPSD Course File Up PDFDocument365 pagesDPSD Course File Up PDFVINOD DNo ratings yet

- Schaum’s Outline of Computer Graphics 2/EFrom EverandSchaum’s Outline of Computer Graphics 2/ERating: 3.5 out of 5 stars3.5/5 (6)

- TABLE OF SPECIFICATIONS (Revised 2019) : A Ur Ora P Ioneer S M Emorial OllegeDocument1 pageTABLE OF SPECIFICATIONS (Revised 2019) : A Ur Ora P Ioneer S M Emorial OllegeDahlia Zamora100% (1)

- Learning Module Plumbing Junior High School Grade 7: A Urora P Ioneers M Emorial OllegeDocument1 pageLearning Module Plumbing Junior High School Grade 7: A Urora P Ioneers M Emorial OllegeDahlia ZamoraNo ratings yet

- Aurora Pioneers Memorial College: Curriculum MapDocument8 pagesAurora Pioneers Memorial College: Curriculum MapDahlia ZamoraNo ratings yet

- CIDAM NeedlecraftDocument13 pagesCIDAM NeedlecraftDahlia ZamoraNo ratings yet

- Tle 9 ModuleDocument5 pagesTle 9 ModuleAl Lhea Bandayanon MoralesNo ratings yet

- 1st Lecture DLDDocument13 pages1st Lecture DLDsibgha ziaNo ratings yet

- ABPROG User's ManualDocument35 pagesABPROG User's ManualMiguel VegaNo ratings yet

- Analog and Digital Electronics 21CS33: Venugopala Rao A S Dept. of Computer Science and Design AIET, MoodbidriDocument40 pagesAnalog and Digital Electronics 21CS33: Venugopala Rao A S Dept. of Computer Science and Design AIET, MoodbidrivenuraoNo ratings yet

- Coa Lecture Unit 3 PipeliningDocument95 pagesCoa Lecture Unit 3 PipeliningSumathy JayaramNo ratings yet

- Lenovo Ideapad La9911p g505 Laptop SchematicsDocument48 pagesLenovo Ideapad La9911p g505 Laptop SchematicsDimaTurcanNo ratings yet

- LVM Mirror Walking - Flash Read PreferredDocument15 pagesLVM Mirror Walking - Flash Read Preferredliew99No ratings yet

- Wistron jv50-cp RSB SchematicsDocument68 pagesWistron jv50-cp RSB SchematicsАлекс ХомичNo ratings yet

- Arm Program ModelDocument4 pagesArm Program ModelvlkumashankardeekshithNo ratings yet

- Static Timing Analysis: - RoshanDocument60 pagesStatic Timing Analysis: - Roshanmani krishna yakkatiNo ratings yet

- Convert Gray Code 101011 Into Its Binary Equivalent. Gray Code: 1 0 1 0 1 1 Binary Code: 1 1 0 0 1 0Document23 pagesConvert Gray Code 101011 Into Its Binary Equivalent. Gray Code: 1 0 1 0 1 1 Binary Code: 1 1 0 0 1 0khadarbasha.n nNo ratings yet

- Desktop Motherboard Service Training-Chip Level: (30 Days 24 Hrs Time) 720 Hrs / (30 Days 1.30 Hrs 45 HRS)Document7 pagesDesktop Motherboard Service Training-Chip Level: (30 Days 24 Hrs Time) 720 Hrs / (30 Days 1.30 Hrs 45 HRS)Rozitarmizi MohammadNo ratings yet

- ch3 1Document48 pagesch3 1Narayanan Ram100% (1)

- Ocr As and A Level Computer Science Heathcote R S Annas ArchiveDocument384 pagesOcr As and A Level Computer Science Heathcote R S Annas Archivemc5279185No ratings yet

- Vsphere 6.7 Configuration - MaximumsDocument13 pagesVsphere 6.7 Configuration - MaximumsRegginaNo ratings yet

- MBL 01Document8 pagesMBL 01Adis LagunaNo ratings yet

- Timing DiagramDocument35 pagesTiming DiagramNew worldNo ratings yet

- Arduino Mega 2560Document3 pagesArduino Mega 2560Wilfredo Aliaga JuárezNo ratings yet

- CST202 Computer Organization and Architecture June 2022Document2 pagesCST202 Computer Organization and Architecture June 2022Abhinav SNo ratings yet

- Microelectronics II 考古題 Part II: 劉昱賢 Yu-Sian LiuDocument25 pagesMicroelectronics II 考古題 Part II: 劉昱賢 Yu-Sian Liu安王No ratings yet

- DH61WW TechProdSpec06 PDFDocument86 pagesDH61WW TechProdSpec06 PDFFelipe Raul Chumpitaz GuevaraNo ratings yet

- Device Tree Tut - Power - ePAPR - APPROVED - v1.1 PDFDocument108 pagesDevice Tree Tut - Power - ePAPR - APPROVED - v1.1 PDFafdgtdsghfNo ratings yet

- HP Pavilion Presario Series PTGDDocument5 pagesHP Pavilion Presario Series PTGDgeorgilaNo ratings yet

- G34a SKL U n16s 20160105 SMTDocument47 pagesG34a SKL U n16s 20160105 SMTAntonio MartiniNo ratings yet

- Digital Circuit Work Book F1Document33 pagesDigital Circuit Work Book F1swaransh patelNo ratings yet

- Instruction Manual: C650 Bay ControllerDocument284 pagesInstruction Manual: C650 Bay Controllernguyen rinNo ratings yet

- Advanced Microprocessor & Microcontroller Lab Manual PDFDocument22 pagesAdvanced Microprocessor & Microcontroller Lab Manual PDFtariq76No ratings yet