Professional Documents

Culture Documents

Iss l8 PDF

Iss l8 PDF

Uploaded by

asyfa dianningrumOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Iss l8 PDF

Iss l8 PDF

Uploaded by

asyfa dianningrumCopyright:

Available Formats

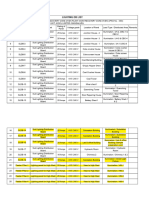

Lecture 8: Data Acquisition II

g Sample and hold

g Multiplexing

g Analog to digital conversion

g Digital to analog conversion

Intelligent Sensor Systems 1

Ricardo Gutierrez-Osuna

Wright State University

Architecture of data acquisition systems

Sensors DAQ DSP DAQ Actuators

S/H

S/H

CPU

ADC FIFO

interface

S/H

S/H

Signal Anti Sample

Sensors conditioning aliasing and hold MUX

From [Tay97]

Lecture 8

Intelligent Sensor Systems 2

Ricardo Gutierrez-Osuna

Wright State University

Sample and hold

g A Sample and hold (S/H) circuit has

two basic operating modes

n Sample mode: The output follows the

input

n Hold mode: The output is held

constant until sample mode is

resumed

g The main application of S/H circuits

is to hold the input signal to an

ADC constant during conversion

n Why? Imagine trying to photograph a

moving object! From [FB00]

Intelligent Sensor Systems 3

Ricardo Gutierrez-Osuna

Wright State University

Basic S/H circuit

g Basic elements

n Voltage followers

n FET switch

From [HH89]

g Operation

n IC1 provides low Zout version of input signal

n Q1 passes the signal during ‘sample’ and disconnects during ‘hold’

n C preserves the value during ‘hold’

n IC2 is a high Zin op-amp to minimize capacitor discharge during ‘hold’

Intelligent Sensor Systems 4

Ricardo Gutierrez-Osuna

Wright State University

S/H response characteristics

g Response parameters

n Aperture time: time required

for the switch to open (~50ns)

n Droop: capacitor discharge

n (~1mV/ms)

n Acquisition time: switch operation

plus capacitor charging time

g Considerations for choosing C From [Ram96]

n C should be large enough to minimize ‘droop’ caused by leakage

currents in Q1 and IC2

n C should be small enough to track fast signals since it forms a low-pass

filter with Q1’s ON resistance!

g In practice, the slew rate of the entire circuit is determined by IC1’s output

current and Q1’s ON resistance

Intelligent Sensor Systems 5

Ricardo Gutierrez-Osuna

Wright State University

Multiplexers

g A multiplexer is a circuit that allows you

to select any of several inputs, as

specified by digital control signals

n Since analog switches are bi-directional, this

circuit could also be used as a de-

multiplexer!

g It could also be uses as a digital MUX since

logic levels are just voltages

From [HH89]

g FET analog switches

n N-channel enhancement-mode MOS-FET

g When Gate is grounded or negative, the FET

is non-conducting

n Drain-source resistance in the order of

10,000MΩ

g Bringing the Gate to +15V puts the drain-

source channel into conduction

From [HH89]

n Drain-source resistance in the order of 100Ω

Intelligent Sensor Systems 6

Ricardo Gutierrez-Osuna

Wright State University

Analog-to-digital converters

g Single slope or ramp

g Successive approximation

g Dual slope

g Parallel or ‘flash’

Intelligent Sensor Systems 7

Ricardo Gutierrez-Osuna

Wright State University

Single slope or ramp ADC

g Composed of three basic elements

n A binary counter

n A digital-to-analog converter

n An analog comparator

g Operation

n Counter is reset

n Analog input is sampled

From [BW96]

n While VA>VB counter increments

n When VA=VB counter stops and binary code is available at the output

g Characteristics

n Relatively slow since conversion time could be up to 2N, where N is the

resolution of the ADC

Intelligent Sensor Systems 8

Ricardo Gutierrez-Osuna

Wright State University

Successive approximation ADC

g Basic elements

n A digital-to-analog converter

n An analog comparator

n A control logic module

n A successive approx. register

g Operation is based on a

binary search

n Initially, the register provides From [BW96]

an output corresponding to half the range (1000…0)

g If the analog input is greater, then MSB=1, else MSB=0

n The register performs the same operation from MSB to LSB

g Characteristics

n Conversion requires only N steps, where N is the resolution of the ADC

g Conversion times of µs are typical

Intelligent Sensor Systems 9

Ricardo Gutierrez-Osuna

Wright State University

Dual slope ADC

g Basic elements

n An integrator

n A zero-crossing detector

n A binary counter

n Logic gates and switches

g Operation

n Counter is reset and switch is connected to the analog input

g The integrator generates a negative ramp whose slope is proportional to the analog

input

g The comparator goes HIGH, enabling clock pulses into the counter

n When counter overflows, it resets to zero and the control circuit switches the

switch to a reference negative voltage

g This causes the integrator to generate a positive slope ramp

g When this ramp reaches zero, the comparator goes low and stops the counter, whose

value represents the analog input

g Characteristics

n Very high resolution, but also slower (30 conversions/sec)

g Widely used in digital multi-meters

n Insensitive to clock drift, RC drifts and high-frequency noise

Intelligent Sensor Systems 10

Ricardo Gutierrez-Osuna

Wright State University

Dual slope ADC

From [Ram96]

Intelligent Sensor Systems 11

Ricardo Gutierrez-Osuna

Wright State University

Parallel or flash ADC

g Basic elements

n A multiple voltage divider

n A set of comparators

n A priority encoder

g Operation

n Analog input applied to

all comparators

n Priority encoder converts

comparator pattern into binary

From [BW96]

g E.g.: A 3-bit ADC:

n For comparator outputs of 0001111, priority encoder generates 100

n For comparator outputs of 0111111, priority encoder generates 110

g Characteristics

n Very fast (e.g., 8-bit ADCs capable of 20 million conversions/sec)

n Very expensive for large N since the number of comparators is 2N-1

Intelligent Sensor Systems 12

Ricardo Gutierrez-Osuna

Wright State University

Digital-to-analog converters

g Binary weighted ladder

g R-2R ladder

g Pulse width modulation

Intelligent Sensor Systems 13

Ricardo Gutierrez-Osuna

Wright State University

Binary weighted ladder

g Based on the summing op-amp circuit from lecture 5

n Each input resistor is twice the value of the previous one

n Inputs are weighted according to their resistors

g Characteristics

n The lowest value resistor R affects the MSB and must have the highest

precision

n This circuit is impractical for large N since it would require high

precision resistors for a wide range

From [BW96]

Intelligent Sensor Systems 14

Ricardo Gutierrez-Osuna

Wright State University

R-2R ladder

g Basic elements

n 2N resistors

n An op-amp

n N switches

From [Ram96]

g Operation

n Switches

g When bit Ik=1, the corresponding switch is connected to VREF

g When bit Ik=0, the corresponding switch is connected to GND

n Assume all the legs but one are grounded

g The one connected to VREF will generate a current that flows towards the

inverting input of the op-amp

g This current is halved by the resistor network at each node

g Therefore, the current contribution of each input is weighted by its position

in the binary number

Intelligent Sensor Systems 15

Ricardo Gutierrez-Osuna

Wright State University

R-2R ladder

g The R-2R operation is better understood by redrawing the

resistor network

n In (b) only the MSB is ON

n In (c) only the next bit to the MSB is ON

From [Tay97]

Intelligent Sensor Systems 16

Ricardo Gutierrez-Osuna

Wright State University

Pulse Width Modulation

g Basic components

n A digital line

n An RC low-pass filter

g Operation

n The digital line is used to generate a train of pulses of fixed frequency

n The width (duty cycle) of the pulse is made proportional to the desired

analog output

n The pulse train is then passed through a low-pass filter, which

generates an output voltage proportional to the average time spent in

the HIGH state

Digital C Analog

pulses output

Intelligent Sensor Systems 17

Ricardo Gutierrez-Osuna

Wright State University

References

[Ram96] D. C. Ramsay, 1996, Principles of Engineering

Instrumentation, Arnold, London, UK

[Tay97] H. R. Taylor, 1997, Data Acquisition for Sensor Systems,

Chapman and Hall, London, UK.

[HH89] P. Horowitz and W. Hill, 1989, The Art of Electronics, 2nd

Ed., Cambridge University Press, Cambridge, UK

[BW96] J. Brignell and N. White, 1996, Intelligent Sensor Systems,

2nd Ed., IOP, Bristol, UK.

[FB00] R. S. Figliola and D.E. Beasley, Theory and design of

Mechanical Measurements, 3rd Ed., Wiley, New York.

Intelligent Sensor Systems 18

Ricardo Gutierrez-Osuna

Wright State University

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5825)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (823)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (403)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Suzuki Swift Diagrama PDFDocument18 pagesSuzuki Swift Diagrama PDFXavier Calvache75% (8)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Ad2 10 1 TTPPDocument31 pagesAd2 10 1 TTPPEldon Adrian Phillips100% (1)

- GO2Bank Template 2021 13543545564Document5 pagesGO2Bank Template 2021 13543545564Marilyn CastilloNo ratings yet

- V RepOverviewPresentationDocument42 pagesV RepOverviewPresentationFernando IsaacNo ratings yet

- Multi-Body Dynamics Modelling of Seated Human Body Under Exposure To Whole-Body VibrationDocument7 pagesMulti-Body Dynamics Modelling of Seated Human Body Under Exposure To Whole-Body Vibrationengineer86No ratings yet

- Lavalle PlanningDocument121 pagesLavalle Planningengineer86No ratings yet

- Proceedings Editia 1Document333 pagesProceedings Editia 1engineer86No ratings yet

- Advanced Mechanics in Robotic SystemsDocument7 pagesAdvanced Mechanics in Robotic Systemsengineer86No ratings yet

- Path Planning Algorithms For A GPS Based Electronic Tow BarDocument6 pagesPath Planning Algorithms For A GPS Based Electronic Tow Barengineer86No ratings yet

- Autonomous Excavator ThesisDocument116 pagesAutonomous Excavator Thesisengineer86No ratings yet

- Electronically Controlled Towing Bar Between Agricultural VehiclesDocument7 pagesElectronically Controlled Towing Bar Between Agricultural Vehiclesengineer86No ratings yet

- Om 20000124Document418 pagesOm 20000124engineer86No ratings yet

- Automation in ConstrnDocument22 pagesAutomation in Constrnarun77cNo ratings yet

- Barnes Etal2003aDocument14 pagesBarnes Etal2003aengineer86No ratings yet

- Testing of RTK-Level Satellite-Based Tractor Auto-Guidance Using A Visual Sensor SystemDocument8 pagesTesting of RTK-Level Satellite-Based Tractor Auto-Guidance Using A Visual Sensor Systemengineer86No ratings yet

- Servo - February 2009 (Malestrom)Document84 pagesServo - February 2009 (Malestrom)engineer86100% (1)

- Electrical ApplicationDocument4 pagesElectrical Applicationengineer86No ratings yet

- Quality Assurance, Testing, and InspectionDocument17 pagesQuality Assurance, Testing, and Inspectionengineer86No ratings yet

- Strain Gages: and AccessoriesDocument100 pagesStrain Gages: and Accessoriesengineer86No ratings yet

- Motoman Robotics - Glossary of Robotics TermsDocument15 pagesMotoman Robotics - Glossary of Robotics Termsengineer86No ratings yet

- Step Motor Engineer (2002 Catlog)Document13 pagesStep Motor Engineer (2002 Catlog)engineer86No ratings yet

- Step Motor Engineer (2002 Catlog)Document13 pagesStep Motor Engineer (2002 Catlog)engineer86No ratings yet

- Simularea Unui Mecanism Cu Ajutorul SimscapeDocument11 pagesSimularea Unui Mecanism Cu Ajutorul Simscapeengineer86No ratings yet

- Configuring and Managing ZonesDocument46 pagesConfiguring and Managing ZoneszingerrrNo ratings yet

- Draw Wire EncoderDocument2 pagesDraw Wire EncoderdiewiesNo ratings yet

- ProofreadingDocument2 pagesProofreadinggs123@hotmail.comNo ratings yet

- PAC-5000A: Multi-Zone All-In-One 2 Bus Mixer AmplifierDocument12 pagesPAC-5000A: Multi-Zone All-In-One 2 Bus Mixer AmplifierJavier TorradoNo ratings yet

- Lunes Martes Miyerkules Huwebes Biyernes: Grade 4 Daily Lesson LogDocument6 pagesLunes Martes Miyerkules Huwebes Biyernes: Grade 4 Daily Lesson LogAlliahNo ratings yet

- Getting Started With Paper Circuits EbookDocument10 pagesGetting Started With Paper Circuits Ebookarmaan shakirNo ratings yet

- LDB - SLDB ListDocument2 pagesLDB - SLDB ListSUSOVAN BISWASNo ratings yet

- Roc RDO23 PORVENIR PENDEN RAPIDROPDocument3 pagesRoc RDO23 PORVENIR PENDEN RAPIDROPJhonatan BlanquicettNo ratings yet

- Dresta SB 60 Ms 3046 Dss11 Web A1Document6 pagesDresta SB 60 Ms 3046 Dss11 Web A1Mgc ElektronikNo ratings yet

- Thermo 1 & 2Document4 pagesThermo 1 & 2Oloj YuNo ratings yet

- Russian Codes: Catalog of Regulations Available To OrderDocument2 pagesRussian Codes: Catalog of Regulations Available To Ordervemps36No ratings yet

- Samsung Lte EpcDocument3 pagesSamsung Lte Epcengineer_3No ratings yet

- Oracle®Solaris ZFSAdministration GuideDocument332 pagesOracle®Solaris ZFSAdministration GuideParashar SinghNo ratings yet

- Scalable OpenSource StorageDocument31 pagesScalable OpenSource Storagejweb911No ratings yet

- Assignment Iv PDFDocument2 pagesAssignment Iv PDFSurya TripathiNo ratings yet

- Wastewater Treatment - Tertiary and Sludge Handling Prepared by Furby RamosDocument23 pagesWastewater Treatment - Tertiary and Sludge Handling Prepared by Furby RamosFrancisco DeLos Angeles IIINo ratings yet

- Quality Index in Prediction of Properties of Aluminum Castings-A ReviewDocument8 pagesQuality Index in Prediction of Properties of Aluminum Castings-A ReviewJailson Da SilvaNo ratings yet

- Manual Medilink-90Document18 pagesManual Medilink-90manuela HurtadoNo ratings yet

- Bts426l1 SMD Infineon (Lu)Document15 pagesBts426l1 SMD Infineon (Lu)BRUNONo ratings yet

- Energy Crisis in PakistanDocument14 pagesEnergy Crisis in PakistanshahmeerbilalNo ratings yet

- BENDY AND THE INK MACHINE SONG (Ft. OR3O) Absolutely Anything (SFM) CG5 - YouTube PDFDocument1 pageBENDY AND THE INK MACHINE SONG (Ft. OR3O) Absolutely Anything (SFM) CG5 - YouTube PDFAlexisNo ratings yet

- 02 Courier System ManagementDocument49 pages02 Courier System Managementranahamid007100% (3)

- Work Breakdown Structures de PMI PDFDocument45 pagesWork Breakdown Structures de PMI PDFGladys Sánchez100% (1)

- Physics Heat Solution PDFDocument4 pagesPhysics Heat Solution PDFsiba padhy100% (1)

- OPTIMA Compact Actuators 53-1180 & 53-1183Document4 pagesOPTIMA Compact Actuators 53-1180 & 53-1183fareedeeNo ratings yet

- FMDS0796Document26 pagesFMDS0796Felipe Mees FaracoNo ratings yet

- WebRTC SIP Gateway Doc PDFDocument44 pagesWebRTC SIP Gateway Doc PDFMicroshare Software SolutionsNo ratings yet