Professional Documents

Culture Documents

White LED Driver With PWM Brightness Control in Small Package

White LED Driver With PWM Brightness Control in Small Package

Uploaded by

Ramíro ChocotecóOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

White LED Driver With PWM Brightness Control in Small Package

White LED Driver With PWM Brightness Control in Small Package

Uploaded by

Ramíro ChocotecóCopyright:

Available Formats

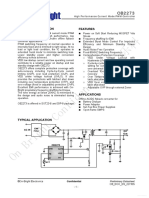

AW9962

Jun 2018 V1.3

White LED Driver with PWM Brightness Control in Small

Package

FEATURES GENERAL DESCRIPTION

1% PWM dimming current accuracy ±20% The AW9962 is a white LED driver with integrated

boost converter. With an internal 40V switch FET,

Support 0.3% PWM dimming(VFB.TYP=0.6mV)

the AW9962 drives up a string of up to 10 LEDs in

PWM control input for CABC operation series. The boost converter runs at 1.1MHz fixed

1.1MHz Switching Frequency switching frequency to reduce output ripple,

improve conversion efficiency, and allows for the

38V Over-voltage Protection for up to 10 LEDs use of small external components.

in Series

The default white LED current is set with the

Innovative CDC Output Drive Technology, external sense resistor RSET, and the feedback

Significantly Improve EMI Performance voltage is regulated to 200mV, as shown in the

200mV Reference Voltage typical application. During the operation, a pulse

width modulation (PWM) signal can be applied to

2.7V to 5.5V Input Voltage Range

the CTRL pin through which the duty cycle

Over-current and Over-temperature Protection determines the feedback reference voltage.

Built-in Soft-start Limits Inrush Current AW9962 integrates built-in soft-start function to

minimize the power supply inrush current.

Ultra Small 2mm*2mm TDFN-6L package

AW9962 also integrates over-current protection ,

LED open protection and over temperature

APPLICATIONS protection(OTP) to prevent chip from entering

abnormal operating conditions.

Mobile Phones

Portable Media Players

PDAs

GPS Receivers

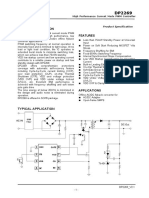

TYPICAL APPLICATION CIRCUIT

L Schottky Diode

VIN

10μH

* * D1

CIN1 CIN2 optional 6 4 COUT2 optional COUT1

10μF 100nF VIN SW 33pF/50V 1μF/50V D2

D3

D4

AW9962DNR

ON/OFF 5 1 D5

CTRL FB

DIMMING CONTROL

2 RSET D6

COMP 10Ω

CCOMP GND D7

47nF

3,7

D8

D9

D10

20mA

Figure 1 Typical Application Circuit of AW9962

All trademarks are the property of their respective owners

www.awinic.com.cn 1 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

PIN CONFIGURATION AND TOP MARK

AW9962DNR TOP VIEW AW9962DNR MARKING

VIN CTRL SW

6 5 4

7

GND

AL62

XXXX

1 2 3

FB COMP GND

AL62—AW9962DNR

XXXX—Manufacture Data Code

Figure 2 Pin Configuration and Top Mark

PIN DEFINITION

No. NAME DESCRIPTION

1 FB Feedback pin for current. Connect the sense resistor from FB to GND.

Output of the transconductance error amplifier. Connect an external

2 COMP

capacitor to this pin to compensate the regulator.

3 GND Ground.

This is the switching node of the IC. Connect the inductor between the

4 SW VIN and SW pin. This pin is also used to sense the output voltage for

open LED protection.

Control pin of the boost regulator. It is a pin which can be used for

5 CTRL

PWM digital dimming.

The input supply pin for the IC. Connect VIN to a supply voltage

6 VIN

between 2.7V and 5.5V.

Exposed pad should be soldered to PCB board and Connected to

7 GND

GND.

www.awinic.com.cn 2 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

FUNCTIONAL BLOCK DIAGRAM

1 2 6 4

FB COMP VIN SW

UVLO

- Thermal

Error OVP

Shutdown

Input Logic Reference Amp

and DAC Control +

PWM Control

5 Soft-Start

CTRL and

Gate Drive

Oscillator

Ramp Current

Generator + Amp

GND

GND

7 3

Figure 3 FUNCTIONAL BLOCK DIAGRAM

www.awinic.com.cn 3 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

TYPICAL APPLICATION CIRCUITS

L Schottky Diode

VIN

10μH *optional

* COUT2 D1

CIN1 CIN2 optional 6 4 COUT1

10μF 33pF/50V 1μF/50V

100nF VIN SW D2

D3

D4

AW9962DNR

ON/OFF 5 1 D5

CTRL FB

DIMMING CONTROL

2 RSET D6

COMP 10Ω

CCOMP GND D7

47nF

3,7

D8

D9

D10

20mA

Figure 4 Typical Application of AW9962

L Schottky Diode 3p6s

VIN

10μH

*optional *optional

CIN1 CIN2 6 4 COUT2 COUT1

10μF 100nF VIN SW 33pF/50V 1μF/50V

AW9962DNR

ON/OFF 5 1

CTRL FB

DIMMING CONTROL

2 RSET

COMP 3.3Ω

CCOMP GND 60mA

47nF

3,7

Figure 5 Drive 18 White LEDs for Large Screen Display

Notice for Typical Application Circuits:

1:Recommended device for AW9962:

L: LQH3NPN100NM0

CIN1: Murata GRM188R61C106MA73

CIN2: Murata GRM155R61C104K

COUT1: Murata GRM21BR71H105KA

www.awinic.com.cn 4 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

COUT2: Murata GRM1555C1H330GA

Schottky Diode: ONsemi MBR0540

2:CIN2 and COUT2 are recommended to use in parallel with the input capacitor and output capacitor to

suppress high frequency noise.

3:Red lines are high current paths, reference to the section APPLICATION INFORMATION.

4:The capacitors (CIN1, CIN2, COUT1, COUT2 and CCOMP) should be placed as close to the pins of the IC as

possible.

5:Minimize trace lengths between the IC and the inductor, the Schottky diode and the output capacitor, keep

these traces short, direct, and wide.

6:Minimize the length and area of all traces connected to the SW pin and always use a ground plane under

the switching regulator to minimize inter-plane coupling.

www.awinic.com.cn 5 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

ORDERING INFORMATION

Moisture

Environmental Delivery

Part Number Temperature Package Marking Sensitivity

Information Form

Level

3000 units/

AW9962DNR -40°C~85°C TDFN2x2-6L AL62 MSL1 ROHS+HF Tape and

Reel

AW9962

Shipping

R: Tape & Reel

Package Type

DN:DFN

Figure 6 Package Information

ABSOLUTE MAXIMUM RATINGS(NOTE1)

PARAMETERS RANGE

Supply voltage range VIN(NOTE 2) -0.3V to 6V

Voltage on FB,CTRL and COMP(NOTE 2) -0.3V to 6V

Voltage on SW (NOTE 2) -0.3V to 40V

Junction-to-ambient thermal resistance θJA 120°C /W

Operating free-air temperature range -40°C to 85°C

Operating Junction temperature TJ 40°C to 150°C

Storage temperature TSTG -65°C to 150°C

Lead Temperature (Soldering 10 Seconds) 260°C

ESD(NOTE 3)

ALL PINS HBM (human body model) (NOTE 4) ±6000V

ALL PINS CDM (charge device model) (NOTE 5) ±2000V

ALL PINS MM (machine model) (NOTE 6) ±300V

Latch-up(NOTE 7)

+IT:400mA

Latch-up current maximum rating per JEDEC standard

-IT:-400mA

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages

to the device. In spite of the limits above, functional operation conditions of the device should within the

ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for

prolonged periods may affect device reliability.

NOTE2: All voltage values are with respect to network ground terminal.

www.awinic.com.cn 6 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

NOTE3: This integrated circuit can be damaged by ESD if you don’t pay attention to ESD protection. AWINIC

recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper

handling and installation procedures can cause damage. ESD damage can range from subtle performance

degradation to complete device failure. Precision integrated circuits may be more susceptible to damage

because very small parametric changes could cause the device not to meet its published specifications.

NOTE4: The human body model is a 100pF capacitor discharged through a 1.5kΩ resistor into each pin. Test

method: MIL-STD-883H Method 3015.8.

NOTE5: Test Condition: JEDEC EIA/JESD22-C101E.

NOTE6: Test Condition: JEDEC EIA/JESD22-A115.

NOTE7: Test Condition: JEDEC STANDARD NO.78D NOVEMBER 2011.

www.awinic.com.cn 7 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

ELECTRICAL CHARACTERISTICS

Test Condition: TA = 25°C, VIN = 3.6V, VCTRL = VIN (Unless otherwise specified).

PARAMETER TEST CONDITION MIN TYP MAX UNIT

SUPPLY VOLTAGE AND CURRENT

VIN Input voltage range 2.7 5.5 V

VUVLO Under-voltage lockout threshold VIN falling 2.2 2.39 V

Under-voltage lockout

VHYS 100 mV

hysteresis

VCTRL = GND,

ISD Shutdown current 0.1 1 A

VIN=4.2V

IQ Operating quiescent current VFB = 1V 0.6 0.9 mA

PWM DIMMING CONTROL

fPWM Frequency of PWM dimming 10 100 kHz

DPWM PWM dimming duty cycle 0.3 100 %

tMIN_ON Minimum on pulse width 50 ns

VOLTAGE AND CURRENT CONTROL

Voltage feedback regulation

VREF 195 200 205 mV

voltage

Voltage feedback regulation PWM duty cycle = 1% 1.6 2 2.4 mV

VREF_PWM voltage under brightness

control PWM duty cycle = 0.3% 0.3 0.6 1.4 mV

Voltage feedback input bias

IFB 0.1 1 A

current

BOOST CONVERTER

N-channel MOSFET VIN = 3.6V 0.36 0.65 Ω

RDS(on)

on-resistance VIN = 3.0V 0.7 Ω

IL_NFET N-channel leakage current VSW = 35V, TA = 25℃ 1 A

fS Oscillator frequency 950 1100 1250 kHz

DMAX Maximum duty cycle 90 95 %

OCP AND OVP

N-channel MOSFET current

ILIM 1.5 2 2.5 A

limit

Open LED overvoltage Measured on the SW

VOVP 36 38 40 V

protection threshold pin

tREF VREF filter time constant 480 s

CTRL INTERFACE

VCTRL_H CTRL logic high voltage VIN = 2.7V to 5.5V 1.4 V

VCTRL_L CTRL logic low voltage VIN = 2.7V to 5.5V 0.4 V

RCTRL CTRL pull down resistor 300 600 700 kΩ

www.awinic.com.cn 8 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

PARAMETER TEST CONDITION MIN TYP MAX UNIT

tOFF CTRL pulse width to shutdown CTRL high to low 2.5 ms

THERMAL SHUTDOWN

TOTP Thermal shutdown threshold 165 °C

Thermal shutdown threshold

THYS 15 °C

hysteresis

www.awinic.com.cn 9 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

TYPICAL CHARACTERISTICS

Table 1 TABLE OF FIGURES

INDEX FIGURE No.

VIN=3.6V, 4,6,8,10 LEDs, FIGURE 7

Efficiency 1

L=10

VIN=4.2/3.6/3.0V, 10 LEDs, FIGURE 8

Efficiency 2

L=10

VIN=2.5~5.5V, 1P10S,

Efficiency 3 FIGURE 9

2P8S,3P6S LEDs, L=10

Switching frequency VIN=2.5~5.5V, 10 LEDs,

FIGURE 10

L=10

PWM dimming linearity PWM Freq = 20 kHz FIGURE 11

Feedback voltage line regulation VIN=2.5~5.5V FIGURE 12

Soft-start waveform VIN=3.6V, 10 LEDs, L=10 FIGURE 13

Switching waveform VIN=3.6V, 10 LEDs, L=10 FIGURE 14

Open LED protection VIN=3.6V, 10 LEDs, L=10 FIGURE 15

100 100

90 90

Efficiency (%)

Efficiency (%)

80 80

VIN=3.6V 70 2P10S

70

2P4S

2P6S VIN=3V

60 60

2P8S VIN=3.6V

2P10S VIN=4.2V

50 50

0 10 20 30 40 0 10 20 30 40

Output Current (mA) Output Current (mA)

Fig7. EFFICIENCY vs OUTPUT CURRENT Fig8. EFFICIENCY vs OUTPUT CURRENT

www.awinic.com.cn 10 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

100 1.3

90

1.2

Efficiency (%)

Frequency (MHz)

80

1.1

70 1P10S

2P8S

3P6S

60 1

2.5 3 3.5 4 4.5 5 5.5 2.5 3 3.5 4 4.5 5 5.5

Input Voltage (V) Input Voltage (V)

Fig9. EFFICIENCY vs INPUT VOLTAGE Fig10. FREQUENCY vs INPUT VOLTAGE

200 210

160 205

120 200

FB Voltage (mV)

FB Voltage (mV)

80 195

40 190

0 185

0 20 40 60 80 100 2.5 3 3.5 4 4.5 5 5.5

PWM Duty Cycle (%) Input Voltage (V)

Fig11. FB vs PWM DUTY CYCLE Fig12. FB vs INPUT VOLTAGE

IL

DC Coupled

CTRL 100mA/div

DC Coupled

1.0V/div

VOUT

DC Coupled

10.0V/div

VOUT

AC Coupled

IL

100mV/div

DC Coupled

200mA/div

Time (1μs/div)

Time (500μs/div)

Fig 14. SWITCHING WAVEFORM

Fig 13. SOFT-START WAVEFORM

www.awinic.com.cn 11 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

VOUT

DC Coupled

10.0V/div

SW

DC Coupled

10.0V/div

IL

DC Coupled

200mA/div

Time (200μs/div)

Fig15. OPEN LED PROTECTION

www.awinic.com.cn 12 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

DETAILED FUNCTIONAL DESCRIPTION

The AW9962 is a high efficiency, high output voltage boost converter in small package size. The device is

ideal for driving up to 10 white LED in series. The serial LED connection provides even illumination by

sourcing the same output current through all LEDs. The device integrates 40V/2.0A switch FET and operates

in pulse width modulation (PWM) with 1.1MHz fixed switching frequency. The duty cycle of the converter is

set by the error amplifier output and the current signal applied to the PWM control comparator. The control

architecture is based on traditional current-mode control. Therefore, slope compensation is added to the

current signal to allow stable operation for duty cycle larger than 50%. The feedback loop regulates the FB pin

to a low reference voltage (200mV typical), reducing the power dissipation in the current sense resistor.

SOFT START-UP

Soft-start circuitry is integrated into the IC to avoid a high inrush current during start-up. After the device is

enabled, the voltage at FB pin ramps up to the reference voltage. This ensures that the output voltage rises

slowly to reduce the input current.

OPEN LED OVER-VOLTAGE PROTECTION

Open LED over-voltage protection circuitry prevents IC damage as the result of white LED disconnection. The

AW9962 monitors the voltage at the SW pin during each switching cycle. The circuitry turns off the switch FET

as soon as the SW voltage exceeds the VOVP threshold for 8 clock cycles.

SHUTDOWN

The CTRL input is used to enable or disable the AW9962. Pulling the CTRL pin higher than 1.4V will enable

the device. The AW9962 has an internal shutdown delay circuitry, when the CTRL pin is held low for an

amount of time longer than 2.5ms, the AW9962 will enter shutdown mode and the input supply current for the

device is less than 1μA. Although the internal FET does not switch in shutdown, there is still a DC current path

between the input and the LEDs through the inductor and Schottky diode. The minimum forward voltage of

the LED array must exceed the maximum input voltage to ensure that the LEDs remain off in shutdown.

However, in the typical application with two or more LEDs, the forward voltage is large enough to reverse bias

the Schottky and keep leakage current low.

UNDER-VOLTAGE LOCKOUT

An under-voltage lockout prevents operation of the device at input voltage below typical 2.2V. When the input

voltage is below the under-voltage threshold, the internal switch FET is turned off. If the input voltage rises by

under-voltage lockout hysteresis, the IC restarts.

CURRENT PROGRAM

The FB voltage is regulated by a low 200mV reference voltage. The LED current is programmed externally

using a current sense resistor in series with the LED string. The value of the R SET can be calculated by the

following equation:

VFB

ILED = (1)

RSET

Where:

ILED = output current of LEDs

VFB = regulated voltage of FB

RSET = current sense resistor

www.awinic.com.cn 13 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

PWM BRIGHTNESS DIMMING

When the CTRL pin is constantly high, the FB voltage is regulated to 200mV typically. However, the CTRL pin

allows a PWM signal to reduce this regulation voltage, it achieves LED brightness dimming. The relationship

between the duty cycle and the FB voltage is given by the following equation:

VFB = Duty x 200mV (2)

Where:

Duty = duty cycle of the PWM signal

200mV = internal reference voltage

As shown in the FIGURE 16, the IC chops up the internal 200mV reference voltage at the duty cycle of the

PWM signal. The pulse signal is then filtered by an internal low pass filter. The output of the filter is connected

to the error amplifier as the reference voltage for the FB pin regulation. Therefore, although a PWM signal is

used for brightness dimming, only the WLED DC current is modulated, which is often referred as analog

dimming. This eliminates the audible noise which often occurs when the LED current is pulsed in replica of the

frequency and duty cycle of PWM control. Unlike other scheme which filters the PWM signal for analog

dimming, AW9962 regulation voltage is independent of the PWM logic voltage level which often has large

variations.

Reference

200mV

CTRL

Err or

Amplifier EA out

FB

Figure16 Block Diagram of Programmable FB Voltage Using PWM Signal

THERMAL SHUTDOWN

An internal thermal shutdown turns off the device when the typical junction temperature of is exceeded 165°C.

The device is released from shutdown automatically when the junction temperature decreases by 15°C.

www.awinic.com.cn 14 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

APPLICATION INFORMATION

MAXIMUM OUTPUT CURRENT

The over-current limit in a boost converter limits the maximum input current and thus maximum input power

for a given input voltage. Maximum output power is less than maximum input power due to power conversion

losses. The current limit setting, input voltage, output voltage and efficiency can all change maximum current

output. Therefore, the ripple has to be subtracted to derive maximum DC current. The ripple current is a

function of switching frequency, inductor value and duty cycle. The following equations take into account of all

the above factors for maximum output current calculation.

1

IP = (3)

1 1

L × Fs × ( + )

VOUT + VF - VIN VIN

Where:

IP = inductor peak to peak ripple

L= inductor value

VF = Schottky diode forward voltage

FS = switching frequency

VOUT = output voltage of the boost converter. It is equal to the sum of VFB and the voltage drop across

LEDs.

VIN (Ilim - IP / 2) η

Iout _ max (4)

VOUT

Where:

Iout_max = maximum output current of the boost converter

Ilim = over-current limit, for worst case calculation the minimum value has to be chosen.

η = efficiency

INDUCTOR SELECTION

The selection of the inductor affects steady state operation as well as transient behavior and loop stability.

These factors make it the most important component in power regulator design. There are three important

inductor specifications, inductor value, DC resistance and saturation current. Considering inductor value

alone is not enough.

The inductor value determines the inductor ripple current. Choose an inductor that can handle the necessary

peak current without saturating. The inductor DC current is given by:

VOUT Iout

IIN _ DC (5)

VIN η

Inductor values can have ±20% tolerance with no current bias. When the inductor current approaches

saturation level, its inductance can decrease 20% to 35% from the 0A value depending on how the inductor

vendor defines saturation current. Using an inductor with a smaller inductance value forces discontinuous

PWM when the inductor current ramps down to zero before the end of each switching cycle. This reduces the

boost converter’s maximum output current, causes large input voltage ripple and reduces efficiency. Large

inductance value provides much more output current and higher conversion efficiency. For these reasons, a

4.7μH to 10μH inductor value range is recommended. A 10μH inductor optimized the efficiency for most

www.awinic.com.cn 15 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

application while maintaining low inductor peak to peak ripple. TABLE 2 lists the recommended inductor for

the AW9962. When recommending inductor value, the factory has considered –40% and +20% tolerance

from its nominal value.

Table 2 Recommended Inductors for AW9962

Part L DCR Max Saturation Current Size

Vendor

Number (μH) (Ω) (mA) (L x W x H mm)

LQH3NPN100NM0 10 0.3 750 3 x 3 x 1.5 Murata

A997AS-220M 22 0.4 510 4 x 4 x 1.8 TOKO

CDH3809/SLD 10 0.3 570 4 x 4 x 1.0 Sumida

LPS4018-472ML 4.7 0.125 1900 4 x 4 x 1.8 Coilcraft

SCHOTTKY DIODE SELECTION

The high switching frequency of the AW9962 demands a high-speed rectification for optimum efficiency.

Ensure that the diode average and peak current rating exceeds the average output current and peak inductor

current. In addition, the diode’s reverse breakdown voltage must exceed the open LED over-voltage

protection voltage. The ONSemi MBR0540 and the ZETEX ZHCS400 are recommended for AW9962.

COMPENSATION CAPACITOR SELECTION

The compensation capacitor CCOMP (see the application circuit), connected from COMP pin to GND, is used to

stabilize the feedback loop of the AW9962. Use 47nF X5R or X7R ceramic capacitor for CCOMP.

For most applications, ceramic capacitors with X7R or X5R temperature characteristic are preferred for use

with the AW9962.

Capacitors with Y5V or Z5U temperature characteristic are generally not recommended for use with the

AW9962.

INPUT AND OUTPUT CAPACITOR SELECTION

The output capacitor is mainly selected to meet the requirements for the output ripple and loop stability. This

ripple voltage is related to the capacitor’s capacitance and its equivalent series resistance (ESR). Assuming a

capacitor with zero ESR, the minimum capacitance needed for a given ripple can be calculated by:

( VOUT - VIN ) Iout

COUT (6)

VOUT FS Vripple

Where, Vripple = peak-to-peak output ripple. The additional output ripple component caused by ESR is

calculated using:

Vripple _ ESR Iout RESR (7)

Due to its low ESR, Vripple_ESR can be neglected for ceramic capacitors, but must be considered if tantalum or

electrolytic capacitors are used.

Care must be taken when evaluating a ceramic capacitor’s derating under dc bias, aging and AC signal. For

example, larger form factor capacitors (in 1206 size) have a resonant frequency in the range of the switching

frequency. So the effective capacitance is significantly lower. The DC bias can also significantly reduce

capacitance. Ceramic capacitors can loss as much as 50% of its capacitance at its rated voltage. Therefore,

leave the margin on the voltage rating to ensure adequate capacitance at the required output voltage.

www.awinic.com.cn 16 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

An X5R or X7R capacitor of 10μF is recommended for input side. The output requires a X5R or X7R capacitor

in the range of 0.47μF to 4.7μF. A 100nF capacitor and a 33 pF capacitor are recommended to use in parallel

with the input capacitor and the output capacitor to suppress high frequency noise.

The output capacitor affects the loop stability of the boost regulator. If the output capacitor is below the range,

the boost regulator can potentially become unstable.

Note that capacitor degradation increases the ripple much. Select the capacitor with 50V rated voltage to

reduce the degradation at the output voltage. If the output ripple is too large, change a capacitor with less

degradation effect or with higher rated voltage could be helpful.

POWER DISSIPATION

The maximum IC junction temperature should be restricted to 125°C under normal operating conditions. This

restriction limits the power dissipation of the AW9962. Calculate the maximum allowable dissipation, PD(max),

and keep the actual dissipation less than or equal to P D(max). The maximum-power-dissipation limit is

determined by using the following equation:

TJ max - TA

PD(max)

θ ja

Where, TJmax is the Maximum Junction Temperature, TA is the maximum ambient temperature for the

application. θja is the thermal resistance junction-to-ambient given in Power Dissipation Table.

The AW9962 comes in a thermally enhanced TDFN package. Compared with the TSOT package, the TDFN

package has better heat dissipation. This package includes a thermal pad that improves the thermal

capabilities of the package. The θja of the TDFN package greatly depends on the PCB layout and thermal pad

connection. The thermal pad must be soldered directly to the analog ground on the PCB. After soldering, the

PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached

directly to the appropriate copper plane, or alternatively, can be attached to a special heatsink structure

designed into the PCB. This design optimizes the heat transfer from the integrated circuit(IC).

Using thermal vias underneath the thermal pad as illustrated in the layout example.

PCB LAYOUT CONSIDERATION

As for all switching power supplies, especially those high frequency and high current ones, layout is an

important design step. If layout is not carefully done, the regulator could suffer from instability as well as noise

problems. To reduce switching losses, the SW pin rise and fall times are made as short as possible. To

prevent radiation of high frequency resonance problems, proper layout of the high frequency switching path is

essential. Minimize the length and area of all traces connected to the SW pin and always use a ground plane

under the switching regulator to minimize inter-plane coupling. The loop including the PWM switch, Schottky

diode, and output capacitor, contains high current rising and falling in nanosecond and should be kept as

short as possible. The input capacitor needs not only to be close to the VIN pin, but also to the GND pin in

order to reduce the IC supply ripple.

Connect the exposed paddle to the PCB ground plane using at least two vias. The input and the output

bypass capacitors should be placed as close to the IC as possible. Minimize trace lengths between the IC and

the inductor, the diode and the output capacitor; keep these traces short, direct, and wide.

A recommended PCB Layout is shown in FIGURE 17. In order to dissipate the package heat, the package

thermal pad must be connected to a large copper area on the ground plane underneath using multiple vias.

www.awinic.com.cn 17 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

Figure 17 Recommended PCB Layout

www.awinic.com.cn 18 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

TAPE AND REEL INFORMATION

Carrier Tape

Pin 1 direction

Pin 1

User Direction of Feed

www.awinic.com.cn 19 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

Reel

PACKAGE DESCRIPTION

D K COMMON DIMENSIIONS

(UNITS OF MEASURE=MILLIMETER

LASER MARK 1 Symbol Min Typ Max

PIN 1 I.D. H A 0.80

0.70 0.75

A1 0.00 0.02 0.05

E E2

A3 0.20REF

e b 0.25 0.30 0.35

D2

b D 1.90 2.00 2.10

E 1.90 2.00 2.10

D2 0.90 1.00 1.10

TOP VIEW L E2 1.50 1.60 1.70

BOTTOM VIEW e 0.55 0.65 0.75

K 0.15 0.25 0.35

L 0.20 0.25 0.30

H 0.20REF

A

A1

A3

SIDE VIEW NOTES:

ALL DIMENSIONS REFER TO JEDEC STANDARD MO-229

DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

www.awinic.com.cn 20 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

LAND PATTERN DATA

NOTE A: All linear dimensions are in millimeters.

NOTE B: This drawing is subject to change without notice.

NOTE C: Publication IPC-7351 is recommended for alternate designs.

NOTE D: This land pattern is designed to be soldered to a thermal pad on the board.

NOTE E: Laser cutting aperture with trapezoidal walls and also rounding corners will offer better paste release.

Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525

for stencil design considerations.

NOTE F: Customers should contact their board fabrication site for solder mask tolerances.

www.awinic.com.cn 21 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

REFLOW

Package Reflow Oven Thermal Profile

Reflow Note Spec

Average ramp-up rate (217°C to Peak) Max. 3°C /sec

Time of Preheat temp.(from 150°C to 200°C) 60-120sec

Time to be maintained above 217°C 60-150sec

Peak Temperature >260°C

Time within 5°C of actual peak temp 20-40sec.

Ramp-down rate Max. 6°C /sec

Time from 25°C to peak temp Max. 8min.

www.awinic.com.cn 22 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

REVISION HISTORY

Vision Date Change Record

V1.0 June 2017 Datasheet V1.0 Released

1. Delete the Chinese introduction of the first page

2. Added MSL Level

V1.1 January 2018

3. Added Environmental Information

4. Added User Direction of Feed

5. Added minimum and maxim parameter in electrical characteristic

V1.2 June 2018 diagram

6. Changed Recommend PCB layout

V1.3 June 2018 7. Changed VOVP max to 40V in electrical characteristic diagram

www.awinic.com.cn 23 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW9962

Jun 2018 V1.3

DISCLAIMER

Information in this document is believed to be accurate and reliable. However, Shanghai AWINIC Technology

Co., Ltd (AWINIC Technology) does not give any representations or warranties, expressed or implied, as to

the accuracy or completeness of such information and shall have no liability for the consequences of use of

such information.

AWINIC Technology reserves the right to make changes to information published in this document, including

without limitation specifications and product descriptions, at any time and without notice. Customers shall

obtain the latest relevant information before placing orders and shall verify that such information is current and

complete. This document supersedes and replaces all information supplied prior to the publication hereof.

AWINIC Technology products are not designed, authorized or warranted to be suitable for use in medical,

military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an

AWINIC Technology product can reasonably be expected to result in personal injury, death or severe property

or environmental damage. AWINIC Technology accepts no liability for inclusion and/or use of AWINIC

Technology products in such equipment or applications and therefore such inclusion and/or use is at the

customer’s own risk.

Applications that are described herein for any of these products are for illustrative purposes only. AWINIC

Technology makes no representation or warranty that such applications will be suitable for the specified use

without further testing or modification.

All products are sold subject to the general terms and conditions of commercial sale supplied at the time of

order acknowledgement.

Nothing in this document may be interpreted or construed as an offer to sell products that is open for

acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other

industrial or intellectual property rights.

Reproduction of AWINIC information in AWINIC data books or data sheets is permissible only if reproduction

is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices.

AWINIC is not responsible or liable for such altered documentation. Information of third parties may be subject

to additional restrictions.

Resale of AWINIC components or services with statements different from or beyond the parameters stated by

AWINIC for that component or service voids all express and any implied warranties for the associated

AWINIC component or service and is an unfair and deceptive business practice. AWINIC is not responsible or

liable for any such statements.

www.awinic.com.cn 24 Copyright © 2017 SHANGHAI AWINIC TECHNOLOGY CO., LTD

You might also like

- Bit3260 PDFDocument1 pageBit3260 PDFSteven Orozco100% (1)

- How To Modify Guitar PedalsDocument25 pagesHow To Modify Guitar PedalsChristopher Karl100% (17)

- LT3932-3932-1-36V, 2A SynchronousDocument30 pagesLT3932-3932-1-36V, 2A Synchronousjustinvil1103No ratings yet

- AL8805 Description Pin Assignments: Not Recommended For New Design USE ORDocument18 pagesAL8805 Description Pin Assignments: Not Recommended For New Design USE ORlakshmananNo ratings yet

- 3 A, 2 MHZ Buck-Regulating Led Driver: Description Features and BenefitsDocument12 pages3 A, 2 MHZ Buck-Regulating Led Driver: Description Features and BenefitsElizabet VallejoNo ratings yet

- AL9910/ AL9910A/ AL9910-5/ AL9910A-5: Universal High Voltage High Brightness Led DriverDocument15 pagesAL9910/ AL9910A/ AL9910-5/ AL9910A-5: Universal High Voltage High Brightness Led DrivernareshNo ratings yet

- SC4541 Rev.2.1Document19 pagesSC4541 Rev.2.1Akhil GargNo ratings yet

- ZXLD1374: Thermal PadDocument39 pagesZXLD1374: Thermal PadAdrian WongNo ratings yet

- LP 8545Document46 pagesLP 8545NalsonNo ratings yet

- Bd81842muv M eDocument34 pagesBd81842muv M eSyeikh KeyderNo ratings yet

- Ic Dnp015 Block Ps4Document13 pagesIc Dnp015 Block Ps4Clément SaillantNo ratings yet

- WS3413 WinsemiDocument8 pagesWS3413 WinsemiCarlos ReisNo ratings yet

- Four-String, White LED Driver For LCD Backlight ApplicationsDocument20 pagesFour-String, White LED Driver For LCD Backlight ApplicationsRig ElectronicaNo ratings yet

- AL8862QDocument17 pagesAL8862QIvo MatosNo ratings yet

- AP3019ADocument12 pagesAP3019ARadu MititeluNo ratings yet

- AD52580B Audio AmplifierDocument3 pagesAD52580B Audio Amplifierhamada13No ratings yet

- Off-Line Quasi-Resonant Switching Regulators: STR-Y6763, STR-Y6765, and STR-Y6766Document13 pagesOff-Line Quasi-Resonant Switching Regulators: STR-Y6763, STR-Y6765, and STR-Y6766Renato Luther escalanteNo ratings yet

- Data Sheet: Beyond Innovation Technology Co., LTDDocument6 pagesData Sheet: Beyond Innovation Technology Co., LTDOlivier OuinaNo ratings yet

- MICRONE Nanjing Micro One Elec ME8204BM6G - C107691Document13 pagesMICRONE Nanjing Micro One Elec ME8204BM6G - C107691hichem_scribdNo ratings yet

- General Description Features: Fan Management ICDocument15 pagesGeneral Description Features: Fan Management ICIyon ManakarraNo ratings yet

- Current Mode PWM Controller: General DescriptionDocument12 pagesCurrent Mode PWM Controller: General DescriptionAlex GerasimenkoNo ratings yet

- DatasheetDocument14 pagesDatasheetsamaya egNo ratings yet

- Features: Lt1375/Lt1376 1.5A, 500Khz Step-Down Switching RegulatorsDocument29 pagesFeatures: Lt1375/Lt1376 1.5A, 500Khz Step-Down Switching RegulatorsSergio MuriloNo ratings yet

- (Top View) : High Performance Boost Led ControllerDocument15 pages(Top View) : High Performance Boost Led ControllerJavier Mendoza CastroNo ratings yet

- Features Description: LT3755/LT3755-1/LT3755-2 40V, 75V LED ControllersDocument28 pagesFeatures Description: LT3755/LT3755-1/LT3755-2 40V, 75V LED ControllersMick Thomson RcNo ratings yet

- MIC2182BM DatasheetzDocument28 pagesMIC2182BM DatasheetzAchilles BermudesNo ratings yet

- lt8356 1-2955993Document27 pageslt8356 1-2955993chawkigenieNo ratings yet

- Datasheet AP72200Document30 pagesDatasheet AP72200ecoplazabrNo ratings yet

- DP2269Document7 pagesDP2269GABRIEL AMORIM ARAUJONo ratings yet

- MT7842 MaxicTechnologyDocument6 pagesMT7842 MaxicTechnologyHeart of mountainNo ratings yet

- HDN-XX o YF3141-COTAG Sot-26 Sot23-6 DC-DCDocument11 pagesHDN-XX o YF3141-COTAG Sot-26 Sot23-6 DC-DCprreNo ratings yet

- Ω Ω Ω Ω Ω, 1.3A Power Switch with Programmable Current LimitDocument14 pagesΩ Ω Ω Ω Ω, 1.3A Power Switch with Programmable Current LimitSurendra SharmaNo ratings yet

- OB3372 On BrightDocument13 pagesOB3372 On BrightPedro Leandro SilvaNo ratings yet

- Lava DoraDocument13 pagesLava DoraRay Zander FebresNo ratings yet

- ZXLD1370Document39 pagesZXLD1370Iqbal Muzhaffar IsmailNo ratings yet

- AP3031Document13 pagesAP3031ALWHBANY Learn TermuxNo ratings yet

- FAN7602 Datasheet PDFDocument17 pagesFAN7602 Datasheet PDFSergio Daniel BarretoNo ratings yet

- BD94062FDocument35 pagesBD94062FMazalan HectorNo ratings yet

- Hysteretic Boost-Buck (Ćuk) LED Driver IC: Features General DescriptionDocument16 pagesHysteretic Boost-Buck (Ćuk) LED Driver IC: Features General DescriptionJohnNo ratings yet

- Acpl 337J 500eDocument18 pagesAcpl 337J 500eAandk NovaNo ratings yet

- OB2273 On BrightDocument12 pagesOB2273 On BrightCarlos PosadaNo ratings yet

- Features: Highly-Integrated Green-Mode PWM ControllerDocument15 pagesFeatures: Highly-Integrated Green-Mode PWM ControllerLester VernalNo ratings yet

- MP62550/MP62551: Precision 60mA-1.7A Programmable Current-Limited Power Distribution SwitchDocument16 pagesMP62550/MP62551: Precision 60mA-1.7A Programmable Current-Limited Power Distribution Switch이강학No ratings yet

- G5657 GlobalMixed ModetechnologyDocument1 pageG5657 GlobalMixed Modetechnologygava hoNo ratings yet

- Current Mode PWM Controller With Frequency Shuffling ME8202Document12 pagesCurrent Mode PWM Controller With Frequency Shuffling ME8202Kukla LossNo ratings yet

- AL3353Document15 pagesAL3353JonathanTaclindoNo ratings yet

- Description Features: Maximizing IC PerformanceDocument6 pagesDescription Features: Maximizing IC PerformanceHernan De OtoNo ratings yet

- SGM6014 SGMicroDocument16 pagesSGM6014 SGMicrowang seikeNo ratings yet

- AL8812Document11 pagesAL8812julio cesar calveteNo ratings yet

- Mp1022arev1 6Document4 pagesMp1022arev1 6juanNo ratings yet

- Dual-Phase DC-DC Controller For AMD Mobile CPU: Features General DescriptionDocument7 pagesDual-Phase DC-DC Controller For AMD Mobile CPU: Features General Descriptionlordycarlos8588No ratings yet

- FSQ100 Green Mode Fairchild Power Switch (FPS™) : Features DescriptionDocument13 pagesFSQ100 Green Mode Fairchild Power Switch (FPS™) : Features Descriptionايهاب فوزيNo ratings yet

- PAM8302A DatasheetDocument15 pagesPAM8302A DatasheetMarius NoybNo ratings yet

- DIO54302 High-Efficiency 3A, 28V Input Synchronous Step Down ConverterDocument11 pagesDIO54302 High-Efficiency 3A, 28V Input Synchronous Step Down ConverterAndrewNo ratings yet

- Data SheetDocument1 pageData Sheetcelestino secundinoNo ratings yet

- Bit 3260Document1 pageBit 3260Iader Salgado100% (1)

- AT1526 GlobalMixed ModetechnologyDocument2 pagesAT1526 GlobalMixed ModetechnologyFafa MangstabNo ratings yet

- STR5A460 Series Data Sheet: For Non-Isolated Off-Line PWM Controllers With Integrated Power MOSFETDocument32 pagesSTR5A460 Series Data Sheet: For Non-Isolated Off-Line PWM Controllers With Integrated Power MOSFETalanNo ratings yet

- Str-A6251 Str-A6252 PDFDocument7 pagesStr-A6251 Str-A6252 PDFrafalero1No ratings yet

- High-Speed Step-Down Controller: Features General DescriptionDocument1 pageHigh-Speed Step-Down Controller: Features General Descriptionedi purwantoNo ratings yet

- Diodo SS32 A 310Document2 pagesDiodo SS32 A 310Ramíro ChocotecóNo ratings yet

- Qualcomm® Snapdragon™ 600E Processor PDFDocument135 pagesQualcomm® Snapdragon™ 600E Processor PDFRamíro ChocotecóNo ratings yet

- SM-A260F Common Tshoo 7 PDFDocument24 pagesSM-A260F Common Tshoo 7 PDFRamíro ChocotecóNo ratings yet

- Safety Precautions: 1-1. Repair PrecautionDocument39 pagesSafety Precautions: 1-1. Repair PrecautionRamíro ChocotecóNo ratings yet

- Level 2 Repair: 7-1. Components On The Rear CaseDocument8 pagesLevel 2 Repair: 7-1. Components On The Rear CaseRamíro ChocotecóNo ratings yet

- C02e PDFDocument154 pagesC02e PDFAndrea BozziNo ratings yet

- Tpa3110d2 PDFDocument36 pagesTpa3110d2 PDFAndres AlegriaNo ratings yet

- MLCC Replacements For Tantalum CapacitorsDocument7 pagesMLCC Replacements For Tantalum CapacitorsIgor PNo ratings yet

- Decoupling2 WPDocument16 pagesDecoupling2 WPZarko RadivojevicNo ratings yet

- CMT2210LC en V0.9 20170817Document20 pagesCMT2210LC en V0.9 20170817Ta ToNo ratings yet

- Repartizare BOM - 2019Document9 pagesRepartizare BOM - 2019Andrei SerbanNo ratings yet

- Tas 5630 BDocument38 pagesTas 5630 BAlexsandro Roberto TeixeiraNo ratings yet

- Cap 220pF 2kVDocument12 pagesCap 220pF 2kVJoão Oliveira BentesNo ratings yet

- XBS444 Lista de Partes PDFDocument22 pagesXBS444 Lista de Partes PDFelita04No ratings yet

- Electronics Workbench Lab 6Document47 pagesElectronics Workbench Lab 6Imran ShaukatNo ratings yet

- Safety Standard Recognized, 900 Series, Radial Disc, Encapsulated, AC Type, X1 440 VAC/Y2 300 VAC (Industrial Grade)Document19 pagesSafety Standard Recognized, 900 Series, Radial Disc, Encapsulated, AC Type, X1 440 VAC/Y2 300 VAC (Industrial Grade)Luis OjedaNo ratings yet

- ANNEX. Exploded View & Part List (UN50KU630DFXZA DA01)Document12 pagesANNEX. Exploded View & Part List (UN50KU630DFXZA DA01)Jose AlbanNo ratings yet

- DatasheetDocument16 pagesDatasheetErick MauricioNo ratings yet

- Compal La-1452 r1c SchematicsDocument48 pagesCompal La-1452 r1c SchematicsgrandemeioNo ratings yet

- +VCCGT Vegas 15341Document8 pages+VCCGT Vegas 15341Eric ArcherNo ratings yet

- Energy StoredDocument6 pagesEnergy StoredMae chelle San AndresNo ratings yet

- Silergy Corp SY8009BABC - C79314Document9 pagesSilergy Corp SY8009BABC - C79314Miller CostaNo ratings yet

- Capacitor Usage (Umar., 2013)Document8 pagesCapacitor Usage (Umar., 2013)Umar SidikNo ratings yet

- Um2208 Getting Started With The Stevalisc003v1 Stusb4710 Evaluation Board Usb PD Controller With Onboard DCDC StmicroelectronicsDocument18 pagesUm2208 Getting Started With The Stevalisc003v1 Stusb4710 Evaluation Board Usb PD Controller With Onboard DCDC StmicroelectronicsJames SpadavecchiaNo ratings yet

- Eup3482aeup3482a PDFDocument11 pagesEup3482aeup3482a PDFfabloNo ratings yet

- Silergy-Corp-SY8286ARAC C178251Document16 pagesSilergy-Corp-SY8286ARAC C178251ziya tutuNo ratings yet

- General Description Features: EzbuckDocument9 pagesGeneral Description Features: EzbuckCristina NistorNo ratings yet

- Advantages of Replacement To A Chip Varistor and Selection PointsDocument16 pagesAdvantages of Replacement To A Chip Varistor and Selection PointsmanojkumarNo ratings yet

- Lenovo V130-15IKB Wistron LV315KB 17807 17807-1 17807-2 17807-3Document105 pagesLenovo V130-15IKB Wistron LV315KB 17807 17807-1 17807-2 17807-3Vefa Özdemir0% (1)

- Sailor 4000 VHFDocument148 pagesSailor 4000 VHFfolkep100% (1)

- AC/DC Medical Power Supply TPP 450B-M Series, 450 Watt: ModelsDocument6 pagesAC/DC Medical Power Supply TPP 450B-M Series, 450 Watt: Modelsal1 alloneNo ratings yet

- 1.intro & High Frequency Behavious of ComponentsDocument54 pages1.intro & High Frequency Behavious of Componentspravallika vysyarajuNo ratings yet

- Practical Papers, Articles and Application Notes: Robert G. Olsen, Technical EditorDocument20 pagesPractical Papers, Articles and Application Notes: Robert G. Olsen, Technical EditorAmir KhanNo ratings yet