Professional Documents

Culture Documents

Hardware Implementation of 8-Bit Adder/subtractor (Using Carry Look Ahead Adder)

Hardware Implementation of 8-Bit Adder/subtractor (Using Carry Look Ahead Adder)

Uploaded by

Nafi SiamOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Hardware Implementation of 8-Bit Adder/subtractor (Using Carry Look Ahead Adder)

Hardware Implementation of 8-Bit Adder/subtractor (Using Carry Look Ahead Adder)

Uploaded by

Nafi SiamCopyright:

Available Formats

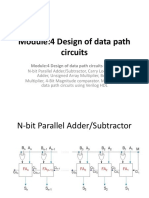

Hardware implementation of 8-bit adder/subtractor (using carry look ahead adder)

The purpose of using Verilog HDL is that it offers many features for hardware design. When the actual

addition is performed, there is no delay from waiting by using carry look-ahead adder. For any circuit

larger than 4-bit, the carry look-ahead adder, the circuit becomes very complicated. So 32-bit carry look-

ahead adder and subtracter will be constructed by combing 4-bit carry look-ahead adders.

The general strategy for designing fast adders is to reduce the time required to form carry signals. One

approach is to compute the input carry needed by stage i directly from carry like signals obtained from

all the preceding stages i-1,i-2,……0,rather than waiting for normal carries to ripple slowly from stages to

stages. Adders that use this principle are called carry look-ahead adders. An n-bit carry look-ahead adder

is formed from n stages , each of which is basically a full adder modified by replacing its carry output line

ci by two auxiliary signals called gi and pi or generate and propagate, respectively ,which are defined by

the following logic equation (1);

gi = xiyi pi = xi+yi ----------------(1)

The name generate comes from the fact that stage i generates a carry of 1(ci=1) independent of the

value of ci-1 if both xi and yi are 1; that is, if xiyi=1.Stage i propagates ci-1; that is makes ci=1 in response

to ci-1=1 if xi or yi is 1__in order words, if xi+yi=1.Now the usual equation ci=xiyi + xici-1 + yici-1,

denoting the carry signal ci to be sent to stage i+1, can be rewritten in terms of gi and pi.

ci =gi + pici-1--------------------- (2)

Similarly, ci-1 can be expressed in terms of gi-1, pi-1 and ci-2,

ci-1 = gi-1 + pi-1ci-2------------ (3)

On substituting Equation (3) into Equation (2),

ci =gi + pigi-1+pipi-1ci-2------- (4)

Continuing in this way, ci can be expressed as a sum-of-products function of the p and g outputs of all

the preceding stages. For example, the carries in a four-stage carry look-ahead adder are defined as

follows:

c0 = g0 + p0.cin

c1 = g1 + p1.g0 + p1.p0.cin

c2 = g2 + p2.g1 + p2.p1.g0 +p2.p1.p0.cin

c3 = g3 + p3.g2 + p3.p2.g1 + p3p2.p1.g0 + p3p2.p1.p0.cin--------- (5)

The components designed for 1-bit addition have been replaced with similar but larger components

intended for 4-bit addition. The expanded design of Fig. 1 can be got. Again 1-bit adders with 4-bit adder

are being replaced, but now each adder stage produces a propagate-generate signal pair pg instead of

cout and a carry look-ahead generator converts the four sets of pg signals to the carry inputs required by

the four stages. The “group” g and p signals produced by each 4-bit stage are defined by [3].

g = xiyi + xi-1 yi-1(xi+yi) + xi-2yi-2(xi + yi) (xi-1 + yi-1) + xi-3

yi-3(xi+yi) (xi-1 + yi-1) (xi-2 + yi-2)........... (6)

p = (xi +yi) (xi-1 + yi-1) (xi-2 +yi-2) (xi-3 + yi-3).......... (7),

For Example:

carry: 1111011

A: 11011001

B: 10101011

.............................

Output: 10000100

You might also like

- Cracked Addons2.2Document84 pagesCracked Addons2.2Erik Andreoni0% (1)

- Housing For Swine ProductionDocument87 pagesHousing For Swine ProductionMaria Leonora Theresa100% (3)

- Dayananda Sagar College of EngineeringDocument11 pagesDayananda Sagar College of EngineeringMrwhoistheboss OkNo ratings yet

- EC312 PS27 - SolutionsDocument3 pagesEC312 PS27 - SolutionsNafi SiamNo ratings yet

- What Is Ontological Relativity? - Paul ClareDocument11 pagesWhat Is Ontological Relativity? - Paul ClareJackEClareNo ratings yet

- Comparison Among Different AddersDocument6 pagesComparison Among Different AddersIOSRjournalNo ratings yet

- Lab10 RegularDocument12 pagesLab10 RegularTyron BiggumsNo ratings yet

- Systemverilog - Lecture 1Document62 pagesSystemverilog - Lecture 1Shilpa ReddyNo ratings yet

- 6.1 Addition and Subtraction of Signed Numbers:: Unit - 6 ArithmeticDocument48 pages6.1 Addition and Subtraction of Signed Numbers:: Unit - 6 ArithmeticTameem AhmedNo ratings yet

- Coa Unit 2 NotesDocument16 pagesCoa Unit 2 NotesHarshitha KANKANALANo ratings yet

- Com Bi National Logic CircuitDocument9 pagesCom Bi National Logic CircuitAsadul HoqueNo ratings yet

- Carry-Propagate AdderDocument6 pagesCarry-Propagate AddersaurabhNo ratings yet

- Parallel Prefix Adders PresentationDocument35 pagesParallel Prefix Adders PresentationYermakov Vadim IvanovichNo ratings yet

- VLSI - Carry Lookahead AdderDocument12 pagesVLSI - Carry Lookahead AdderK.R.RaguramNo ratings yet

- 4-Bit Carry Look Ahead AdderDocument5 pages4-Bit Carry Look Ahead AdderluqmansulymanNo ratings yet

- ALUDocument21 pagesALUprathabapandianNo ratings yet

- 02 SystemVerilogLecture1Document31 pages02 SystemVerilogLecture1Mihaela ScanteianuNo ratings yet

- Logic Design With MSI Circuits: 1. Binary Adder - SubtractorDocument10 pagesLogic Design With MSI Circuits: 1. Binary Adder - SubtractorBalaji PalanisamyNo ratings yet

- Adders + Subtractors PDFDocument9 pagesAdders + Subtractors PDFSambit PatraNo ratings yet

- COA Module - 4Document43 pagesCOA Module - 4shashidh1234No ratings yet

- Efficient VLSI Implementation of Modulo Addition and MultiplicationDocument10 pagesEfficient VLSI Implementation of Modulo Addition and Multiplicationvka_princeNo ratings yet

- As 00001030Document32 pagesAs 00001030Akshat soniNo ratings yet

- Unit-Iv Adders:: Binary Adder Notations and OperationsDocument33 pagesUnit-Iv Adders:: Binary Adder Notations and OperationsRene DevNo ratings yet

- Vlsi Implementation of High Speed Adders in Fpga-SaranyaDocument5 pagesVlsi Implementation of High Speed Adders in Fpga-SaranyaSARANYA,Mba2021 Vel Tech, ChennaiNo ratings yet

- Unit2 Arithmetics 120411093803 Phpapp01Document79 pagesUnit2 Arithmetics 120411093803 Phpapp01Vani BalamuraliNo ratings yet

- DDCA Ch5Document101 pagesDDCA Ch5Dheer MehrotraNo ratings yet

- CLA: Carry Look Ahead AdderDocument3 pagesCLA: Carry Look Ahead AdderAmit GuptaNo ratings yet

- Final Note Arithmetic VtuDocument30 pagesFinal Note Arithmetic VtuadddataNo ratings yet

- Ripple Carry and Carry Lookahead Addition and Subtraction CircuitsDocument19 pagesRipple Carry and Carry Lookahead Addition and Subtraction CircuitsSurya KanthNo ratings yet

- Chapter 4Document45 pagesChapter 4Mohammad Ahmed ChoudhryNo ratings yet

- Design of Parallel Prefix Adders PDFDocument5 pagesDesign of Parallel Prefix Adders PDFKavyashreeMNo ratings yet

- Introduction To VLSI Circuits and SystemsDocument31 pagesIntroduction To VLSI Circuits and SystemsraviNo ratings yet

- Combinational CircuitsDocument68 pagesCombinational Circuitsavita207No ratings yet

- Co-Unit 6Document19 pagesCo-Unit 6Priyanka H VNo ratings yet

- ArithmeticDocument43 pagesArithmeticzatharoxNo ratings yet

- EEE 270 Advanced Topics in Logic Design: Read Before ClassDocument35 pagesEEE 270 Advanced Topics in Logic Design: Read Before ClassPraveen MeduriNo ratings yet

- ADVD T2 2009-2010 Answer KeyDocument5 pagesADVD T2 2009-2010 Answer KeyAnimesh ChoudharyNo ratings yet

- Module 4 PDFDocument25 pagesModule 4 PDFRoopa NNo ratings yet

- Basic Digital Logic Design Notes PDFDocument138 pagesBasic Digital Logic Design Notes PDFnandams100% (1)

- Nov/Dec 2008 CS1354 Answer Key B.E / B.Tech Degree Examination Nov/Dec 2008 R 3261 CS1354 Computer Graphics and Multimedia Part ADocument10 pagesNov/Dec 2008 CS1354 Answer Key B.E / B.Tech Degree Examination Nov/Dec 2008 R 3261 CS1354 Computer Graphics and Multimedia Part AgspriyadarshiniNo ratings yet

- Experiment No-9: Starter Kit (DSK)Document10 pagesExperiment No-9: Starter Kit (DSK)Mayank Sardana100% (1)

- Badass Tutorial Unit 6 Adders SubtractorsDocument23 pagesBadass Tutorial Unit 6 Adders SubtractorsdjpsychoscientzNo ratings yet

- ARITHMETIC and LOGIC UNIT - in This Lecture, We Will Examine HowDocument12 pagesARITHMETIC and LOGIC UNIT - in This Lecture, We Will Examine HowbokadashNo ratings yet

- What's The Deal?: Two-Operand AdditionDocument28 pagesWhat's The Deal?: Two-Operand AdditionFatiLilyNo ratings yet

- VHDL Cheat Sheet Exam 1Document3 pagesVHDL Cheat Sheet Exam 1Kevin Wilczak100% (1)

- Logic DesignCh05Document92 pagesLogic DesignCh05Akshay Nagar100% (1)

- 09-Addition MultiplicationDocument27 pages09-Addition MultiplicationJbanfulNo ratings yet

- Carry-Lookahead & Carry-Select Adders: ECE 645: Lecture 4Document12 pagesCarry-Lookahead & Carry-Select Adders: ECE 645: Lecture 4balu2103No ratings yet

- Basic Digital Logic Design NotesDocument138 pagesBasic Digital Logic Design NotesSagar AgarwalNo ratings yet

- EEE 241 Chap 04Document74 pagesEEE 241 Chap 04Husnain GhaffarNo ratings yet

- Lecture 5-6-7Document23 pagesLecture 5-6-7Aditya AgarwalNo ratings yet

- Unit 2Document38 pagesUnit 2toshgangwarNo ratings yet

- Lecture #9Document15 pagesLecture #9Teshome GirmaNo ratings yet

- Module:4 Design of Data Path Circuits 6 HoursDocument44 pagesModule:4 Design of Data Path Circuits 6 HoursSahana MecheriNo ratings yet

- Comb CircDocument63 pagesComb Circm.sangeethjaNo ratings yet

- Addition / Subtraction: Parts Chapters IDocument103 pagesAddition / Subtraction: Parts Chapters ITooba Sami ArifeenNo ratings yet

- P05-Digital Systems - Lecture - 17-20Document46 pagesP05-Digital Systems - Lecture - 17-20JAINo ratings yet

- Computer Graphics Lab (CSP-305) Worksheet-2Document5 pagesComputer Graphics Lab (CSP-305) Worksheet-2Samridh GargNo ratings yet

- Module 4Document19 pagesModule 4Amruta KhangaonkarNo ratings yet

- Note5 DigitalDocument63 pagesNote5 DigitalChintala Thrinadh 21BEE1006No ratings yet

- Inverse Trigonometric Functions (Trigonometry) Mathematics Question BankFrom EverandInverse Trigonometric Functions (Trigonometry) Mathematics Question BankNo ratings yet

- Ten-Decimal Tables of the Logarithms of Complex Numbers and for the Transformation from Cartesian to Polar Coordinates: Volume 33 in Mathematical Tables SeriesFrom EverandTen-Decimal Tables of the Logarithms of Complex Numbers and for the Transformation from Cartesian to Polar Coordinates: Volume 33 in Mathematical Tables SeriesNo ratings yet

- LED Matrix: Md. Fahim Bhuiyan, Nazmus Sakib, Mohammad Rejwan Uddin, and Khosru M SalimDocument6 pagesLED Matrix: Md. Fahim Bhuiyan, Nazmus Sakib, Mohammad Rejwan Uddin, and Khosru M SalimNafi SiamNo ratings yet

- Cis Project Presentation On Inventory Management System (Ims)Document19 pagesCis Project Presentation On Inventory Management System (Ims)Nafi SiamNo ratings yet

- Room For Rent: 1 February FacilitiesDocument1 pageRoom For Rent: 1 February FacilitiesNafi SiamNo ratings yet

- S D B A: Emiconductor Iodes IN Asic PplicationsDocument9 pagesS D B A: Emiconductor Iodes IN Asic PplicationsNafi SiamNo ratings yet

- JavaDocument3 pagesJavaNafi SiamNo ratings yet

- Team Members: Saila Ishrat Annei, Zaima Tasneem, Rokeya Mumtahana Mou, Ayesha Siddiqua JyotiDocument1 pageTeam Members: Saila Ishrat Annei, Zaima Tasneem, Rokeya Mumtahana Mou, Ayesha Siddiqua JyotiNafi SiamNo ratings yet

- Course Outline CSE214 Summer2019Document6 pagesCourse Outline CSE214 Summer2019Nafi SiamNo ratings yet

- Bangladesh Railway e TicketDocument1 pageBangladesh Railway e TicketNafi SiamNo ratings yet

- Assignment Instruction EHDocument2 pagesAssignment Instruction EHNafi SiamNo ratings yet

- Airbnb MilestoneDocument1 pageAirbnb MilestoneNafi SiamNo ratings yet

- A3 - CSE307Sec02Summer2020 - 1631256 - MD. NAFIU IBNE MAZHAR SIAMDocument7 pagesA3 - CSE307Sec02Summer2020 - 1631256 - MD. NAFIU IBNE MAZHAR SIAMNafi SiamNo ratings yet

- Worksheet10 1Document7 pagesWorksheet10 1Nafi SiamNo ratings yet

- SystemsAnalysisAndDesign PDFDocument64 pagesSystemsAnalysisAndDesign PDFNafi SiamNo ratings yet

- K-Means Clustering and Related Algorithms: Ryan P. AdamsDocument16 pagesK-Means Clustering and Related Algorithms: Ryan P. AdamsNafi SiamNo ratings yet

- To Be Entity Relationship DiagramDocument1 pageTo Be Entity Relationship DiagramNafi SiamNo ratings yet

- Homework PDFDocument4 pagesHomework PDFNafi SiamNo ratings yet

- What Is PlasticDocument12 pagesWhat Is PlasticNafi SiamNo ratings yet

- In 1907 Leo Baekeland Invented BakeliteDocument1 pageIn 1907 Leo Baekeland Invented BakeliteNafi SiamNo ratings yet

- Design of A Whole Sale Inventory Management System Using UmlDocument7 pagesDesign of A Whole Sale Inventory Management System Using UmlNafi SiamNo ratings yet

- Course ID: CSE-303 Course Title: Database Management Section: 03 Assignment 1Document17 pagesCourse ID: CSE-303 Course Title: Database Management Section: 03 Assignment 1Nafi SiamNo ratings yet

- Multicore Processor Technology-Advantages and Challenges: Anil Sethi, Himanshu KushwahDocument3 pagesMulticore Processor Technology-Advantages and Challenges: Anil Sethi, Himanshu KushwahNafi SiamNo ratings yet

- To Be Entity Relationship DiagramDocument1 pageTo Be Entity Relationship DiagramNafi SiamNo ratings yet

- Milestone - 2 - MediaProductionHouse - (Noor Shila Haider - 1620473 - Sec3) - & - (MD Nafiu Ibne Mazhar - 1631256 - Sec1)Document4 pagesMilestone - 2 - MediaProductionHouse - (Noor Shila Haider - 1620473 - Sec3) - & - (MD Nafiu Ibne Mazhar - 1631256 - Sec1)Nafi SiamNo ratings yet

- Project 4Document6 pagesProject 4Trai TranNo ratings yet

- Pola Seismic Code CommentaryDocument15 pagesPola Seismic Code Commentary_ARCUL_100% (1)

- TarangMini ST13SMxxDocument1 pageTarangMini ST13SMxxPrasad ChabbiNo ratings yet

- Golden Power ATF DEX III TDSDocument1 pageGolden Power ATF DEX III TDSsimon.clove034No ratings yet

- Z:/windchill/codebase Z:/windchill/codebaseDocument3 pagesZ:/windchill/codebase Z:/windchill/codebaseamalNo ratings yet

- Astm D2414-21Document9 pagesAstm D2414-21Rajdeep MalNo ratings yet

- Q400 - 12. PropellersDocument14 pagesQ400 - 12. PropellersDavid Owen100% (1)

- Edited - GROUP GAMES - COURSE SYLLABUS 1st Sem AY2023 2024Document7 pagesEdited - GROUP GAMES - COURSE SYLLABUS 1st Sem AY2023 2024B09 Kurt Benedict HillNo ratings yet

- Nethravathi River - Water Supply Scheme in DakshinDocument8 pagesNethravathi River - Water Supply Scheme in DakshinMitria WidianingtiasNo ratings yet

- Book Order FormDocument2 pagesBook Order Formbinaya BehuraNo ratings yet

- Petroleum Geomechanics Assignment 3Document6 pagesPetroleum Geomechanics Assignment 3Binish KhanNo ratings yet

- 2012 KCSE Physics Paper 3Document5 pages2012 KCSE Physics Paper 3lixus mwangiNo ratings yet

- Strategic Marketing 10th Edition Cravens Test BankDocument9 pagesStrategic Marketing 10th Edition Cravens Test Bankdanielxavia55fok100% (17)

- BS 410Document22 pagesBS 410RajaKuppan100% (2)

- A Study On Marketing Strategies of LIC Agents With Special Reference To Branches in Madurai DivisionDocument14 pagesA Study On Marketing Strategies of LIC Agents With Special Reference To Branches in Madurai DivisionAjanta BearingNo ratings yet

- WhitePaper AVEVA PredictiveAnalyticsPower 22-04Document6 pagesWhitePaper AVEVA PredictiveAnalyticsPower 22-04matiasnNo ratings yet

- Andrew GroveDocument16 pagesAndrew GroveArslanNo ratings yet

- Brochure Bb3102 Eva Pur-C Pur-NDocument2 pagesBrochure Bb3102 Eva Pur-C Pur-NĐinh ThuậnNo ratings yet

- Cot Eng6q3Document6 pagesCot Eng6q3Arlyn Borbe BordeosNo ratings yet

- Syllabus PDFDocument51 pagesSyllabus PDFPalashNo ratings yet

- How Does The Jigsaw Technique Work?Document9 pagesHow Does The Jigsaw Technique Work?Italo Aarón Milla LozanoNo ratings yet

- ECILDocument21 pagesECILpip_lokare350% (1)

- WPS - 016Document11 pagesWPS - 016MAT-LIONNo ratings yet

- TenderdocumentDocument53 pagesTenderdocumentBalaji AssociatesNo ratings yet

- Green Façades: Marwa Hisham Salem El-ZoklahDocument16 pagesGreen Façades: Marwa Hisham Salem El-ZoklahEphremZelekeNo ratings yet

- Astm F467MDocument9 pagesAstm F467Mhouk sukNo ratings yet