Professional Documents

Culture Documents

0 ratings0% found this document useful (0 votes)

22 viewsECE/EEE F311 Communication Systems - Laboratory. Lab Report: Steps Observation: Step S Observation

ECE/EEE F311 Communication Systems - Laboratory. Lab Report: Steps Observation: Step S Observation

Uploaded by

Mohit DhayalThis lab report summarizes experiments on analog to digital and digital to analog conversion using nonlinear PCM encoding schemes. Key steps include:

1) Implementing circuits to convert analog sine waves to digital using an 8-bit ADC and recover the analog signal using an 8-bit DAC.

2) Exploring the A-law and μ-law compression techniques to encode analog signals digitally and reconstruct the original signal.

3) Observing the input and output signals at different stages of the quantization and encoding process on oscilloscope plots.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You might also like

- Microsoft: Exam Questions DP-203Document17 pagesMicrosoft: Exam Questions DP-203dfdsa100% (1)

- College Management SystemDocument117 pagesCollege Management Systemashishthecool90% (10)

- EMH - Full Rev1 With ToC PDFDocument269 pagesEMH - Full Rev1 With ToC PDFnenon2006No ratings yet

- PSK Lab ManualDocument4 pagesPSK Lab ManualSakshi DewadeNo ratings yet

- Biomedical Instrumentation Lab 1Document95 pagesBiomedical Instrumentation Lab 1EmirDefa50% (2)

- DC Manual FinalDocument42 pagesDC Manual FinalsrvsbondNo ratings yet

- DCLabDocument31 pagesDCLabani rohiraNo ratings yet

- Me 365 Experiment 2 Introduction To Digital Data Acquisition ObjectivesDocument13 pagesMe 365 Experiment 2 Introduction To Digital Data Acquisition ObjectivesSenthil KumarNo ratings yet

- Digital StethoscopeDocument4 pagesDigital StethoscopeDhaval ShahNo ratings yet

- Manual Flow Comp 405ADocument43 pagesManual Flow Comp 405ADeden TarsomaNo ratings yet

- Lab Design and Analysis of Active CS and Cascode AmplifierDocument3 pagesLab Design and Analysis of Active CS and Cascode AmplifierAzure HereNo ratings yet

- New DC Lab ManualDocument53 pagesNew DC Lab Manualsriram128No ratings yet

- Table of Content: Digital OhmmeterDocument23 pagesTable of Content: Digital OhmmeterLow Koon Yee100% (1)

- Digital Communications Lab: List of ExperimentsDocument50 pagesDigital Communications Lab: List of ExperimentsNeel SarkarNo ratings yet

- Cad For Electronics Lab Kec-653Document59 pagesCad For Electronics Lab Kec-653Aviral VarshneyNo ratings yet

- Communication II Lab (EELE 4170)Document6 pagesCommunication II Lab (EELE 4170)Fahim MunawarNo ratings yet

- PCM (1)Document6 pagesPCM (1)M OdehNo ratings yet

- Design of A Comparator in A 0.25 M CMOS Technology.: Block Diagram of The Beetle ChipDocument5 pagesDesign of A Comparator in A 0.25 M CMOS Technology.: Block Diagram of The Beetle ChipankurkanodiaNo ratings yet

- CS EXPERIMENT 11 01012021 095140am 18012021 012709amDocument13 pagesCS EXPERIMENT 11 01012021 095140am 18012021 012709amAsif AliNo ratings yet

- Lab BookDocument70 pagesLab Bookअमरेश झाNo ratings yet

- Experiment Manual For PCM ModulatorDocument6 pagesExperiment Manual For PCM Modulatorrajivsharma1610100% (1)

- EXP 9 - Pulse Code Modulation & DemodulationDocument5 pagesEXP 9 - Pulse Code Modulation & DemodulationsasankflyNo ratings yet

- Elec4505 Exp0Document7 pagesElec4505 Exp0muafhanNo ratings yet

- A/D and D/A Conversion Testing: V G 2 V VDocument7 pagesA/D and D/A Conversion Testing: V G 2 V VRichard NewbyNo ratings yet

- L4 EaDocument7 pagesL4 EaIoanaNicoletaNo ratings yet

- CN Lab ManualDocument29 pagesCN Lab ManualDominicPNo ratings yet

- Communication LabDocument34 pagesCommunication LabSingam DonNo ratings yet

- AnalogDocument16 pagesAnalogchandushar1604No ratings yet

- DSP GateDocument5 pagesDSP Gatebodige123No ratings yet

- Interfacing A Servo To The Atmega16: 7 "#&0F99"007F +&9%G5 " 3.?& :30& H&0 F ". 0&I3 &) "& "& %J&Document7 pagesInterfacing A Servo To The Atmega16: 7 "#&0F99"007F +&9%G5 " 3.?& :30& H&0 F ". 0&I3 &) "& "& %J&Gaurang 'TottaPhilic' GuptaNo ratings yet

- Lecture 7Document33 pagesLecture 7Youssef AshrafNo ratings yet

- DC Lab ManualDocument49 pagesDC Lab ManualSnigdha SidduNo ratings yet

- Adaptive Delta ModulationDocument15 pagesAdaptive Delta ModulationVinita DahiyaNo ratings yet

- Exp 8Document7 pagesExp 8growthman.100No ratings yet

- ECNG 3016 Advanced Digital Electronics: Eneral NformationDocument10 pagesECNG 3016 Advanced Digital Electronics: Eneral NformationMarlon BoucaudNo ratings yet

- Experiment02 PCM-EncodingDocument13 pagesExperiment02 PCM-EncodingMary Rose P Delos SantosNo ratings yet

- PCM Tta BatchDocument84 pagesPCM Tta BatchGourav RoyNo ratings yet

- ADE - Pspice Lab ManualDocument12 pagesADE - Pspice Lab ManualShashiNo ratings yet

- Comm Lab Exp7Document2 pagesComm Lab Exp7Carlin MendozaNo ratings yet

- Mbed BK Ed2 CH 5Document20 pagesMbed BK Ed2 CH 5NecNo ratings yet

- International Islamic University Islamabad: Communication Systems LabDocument4 pagesInternational Islamic University Islamabad: Communication Systems LabkashafNo ratings yet

- Flash ADC Design in ElectricDocument22 pagesFlash ADC Design in ElectricNagaraj HegdeNo ratings yet

- Basics of InvertersDocument12 pagesBasics of InvertersTatenda BizureNo ratings yet

- Communication Systems Ii - LabmanualDocument12 pagesCommunication Systems Ii - LabmanualpramodNo ratings yet

- PCM Lab ManualDocument5 pagesPCM Lab ManualSakshi DewadeNo ratings yet

- Clap CounterDocument4 pagesClap CounterVivek jhaNo ratings yet

- M4 Micro OneNoteDocument6 pagesM4 Micro OneNoteAryan RaiNo ratings yet

- ADEL Lab ManualDocument44 pagesADEL Lab ManualRehan KitturNo ratings yet

- National Institute of Technology, Rourkela: Embedded Systems LaboratoryDocument13 pagesNational Institute of Technology, Rourkela: Embedded Systems Laboratoryprateekkumardash2002No ratings yet

- Home Work No 13Document3 pagesHome Work No 13VamshiKrishna100% (1)

- Berkes - Interfacing Exp ArrangementDocument20 pagesBerkes - Interfacing Exp ArrangementAditya K NNo ratings yet

- Design of The Sine Wave Generating Circuit Based On The Atmega128A MicrocontrollerDocument5 pagesDesign of The Sine Wave Generating Circuit Based On The Atmega128A MicrocontrollerhamidNo ratings yet

- PCMDocument11 pagesPCMAmit KurudNo ratings yet

- Sensors and ActuatorsDocument31 pagesSensors and ActuatorsDhiraj MahajanNo ratings yet

- Electronic Circuit Analysis PSPICEDocument13 pagesElectronic Circuit Analysis PSPICEUmera AnjumNo ratings yet

- Ofc Lab Manual 2Document21 pagesOfc Lab Manual 2Shobhit JainNo ratings yet

- Analog and Digital Electronics Lab Manual (17CSL37) : Department of Computer Science and EngineeringDocument61 pagesAnalog and Digital Electronics Lab Manual (17CSL37) : Department of Computer Science and Engineeringvadla77No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Here Is The Complete Circuit of The DREAM 6800 Minus The Power SupplyDocument1 pageHere Is The Complete Circuit of The DREAM 6800 Minus The Power SupplyHernan BenitesNo ratings yet

- The Influence of Shared Mental Models On Team Process and PerformanceDocument11 pagesThe Influence of Shared Mental Models On Team Process and PerformanceFiorela JulianNo ratings yet

- 6-Schedule E (231-242)Document14 pages6-Schedule E (231-242)Baskaran GangatharanNo ratings yet

- Role of Cyber Law in Cyber Security in IndiaDocument4 pagesRole of Cyber Law in Cyber Security in IndiaHJ ManviNo ratings yet

- Which of The Following Is Not A Characteristic of An EntrepreneurDocument2 pagesWhich of The Following Is Not A Characteristic of An EntrepreneurbrianmongeNo ratings yet

- TmaDocument3 pagesTmaSteveAbonyiNo ratings yet

- Robot Specifications - Robot ProgrammingDocument54 pagesRobot Specifications - Robot ProgrammingPriyanshu NainNo ratings yet

- Classification of Distribution Systems: Classification According To The Nature of The CurrentDocument7 pagesClassification of Distribution Systems: Classification According To The Nature of The CurrentSew KariyawasamNo ratings yet

- Exam Unit 1 Out and About 1º BachilleratoDocument5 pagesExam Unit 1 Out and About 1º Bachilleratolisikratis1980No ratings yet

- Arnav Kapur Fact Sheet PDF (Lemelson Mit)Document3 pagesArnav Kapur Fact Sheet PDF (Lemelson Mit)Edward NewgateNo ratings yet

- Internet Programming - Elective - KSDocument4 pagesInternet Programming - Elective - KSSrinivasan KrishnanNo ratings yet

- UNIT 4 FILE AND CLASSIFICATION OF DOCUMENTS PendienteDocument13 pagesUNIT 4 FILE AND CLASSIFICATION OF DOCUMENTS PendienteDavid RuizNo ratings yet

- ANSI Device Numbers PDFDocument1 pageANSI Device Numbers PDFPutra Kusuma HarditoNo ratings yet

- Supply Chain Management: Fedex: Delivering The GoodsDocument29 pagesSupply Chain Management: Fedex: Delivering The Goodslucy01123No ratings yet

- S820 CNC Plasma Cutting Machine-CompressedDocument106 pagesS820 CNC Plasma Cutting Machine-CompressedNguyen Quyet Thang100% (2)

- Zinc Air Batteries AdvantagesDocument2 pagesZinc Air Batteries AdvantagesCegasaMotionEnergyNo ratings yet

- SOP - Kiln Stopping ProcedureDocument2 pagesSOP - Kiln Stopping ProcedureJCS100% (1)

- Testo 735 Instruction ManualDocument28 pagesTesto 735 Instruction Manualmatheus ramosNo ratings yet

- Chapter 1Document15 pagesChapter 1kelzoiNo ratings yet

- Case Study SkanskaDocument4 pagesCase Study SkanskaRogger Guillermo FloresNo ratings yet

- Toshiba Portege Z30 C Z12 WebDocument2 pagesToshiba Portege Z30 C Z12 WebUsman KhanNo ratings yet

- R 505 0128 Dismantling and Assembling Plant or Machinery Components To Replace Worn Damaged or Faulty Parts in The WorkplaceDocument4 pagesR 505 0128 Dismantling and Assembling Plant or Machinery Components To Replace Worn Damaged or Faulty Parts in The WorkplaceGiang LamNo ratings yet

- TPE2 (D), TPE3 (D) : Safety Instructions and Other Important InformationDocument14 pagesTPE2 (D), TPE3 (D) : Safety Instructions and Other Important Informationhvacr061No ratings yet

- HILTI Catalogue 2012Document314 pagesHILTI Catalogue 2012Marius RizeaNo ratings yet

- Generations of Programming LanguagesDocument2 pagesGenerations of Programming LanguagesEmmanuel OlorunsholaNo ratings yet

- AutoMate 552 Install ManualDocument42 pagesAutoMate 552 Install ManualNathan MossorNo ratings yet

- Katalog Luxon & Zeron 2020 + All in One SL - NSSDocument90 pagesKatalog Luxon & Zeron 2020 + All in One SL - NSSBOCAH MAH BEBASNo ratings yet

ECE/EEE F311 Communication Systems - Laboratory. Lab Report: Steps Observation: Step S Observation

ECE/EEE F311 Communication Systems - Laboratory. Lab Report: Steps Observation: Step S Observation

Uploaded by

Mohit Dhayal0 ratings0% found this document useful (0 votes)

22 views12 pagesThis lab report summarizes experiments on analog to digital and digital to analog conversion using nonlinear PCM encoding schemes. Key steps include:

1) Implementing circuits to convert analog sine waves to digital using an 8-bit ADC and recover the analog signal using an 8-bit DAC.

2) Exploring the A-law and μ-law compression techniques to encode analog signals digitally and reconstruct the original signal.

3) Observing the input and output signals at different stages of the quantization and encoding process on oscilloscope plots.

Original Description:

Expt 6 lab

Original Title

Expt 6

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis lab report summarizes experiments on analog to digital and digital to analog conversion using nonlinear PCM encoding schemes. Key steps include:

1) Implementing circuits to convert analog sine waves to digital using an 8-bit ADC and recover the analog signal using an 8-bit DAC.

2) Exploring the A-law and μ-law compression techniques to encode analog signals digitally and reconstruct the original signal.

3) Observing the input and output signals at different stages of the quantization and encoding process on oscilloscope plots.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

22 views12 pagesECE/EEE F311 Communication Systems - Laboratory. Lab Report: Steps Observation: Step S Observation

ECE/EEE F311 Communication Systems - Laboratory. Lab Report: Steps Observation: Step S Observation

Uploaded by

Mohit DhayalThis lab report summarizes experiments on analog to digital and digital to analog conversion using nonlinear PCM encoding schemes. Key steps include:

1) Implementing circuits to convert analog sine waves to digital using an 8-bit ADC and recover the analog signal using an 8-bit DAC.

2) Exploring the A-law and μ-law compression techniques to encode analog signals digitally and reconstruct the original signal.

3) Observing the input and output signals at different stages of the quantization and encoding process on oscilloscope plots.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 12

ECE/EEE F311 Communication Systems –

Laboratory.

Lab report

ID No 2018A3PS0474G Name: Mohit

Experiment started on: 29/09/2020

Completed on: 08/10/2020 Expt #: 6

Name of the expt.: A to D and D to A conversion, Non-Linear PCM

Steps Observation:

Step Observation

s

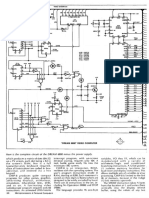

A1 Implement the circuit given below

Parameters for the

three sine waves are

1V at 500Hz,

1/3V at 1500Hz,

1/5V at 2500Hz

Set pulse at 1V and 10% duty cycle for pulse generator.

Set the simulation rate at 8 kHz, and set runtime for simulation as 5 msec.

A2 Set the ‘Uniform Encoder’ with the peak of 1.3V and 8-bits per sample

and Output Type as Signed Integer.

For the ‘To Workshop’ block, rename it as ‘simout’ and set to limit points to

last 100.

A3 Go the MATLAB Workshop window, and double click on simout icon, and

observe the following table.

A4 The signal to be quantised is as follows

Graph for impulse samples is given below

The output of Sample & Hold block is given below

The quantized signal is given below,

The output for quantisation error is

The output for the Encoded signal is,

The output for Encoded signal in bits is as follows,

B1 Implement the following circuit

B2 In A-Law Compressor, set ‘Peak signal Magnitude’ as

1V, Ramp signal varies between ± 1V, starting at 0V,

at t=0

Set the simulation sample time as 1 msec , and run the simulation for 2 sec.

B3 Output for the Ramp is as follows,,

When the graph of A-compressor vs ramp input is plotted,

After passing through the A-Law compressor, the output comes out as

follows,

After passing through A-Law Expander, the output is as follows,

C1 Implement the 8-bit PCM system as given below

Parameters for input sine wave

Amplitude = 1 V

Frequency = 300 Hz

And for the Low Pass Filter

Set filter order = 8, edge frequency = 350 Hz

C2 Implement the 8-bit ADC as follows,

For Pulse Generator,

Amplitude = 1V, Period=1/8000, and 50% duty cycle.

For Uniform Encoder

Peak=1.3, bits=8

For Integer to Bit Converter, number of bits per integer=8, treat input as

‘unsigned’.

For Repeating Sequence Stair specs,

Vector of output value=[1 2 3 4 5 6 7 8]

Sample time = 1/64000

Multiport Switch, Number of data ports

=8 Implement the 8-bit DAC, as shown in

figure,

Clock (Pulse Generator) specs,

Amplitude = 1V, Period= 1/64000, 50% duty cycle

DAC o/p sampled specs

Amplitude =1V, Period= 1/8000, 50% duty cycle.

C3 Set the stop time as 0.025 secs and run the simulation.

The following graph is input sine wave, with 1V as amplitude and

300Hz frequency.

The output of DAC is

The Mu-law graph comes out as

And the final recovered signal is given below

Name: Mohit

Date: 08/10/2020

You might also like

- Microsoft: Exam Questions DP-203Document17 pagesMicrosoft: Exam Questions DP-203dfdsa100% (1)

- College Management SystemDocument117 pagesCollege Management Systemashishthecool90% (10)

- EMH - Full Rev1 With ToC PDFDocument269 pagesEMH - Full Rev1 With ToC PDFnenon2006No ratings yet

- PSK Lab ManualDocument4 pagesPSK Lab ManualSakshi DewadeNo ratings yet

- Biomedical Instrumentation Lab 1Document95 pagesBiomedical Instrumentation Lab 1EmirDefa50% (2)

- DC Manual FinalDocument42 pagesDC Manual FinalsrvsbondNo ratings yet

- DCLabDocument31 pagesDCLabani rohiraNo ratings yet

- Me 365 Experiment 2 Introduction To Digital Data Acquisition ObjectivesDocument13 pagesMe 365 Experiment 2 Introduction To Digital Data Acquisition ObjectivesSenthil KumarNo ratings yet

- Digital StethoscopeDocument4 pagesDigital StethoscopeDhaval ShahNo ratings yet

- Manual Flow Comp 405ADocument43 pagesManual Flow Comp 405ADeden TarsomaNo ratings yet

- Lab Design and Analysis of Active CS and Cascode AmplifierDocument3 pagesLab Design and Analysis of Active CS and Cascode AmplifierAzure HereNo ratings yet

- New DC Lab ManualDocument53 pagesNew DC Lab Manualsriram128No ratings yet

- Table of Content: Digital OhmmeterDocument23 pagesTable of Content: Digital OhmmeterLow Koon Yee100% (1)

- Digital Communications Lab: List of ExperimentsDocument50 pagesDigital Communications Lab: List of ExperimentsNeel SarkarNo ratings yet

- Cad For Electronics Lab Kec-653Document59 pagesCad For Electronics Lab Kec-653Aviral VarshneyNo ratings yet

- Communication II Lab (EELE 4170)Document6 pagesCommunication II Lab (EELE 4170)Fahim MunawarNo ratings yet

- PCM (1)Document6 pagesPCM (1)M OdehNo ratings yet

- Design of A Comparator in A 0.25 M CMOS Technology.: Block Diagram of The Beetle ChipDocument5 pagesDesign of A Comparator in A 0.25 M CMOS Technology.: Block Diagram of The Beetle ChipankurkanodiaNo ratings yet

- CS EXPERIMENT 11 01012021 095140am 18012021 012709amDocument13 pagesCS EXPERIMENT 11 01012021 095140am 18012021 012709amAsif AliNo ratings yet

- Lab BookDocument70 pagesLab Bookअमरेश झाNo ratings yet

- Experiment Manual For PCM ModulatorDocument6 pagesExperiment Manual For PCM Modulatorrajivsharma1610100% (1)

- EXP 9 - Pulse Code Modulation & DemodulationDocument5 pagesEXP 9 - Pulse Code Modulation & DemodulationsasankflyNo ratings yet

- Elec4505 Exp0Document7 pagesElec4505 Exp0muafhanNo ratings yet

- A/D and D/A Conversion Testing: V G 2 V VDocument7 pagesA/D and D/A Conversion Testing: V G 2 V VRichard NewbyNo ratings yet

- L4 EaDocument7 pagesL4 EaIoanaNicoletaNo ratings yet

- CN Lab ManualDocument29 pagesCN Lab ManualDominicPNo ratings yet

- Communication LabDocument34 pagesCommunication LabSingam DonNo ratings yet

- AnalogDocument16 pagesAnalogchandushar1604No ratings yet

- DSP GateDocument5 pagesDSP Gatebodige123No ratings yet

- Interfacing A Servo To The Atmega16: 7 "#&0F99"007F +&9%G5 " 3.?& :30& H&0 F ". 0&I3 &) "& "& %J&Document7 pagesInterfacing A Servo To The Atmega16: 7 "#&0F99"007F +&9%G5 " 3.?& :30& H&0 F ". 0&I3 &) "& "& %J&Gaurang 'TottaPhilic' GuptaNo ratings yet

- Lecture 7Document33 pagesLecture 7Youssef AshrafNo ratings yet

- DC Lab ManualDocument49 pagesDC Lab ManualSnigdha SidduNo ratings yet

- Adaptive Delta ModulationDocument15 pagesAdaptive Delta ModulationVinita DahiyaNo ratings yet

- Exp 8Document7 pagesExp 8growthman.100No ratings yet

- ECNG 3016 Advanced Digital Electronics: Eneral NformationDocument10 pagesECNG 3016 Advanced Digital Electronics: Eneral NformationMarlon BoucaudNo ratings yet

- Experiment02 PCM-EncodingDocument13 pagesExperiment02 PCM-EncodingMary Rose P Delos SantosNo ratings yet

- PCM Tta BatchDocument84 pagesPCM Tta BatchGourav RoyNo ratings yet

- ADE - Pspice Lab ManualDocument12 pagesADE - Pspice Lab ManualShashiNo ratings yet

- Comm Lab Exp7Document2 pagesComm Lab Exp7Carlin MendozaNo ratings yet

- Mbed BK Ed2 CH 5Document20 pagesMbed BK Ed2 CH 5NecNo ratings yet

- International Islamic University Islamabad: Communication Systems LabDocument4 pagesInternational Islamic University Islamabad: Communication Systems LabkashafNo ratings yet

- Flash ADC Design in ElectricDocument22 pagesFlash ADC Design in ElectricNagaraj HegdeNo ratings yet

- Basics of InvertersDocument12 pagesBasics of InvertersTatenda BizureNo ratings yet

- Communication Systems Ii - LabmanualDocument12 pagesCommunication Systems Ii - LabmanualpramodNo ratings yet

- PCM Lab ManualDocument5 pagesPCM Lab ManualSakshi DewadeNo ratings yet

- Clap CounterDocument4 pagesClap CounterVivek jhaNo ratings yet

- M4 Micro OneNoteDocument6 pagesM4 Micro OneNoteAryan RaiNo ratings yet

- ADEL Lab ManualDocument44 pagesADEL Lab ManualRehan KitturNo ratings yet

- National Institute of Technology, Rourkela: Embedded Systems LaboratoryDocument13 pagesNational Institute of Technology, Rourkela: Embedded Systems Laboratoryprateekkumardash2002No ratings yet

- Home Work No 13Document3 pagesHome Work No 13VamshiKrishna100% (1)

- Berkes - Interfacing Exp ArrangementDocument20 pagesBerkes - Interfacing Exp ArrangementAditya K NNo ratings yet

- Design of The Sine Wave Generating Circuit Based On The Atmega128A MicrocontrollerDocument5 pagesDesign of The Sine Wave Generating Circuit Based On The Atmega128A MicrocontrollerhamidNo ratings yet

- PCMDocument11 pagesPCMAmit KurudNo ratings yet

- Sensors and ActuatorsDocument31 pagesSensors and ActuatorsDhiraj MahajanNo ratings yet

- Electronic Circuit Analysis PSPICEDocument13 pagesElectronic Circuit Analysis PSPICEUmera AnjumNo ratings yet

- Ofc Lab Manual 2Document21 pagesOfc Lab Manual 2Shobhit JainNo ratings yet

- Analog and Digital Electronics Lab Manual (17CSL37) : Department of Computer Science and EngineeringDocument61 pagesAnalog and Digital Electronics Lab Manual (17CSL37) : Department of Computer Science and Engineeringvadla77No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Here Is The Complete Circuit of The DREAM 6800 Minus The Power SupplyDocument1 pageHere Is The Complete Circuit of The DREAM 6800 Minus The Power SupplyHernan BenitesNo ratings yet

- The Influence of Shared Mental Models On Team Process and PerformanceDocument11 pagesThe Influence of Shared Mental Models On Team Process and PerformanceFiorela JulianNo ratings yet

- 6-Schedule E (231-242)Document14 pages6-Schedule E (231-242)Baskaran GangatharanNo ratings yet

- Role of Cyber Law in Cyber Security in IndiaDocument4 pagesRole of Cyber Law in Cyber Security in IndiaHJ ManviNo ratings yet

- Which of The Following Is Not A Characteristic of An EntrepreneurDocument2 pagesWhich of The Following Is Not A Characteristic of An EntrepreneurbrianmongeNo ratings yet

- TmaDocument3 pagesTmaSteveAbonyiNo ratings yet

- Robot Specifications - Robot ProgrammingDocument54 pagesRobot Specifications - Robot ProgrammingPriyanshu NainNo ratings yet

- Classification of Distribution Systems: Classification According To The Nature of The CurrentDocument7 pagesClassification of Distribution Systems: Classification According To The Nature of The CurrentSew KariyawasamNo ratings yet

- Exam Unit 1 Out and About 1º BachilleratoDocument5 pagesExam Unit 1 Out and About 1º Bachilleratolisikratis1980No ratings yet

- Arnav Kapur Fact Sheet PDF (Lemelson Mit)Document3 pagesArnav Kapur Fact Sheet PDF (Lemelson Mit)Edward NewgateNo ratings yet

- Internet Programming - Elective - KSDocument4 pagesInternet Programming - Elective - KSSrinivasan KrishnanNo ratings yet

- UNIT 4 FILE AND CLASSIFICATION OF DOCUMENTS PendienteDocument13 pagesUNIT 4 FILE AND CLASSIFICATION OF DOCUMENTS PendienteDavid RuizNo ratings yet

- ANSI Device Numbers PDFDocument1 pageANSI Device Numbers PDFPutra Kusuma HarditoNo ratings yet

- Supply Chain Management: Fedex: Delivering The GoodsDocument29 pagesSupply Chain Management: Fedex: Delivering The Goodslucy01123No ratings yet

- S820 CNC Plasma Cutting Machine-CompressedDocument106 pagesS820 CNC Plasma Cutting Machine-CompressedNguyen Quyet Thang100% (2)

- Zinc Air Batteries AdvantagesDocument2 pagesZinc Air Batteries AdvantagesCegasaMotionEnergyNo ratings yet

- SOP - Kiln Stopping ProcedureDocument2 pagesSOP - Kiln Stopping ProcedureJCS100% (1)

- Testo 735 Instruction ManualDocument28 pagesTesto 735 Instruction Manualmatheus ramosNo ratings yet

- Chapter 1Document15 pagesChapter 1kelzoiNo ratings yet

- Case Study SkanskaDocument4 pagesCase Study SkanskaRogger Guillermo FloresNo ratings yet

- Toshiba Portege Z30 C Z12 WebDocument2 pagesToshiba Portege Z30 C Z12 WebUsman KhanNo ratings yet

- R 505 0128 Dismantling and Assembling Plant or Machinery Components To Replace Worn Damaged or Faulty Parts in The WorkplaceDocument4 pagesR 505 0128 Dismantling and Assembling Plant or Machinery Components To Replace Worn Damaged or Faulty Parts in The WorkplaceGiang LamNo ratings yet

- TPE2 (D), TPE3 (D) : Safety Instructions and Other Important InformationDocument14 pagesTPE2 (D), TPE3 (D) : Safety Instructions and Other Important Informationhvacr061No ratings yet

- HILTI Catalogue 2012Document314 pagesHILTI Catalogue 2012Marius RizeaNo ratings yet

- Generations of Programming LanguagesDocument2 pagesGenerations of Programming LanguagesEmmanuel OlorunsholaNo ratings yet

- AutoMate 552 Install ManualDocument42 pagesAutoMate 552 Install ManualNathan MossorNo ratings yet

- Katalog Luxon & Zeron 2020 + All in One SL - NSSDocument90 pagesKatalog Luxon & Zeron 2020 + All in One SL - NSSBOCAH MAH BEBASNo ratings yet