Professional Documents

Culture Documents

Accelerometer SPI Mode

Accelerometer SPI Mode

Uploaded by

BraulioGonzalezPalaciosCopyright:

Available Formats

You might also like

- Docu67723 VNX Operating Environment For Block 05.33.009.5.184 and For File 8.1.9.184, and Unisphere 1.3.9.1.184 Release NotesDocument105 pagesDocu67723 VNX Operating Environment For Block 05.33.009.5.184 and For File 8.1.9.184, and Unisphere 1.3.9.1.184 Release NotesafjeieNo ratings yet

- Rodrigo Trevino Resume EnglishDocument3 pagesRodrigo Trevino Resume EnglishRodrigo HasidNo ratings yet

- Accelerometer SPI ModeDocument6 pagesAccelerometer SPI ModecointoinNo ratings yet

- Accelerometer SPI ModeDocument6 pagesAccelerometer SPI ModecointoinNo ratings yet

- Chapter 4 Microprocessor SystemDocument71 pagesChapter 4 Microprocessor SystemGetTrendingNo ratings yet

- Microprocessor and Micro Controller Lecture NotesDocument118 pagesMicroprocessor and Micro Controller Lecture NotesSivanesh SK50% (2)

- 8-Bit Microcontroller With 2K Bytes of In-System Programmable Flash AT90S2313Document92 pages8-Bit Microcontroller With 2K Bytes of In-System Programmable Flash AT90S2313nullsoft69No ratings yet

- WWW Sparkfun Com Tutorials 240Document14 pagesWWW Sparkfun Com Tutorials 240ramnag4No ratings yet

- At Tiny 13Document146 pagesAt Tiny 13Hasri AwalNo ratings yet

- Internal Architecture of 8085 Microprocessor: A. Control UnitDocument17 pagesInternal Architecture of 8085 Microprocessor: A. Control Unitmech mech1No ratings yet

- M4 Yash AllabadiDocument6 pagesM4 Yash Allabadidegijon661No ratings yet

- Practical 1 Dyna KitDocument5 pagesPractical 1 Dyna KitHet PatelNo ratings yet

- MCT Unit 2Document26 pagesMCT Unit 2Aravind RajNo ratings yet

- 8085 MaterialDocument12 pages8085 MaterialsameerNo ratings yet

- Notes Unit 1Document25 pagesNotes Unit 1Ashish YadavNo ratings yet

- Laboratory Exercise 10: An Enhanced ProcessorDocument4 pagesLaboratory Exercise 10: An Enhanced ProcessorKhánh ConNo ratings yet

- Microprocessor NotesDocument21 pagesMicroprocessor NotesAdhithyaNo ratings yet

- 8-Bit Microcontroller With 4K Bytes In-System Programmable Flash AT90S4414 PreliminaryDocument10 pages8-Bit Microcontroller With 4K Bytes In-System Programmable Flash AT90S4414 PreliminaryYerson CrespoNo ratings yet

- Chapter 4 Microprocessor SystemDocument50 pagesChapter 4 Microprocessor SystemRajkishor YadavNo ratings yet

- An Introduction To INTEL 8085 Microprocessor: By:Ravindra Nadh.V, Assistant Professor, GST, BangaloreDocument35 pagesAn Introduction To INTEL 8085 Microprocessor: By:Ravindra Nadh.V, Assistant Professor, GST, BangaloreVasudev Rao KonjetiNo ratings yet

- Micro Hihihi HDocument4 pagesMicro Hihihi HbrycheezyNo ratings yet

- Lec 03 Internal Micro ArchitectureDocument24 pagesLec 03 Internal Micro ArchitecturePaarth JamwalNo ratings yet

- 8085 Architecture: Control UnitDocument10 pages8085 Architecture: Control UnitsweetmemoriesneverdiNo ratings yet

- 8 Bit Microprocessor Using VHDL: Pallavi Deshmane, Maithili Lad & Pooja Mhetre Sharan KumarDocument6 pages8 Bit Microprocessor Using VHDL: Pallavi Deshmane, Maithili Lad & Pooja Mhetre Sharan KumarshubhamNo ratings yet

- Unit Ii 8085 Micro Processor 8085 Architecture:: ME 6702 Mechatronics Mechanical Engineering 2019-20Document26 pagesUnit Ii 8085 Micro Processor 8085 Architecture:: ME 6702 Mechatronics Mechanical Engineering 2019-20GopinathNo ratings yet

- Speed Detector For HighwaysDocument29 pagesSpeed Detector For HighwaysShama MahinNo ratings yet

- Snug04 Bromley Smith PaperDocument16 pagesSnug04 Bromley Smith PaperDheeraj SinglaNo ratings yet

- Tutorial: Subject Code: 2150707 Subject Name: Microprocessor & InterfacingDocument6 pagesTutorial: Subject Code: 2150707 Subject Name: Microprocessor & InterfacingShaili PalejkarNo ratings yet

- Microprocessor and Micro ControllerDocument118 pagesMicroprocessor and Micro ControllerShiva ShanNo ratings yet

- Question With Answer MP & MCDocument13 pagesQuestion With Answer MP & MCMATHANKUMAR.SNo ratings yet

- ARM Core Data Flow Model and 3 Stage PipeliningDocument42 pagesARM Core Data Flow Model and 3 Stage Pipeliningjkumarmtech22No ratings yet

- 1-Architecture of 8085Document34 pages1-Architecture of 8085Pinki KumariNo ratings yet

- Architecture 8085Document46 pagesArchitecture 8085milf hunterNo ratings yet

- Microprocessor Lab ManualDocument85 pagesMicroprocessor Lab ManualReddyNo ratings yet

- FPGA Altera DE2 RS232 PDFDocument5 pagesFPGA Altera DE2 RS232 PDFidiot930902No ratings yet

- MPDocument34 pagesMPAbhinandan JainNo ratings yet

- MPMC Model Exam Answer KeyDocument21 pagesMPMC Model Exam Answer KeyVenkatesan SundaramNo ratings yet

- Microprocessor 8085 ArchitectureDocument19 pagesMicroprocessor 8085 ArchitectureSindhujaSindhuNo ratings yet

- Experiment No. 1: Department of Electronics & Comm - EnggDocument7 pagesExperiment No. 1: Department of Electronics & Comm - EnggJaspreet KaurNo ratings yet

- Microprocessor Basics and Related TermsDocument27 pagesMicroprocessor Basics and Related TermsJai Sai RamNo ratings yet

- Ee8551 8085 NotesDocument31 pagesEe8551 8085 NotesKUMARANSCRNo ratings yet

- Microprocessors and Microcontrollers NotesDocument293 pagesMicroprocessors and Microcontrollers NotesKumar ChaitanyaNo ratings yet

- Advanced RISC Machine-ARM Notes BhurchandiDocument8 pagesAdvanced RISC Machine-ARM Notes BhurchandiVipin TiwariNo ratings yet

- 19 MSP1056 MicroprocessorDocument9 pages19 MSP1056 Microprocessorsakshi sharmaNo ratings yet

- 8085 MicroprocessorDocument13 pages8085 MicroprocessorSajid Akram100% (1)

- CH 3Document8 pagesCH 3Parth ThakkarNo ratings yet

- ESD Manual StudentsDocument55 pagesESD Manual StudentsNimesh PrajapatiNo ratings yet

- 8085 ppt 1Document17 pages8085 ppt 1usgaonkard10No ratings yet

- ANS Computer Awareness Year 1Document4 pagesANS Computer Awareness Year 1virad25No ratings yet

- 04 AVR ALU and SREG SetDocument12 pages04 AVR ALU and SREG SetDerbendeNo ratings yet

- Intel 8085 Architecture: AccumulatorDocument6 pagesIntel 8085 Architecture: AccumulatorDipesh YadavNo ratings yet

- 8085 ArchitectureDocument17 pages8085 ArchitectureSamaira Shahnoor ParvinNo ratings yet

- Microprocessor Lecture Notes 1 10Document202 pagesMicroprocessor Lecture Notes 1 10Ambarish SinghNo ratings yet

- Microprocessor Lecture 1Document4 pagesMicroprocessor Lecture 1rspahlobNo ratings yet

- MICROPORCESSOR 8085 Lab ManualDocument53 pagesMICROPORCESSOR 8085 Lab ManualAjay PatilNo ratings yet

- Data SheetDocument211 pagesData SheetYana PrikitiwNo ratings yet

- 8085 Microprocessor Architecture, Pin DiagramDocument10 pages8085 Microprocessor Architecture, Pin DiagramSachin Jaysenan0% (1)

- Microprocessors - II: Yashar HajiyevDocument62 pagesMicroprocessors - II: Yashar HajiyevMurad QəhramanovNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Business Intelligence ImplementationDocument88 pagesBusiness Intelligence ImplementationFabiyi Olawale100% (1)

- CTS-AutomotiveServiceTech310S L1 MP EN PDFDocument59 pagesCTS-AutomotiveServiceTech310S L1 MP EN PDFDoDuyBacNo ratings yet

- Protection of Multimedia Works Under: Research SynopsisDocument7 pagesProtection of Multimedia Works Under: Research SynopsisAvtar singhNo ratings yet

- How Did Semiconductors Change Our LivesDocument4 pagesHow Did Semiconductors Change Our Livesmunnayadav555No ratings yet

- Problem Reduction: - AND-OR Graph - AO SearchDocument31 pagesProblem Reduction: - AND-OR Graph - AO Searchmiriyala nagendraNo ratings yet

- IEEE Xplore - The Evolution of Robotics ResearchDocument1 pageIEEE Xplore - The Evolution of Robotics ResearchManu Sathish NairNo ratings yet

- Enrollment Form 3Document1 pageEnrollment Form 3حيدرالركابيNo ratings yet

- Ebook - Top Angel Investors PDFDocument49 pagesEbook - Top Angel Investors PDFPankaj GourNo ratings yet

- Cam Module 5 RomDocument28 pagesCam Module 5 Romnamitha rNo ratings yet

- Siebel Systems Case Analysis: Group 10 - Section BDocument7 pagesSiebel Systems Case Analysis: Group 10 - Section BAmit RajNo ratings yet

- M09 Access & Use InterDocument85 pagesM09 Access & Use Interbeye asheNo ratings yet

- DD Project Book StudentDocument40 pagesDD Project Book StudentLord_nNo ratings yet

- Scanprint IMS enDocument8 pagesScanprint IMS enMarios DomoxoudisNo ratings yet

- BcdinfoDocument3 pagesBcdinforegeniusNo ratings yet

- Excel Cash BookDocument16 pagesExcel Cash BookzeeshanNo ratings yet

- 969c4824-5909-4c92-b584-7db17876a664Document6 pages969c4824-5909-4c92-b584-7db17876a664Swamy Dhas DhasNo ratings yet

- Assignment 1: COMPUTER (CCM10802) Parts of Computer SystemDocument7 pagesAssignment 1: COMPUTER (CCM10802) Parts of Computer Systemangelerryshaforever100% (1)

- PCT M1 FlowDocument2 pagesPCT M1 FlowRms VicNo ratings yet

- SOF Sample Paper Class 3Document8 pagesSOF Sample Paper Class 3govimano100% (1)

- Clean LogDocument2 pagesClean LogAji MauLanaNo ratings yet

- ComProg Module - M5 FinalDocument6 pagesComProg Module - M5 FinalLEO JR GREFALDONo ratings yet

- How To Move Sepm From One Server To Another ServerDocument4 pagesHow To Move Sepm From One Server To Another ServerNan Win AungNo ratings yet

- Solution Manual For Avr Microcontroller and Embedded Systems Using Assembly and C Muhammad Ali Mazidi Sarmad Naimi Sepehr NaimiDocument37 pagesSolution Manual For Avr Microcontroller and Embedded Systems Using Assembly and C Muhammad Ali Mazidi Sarmad Naimi Sepehr Naimidespendcaduke80ux100% (20)

- User Manual For New Firmware of The 3/3.5-Inch Color Screen: Date: April 2013Document63 pagesUser Manual For New Firmware of The 3/3.5-Inch Color Screen: Date: April 2013Denny De Leon LaurencioNo ratings yet

- المكتبات الذكية 2Document28 pagesالمكتبات الذكية 2malik 1992No ratings yet

- Teaching NLTK NorwegianDocument68 pagesTeaching NLTK NorwegianRamesh AkulaNo ratings yet

- DTMF Based Speed Control of DC Motor PDFDocument3 pagesDTMF Based Speed Control of DC Motor PDFInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Standard Colour Cable CodeDocument1 pageStandard Colour Cable CodeVerli AndreansyahNo ratings yet

Accelerometer SPI Mode

Accelerometer SPI Mode

Uploaded by

BraulioGonzalezPalaciosOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Accelerometer SPI Mode

Accelerometer SPI Mode

Uploaded by

BraulioGonzalezPalaciosCopyright:

Available Formats

Accelerometer SPI Mode Core

for DE-Series Boards

For Quartus II 14.0

This document describes the Altera University Program’s IP core that can be used to access the accelerometer

peripheral found on Altera’s DE0-Nano and VEEK-MT boards.

1 Accelerometer Chip

The accelerometer peripheral consists of the Analog Devices’ ADXL345 chip. It measures acceleration in three

directions, which are referred to as x -axis, y -axis and z -axis. When stationary, the only acceleration experienced by

the chip is due to gravity. The measured results have 13-bit resolution in the range up to ±16 g .

The accelerometer chip includes a set of eight-bit registers that store the results of measurements and provide settings

for various modes of operation. To accommodate the 13-bit size, the measured values of x , y and z are stored in

pairs of registers.

The AXDL345 chip supports serial communication using either the SPI (Serial Peripheral Interface Bus) or I2 C

(Inter-Integrated Circuit) Standards. The SPI communication is supported using either a three-wire or four-wire

connection. On the DE0-Nano and VEEK-MT boards, the accelerometer chip is connected to the FPGA chip by the

three-wire SPI arrangement.

A full description can be found in Analog Devices datasheets: Digital Accelerometer ADXL345.

2 UP Accelerometer Core Overview

The UP Accelerometer Core provides a convenient interface for accessing the accelerometer chip. The core can

be instantiated in systems designed by using the Qsys tool in Quartus II software. The core is also included in the

DE0-Nano Computer, which can be conveniently used within Altera University Program’s Monitor Program.

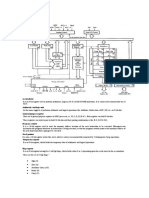

Figure 1 shows a high-level block diagram of the core. To set up the accelerometer device, the core takes information

from a program (via the Avalon bus) or an auto-initialization circuit and sends it out via the serial bus.

Altera Corporation - University Program 1

August 2014

ACCELEROMETER SPI M ODE C ORE FOR DE-S ERIES B OARDS For Quartus II 14.0

Avalon

Bus Serial

Bus

Serializer

Auto-Init

Figure 1. High-level block diagram of the UP Accelerometer Core.

3 Instantiating the Core

The UP Accelerometer core can be instantiated in a system using Qsys or as a standalone component from the IP

Catalog within the Quartus II software. Designers who wish to include the UP Accelerometer Core in their custom

systems should use the core’s configuration wizard. The wizard is depicted in Figure 2. It has no options, as indicated

in the figure.

Figure 2. Configuration Wizard for the UP Accelerometer Core.

2 Altera Corporation - University Program

August 2014

ACCELEROMETER SPI M ODE C ORE FOR DE-S ERIES B OARDS For Quartus II 14.0

4 Software Programming Model

The UP Accelerometer Core can be controlled by a program running on a processor. This is accomplished by reading

from and writing to two memory-mapped registers in the core. This can be done by directly accessing these registers.

Alternatively, for the Nios II processor, those registers can be manipulated using C-language functions accessible

through the Hardware Abstraction Layer (HAL) interface.

In the following sections, we describe the memory-mapped registers and how to use them, both directly and using

the HAL interface.

4.1 Registers in the UP Accelerometer Core

The UP Accelerometer Core has two 8-bit registers, called address and data. They are mapped to specific memory

addresses at the time the core is instantiated in a Qsys-developed system. Their addresses are offset by one byte, as

indicated in Table 1. The table shows the byte offset, access rights (Read/Write) and the meaning of each bit in the

registers.

By writing into these registers, the processor can specify the operationg mode of the accelerometer and read its

current values.

Table 1. UP Accelerometer Core Registers

Offset in Register

Read/Write 7. . . 6 5. . . 0

bytes Name

0 address W 0 Addr

1 data R/W Data

4.1.1 Address Register

The address register is used to transmit the address of a register in the ADXL345 device that is to be accessed.

The desired address is is given in the six least-significant bits, as shown in Table 1.

4.1.2 Data Register

The data register is used to transmit data from/to the registers in the ADXL345 device. Reading from or writing to

this register will initiate a serial transfer from/to the accelerometer.

4.2 Registers in the ADXL345 Device

The ADXL345 chip has a number of control and data registers, which are identified by six-bit addresses in the range

0x00 to 0x39. All registers are eight bits long. The control registers are used to define various modes of operation.

They are loaded by performing a write operation. Their contents can be examined by performing a read operation.

The data registers comprise three pairs of registers, which hold the currently measured values of acceleration in the

x , y and z directions.

Data registers DATAX0 and DATAX1, with addresses 0x32 and 0x33, hold the 2’s-complement value of the x -axis

measurement. The DATAX0 register holds the low-order byte and DATAX1 holds the high-order byte. Similarly,

Altera Corporation - University Program 3

August 2014

ACCELEROMETER SPI M ODE C ORE FOR DE-S ERIES B OARDS For Quartus II 14.0

DATAY0 and DATAY1, with addresses 0x34 and 0x35, hold the y -axis value, while DATAZ0 and DATAZ1, with

addresses 0x36 and 0x37, hold the z -axis value.

4.3 Configuring the Accelerometer

The accelerometer chip has to be configured to perform the desired functions, which is accomplished by writing

into the appropriate control registers. Using the UP Accelerometer Core, this can be achieved by writing the nec-

essary addresses and data into the address and data registers in the core. However, the UP Accelerator Core has an

auto-initialize option, which automatically configures it into a mode that causes measurements to be continuously

performed and allows reading of the results through the X , Y and Z register pairs using the resolution of ±2 g .

The automatic initialization is performed whenever the core is reset, which also occurs when the hardware system

that contains the core is downloaded into the FPGA device on the board.

5 Device Driver for the Nios II Processor

For use with the Nios II processor, the UP Accelerometer Core is packaged with C-language functions accessible

through the hardware abstraction layer (HAL). These functions enable users to communicate with the accelerometer

based on the register address and data given. Users should refer to the description of registers in the ADXL345

datasheets.

To use the functions, the C code must include the statement:

#include "altera_up_avalon_accelerometer_spi.h"

5.1 alt up accelerometer spi open dev

Prototype: alt_up_accelerometer_spi_dev*

alt_up_accelerometer_spi_open_dev(const char

*name)

Include: <altera_up_avalon_accelerometer_spi_spi.h>

Parameters: name – the accelerometer_spi component name in Qsys.

Returns: The corresponding device structure, or NULL if the device is not found.

Description: Opens the accelerometer_spi device specified by name .

4 Altera Corporation - University Program

August 2014

ACCELEROMETER SPI M ODE C ORE FOR DE-S ERIES B OARDS For Quartus II 14.0

5.2 alt up accelerometer spi read address register

Prototype: int alt_up_accelerometer_spi_read_address_register(alt_up_accelerometer_sp

*accel, alt_u8 *addr)

Include: <altera_up_avalon_accelerometer_spi.h>

Parameters: accel – the device structure

addr – a pointer to the location where the read address should be stored

Returns: 0 for success

Description: Reads configuration data from one of the accelerometer’s registers.

5.3 alt up accelerometer spi read

Prototype: int alt_up_accelerometer_spi_read(alt_up_accelerometer_spi_dev

*accel_spi, alt_u8 addr, alt_u8 *data)

Include: <altera_up_avalon_accelerometer.h>

Parameters: accel – the device structure

addr – the accelerometer register’s address

data – a pointer to the location where the read data should be stored

Returns: 0 for success

Description: Reads data from the accelerometer’s registers.

5.4 alt up accelerometer spi write

Prototype: int alt_up_accelerometer_spi_write(alt_up_accelerometer_spi_dev

*accel, alt_u8 addr, alt_u8 data)

Include: <altera_up_avalon_accelerometer.h>

Parameters: accel – the device structure

addr – the accelerometer register’s address

data – the data to be written

Returns: 0 for success

Description: Writes data to the accelerometer’s registers.

5.5 alt up accelerometer spi read x axis

Prototype: int alt_up_accelerometer_spi_read_x_axis(alt_up_accelerometer_spi_dev

*accel_spi, alt_32 *x_axis)

Include: <altera_up_avalon_accelerometer.h>

Parameters: accel – the device structure

x_axis – a pointer to the location where the x -axis data should be

stored

Returns: 0 for success

Description: Reads the x -xis value from both registers, DATAX0 and DATAX1, and

converts the value to a signed integer.

Altera Corporation - University Program 5

August 2014

ACCELEROMETER SPI M ODE C ORE FOR DE-S ERIES B OARDS For Quartus II 14.0

5.6 alt up accelerometer spi read y axis

Prototype: int alt_up_accelerometer_spi_read_y_axis(alt_up_accelerometer_spi_dev

*accel, alt_32 *y_axis)

Include: <altera_up_avalon_accelerometer.h>

Parameters: accel – the device structure

y_axis – a pointer to the location where the y -axis data should be

stored

Returns: 0 for success

Description: Reads the y -axis value from both registers, DATAY0 and DATAY1, and

converts the value to a signed integer.

5.7 alt up accelerometer spi read z axis

Prototype: int alt_up_accelerometer_spi_read_z_axis(alt_up_accelerometer_spi_dev

*accel, alt_32 *z_axis)

Include: <altera_up_avalon_accelerometer.h>

Parameters: accel – the device structure

z_axis – a pointer to the location where the z -axis data should be

stored

Returns: 0 for success

Description: Reads the z -axis value from both registers, DATAZ0 and DATAZ1, and

converts the value to a signed integer.

6 Altera Corporation - University Program

August 2014

You might also like

- Docu67723 VNX Operating Environment For Block 05.33.009.5.184 and For File 8.1.9.184, and Unisphere 1.3.9.1.184 Release NotesDocument105 pagesDocu67723 VNX Operating Environment For Block 05.33.009.5.184 and For File 8.1.9.184, and Unisphere 1.3.9.1.184 Release NotesafjeieNo ratings yet

- Rodrigo Trevino Resume EnglishDocument3 pagesRodrigo Trevino Resume EnglishRodrigo HasidNo ratings yet

- Accelerometer SPI ModeDocument6 pagesAccelerometer SPI ModecointoinNo ratings yet

- Accelerometer SPI ModeDocument6 pagesAccelerometer SPI ModecointoinNo ratings yet

- Chapter 4 Microprocessor SystemDocument71 pagesChapter 4 Microprocessor SystemGetTrendingNo ratings yet

- Microprocessor and Micro Controller Lecture NotesDocument118 pagesMicroprocessor and Micro Controller Lecture NotesSivanesh SK50% (2)

- 8-Bit Microcontroller With 2K Bytes of In-System Programmable Flash AT90S2313Document92 pages8-Bit Microcontroller With 2K Bytes of In-System Programmable Flash AT90S2313nullsoft69No ratings yet

- WWW Sparkfun Com Tutorials 240Document14 pagesWWW Sparkfun Com Tutorials 240ramnag4No ratings yet

- At Tiny 13Document146 pagesAt Tiny 13Hasri AwalNo ratings yet

- Internal Architecture of 8085 Microprocessor: A. Control UnitDocument17 pagesInternal Architecture of 8085 Microprocessor: A. Control Unitmech mech1No ratings yet

- M4 Yash AllabadiDocument6 pagesM4 Yash Allabadidegijon661No ratings yet

- Practical 1 Dyna KitDocument5 pagesPractical 1 Dyna KitHet PatelNo ratings yet

- MCT Unit 2Document26 pagesMCT Unit 2Aravind RajNo ratings yet

- 8085 MaterialDocument12 pages8085 MaterialsameerNo ratings yet

- Notes Unit 1Document25 pagesNotes Unit 1Ashish YadavNo ratings yet

- Laboratory Exercise 10: An Enhanced ProcessorDocument4 pagesLaboratory Exercise 10: An Enhanced ProcessorKhánh ConNo ratings yet

- Microprocessor NotesDocument21 pagesMicroprocessor NotesAdhithyaNo ratings yet

- 8-Bit Microcontroller With 4K Bytes In-System Programmable Flash AT90S4414 PreliminaryDocument10 pages8-Bit Microcontroller With 4K Bytes In-System Programmable Flash AT90S4414 PreliminaryYerson CrespoNo ratings yet

- Chapter 4 Microprocessor SystemDocument50 pagesChapter 4 Microprocessor SystemRajkishor YadavNo ratings yet

- An Introduction To INTEL 8085 Microprocessor: By:Ravindra Nadh.V, Assistant Professor, GST, BangaloreDocument35 pagesAn Introduction To INTEL 8085 Microprocessor: By:Ravindra Nadh.V, Assistant Professor, GST, BangaloreVasudev Rao KonjetiNo ratings yet

- Micro Hihihi HDocument4 pagesMicro Hihihi HbrycheezyNo ratings yet

- Lec 03 Internal Micro ArchitectureDocument24 pagesLec 03 Internal Micro ArchitecturePaarth JamwalNo ratings yet

- 8085 Architecture: Control UnitDocument10 pages8085 Architecture: Control UnitsweetmemoriesneverdiNo ratings yet

- 8 Bit Microprocessor Using VHDL: Pallavi Deshmane, Maithili Lad & Pooja Mhetre Sharan KumarDocument6 pages8 Bit Microprocessor Using VHDL: Pallavi Deshmane, Maithili Lad & Pooja Mhetre Sharan KumarshubhamNo ratings yet

- Unit Ii 8085 Micro Processor 8085 Architecture:: ME 6702 Mechatronics Mechanical Engineering 2019-20Document26 pagesUnit Ii 8085 Micro Processor 8085 Architecture:: ME 6702 Mechatronics Mechanical Engineering 2019-20GopinathNo ratings yet

- Speed Detector For HighwaysDocument29 pagesSpeed Detector For HighwaysShama MahinNo ratings yet

- Snug04 Bromley Smith PaperDocument16 pagesSnug04 Bromley Smith PaperDheeraj SinglaNo ratings yet

- Tutorial: Subject Code: 2150707 Subject Name: Microprocessor & InterfacingDocument6 pagesTutorial: Subject Code: 2150707 Subject Name: Microprocessor & InterfacingShaili PalejkarNo ratings yet

- Microprocessor and Micro ControllerDocument118 pagesMicroprocessor and Micro ControllerShiva ShanNo ratings yet

- Question With Answer MP & MCDocument13 pagesQuestion With Answer MP & MCMATHANKUMAR.SNo ratings yet

- ARM Core Data Flow Model and 3 Stage PipeliningDocument42 pagesARM Core Data Flow Model and 3 Stage Pipeliningjkumarmtech22No ratings yet

- 1-Architecture of 8085Document34 pages1-Architecture of 8085Pinki KumariNo ratings yet

- Architecture 8085Document46 pagesArchitecture 8085milf hunterNo ratings yet

- Microprocessor Lab ManualDocument85 pagesMicroprocessor Lab ManualReddyNo ratings yet

- FPGA Altera DE2 RS232 PDFDocument5 pagesFPGA Altera DE2 RS232 PDFidiot930902No ratings yet

- MPDocument34 pagesMPAbhinandan JainNo ratings yet

- MPMC Model Exam Answer KeyDocument21 pagesMPMC Model Exam Answer KeyVenkatesan SundaramNo ratings yet

- Microprocessor 8085 ArchitectureDocument19 pagesMicroprocessor 8085 ArchitectureSindhujaSindhuNo ratings yet

- Experiment No. 1: Department of Electronics & Comm - EnggDocument7 pagesExperiment No. 1: Department of Electronics & Comm - EnggJaspreet KaurNo ratings yet

- Microprocessor Basics and Related TermsDocument27 pagesMicroprocessor Basics and Related TermsJai Sai RamNo ratings yet

- Ee8551 8085 NotesDocument31 pagesEe8551 8085 NotesKUMARANSCRNo ratings yet

- Microprocessors and Microcontrollers NotesDocument293 pagesMicroprocessors and Microcontrollers NotesKumar ChaitanyaNo ratings yet

- Advanced RISC Machine-ARM Notes BhurchandiDocument8 pagesAdvanced RISC Machine-ARM Notes BhurchandiVipin TiwariNo ratings yet

- 19 MSP1056 MicroprocessorDocument9 pages19 MSP1056 Microprocessorsakshi sharmaNo ratings yet

- 8085 MicroprocessorDocument13 pages8085 MicroprocessorSajid Akram100% (1)

- CH 3Document8 pagesCH 3Parth ThakkarNo ratings yet

- ESD Manual StudentsDocument55 pagesESD Manual StudentsNimesh PrajapatiNo ratings yet

- 8085 ppt 1Document17 pages8085 ppt 1usgaonkard10No ratings yet

- ANS Computer Awareness Year 1Document4 pagesANS Computer Awareness Year 1virad25No ratings yet

- 04 AVR ALU and SREG SetDocument12 pages04 AVR ALU and SREG SetDerbendeNo ratings yet

- Intel 8085 Architecture: AccumulatorDocument6 pagesIntel 8085 Architecture: AccumulatorDipesh YadavNo ratings yet

- 8085 ArchitectureDocument17 pages8085 ArchitectureSamaira Shahnoor ParvinNo ratings yet

- Microprocessor Lecture Notes 1 10Document202 pagesMicroprocessor Lecture Notes 1 10Ambarish SinghNo ratings yet

- Microprocessor Lecture 1Document4 pagesMicroprocessor Lecture 1rspahlobNo ratings yet

- MICROPORCESSOR 8085 Lab ManualDocument53 pagesMICROPORCESSOR 8085 Lab ManualAjay PatilNo ratings yet

- Data SheetDocument211 pagesData SheetYana PrikitiwNo ratings yet

- 8085 Microprocessor Architecture, Pin DiagramDocument10 pages8085 Microprocessor Architecture, Pin DiagramSachin Jaysenan0% (1)

- Microprocessors - II: Yashar HajiyevDocument62 pagesMicroprocessors - II: Yashar HajiyevMurad QəhramanovNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Business Intelligence ImplementationDocument88 pagesBusiness Intelligence ImplementationFabiyi Olawale100% (1)

- CTS-AutomotiveServiceTech310S L1 MP EN PDFDocument59 pagesCTS-AutomotiveServiceTech310S L1 MP EN PDFDoDuyBacNo ratings yet

- Protection of Multimedia Works Under: Research SynopsisDocument7 pagesProtection of Multimedia Works Under: Research SynopsisAvtar singhNo ratings yet

- How Did Semiconductors Change Our LivesDocument4 pagesHow Did Semiconductors Change Our Livesmunnayadav555No ratings yet

- Problem Reduction: - AND-OR Graph - AO SearchDocument31 pagesProblem Reduction: - AND-OR Graph - AO Searchmiriyala nagendraNo ratings yet

- IEEE Xplore - The Evolution of Robotics ResearchDocument1 pageIEEE Xplore - The Evolution of Robotics ResearchManu Sathish NairNo ratings yet

- Enrollment Form 3Document1 pageEnrollment Form 3حيدرالركابيNo ratings yet

- Ebook - Top Angel Investors PDFDocument49 pagesEbook - Top Angel Investors PDFPankaj GourNo ratings yet

- Cam Module 5 RomDocument28 pagesCam Module 5 Romnamitha rNo ratings yet

- Siebel Systems Case Analysis: Group 10 - Section BDocument7 pagesSiebel Systems Case Analysis: Group 10 - Section BAmit RajNo ratings yet

- M09 Access & Use InterDocument85 pagesM09 Access & Use Interbeye asheNo ratings yet

- DD Project Book StudentDocument40 pagesDD Project Book StudentLord_nNo ratings yet

- Scanprint IMS enDocument8 pagesScanprint IMS enMarios DomoxoudisNo ratings yet

- BcdinfoDocument3 pagesBcdinforegeniusNo ratings yet

- Excel Cash BookDocument16 pagesExcel Cash BookzeeshanNo ratings yet

- 969c4824-5909-4c92-b584-7db17876a664Document6 pages969c4824-5909-4c92-b584-7db17876a664Swamy Dhas DhasNo ratings yet

- Assignment 1: COMPUTER (CCM10802) Parts of Computer SystemDocument7 pagesAssignment 1: COMPUTER (CCM10802) Parts of Computer Systemangelerryshaforever100% (1)

- PCT M1 FlowDocument2 pagesPCT M1 FlowRms VicNo ratings yet

- SOF Sample Paper Class 3Document8 pagesSOF Sample Paper Class 3govimano100% (1)

- Clean LogDocument2 pagesClean LogAji MauLanaNo ratings yet

- ComProg Module - M5 FinalDocument6 pagesComProg Module - M5 FinalLEO JR GREFALDONo ratings yet

- How To Move Sepm From One Server To Another ServerDocument4 pagesHow To Move Sepm From One Server To Another ServerNan Win AungNo ratings yet

- Solution Manual For Avr Microcontroller and Embedded Systems Using Assembly and C Muhammad Ali Mazidi Sarmad Naimi Sepehr NaimiDocument37 pagesSolution Manual For Avr Microcontroller and Embedded Systems Using Assembly and C Muhammad Ali Mazidi Sarmad Naimi Sepehr Naimidespendcaduke80ux100% (20)

- User Manual For New Firmware of The 3/3.5-Inch Color Screen: Date: April 2013Document63 pagesUser Manual For New Firmware of The 3/3.5-Inch Color Screen: Date: April 2013Denny De Leon LaurencioNo ratings yet

- المكتبات الذكية 2Document28 pagesالمكتبات الذكية 2malik 1992No ratings yet

- Teaching NLTK NorwegianDocument68 pagesTeaching NLTK NorwegianRamesh AkulaNo ratings yet

- DTMF Based Speed Control of DC Motor PDFDocument3 pagesDTMF Based Speed Control of DC Motor PDFInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Standard Colour Cable CodeDocument1 pageStandard Colour Cable CodeVerli AndreansyahNo ratings yet