Professional Documents

Culture Documents

Ece HDL 18ec56 5a Ia Test

Ece HDL 18ec56 5a Ia Test

Uploaded by

jai kumarCopyright:

Available Formats

You might also like

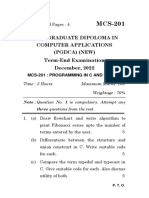

- MCS 201Document4 pagesMCS 201Bedodipti ChoudharyNo ratings yet

- 9A04706 Digital Design Through Verilog HDL PDFDocument1 page9A04706 Digital Design Through Verilog HDL PDFTayyabunnissa BegumNo ratings yet

- Question Paper FormatDocument2 pagesQuestion Paper FormatwroxtarNo ratings yet

- ComputerDocument50 pagesComputerx yNo ratings yet

- Pdfjoiner PDFDocument26 pagesPdfjoiner PDFbakosey323No ratings yet

- AACS1084 PCD II (Question) - Final 202201Document5 pagesAACS1084 PCD II (Question) - Final 202201vlora.william15No ratings yet

- WWW - Manaresults.co - In: Set No. 1Document4 pagesWWW - Manaresults.co - In: Set No. 1Machine BatteryNo ratings yet

- SBC-SBC-SBC: Eighth Semester B.Tech. Degree Examinations, September 2020Document2 pagesSBC-SBC-SBC: Eighth Semester B.Tech. Degree Examinations, September 2020Jinu ThomasNo ratings yet

- Design and Analysis of AlgorithmsDocument5 pagesDesign and Analysis of AlgorithmsShubham JoshiNo ratings yet

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Document2 pagesWWW - Manaresults.Co - In: (Electronics and Communication Engineering)Babu GundlapallyNo ratings yet

- Asic - QPDocument2 pagesAsic - QPveeramaniks408No ratings yet

- Btech 1 Sem Programming For Problem Solving kcs101 2021Document1 pageBtech 1 Sem Programming For Problem Solving kcs101 2021rishabhchauhan2266No ratings yet

- BCS-011 - D16 - CompressedDocument4 pagesBCS-011 - D16 - CompressedotuneschannelNo ratings yet

- Object Oriented Programming 20CSC03Document2 pagesObject Oriented Programming 20CSC03abhireddie65No ratings yet

- Total Pages:2: Answer All Questions, Each Carries 3 MarksDocument2 pagesTotal Pages:2: Answer All Questions, Each Carries 3 MarksKrishnapriya MenonNo ratings yet

- 159.102 Computer Science Fundamentals - Massey - Exam - S2 2016Document5 pages159.102 Computer Science Fundamentals - Massey - Exam - S2 2016DonNo ratings yet

- Linux and OS Question SEM FINAL QUESTION BANKDocument65 pagesLinux and OS Question SEM FINAL QUESTION BANKIndia RaniNo ratings yet

- Papers 2020Document33 pagesPapers 2020anish231003No ratings yet

- Computer Science 2021Document5 pagesComputer Science 2021Ifthikhar AhmadNo ratings yet

- PEC-CSE 511 (A) (NEW)Document2 pagesPEC-CSE 511 (A) (NEW)Madhumay Kanti BhattacharjeeNo ratings yet

- 131 Ad 052018Document2 pages131 Ad 052018vrkoradaNo ratings yet

- 13 Problem Solving Techniques Using C - April May 2021 (F+ R CBCS Y2K14)Document2 pages13 Problem Solving Techniques Using C - April May 2021 (F+ R CBCS Y2K14)yashkrish722No ratings yet

- ACSE0202Document5 pagesACSE0202Vipul ThakurNo ratings yet

- Programming for Problem Solving KCS101TDocument1 pageProgramming for Problem Solving KCS101Tarush patelNo ratings yet

- Wipro Elite NTH Coding Paper 1Document6 pagesWipro Elite NTH Coding Paper 1Atrayee GayenNo ratings yet

- Iv-I Cse Question Bank - R15Document53 pagesIv-I Cse Question Bank - R15jollyggNo ratings yet

- WWW - Manaresults.Co - In: (Information Technology)Document2 pagesWWW - Manaresults.Co - In: (Information Technology)mallesandeepNo ratings yet

- PSP Set-I Used For Nov 2021Document2 pagesPSP Set-I Used For Nov 2021kisnamohanNo ratings yet

- 2018 April IT301-BDocument2 pages2018 April IT301-BHisana Thasneem A HNo ratings yet

- Gce A Level - New Computer Science - A2 Unit 3: Programming and System DevelopmentDocument4 pagesGce A Level - New Computer Science - A2 Unit 3: Programming and System DevelopmentWyatt CtNo ratings yet

- MCSL 025 PDFDocument56 pagesMCSL 025 PDFNerdy Fella100% (1)

- Following Paper ID and Roll No. To Be Filled in Your Answer BookDocument3 pagesFollowing Paper ID and Roll No. To Be Filled in Your Answer BookShaurya SumanNo ratings yet

- Web Programming Sep Oct 2022Document2 pagesWeb Programming Sep Oct 2022Rock MaheshNo ratings yet

- Web Programming Sep Oct 2022Document2 pagesWeb Programming Sep Oct 2022kgf7026No ratings yet

- Web Programming Sep Oct 2022Document2 pagesWeb Programming Sep Oct 2022knihal794No ratings yet

- Advance Digital Design Using Verilog Nec024rDocument2 pagesAdvance Digital Design Using Verilog Nec024rManjeet SinghNo ratings yet

- CD Model Set-5 Answer KeyDocument32 pagesCD Model Set-5 Answer Keysrinathgopinath87No ratings yet

- BCN1043 Computer Arc & Org S1 0119Document6 pagesBCN1043 Computer Arc & Org S1 0119m-868020No ratings yet

- Btech Cse It Principles Progrmmng Language 20161460440258Document4 pagesBtech Cse It Principles Progrmmng Language 20161460440258Shalynee SuthaharNo ratings yet

- Answer All QuestionsDocument4 pagesAnswer All QuestionsShalynee SuthaharNo ratings yet

- Btech Cse 3 Sem System Programming Pcs3i103 2018Document2 pagesBtech Cse 3 Sem System Programming Pcs3i103 2018Abhas Kumar SinhaNo ratings yet

- 9A04706 Digital Design Through Verilog HDL PDFDocument4 pages9A04706 Digital Design Through Verilog HDL PDFTayyabunnissa BegumNo ratings yet

- R17 CP Model QP SET-IDocument2 pagesR17 CP Model QP SET-IkisnamohanNo ratings yet

- Question BCS011Document88 pagesQuestion BCS011sdfbfbbgvNo ratings yet

- VI Sem, Jan, Feb 2005Document4 pagesVI Sem, Jan, Feb 2005Veeresh NicolyteNo ratings yet

- December 2012: Amiete - Cs/ItDocument4 pagesDecember 2012: Amiete - Cs/ItM Taher BamyaniNo ratings yet

- B H192030 Pages:2: Answer All Questions, Each Carries 4 MarksDocument2 pagesB H192030 Pages:2: Answer All Questions, Each Carries 4 MarksSrinivas R PaiNo ratings yet

- Woo Back BabyDocument4 pagesWoo Back BabyTapiwa gingoNo ratings yet

- Design and Algo 2022 DecDocument4 pagesDesign and Algo 2022 DecMd Nisu AhmadNo ratings yet

- 2014 End-Regu Coa QuestionDocument3 pages2014 End-Regu Coa QuestionAnurag BhattacharjeeNo ratings yet

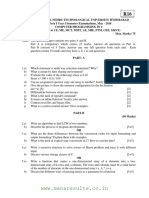

- Time: 3 Hours Maximum Marks: 100 (Weightage: 75%) Question Number Is and Carries 40 Marks. Attempt Any Questions From The RestDocument3 pagesTime: 3 Hours Maximum Marks: 100 (Weightage: 75%) Question Number Is and Carries 40 Marks. Attempt Any Questions From The RestAbhijeetNo ratings yet

- CT2369Document2 pagesCT2369DIVYAM PADOLENo ratings yet

- BCA May 2018 Question Papers PDFDocument45 pagesBCA May 2018 Question Papers PDFsakthivelNo ratings yet

- Barani Institute of Management Sciences: BS (CS) - 5B & 5D Computer Architecture CS-532Document1 pageBarani Institute of Management Sciences: BS (CS) - 5B & 5D Computer Architecture CS-532Yaseen ShahidNo ratings yet

- Ii - Semester-Mca III - TEST - May. - 2010 Time: 90 Minutes Section-A/B Max - Marks: 50Document1 pageIi - Semester-Mca III - TEST - May. - 2010 Time: 90 Minutes Section-A/B Max - Marks: 50arunn1588No ratings yet

- ACSBS0502Document4 pagesACSBS0502Anubhav awasthiNo ratings yet

- Jntuworld: Time: 3 Hours Max. Marks: 75Document1 pageJntuworld: Time: 3 Hours Max. Marks: 75saiteja1234No ratings yet

- 9A05101 Programming in C and Data StructuresDocument4 pages9A05101 Programming in C and Data StructuressivabharathamurthyNo ratings yet

- BSCS 308 - End of Semester Draft ExamDocument4 pagesBSCS 308 - End of Semester Draft Examcraigcarlos95No ratings yet

Ece HDL 18ec56 5a Ia Test

Ece HDL 18ec56 5a Ia Test

Uploaded by

jai kumarOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ece HDL 18ec56 5a Ia Test

Ece HDL 18ec56 5a Ia Test

Uploaded by

jai kumarCopyright:

Available Formats

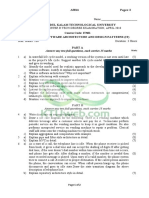

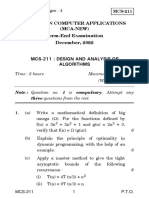

SDM INSTITUTE OF TECHNOLOGY, UJIRE

I Internal Assessment Test

VERILOG HDL (18EC56)

V Sem A. ECE Dept Time: 1 hour Max. marks: 30

Instructions:

(1) Write your USN, Name, Subject Code, Subject Title and append your signature on

the top of the answer script. Mention page number at the bottom of every page

without fail.

(2) Save in one single PDF format by giving the name of the file ‘USN_first IA_Subject

code.pdf’

(3) Email the scanned PDF file to varunsk@sdmit.in (Cell No. 9480716174 ) within 15

minutes after completion of the test.

Answer ONE full question from PART A and ONE full question from PART B

Q. No. Marks

PART A

1 (a) Draw the diagram of typical HDL design flow and elaborate each block

10

in few words.

(b) Apply the Bottom-Up design methodology for the design of 4:1 MUX

using 2:1 MUX. 5

OR

2 (a) Design 4-Bit Ripple carry adder using 1-bit Full adder and explain the

design block and simulation block. 10

(b) Mention the two styles of stimulus application of component of a

simulation. With the example explain the same. 5

PART B

3 (a) List the Data types used in the Verilog HDL. Explain with examples. 10

(b) Declare the following variables in Verilog.

1. An &bit vector net called a-in.

2. An integer called count.

3. A time variable called snap-shot.

4. An array called delays. Array contains 20 elements of the type

integer.

5. A parameter cache-size equal to 512. 5

OR

4 (a) Design SR-Flipflop using basic gates. Write the module definition for

this module. Include the list of ports and port declarations. 10

(b) With an examples elaborate port connections rules. 5

You might also like

- MCS 201Document4 pagesMCS 201Bedodipti ChoudharyNo ratings yet

- 9A04706 Digital Design Through Verilog HDL PDFDocument1 page9A04706 Digital Design Through Verilog HDL PDFTayyabunnissa BegumNo ratings yet

- Question Paper FormatDocument2 pagesQuestion Paper FormatwroxtarNo ratings yet

- ComputerDocument50 pagesComputerx yNo ratings yet

- Pdfjoiner PDFDocument26 pagesPdfjoiner PDFbakosey323No ratings yet

- AACS1084 PCD II (Question) - Final 202201Document5 pagesAACS1084 PCD II (Question) - Final 202201vlora.william15No ratings yet

- WWW - Manaresults.co - In: Set No. 1Document4 pagesWWW - Manaresults.co - In: Set No. 1Machine BatteryNo ratings yet

- SBC-SBC-SBC: Eighth Semester B.Tech. Degree Examinations, September 2020Document2 pagesSBC-SBC-SBC: Eighth Semester B.Tech. Degree Examinations, September 2020Jinu ThomasNo ratings yet

- Design and Analysis of AlgorithmsDocument5 pagesDesign and Analysis of AlgorithmsShubham JoshiNo ratings yet

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Document2 pagesWWW - Manaresults.Co - In: (Electronics and Communication Engineering)Babu GundlapallyNo ratings yet

- Asic - QPDocument2 pagesAsic - QPveeramaniks408No ratings yet

- Btech 1 Sem Programming For Problem Solving kcs101 2021Document1 pageBtech 1 Sem Programming For Problem Solving kcs101 2021rishabhchauhan2266No ratings yet

- BCS-011 - D16 - CompressedDocument4 pagesBCS-011 - D16 - CompressedotuneschannelNo ratings yet

- Object Oriented Programming 20CSC03Document2 pagesObject Oriented Programming 20CSC03abhireddie65No ratings yet

- Total Pages:2: Answer All Questions, Each Carries 3 MarksDocument2 pagesTotal Pages:2: Answer All Questions, Each Carries 3 MarksKrishnapriya MenonNo ratings yet

- 159.102 Computer Science Fundamentals - Massey - Exam - S2 2016Document5 pages159.102 Computer Science Fundamentals - Massey - Exam - S2 2016DonNo ratings yet

- Linux and OS Question SEM FINAL QUESTION BANKDocument65 pagesLinux and OS Question SEM FINAL QUESTION BANKIndia RaniNo ratings yet

- Papers 2020Document33 pagesPapers 2020anish231003No ratings yet

- Computer Science 2021Document5 pagesComputer Science 2021Ifthikhar AhmadNo ratings yet

- PEC-CSE 511 (A) (NEW)Document2 pagesPEC-CSE 511 (A) (NEW)Madhumay Kanti BhattacharjeeNo ratings yet

- 131 Ad 052018Document2 pages131 Ad 052018vrkoradaNo ratings yet

- 13 Problem Solving Techniques Using C - April May 2021 (F+ R CBCS Y2K14)Document2 pages13 Problem Solving Techniques Using C - April May 2021 (F+ R CBCS Y2K14)yashkrish722No ratings yet

- ACSE0202Document5 pagesACSE0202Vipul ThakurNo ratings yet

- Programming for Problem Solving KCS101TDocument1 pageProgramming for Problem Solving KCS101Tarush patelNo ratings yet

- Wipro Elite NTH Coding Paper 1Document6 pagesWipro Elite NTH Coding Paper 1Atrayee GayenNo ratings yet

- Iv-I Cse Question Bank - R15Document53 pagesIv-I Cse Question Bank - R15jollyggNo ratings yet

- WWW - Manaresults.Co - In: (Information Technology)Document2 pagesWWW - Manaresults.Co - In: (Information Technology)mallesandeepNo ratings yet

- PSP Set-I Used For Nov 2021Document2 pagesPSP Set-I Used For Nov 2021kisnamohanNo ratings yet

- 2018 April IT301-BDocument2 pages2018 April IT301-BHisana Thasneem A HNo ratings yet

- Gce A Level - New Computer Science - A2 Unit 3: Programming and System DevelopmentDocument4 pagesGce A Level - New Computer Science - A2 Unit 3: Programming and System DevelopmentWyatt CtNo ratings yet

- MCSL 025 PDFDocument56 pagesMCSL 025 PDFNerdy Fella100% (1)

- Following Paper ID and Roll No. To Be Filled in Your Answer BookDocument3 pagesFollowing Paper ID and Roll No. To Be Filled in Your Answer BookShaurya SumanNo ratings yet

- Web Programming Sep Oct 2022Document2 pagesWeb Programming Sep Oct 2022Rock MaheshNo ratings yet

- Web Programming Sep Oct 2022Document2 pagesWeb Programming Sep Oct 2022kgf7026No ratings yet

- Web Programming Sep Oct 2022Document2 pagesWeb Programming Sep Oct 2022knihal794No ratings yet

- Advance Digital Design Using Verilog Nec024rDocument2 pagesAdvance Digital Design Using Verilog Nec024rManjeet SinghNo ratings yet

- CD Model Set-5 Answer KeyDocument32 pagesCD Model Set-5 Answer Keysrinathgopinath87No ratings yet

- BCN1043 Computer Arc & Org S1 0119Document6 pagesBCN1043 Computer Arc & Org S1 0119m-868020No ratings yet

- Btech Cse It Principles Progrmmng Language 20161460440258Document4 pagesBtech Cse It Principles Progrmmng Language 20161460440258Shalynee SuthaharNo ratings yet

- Answer All QuestionsDocument4 pagesAnswer All QuestionsShalynee SuthaharNo ratings yet

- Btech Cse 3 Sem System Programming Pcs3i103 2018Document2 pagesBtech Cse 3 Sem System Programming Pcs3i103 2018Abhas Kumar SinhaNo ratings yet

- 9A04706 Digital Design Through Verilog HDL PDFDocument4 pages9A04706 Digital Design Through Verilog HDL PDFTayyabunnissa BegumNo ratings yet

- R17 CP Model QP SET-IDocument2 pagesR17 CP Model QP SET-IkisnamohanNo ratings yet

- Question BCS011Document88 pagesQuestion BCS011sdfbfbbgvNo ratings yet

- VI Sem, Jan, Feb 2005Document4 pagesVI Sem, Jan, Feb 2005Veeresh NicolyteNo ratings yet

- December 2012: Amiete - Cs/ItDocument4 pagesDecember 2012: Amiete - Cs/ItM Taher BamyaniNo ratings yet

- B H192030 Pages:2: Answer All Questions, Each Carries 4 MarksDocument2 pagesB H192030 Pages:2: Answer All Questions, Each Carries 4 MarksSrinivas R PaiNo ratings yet

- Woo Back BabyDocument4 pagesWoo Back BabyTapiwa gingoNo ratings yet

- Design and Algo 2022 DecDocument4 pagesDesign and Algo 2022 DecMd Nisu AhmadNo ratings yet

- 2014 End-Regu Coa QuestionDocument3 pages2014 End-Regu Coa QuestionAnurag BhattacharjeeNo ratings yet

- Time: 3 Hours Maximum Marks: 100 (Weightage: 75%) Question Number Is and Carries 40 Marks. Attempt Any Questions From The RestDocument3 pagesTime: 3 Hours Maximum Marks: 100 (Weightage: 75%) Question Number Is and Carries 40 Marks. Attempt Any Questions From The RestAbhijeetNo ratings yet

- CT2369Document2 pagesCT2369DIVYAM PADOLENo ratings yet

- BCA May 2018 Question Papers PDFDocument45 pagesBCA May 2018 Question Papers PDFsakthivelNo ratings yet

- Barani Institute of Management Sciences: BS (CS) - 5B & 5D Computer Architecture CS-532Document1 pageBarani Institute of Management Sciences: BS (CS) - 5B & 5D Computer Architecture CS-532Yaseen ShahidNo ratings yet

- Ii - Semester-Mca III - TEST - May. - 2010 Time: 90 Minutes Section-A/B Max - Marks: 50Document1 pageIi - Semester-Mca III - TEST - May. - 2010 Time: 90 Minutes Section-A/B Max - Marks: 50arunn1588No ratings yet

- ACSBS0502Document4 pagesACSBS0502Anubhav awasthiNo ratings yet

- Jntuworld: Time: 3 Hours Max. Marks: 75Document1 pageJntuworld: Time: 3 Hours Max. Marks: 75saiteja1234No ratings yet

- 9A05101 Programming in C and Data StructuresDocument4 pages9A05101 Programming in C and Data StructuressivabharathamurthyNo ratings yet

- BSCS 308 - End of Semester Draft ExamDocument4 pagesBSCS 308 - End of Semester Draft Examcraigcarlos95No ratings yet