Professional Documents

Culture Documents

0 ratings0% found this document useful (0 votes)

10 viewsExamen Unidad 2: Walter Manuel Ruiz Naranjo

Examen Unidad 2: Walter Manuel Ruiz Naranjo

Uploaded by

Manuel RuizCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You might also like

- DSD Lab3 Fa20-Bce-029 PDFDocument5 pagesDSD Lab3 Fa20-Bce-029 PDFabdullahNo ratings yet

- Universidad Nacional Tecnologica de Lima SurDocument5 pagesUniversidad Nacional Tecnologica de Lima SurJoseph JesusNo ratings yet

- Universidad Nacional Tecnologica de Lima SurDocument5 pagesUniversidad Nacional Tecnologica de Lima SurJoseph JesusNo ratings yet

- 10100Document7 pages10100Đạt NguyễnNo ratings yet

- Exam1 (Example With Solutions)Document5 pagesExam1 (Example With Solutions)Rüya Gïbî100% (1)

- Trabajo de Diseño02Document10 pagesTrabajo de Diseño02Alvaro SegoviaNo ratings yet

- Trabajo de Diseño02Document10 pagesTrabajo de Diseño02Victor yurivilca lazoNo ratings yet

- лр 5 архDocument2 pagesлр 5 архspam trachNo ratings yet

- Structure of A Typical Digital SystemDocument29 pagesStructure of A Typical Digital SystemQasimNo ratings yet

- 수정 전 코드Document2 pages수정 전 코드붕붕부릉부릉No ratings yet

- Quadrature EncoderDocument5 pagesQuadrature EncoderJaime Santiago Sanchez ReinosoNo ratings yet

- Moore Machine VHDL CodeDocument2 pagesMoore Machine VHDL CodeKewl84No ratings yet

- BT3 TuvietDocument2 pagesBT3 TuvietChúc Văn KiênNo ratings yet

- SemaforoDocument2 pagesSemaforoVictor yurivilca lazoNo ratings yet

- Bài 1: Mạch giải mã BCD - 7 đoạn cho LED loại katot chungDocument9 pagesBài 1: Mạch giải mã BCD - 7 đoạn cho LED loại katot chungDoi Gio HuNo ratings yet

- Impletar en VHDL La Siguiente Maquina de EstadosDocument10 pagesImpletar en VHDL La Siguiente Maquina de EstadosGian SusanaNo ratings yet

- VHDL Codes For 32-Bit Processor: AARON T IMMANUEL (217-74-907)Document7 pagesVHDL Codes For 32-Bit Processor: AARON T IMMANUEL (217-74-907)adormentNo ratings yet

- FSM Design Verilog HDL PDFDocument7 pagesFSM Design Verilog HDL PDFajayNo ratings yet

- Lab11 - Achmad Mauludin - 165060301111002Document17 pagesLab11 - Achmad Mauludin - 165060301111002Mauudin BRgNo ratings yet

- Exp 2 - PIPODocument6 pagesExp 2 - PIPOAnkit GovindNo ratings yet

- Alu ArithmeticDocument7 pagesAlu ArithmeticTech-savvy GirishaNo ratings yet

- Beginning FPGA Programming - Partie41 PDFDocument5 pagesBeginning FPGA Programming - Partie41 PDFali alilouNo ratings yet

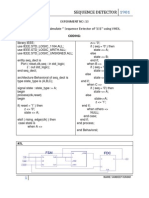

- Sequence Detector: Experiment No: 10 Activity: To Design and Simulate ' Sequence Detector of 101'' Using VHDLDocument2 pagesSequence Detector: Experiment No: 10 Activity: To Design and Simulate ' Sequence Detector of 101'' Using VHDLSaurabh KhandelwalNo ratings yet

- MemoriaDocument10 pagesMemoriaAlvaroNo ratings yet

- Name:waqar Baig SID:8878: Assignment) Design A FSM To Detect SequenceDocument4 pagesName:waqar Baig SID:8878: Assignment) Design A FSM To Detect Sequencesyed talibNo ratings yet

- Moore 1011 Overlapping SequenceDocument7 pagesMoore 1011 Overlapping Sequencedinesh100% (1)

- Chuong Trinh Den Giao ThongDocument2 pagesChuong Trinh Den Giao ThongHồng PhượngNo ratings yet

- AIM OF THE EXPERIMENT:-Binary To Decimal, Gray Code Apparatus RequiredDocument8 pagesAIM OF THE EXPERIMENT:-Binary To Decimal, Gray Code Apparatus RequiredSai KaneNo ratings yet

- Dcs-Ii Lab File: - Anupam Sobti 17/EC/09Document19 pagesDcs-Ii Lab File: - Anupam Sobti 17/EC/09Ankit GoelNo ratings yet

- Using Case Statement VHDL Code:: Assignment 2Document15 pagesUsing Case Statement VHDL Code:: Assignment 2innovatorinnovatorNo ratings yet

- Binary 1's and 0's CounterDocument13 pagesBinary 1's and 0's CounterKetan SalviNo ratings yet

- MAQUINA DE ESTADOS1 (Autoguardado)Document19 pagesMAQUINA DE ESTADOS1 (Autoguardado)YealsatoNo ratings yet

- experiment 8 //design of FSM - Vending MachineDocument8 pagesexperiment 8 //design of FSM - Vending MachineRishabNo ratings yet

- VHDL Code For A D Flip FlopDocument9 pagesVHDL Code For A D Flip FlopYogesh KhollamNo ratings yet

- VHDL Interfacing ProgramsDocument22 pagesVHDL Interfacing ProgramsNithish ManjuNo ratings yet

- Electiva - CIRCUITOS SECUENCIALES EN VHDLDocument5 pagesElectiva - CIRCUITOS SECUENCIALES EN VHDLfer gutiNo ratings yet

- Bach Khoa University of Technology: Digital Systems Laboratory Prelab 4 Finite State MachineDocument11 pagesBach Khoa University of Technology: Digital Systems Laboratory Prelab 4 Finite State MachineMờ LanhNo ratings yet

- Problema 1 "Lavadora" Código VHDL ModuleDocument40 pagesProblema 1 "Lavadora" Código VHDL ModuleLeonardoNo ratings yet

- EE 360M - Digital Systems Design Using VHDL: Lizy K. John University of Texas at AustinDocument73 pagesEE 360M - Digital Systems Design Using VHDL: Lizy K. John University of Texas at AustindnachegariNo ratings yet

- FSM Modeling Using VHDL: Dr. Gaganpreet KaurDocument12 pagesFSM Modeling Using VHDL: Dr. Gaganpreet KaurjajaNo ratings yet

- Verilog Code - State MachinesDocument3 pagesVerilog Code - State MachinesvasuvlsiNo ratings yet

- FA (BHVR) - CodeDocument1 pageFA (BHVR) - Codebhslegion1498No ratings yet

- Ejemplos VHDLDocument5 pagesEjemplos VHDLLeón Emmanuel NNo ratings yet

- 1.-Programa de Secuencia (Latch D)Document7 pages1.-Programa de Secuencia (Latch D)andy77740No ratings yet

- Combinational Circuit2Document6 pagesCombinational Circuit2Rinki KarNo ratings yet

- Piranti Terprogram - FSMDocument8 pagesPiranti Terprogram - FSMnamirarizqi annisaNo ratings yet

- Lab 5 Firna FrilanisaDocument18 pagesLab 5 Firna FrilanisaFirna FrilanisaNo ratings yet

- Demo!: GoalDocument24 pagesDemo!: GoalVaibhaviNo ratings yet

- Entity Alu IsDocument3 pagesEntity Alu IsDiego Jarosky Chachayma FarfánNo ratings yet

- Lab # 11: This Lab Has Been Designed To Familiarize With The Design of A Keypad Scanner Using VHDL and Show The Output On The FPGA BoardDocument4 pagesLab # 11: This Lab Has Been Designed To Familiarize With The Design of A Keypad Scanner Using VHDL and Show The Output On The FPGA Boardshermeen445No ratings yet

- Lab10 Dice GameDocument10 pagesLab10 Dice GamePhuc Van NguyenNo ratings yet

- TopDocument1 pageTopayberkktural21No ratings yet

- Algorithmic State Machine (ASM) Charts: VHDL Code & Timing DiagramsDocument32 pagesAlgorithmic State Machine (ASM) Charts: VHDL Code & Timing DiagramsManuel Garay GutierrezNo ratings yet

- Rekonstrukt: FPGA Based Forth Development Environment / Forth Based FPGA Development EnvironmentDocument4 pagesRekonstrukt: FPGA Based Forth Development Environment / Forth Based FPGA Development EnvironmentSuraj Kumar100% (1)

- Họ và tên: Lê Hồng Phú MSSV: 41801040 Bài tập 6 - buổi học 20211030Document8 pagesHọ và tên: Lê Hồng Phú MSSV: 41801040 Bài tập 6 - buổi học 20211030Hồng PhúNo ratings yet

- Lab 1 ReportDocument7 pagesLab 1 ReportNguyễn ThắngNo ratings yet

- Program I: To Simulate and Gate: Digital Circuits and Systems - Ii LabDocument72 pagesProgram I: To Simulate and Gate: Digital Circuits and Systems - Ii LabVarun GuptaNo ratings yet

- EXC11Document4 pagesEXC11Rishi KeshNo ratings yet

- Digital Design With SM ChartsDocument26 pagesDigital Design With SM ChartsAmar NathNo ratings yet

Examen Unidad 2: Walter Manuel Ruiz Naranjo

Examen Unidad 2: Walter Manuel Ruiz Naranjo

Uploaded by

Manuel Ruiz0 ratings0% found this document useful (0 votes)

10 views8 pagesOriginal Title

Examen.docx

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

0 ratings0% found this document useful (0 votes)

10 views8 pagesExamen Unidad 2: Walter Manuel Ruiz Naranjo

Examen Unidad 2: Walter Manuel Ruiz Naranjo

Uploaded by

Manuel RuizCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

You are on page 1of 8

Examen Unidad 2:

WALTER MANUEL RUIZ NARANJO

Library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity Nivel_FMS is

Port ( clk: in STDA_LOGIC;

Reset: in STD_LOGIC;

SV : in STD_LOGIC

SL : in STD_LOGIC;

SR : in STD_LOGIC;

IV : in STD_LOGIC;

ILL : in STD_LOGIC;

ILO: in STD_LOGIC;

IR: in STD_LOGIC;

IA : in STD_LOGIC;

B1 : in STD_LOGIC;

B2 : in STD_LOGIC;

End Nivel_FSM;

Architecture Behavioral of Nivel_FSM is

Type estados is (S0,S1,S2,S3,S4);

Signal state_reg, state_netx: estados;

Begin

Process(clk, reset)

Begin

If reset = ‘1’ then

state_reg <= S0;

Elsif (clk’eent and clk=’1’) then

state_reg <= state_next;

end if;

end process;

process(state_reg, SV,SL, SR)

begin

IV <= ‘0’;

ILL <= ‘0’;

ILO <= ’0’;

IR < = ‘0’;

IA <= ‘0’

B1 <= ‘0’;

Case state_reg is

When S0 =>

IV <= ‘1’;

B1 <= ‘1’;

B2 <= ‘1’;

If SV = ‘1’ and SL=’0’ and SR=’0’ then

B1 <= ‘1’;

B2 <= ‘1’;

State_next <= S1;

End if

When S1 =>

ILL <= ‘1’;

B2 <= ‘1’;

If SV = ‘1’ and SL= ‘1’ and SR = ‘0’ then

B1 <= ‘1’;

B2 <= ‘0’;

State_next < = S2;

End if;

When S2 =>

ILO <= ‘1’;

B1 <=’1’;

B2 <= ‘0’;

If SV= ‘1’ AND SL=’1’ AND SR = ‘1’ then

B1 <= ‘0’;

B2 <= ‘0’;

State_next <= S3

End if;

When S3 =>

IR <= ‘1’;

B1 <= ‘0’;

B2 <=’0’;

If SV=’1’ AND SL = ‘0’ AND SR=’1’ THEN

B1 <= ‘0’;

B2 <= ‘0’;

State_next <= s4;

End if

When S4 =>

IA <= ‘1’;

If (SV = ‘0’ AND SL=’0’ AND SR=’0’) THEN

B1 <= ‘0’;

B2 <= ‘0’;

State_next <= S0;

Elsif (SV= ‘1’ AND SL = ‘0’ AND SR = ‘0’) THEN

B1 <=’1’;

B2 <= ‘0’;

State_next <= S2;

Elsif (SV = ‘1’ AND SL = ‘1’ AND SR = ‘1’) THEN

B1 <= ‘0’;

B2 <= ‘0’;

State_next <= S3;

End if;

End case;

End process;

End Behavioral

You might also like

- DSD Lab3 Fa20-Bce-029 PDFDocument5 pagesDSD Lab3 Fa20-Bce-029 PDFabdullahNo ratings yet

- Universidad Nacional Tecnologica de Lima SurDocument5 pagesUniversidad Nacional Tecnologica de Lima SurJoseph JesusNo ratings yet

- Universidad Nacional Tecnologica de Lima SurDocument5 pagesUniversidad Nacional Tecnologica de Lima SurJoseph JesusNo ratings yet

- 10100Document7 pages10100Đạt NguyễnNo ratings yet

- Exam1 (Example With Solutions)Document5 pagesExam1 (Example With Solutions)Rüya Gïbî100% (1)

- Trabajo de Diseño02Document10 pagesTrabajo de Diseño02Alvaro SegoviaNo ratings yet

- Trabajo de Diseño02Document10 pagesTrabajo de Diseño02Victor yurivilca lazoNo ratings yet

- лр 5 архDocument2 pagesлр 5 архspam trachNo ratings yet

- Structure of A Typical Digital SystemDocument29 pagesStructure of A Typical Digital SystemQasimNo ratings yet

- 수정 전 코드Document2 pages수정 전 코드붕붕부릉부릉No ratings yet

- Quadrature EncoderDocument5 pagesQuadrature EncoderJaime Santiago Sanchez ReinosoNo ratings yet

- Moore Machine VHDL CodeDocument2 pagesMoore Machine VHDL CodeKewl84No ratings yet

- BT3 TuvietDocument2 pagesBT3 TuvietChúc Văn KiênNo ratings yet

- SemaforoDocument2 pagesSemaforoVictor yurivilca lazoNo ratings yet

- Bài 1: Mạch giải mã BCD - 7 đoạn cho LED loại katot chungDocument9 pagesBài 1: Mạch giải mã BCD - 7 đoạn cho LED loại katot chungDoi Gio HuNo ratings yet

- Impletar en VHDL La Siguiente Maquina de EstadosDocument10 pagesImpletar en VHDL La Siguiente Maquina de EstadosGian SusanaNo ratings yet

- VHDL Codes For 32-Bit Processor: AARON T IMMANUEL (217-74-907)Document7 pagesVHDL Codes For 32-Bit Processor: AARON T IMMANUEL (217-74-907)adormentNo ratings yet

- FSM Design Verilog HDL PDFDocument7 pagesFSM Design Verilog HDL PDFajayNo ratings yet

- Lab11 - Achmad Mauludin - 165060301111002Document17 pagesLab11 - Achmad Mauludin - 165060301111002Mauudin BRgNo ratings yet

- Exp 2 - PIPODocument6 pagesExp 2 - PIPOAnkit GovindNo ratings yet

- Alu ArithmeticDocument7 pagesAlu ArithmeticTech-savvy GirishaNo ratings yet

- Beginning FPGA Programming - Partie41 PDFDocument5 pagesBeginning FPGA Programming - Partie41 PDFali alilouNo ratings yet

- Sequence Detector: Experiment No: 10 Activity: To Design and Simulate ' Sequence Detector of 101'' Using VHDLDocument2 pagesSequence Detector: Experiment No: 10 Activity: To Design and Simulate ' Sequence Detector of 101'' Using VHDLSaurabh KhandelwalNo ratings yet

- MemoriaDocument10 pagesMemoriaAlvaroNo ratings yet

- Name:waqar Baig SID:8878: Assignment) Design A FSM To Detect SequenceDocument4 pagesName:waqar Baig SID:8878: Assignment) Design A FSM To Detect Sequencesyed talibNo ratings yet

- Moore 1011 Overlapping SequenceDocument7 pagesMoore 1011 Overlapping Sequencedinesh100% (1)

- Chuong Trinh Den Giao ThongDocument2 pagesChuong Trinh Den Giao ThongHồng PhượngNo ratings yet

- AIM OF THE EXPERIMENT:-Binary To Decimal, Gray Code Apparatus RequiredDocument8 pagesAIM OF THE EXPERIMENT:-Binary To Decimal, Gray Code Apparatus RequiredSai KaneNo ratings yet

- Dcs-Ii Lab File: - Anupam Sobti 17/EC/09Document19 pagesDcs-Ii Lab File: - Anupam Sobti 17/EC/09Ankit GoelNo ratings yet

- Using Case Statement VHDL Code:: Assignment 2Document15 pagesUsing Case Statement VHDL Code:: Assignment 2innovatorinnovatorNo ratings yet

- Binary 1's and 0's CounterDocument13 pagesBinary 1's and 0's CounterKetan SalviNo ratings yet

- MAQUINA DE ESTADOS1 (Autoguardado)Document19 pagesMAQUINA DE ESTADOS1 (Autoguardado)YealsatoNo ratings yet

- experiment 8 //design of FSM - Vending MachineDocument8 pagesexperiment 8 //design of FSM - Vending MachineRishabNo ratings yet

- VHDL Code For A D Flip FlopDocument9 pagesVHDL Code For A D Flip FlopYogesh KhollamNo ratings yet

- VHDL Interfacing ProgramsDocument22 pagesVHDL Interfacing ProgramsNithish ManjuNo ratings yet

- Electiva - CIRCUITOS SECUENCIALES EN VHDLDocument5 pagesElectiva - CIRCUITOS SECUENCIALES EN VHDLfer gutiNo ratings yet

- Bach Khoa University of Technology: Digital Systems Laboratory Prelab 4 Finite State MachineDocument11 pagesBach Khoa University of Technology: Digital Systems Laboratory Prelab 4 Finite State MachineMờ LanhNo ratings yet

- Problema 1 "Lavadora" Código VHDL ModuleDocument40 pagesProblema 1 "Lavadora" Código VHDL ModuleLeonardoNo ratings yet

- EE 360M - Digital Systems Design Using VHDL: Lizy K. John University of Texas at AustinDocument73 pagesEE 360M - Digital Systems Design Using VHDL: Lizy K. John University of Texas at AustindnachegariNo ratings yet

- FSM Modeling Using VHDL: Dr. Gaganpreet KaurDocument12 pagesFSM Modeling Using VHDL: Dr. Gaganpreet KaurjajaNo ratings yet

- Verilog Code - State MachinesDocument3 pagesVerilog Code - State MachinesvasuvlsiNo ratings yet

- FA (BHVR) - CodeDocument1 pageFA (BHVR) - Codebhslegion1498No ratings yet

- Ejemplos VHDLDocument5 pagesEjemplos VHDLLeón Emmanuel NNo ratings yet

- 1.-Programa de Secuencia (Latch D)Document7 pages1.-Programa de Secuencia (Latch D)andy77740No ratings yet

- Combinational Circuit2Document6 pagesCombinational Circuit2Rinki KarNo ratings yet

- Piranti Terprogram - FSMDocument8 pagesPiranti Terprogram - FSMnamirarizqi annisaNo ratings yet

- Lab 5 Firna FrilanisaDocument18 pagesLab 5 Firna FrilanisaFirna FrilanisaNo ratings yet

- Demo!: GoalDocument24 pagesDemo!: GoalVaibhaviNo ratings yet

- Entity Alu IsDocument3 pagesEntity Alu IsDiego Jarosky Chachayma FarfánNo ratings yet

- Lab # 11: This Lab Has Been Designed To Familiarize With The Design of A Keypad Scanner Using VHDL and Show The Output On The FPGA BoardDocument4 pagesLab # 11: This Lab Has Been Designed To Familiarize With The Design of A Keypad Scanner Using VHDL and Show The Output On The FPGA Boardshermeen445No ratings yet

- Lab10 Dice GameDocument10 pagesLab10 Dice GamePhuc Van NguyenNo ratings yet

- TopDocument1 pageTopayberkktural21No ratings yet

- Algorithmic State Machine (ASM) Charts: VHDL Code & Timing DiagramsDocument32 pagesAlgorithmic State Machine (ASM) Charts: VHDL Code & Timing DiagramsManuel Garay GutierrezNo ratings yet

- Rekonstrukt: FPGA Based Forth Development Environment / Forth Based FPGA Development EnvironmentDocument4 pagesRekonstrukt: FPGA Based Forth Development Environment / Forth Based FPGA Development EnvironmentSuraj Kumar100% (1)

- Họ và tên: Lê Hồng Phú MSSV: 41801040 Bài tập 6 - buổi học 20211030Document8 pagesHọ và tên: Lê Hồng Phú MSSV: 41801040 Bài tập 6 - buổi học 20211030Hồng PhúNo ratings yet

- Lab 1 ReportDocument7 pagesLab 1 ReportNguyễn ThắngNo ratings yet

- Program I: To Simulate and Gate: Digital Circuits and Systems - Ii LabDocument72 pagesProgram I: To Simulate and Gate: Digital Circuits and Systems - Ii LabVarun GuptaNo ratings yet

- EXC11Document4 pagesEXC11Rishi KeshNo ratings yet

- Digital Design With SM ChartsDocument26 pagesDigital Design With SM ChartsAmar NathNo ratings yet