Professional Documents

Culture Documents

0 ratings0% found this document useful (0 votes)

14 viewsBig Question

Big Question

Uploaded by

Abinaya TThis document outlines a test for an Electronic Circuits I course, including:

- 3 parts (B, C, and D) containing multiple choice and numerical questions.

- Part B contains 3 questions, each with 2 sub-questions worth 12 marks. Topics include compensation techniques in BJTs, voltage divider bias, and small signal analysis of amplifiers.

- Part C contains 1 question with 2 sub-questions worth 14 marks, involving designing a voltage divider bias circuit and evaluating small signal voltage gain.

- The test was prepared by the Head of Department P. Manoj for second year ECE students, with a maximum mark of 50 over 1.5 hours.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You might also like

- An Introduction To TattvasDocument13 pagesAn Introduction To TattvasTemple of the stars83% (6)

- Chapter6 Ex SolDocument26 pagesChapter6 Ex SolShivani YadavNo ratings yet

- SRL NVQ Tech TestDocument4 pagesSRL NVQ Tech TestShohan TaylorNo ratings yet

- Feedback Part of A System (Dylan Wiliam)Document4 pagesFeedback Part of A System (Dylan Wiliam)ajmccarthynzNo ratings yet

- Question Paper Code:: Reg. No.Document3 pagesQuestion Paper Code:: Reg. No.Samraj JebasinghNo ratings yet

- EC8351 EC I ModelDocument2 pagesEC8351 EC I ModelDeepak RameshNo ratings yet

- 20A04101T Electronic Devices & CircuitsDocument2 pages20A04101T Electronic Devices & CircuitsSiddu Charan GurramNo ratings yet

- Ec-101 - Final PDFDocument2 pagesEc-101 - Final PDFarjunv_14No ratings yet

- Analog Circuits: Time Allotted: 3 Hrs Full Marks: 70Document4 pagesAnalog Circuits: Time Allotted: 3 Hrs Full Marks: 70Vikash KumarNo ratings yet

- EC21101 Basic Electronics ES 2018Document4 pagesEC21101 Basic Electronics ES 2018Santanu KunduNo ratings yet

- Basic Electronics (ECEN 1011) : Time Allotted: 3 Hrs. Full Marks: 70Document4 pagesBasic Electronics (ECEN 1011) : Time Allotted: 3 Hrs. Full Marks: 70014 Debayan Kumar GhoshNo ratings yet

- EDC - Old Question Papers For Unit 3, 4, 5Document19 pagesEDC - Old Question Papers For Unit 3, 4, 5Deepak SahuNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)GOJAN ECENo ratings yet

- EDC Model PapersDocument12 pagesEDC Model PapersanithaNo ratings yet

- KTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedDocument16 pagesKTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedsunNo ratings yet

- ECE201CDocument2 pagesECE201CMahakNo ratings yet

- 1 Ec205 Electronic Circuits (Ae, Ec)Document2 pages1 Ec205 Electronic Circuits (Ae, Ec)ABHILESH G KNo ratings yet

- WWW - Manaresults.Co - In: (Common To Eee, Ece, Cse, Eie, It, Etm, MCT)Document2 pagesWWW - Manaresults.Co - In: (Common To Eee, Ece, Cse, Eie, It, Etm, MCT)Roman CenaNo ratings yet

- BMS College of Engineering, Bangalore-560019: December 2015 Semester End Main ExaminationsDocument3 pagesBMS College of Engineering, Bangalore-560019: December 2015 Semester End Main ExaminationsrameshNo ratings yet

- B. Sc. EXAMINATION, 2020: No. of Printed Pages: 06 Roll No. ......................Document6 pagesB. Sc. EXAMINATION, 2020: No. of Printed Pages: 06 Roll No. ......................Vishal TanwarNo ratings yet

- Code: 20A02101TDocument2 pagesCode: 20A02101Tkurubamailagani ravaliNo ratings yet

- CT3 QP-18EES101J BEEE - Set2Document2 pagesCT3 QP-18EES101J BEEE - Set2skarthikpriyaNo ratings yet

- r5100207 Electronic Devices and CircuitsDocument4 pagesr5100207 Electronic Devices and CircuitssivabharathamurthyNo ratings yet

- 22216-2023-Summer-Question-Paper (Msbte Study Resources)Document4 pages22216-2023-Summer-Question-Paper (Msbte Study Resources)rampatil290905No ratings yet

- Basic Electronics Rec201 1Document4 pagesBasic Electronics Rec201 1ranveeryadav3710No ratings yet

- December 2016: AMIETE - ET (Current & New Scheme)Document3 pagesDecember 2016: AMIETE - ET (Current & New Scheme)mraavulaNo ratings yet

- Ec 2 UniversityDocument2 pagesEc 2 UniversityPrabu KumarNo ratings yet

- CT3 QP-18EES101J BEEE - Set1Document2 pagesCT3 QP-18EES101J BEEE - Set1skarthikpriyaNo ratings yet

- Ee 3 Sem Electronic Devices and Circuits 2016Document3 pagesEe 3 Sem Electronic Devices and Circuits 2016Priyanshu AgaseNo ratings yet

- Analog Electronics (0500625) SET 1Document8 pagesAnalog Electronics (0500625) SET 1Avinash PandeyNo ratings yet

- C1EC01-C1405 - ELECTRONIC CIRCUIT ANALYSIS & DESIGN MergedDocument18 pagesC1EC01-C1405 - ELECTRONIC CIRCUIT ANALYSIS & DESIGN Mergedchini_naniNo ratings yet

- Eee Ec I Set IDocument3 pagesEee Ec I Set IkisnamohanNo ratings yet

- 313ect06 Ec-IDocument2 pages313ect06 Ec-IramkumarrajaNo ratings yet

- r05210404 Electronic Circuit Analysis November 2008Document8 pagesr05210404 Electronic Circuit Analysis November 2008Tamire santhosh mohanNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument4 pages3 Hours / 70 Marks: Seat NoThanos LadNo ratings yet

- EC8351-Electronic Circuits IDocument2 pagesEC8351-Electronic Circuits Isyed1188No ratings yet

- Ex05 - Question Paper Ada Te-1Document2 pagesEx05 - Question Paper Ada Te-1shankarNo ratings yet

- Set - A Beee QPDocument2 pagesSet - A Beee QPThiaga RajanNo ratings yet

- Answer Answer All Questions, Each Carries 3 MarksDocument2 pagesAnswer Answer All Questions, Each Carries 3 MarksAjayShankarNo ratings yet

- Attempt All Sections. If Require Any Missing Data Then Choose SuitablyDocument3 pagesAttempt All Sections. If Require Any Missing Data Then Choose Suitablypcjoshi02No ratings yet

- Eec Final Set 2Document3 pagesEec Final Set 2Said RahmanNo ratings yet

- 13A99101 Basic Electrial & Electronics EngineeringDocument2 pages13A99101 Basic Electrial & Electronics EngineeringjagadeeshNo ratings yet

- FEE Model 1Document2 pagesFEE Model 1amangamingofficial2020No ratings yet

- Semiconductors - DPP 02Document3 pagesSemiconductors - DPP 02mv7602456No ratings yet

- WWW - Manaresults.Co - In: (Common To Eee, Ece, Cse, Eie, It, MCT)Document2 pagesWWW - Manaresults.Co - In: (Common To Eee, Ece, Cse, Eie, It, MCT)pramodNo ratings yet

- Eet205 Analog Electronics, December 2021Document3 pagesEet205 Analog Electronics, December 2021Midun RamkumarNo ratings yet

- Electronic Devices and Circuits: C2 Review Test: Date: 14/07/2021 Scaled MM 30 Duration: 2 HrsDocument5 pagesElectronic Devices and Circuits: C2 Review Test: Date: 14/07/2021 Scaled MM 30 Duration: 2 HrsSai Kiran Reddy VantedduNo ratings yet

- 22216-2023-Winter-Question-Paper (Msbte Study Resources)Document4 pages22216-2023-Winter-Question-Paper (Msbte Study Resources)rampatil290905No ratings yet

- Btech Ee 8 Sem Power System Dynamics and Control 2012Document4 pagesBtech Ee 8 Sem Power System Dynamics and Control 2012Swagatam BanerjeeNo ratings yet

- PUE Question Paper Format - 100 MarksDocument3 pagesPUE Question Paper Format - 100 MarksnupurnehaNo ratings yet

- End Term E3 238Document6 pagesEnd Term E3 238bommena vishwa tejaNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityRushabh PatelNo ratings yet

- r5100406 Network AnalysisDocument2 pagesr5100406 Network AnalysissivabharathamurthyNo ratings yet

- 22225-2023-Winter-Question-Paper (Msbte Study Resources)Document4 pages22225-2023-Winter-Question-Paper (Msbte Study Resources)Ronit PatilNo ratings yet

- 2022 Summer Question Paper (Msbte Study Resources)Document4 pages2022 Summer Question Paper (Msbte Study Resources)xilaci9315No ratings yet

- 3 Hours / 70 Marks: Seat NoDocument4 pages3 Hours / 70 Marks: Seat NoMeet TodankarNo ratings yet

- QP D15 De57 PDFDocument3 pagesQP D15 De57 PDFRajashekarBalyaNo ratings yet

- ADE Papaer IDocument3 pagesADE Papaer IPrabhat MishraNo ratings yet

- Ec8252ed Set2 PDFDocument2 pagesEc8252ed Set2 PDFRajkumar PerumalNo ratings yet

- 4th Sem 2022 MidsemDocument6 pages4th Sem 2022 MidsemAditya KumarNo ratings yet

- Analog Circuits (Ecen 2101)Document5 pagesAnalog Circuits (Ecen 2101)sumitbhuia10No ratings yet

- Electromagnetic Compatibility (EMC) Design and Test Case AnalysisFrom EverandElectromagnetic Compatibility (EMC) Design and Test Case AnalysisNo ratings yet

- National Hospital's GarmentsDocument1 pageNational Hospital's GarmentsShekhar GuptaNo ratings yet

- Scorpio SCDC LHD Mhawk Eiii v2 Mar12Document154 pagesScorpio SCDC LHD Mhawk Eiii v2 Mar12Romel Bladimir Valenzuela ValenzuelaNo ratings yet

- Europe & ThailandDocument1 pageEurope & ThailandTipitaka TripitakaNo ratings yet

- Shady Othman Nour El Deen: Doha, QatarDocument3 pagesShady Othman Nour El Deen: Doha, QatarHatem HusseinNo ratings yet

- Affidavit of Loss - Bir.or - Car.1.2020Document1 pageAffidavit of Loss - Bir.or - Car.1.2020black stalkerNo ratings yet

- DZ (S) FlyerDocument2 pagesDZ (S) FlyerIjjat IjjudinNo ratings yet

- Toaz - Info Learn Wordpress From Scratch PRDocument103 pagesToaz - Info Learn Wordpress From Scratch PRAhmed Wa SsiNo ratings yet

- Case Study On Akshaya Patra Group-1Document9 pagesCase Study On Akshaya Patra Group-1swaroopNo ratings yet

- SyllabusDocument6 pagesSyllabusMadhu ChauhanNo ratings yet

- UntitledDocument292 pagesUntitledD17CQAT01-N LE THANH TUANNo ratings yet

- TR - 2D Game Art Development NC IIIDocument66 pagesTR - 2D Game Art Development NC IIIfor pokeNo ratings yet

- GEN005 - Quiz 2 ANSWER KEYDocument4 pagesGEN005 - Quiz 2 ANSWER KEYELLE WOODS0% (1)

- List - Parts of Bahay Na Bato - Filipiniana 101Document7 pagesList - Parts of Bahay Na Bato - Filipiniana 101Eriellynn Liza100% (1)

- Champschicken Com Seocheck 2020 12 17Document17 pagesChampschicken Com Seocheck 2020 12 17Dayanand baraNo ratings yet

- Past Tenses ReviewDocument9 pagesPast Tenses ReviewmariaNo ratings yet

- Perfetti Van MelleDocument24 pagesPerfetti Van MelleYahya Niazi100% (1)

- OutputDocument39 pagesOutputRuben Condori Canaviri100% (2)

- Stem Cells InformationDocument2 pagesStem Cells InformationPauline ZwanikkenNo ratings yet

- Wax-Las Vegas Bus TimingsDocument4 pagesWax-Las Vegas Bus TimingsLuvNo ratings yet

- Case Study 1: The London 2012 Olympic Stadium 1. The ProjectDocument15 pagesCase Study 1: The London 2012 Olympic Stadium 1. The ProjectIván Comprés GuzmánNo ratings yet

- Heresite Corrosion ProtectionDocument2 pagesHeresite Corrosion ProtectionDANIEL PEREZNo ratings yet

- OISD ChecklistDocument3 pagesOISD ChecklistLoganathan DharmarNo ratings yet

- CESTARO - Plan-Tonificacion Inicial MujerDocument14 pagesCESTARO - Plan-Tonificacion Inicial MujerLucas Javier VidalNo ratings yet

- Professional Diploma in Marketing: Reading List 2011 - 2012Document6 pagesProfessional Diploma in Marketing: Reading List 2011 - 2012yaqub19799141100% (1)

- Ni Based Superalloy: Casting Technology, Metallurgy, Development, Properties and ApplicationsDocument46 pagesNi Based Superalloy: Casting Technology, Metallurgy, Development, Properties and ApplicationsffazlaliNo ratings yet

- Group Assignment 2Document2 pagesGroup Assignment 2zinilNo ratings yet

- Chapter 123 Final Na!!!Document34 pagesChapter 123 Final Na!!!Ricell Joy RocamoraNo ratings yet

- PANASONIC sdr-h100-h101Document73 pagesPANASONIC sdr-h100-h101Marco RamosNo ratings yet

Big Question

Big Question

Uploaded by

Abinaya T0 ratings0% found this document useful (0 votes)

14 views2 pagesThis document outlines a test for an Electronic Circuits I course, including:

- 3 parts (B, C, and D) containing multiple choice and numerical questions.

- Part B contains 3 questions, each with 2 sub-questions worth 12 marks. Topics include compensation techniques in BJTs, voltage divider bias, and small signal analysis of amplifiers.

- Part C contains 1 question with 2 sub-questions worth 14 marks, involving designing a voltage divider bias circuit and evaluating small signal voltage gain.

- The test was prepared by the Head of Department P. Manoj for second year ECE students, with a maximum mark of 50 over 1.5 hours.

Original Description:

Original Title

big question

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document outlines a test for an Electronic Circuits I course, including:

- 3 parts (B, C, and D) containing multiple choice and numerical questions.

- Part B contains 3 questions, each with 2 sub-questions worth 12 marks. Topics include compensation techniques in BJTs, voltage divider bias, and small signal analysis of amplifiers.

- Part C contains 1 question with 2 sub-questions worth 14 marks, involving designing a voltage divider bias circuit and evaluating small signal voltage gain.

- The test was prepared by the Head of Department P. Manoj for second year ECE students, with a maximum mark of 50 over 1.5 hours.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

0 ratings0% found this document useful (0 votes)

14 views2 pagesBig Question

Big Question

Uploaded by

Abinaya TThis document outlines a test for an Electronic Circuits I course, including:

- 3 parts (B, C, and D) containing multiple choice and numerical questions.

- Part B contains 3 questions, each with 2 sub-questions worth 12 marks. Topics include compensation techniques in BJTs, voltage divider bias, and small signal analysis of amplifiers.

- Part C contains 1 question with 2 sub-questions worth 14 marks, involving designing a voltage divider bias circuit and evaluating small signal voltage gain.

- The test was prepared by the Head of Department P. Manoj for second year ECE students, with a maximum mark of 50 over 1.5 hours.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

You are on page 1of 2

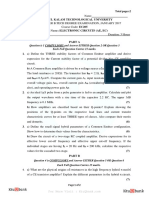

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

ACADEMIC YEAR 2018-2019 (ODD SEMESTER) Prepared By HOD

PART B&C QUESTION TEST [P.MANOJ]

Sub. Code &Name: EC8351– ELECTRONIC CIRCUITS I Date:08/10/2018

Year/branch/section: II-ECE Session &Duration: FN & 1hr 30 min.

Semester: 03 Max. Mark: 50 DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

ACADEMIC YEAR 2018-2019 (ODD SEMESTER)

PART B (3×12=36) (Answer all Questions under “either or “ type)

PART B&C QUESTION TEST

1 a) What are the types of compensation technique in BJT? and explain all Sub. Code &Name: EC8351– ELECTRONIC CIRCUITS I Date:08/10/2018

the Compensation techniques in detail. (12) Year/branch/section: II-ECE Session &Duration: FN & 1hr 30 min.

(OR) Semester: 03 Max. Mark: 50

b) Construct voltage divider bias of BJT and formulate the Stability PART B (3×12=36) (Answer all Questions under “either or “ type)

factors. (12) 1 a) What are the types of compensation technique in BJT? and explain all

the Compensation techniques in detail. (12)

2 a) Discuss in detail about the small signal analysis of common source

amplifier with un bypassed capacitor (12) (OR)

(OR) b) Construct voltage divider bias of BJT and formulate the Stability

factors. (12)

b) Construct the small signal equivalent model of CC amplifier circuit

and analyze the circuit to obtain its gain, input and output impedance. (12) 2 a) Discuss in detail about the small signal analysis of common source

amplifier with un bypassed capacitor (12)

3 a) Discuss in detail about the analysis of Darlington amplifier and derive

an expression for Ai and Ri. (12) (OR)

(OR) b) Construct the small signal equivalent model of CC amplifier circuit

and analyze the circuit to obtain its gain, input and output impedance. (12)

b) Sketch emitter coupled differential amplifier and determine the

differential Mode gain, Common mode gain and CMRR. (12) 3 a) Discuss in detail about the analysis of Darlington amplifier and derive

an expression for Ai and Ri. (12)

PART C (1×14=14) (Answer all Questions under “either or “ type) (OR)

4 a) Design the voltage divider bias circuit to have V CE=VE=5V, the (14) b) Sketch emitter coupled differential amplifier and determine the

supply voltage is 15V, Assume the transistor hfe is 100 and ICQ=4mA. differential Mode gain, Common mode gain and CMRR. (12)

(OR)

b) Experiment the circuit shown in figure and evaluate the small signal PART C (1×14=14) (Answer all Questions under “either or “ type)

voltage gain assume. Idss=12mA,Vp=-4V and λ =0.005V-1 4 a) Design the voltage divider bias circuit to have V CE=VE=5V, the (14)

supply voltage is 15V, Assume the transistor hfe is 100 and ICQ=4mA.

(OR)

b) Experiment the circuit shown in figure and evaluate the small signal

voltage gain assume Idss=12mA,Vp=-4V and λ =0.005V-1

Prepared By HOD

[P.MANOJ]

You might also like

- An Introduction To TattvasDocument13 pagesAn Introduction To TattvasTemple of the stars83% (6)

- Chapter6 Ex SolDocument26 pagesChapter6 Ex SolShivani YadavNo ratings yet

- SRL NVQ Tech TestDocument4 pagesSRL NVQ Tech TestShohan TaylorNo ratings yet

- Feedback Part of A System (Dylan Wiliam)Document4 pagesFeedback Part of A System (Dylan Wiliam)ajmccarthynzNo ratings yet

- Question Paper Code:: Reg. No.Document3 pagesQuestion Paper Code:: Reg. No.Samraj JebasinghNo ratings yet

- EC8351 EC I ModelDocument2 pagesEC8351 EC I ModelDeepak RameshNo ratings yet

- 20A04101T Electronic Devices & CircuitsDocument2 pages20A04101T Electronic Devices & CircuitsSiddu Charan GurramNo ratings yet

- Ec-101 - Final PDFDocument2 pagesEc-101 - Final PDFarjunv_14No ratings yet

- Analog Circuits: Time Allotted: 3 Hrs Full Marks: 70Document4 pagesAnalog Circuits: Time Allotted: 3 Hrs Full Marks: 70Vikash KumarNo ratings yet

- EC21101 Basic Electronics ES 2018Document4 pagesEC21101 Basic Electronics ES 2018Santanu KunduNo ratings yet

- Basic Electronics (ECEN 1011) : Time Allotted: 3 Hrs. Full Marks: 70Document4 pagesBasic Electronics (ECEN 1011) : Time Allotted: 3 Hrs. Full Marks: 70014 Debayan Kumar GhoshNo ratings yet

- EDC - Old Question Papers For Unit 3, 4, 5Document19 pagesEDC - Old Question Papers For Unit 3, 4, 5Deepak SahuNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)GOJAN ECENo ratings yet

- EDC Model PapersDocument12 pagesEDC Model PapersanithaNo ratings yet

- KTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedDocument16 pagesKTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedsunNo ratings yet

- ECE201CDocument2 pagesECE201CMahakNo ratings yet

- 1 Ec205 Electronic Circuits (Ae, Ec)Document2 pages1 Ec205 Electronic Circuits (Ae, Ec)ABHILESH G KNo ratings yet

- WWW - Manaresults.Co - In: (Common To Eee, Ece, Cse, Eie, It, Etm, MCT)Document2 pagesWWW - Manaresults.Co - In: (Common To Eee, Ece, Cse, Eie, It, Etm, MCT)Roman CenaNo ratings yet

- BMS College of Engineering, Bangalore-560019: December 2015 Semester End Main ExaminationsDocument3 pagesBMS College of Engineering, Bangalore-560019: December 2015 Semester End Main ExaminationsrameshNo ratings yet

- B. Sc. EXAMINATION, 2020: No. of Printed Pages: 06 Roll No. ......................Document6 pagesB. Sc. EXAMINATION, 2020: No. of Printed Pages: 06 Roll No. ......................Vishal TanwarNo ratings yet

- Code: 20A02101TDocument2 pagesCode: 20A02101Tkurubamailagani ravaliNo ratings yet

- CT3 QP-18EES101J BEEE - Set2Document2 pagesCT3 QP-18EES101J BEEE - Set2skarthikpriyaNo ratings yet

- r5100207 Electronic Devices and CircuitsDocument4 pagesr5100207 Electronic Devices and CircuitssivabharathamurthyNo ratings yet

- 22216-2023-Summer-Question-Paper (Msbte Study Resources)Document4 pages22216-2023-Summer-Question-Paper (Msbte Study Resources)rampatil290905No ratings yet

- Basic Electronics Rec201 1Document4 pagesBasic Electronics Rec201 1ranveeryadav3710No ratings yet

- December 2016: AMIETE - ET (Current & New Scheme)Document3 pagesDecember 2016: AMIETE - ET (Current & New Scheme)mraavulaNo ratings yet

- Ec 2 UniversityDocument2 pagesEc 2 UniversityPrabu KumarNo ratings yet

- CT3 QP-18EES101J BEEE - Set1Document2 pagesCT3 QP-18EES101J BEEE - Set1skarthikpriyaNo ratings yet

- Ee 3 Sem Electronic Devices and Circuits 2016Document3 pagesEe 3 Sem Electronic Devices and Circuits 2016Priyanshu AgaseNo ratings yet

- Analog Electronics (0500625) SET 1Document8 pagesAnalog Electronics (0500625) SET 1Avinash PandeyNo ratings yet

- C1EC01-C1405 - ELECTRONIC CIRCUIT ANALYSIS & DESIGN MergedDocument18 pagesC1EC01-C1405 - ELECTRONIC CIRCUIT ANALYSIS & DESIGN Mergedchini_naniNo ratings yet

- Eee Ec I Set IDocument3 pagesEee Ec I Set IkisnamohanNo ratings yet

- 313ect06 Ec-IDocument2 pages313ect06 Ec-IramkumarrajaNo ratings yet

- r05210404 Electronic Circuit Analysis November 2008Document8 pagesr05210404 Electronic Circuit Analysis November 2008Tamire santhosh mohanNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument4 pages3 Hours / 70 Marks: Seat NoThanos LadNo ratings yet

- EC8351-Electronic Circuits IDocument2 pagesEC8351-Electronic Circuits Isyed1188No ratings yet

- Ex05 - Question Paper Ada Te-1Document2 pagesEx05 - Question Paper Ada Te-1shankarNo ratings yet

- Set - A Beee QPDocument2 pagesSet - A Beee QPThiaga RajanNo ratings yet

- Answer Answer All Questions, Each Carries 3 MarksDocument2 pagesAnswer Answer All Questions, Each Carries 3 MarksAjayShankarNo ratings yet

- Attempt All Sections. If Require Any Missing Data Then Choose SuitablyDocument3 pagesAttempt All Sections. If Require Any Missing Data Then Choose Suitablypcjoshi02No ratings yet

- Eec Final Set 2Document3 pagesEec Final Set 2Said RahmanNo ratings yet

- 13A99101 Basic Electrial & Electronics EngineeringDocument2 pages13A99101 Basic Electrial & Electronics EngineeringjagadeeshNo ratings yet

- FEE Model 1Document2 pagesFEE Model 1amangamingofficial2020No ratings yet

- Semiconductors - DPP 02Document3 pagesSemiconductors - DPP 02mv7602456No ratings yet

- WWW - Manaresults.Co - In: (Common To Eee, Ece, Cse, Eie, It, MCT)Document2 pagesWWW - Manaresults.Co - In: (Common To Eee, Ece, Cse, Eie, It, MCT)pramodNo ratings yet

- Eet205 Analog Electronics, December 2021Document3 pagesEet205 Analog Electronics, December 2021Midun RamkumarNo ratings yet

- Electronic Devices and Circuits: C2 Review Test: Date: 14/07/2021 Scaled MM 30 Duration: 2 HrsDocument5 pagesElectronic Devices and Circuits: C2 Review Test: Date: 14/07/2021 Scaled MM 30 Duration: 2 HrsSai Kiran Reddy VantedduNo ratings yet

- 22216-2023-Winter-Question-Paper (Msbte Study Resources)Document4 pages22216-2023-Winter-Question-Paper (Msbte Study Resources)rampatil290905No ratings yet

- Btech Ee 8 Sem Power System Dynamics and Control 2012Document4 pagesBtech Ee 8 Sem Power System Dynamics and Control 2012Swagatam BanerjeeNo ratings yet

- PUE Question Paper Format - 100 MarksDocument3 pagesPUE Question Paper Format - 100 MarksnupurnehaNo ratings yet

- End Term E3 238Document6 pagesEnd Term E3 238bommena vishwa tejaNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityRushabh PatelNo ratings yet

- r5100406 Network AnalysisDocument2 pagesr5100406 Network AnalysissivabharathamurthyNo ratings yet

- 22225-2023-Winter-Question-Paper (Msbte Study Resources)Document4 pages22225-2023-Winter-Question-Paper (Msbte Study Resources)Ronit PatilNo ratings yet

- 2022 Summer Question Paper (Msbte Study Resources)Document4 pages2022 Summer Question Paper (Msbte Study Resources)xilaci9315No ratings yet

- 3 Hours / 70 Marks: Seat NoDocument4 pages3 Hours / 70 Marks: Seat NoMeet TodankarNo ratings yet

- QP D15 De57 PDFDocument3 pagesQP D15 De57 PDFRajashekarBalyaNo ratings yet

- ADE Papaer IDocument3 pagesADE Papaer IPrabhat MishraNo ratings yet

- Ec8252ed Set2 PDFDocument2 pagesEc8252ed Set2 PDFRajkumar PerumalNo ratings yet

- 4th Sem 2022 MidsemDocument6 pages4th Sem 2022 MidsemAditya KumarNo ratings yet

- Analog Circuits (Ecen 2101)Document5 pagesAnalog Circuits (Ecen 2101)sumitbhuia10No ratings yet

- Electromagnetic Compatibility (EMC) Design and Test Case AnalysisFrom EverandElectromagnetic Compatibility (EMC) Design and Test Case AnalysisNo ratings yet

- National Hospital's GarmentsDocument1 pageNational Hospital's GarmentsShekhar GuptaNo ratings yet

- Scorpio SCDC LHD Mhawk Eiii v2 Mar12Document154 pagesScorpio SCDC LHD Mhawk Eiii v2 Mar12Romel Bladimir Valenzuela ValenzuelaNo ratings yet

- Europe & ThailandDocument1 pageEurope & ThailandTipitaka TripitakaNo ratings yet

- Shady Othman Nour El Deen: Doha, QatarDocument3 pagesShady Othman Nour El Deen: Doha, QatarHatem HusseinNo ratings yet

- Affidavit of Loss - Bir.or - Car.1.2020Document1 pageAffidavit of Loss - Bir.or - Car.1.2020black stalkerNo ratings yet

- DZ (S) FlyerDocument2 pagesDZ (S) FlyerIjjat IjjudinNo ratings yet

- Toaz - Info Learn Wordpress From Scratch PRDocument103 pagesToaz - Info Learn Wordpress From Scratch PRAhmed Wa SsiNo ratings yet

- Case Study On Akshaya Patra Group-1Document9 pagesCase Study On Akshaya Patra Group-1swaroopNo ratings yet

- SyllabusDocument6 pagesSyllabusMadhu ChauhanNo ratings yet

- UntitledDocument292 pagesUntitledD17CQAT01-N LE THANH TUANNo ratings yet

- TR - 2D Game Art Development NC IIIDocument66 pagesTR - 2D Game Art Development NC IIIfor pokeNo ratings yet

- GEN005 - Quiz 2 ANSWER KEYDocument4 pagesGEN005 - Quiz 2 ANSWER KEYELLE WOODS0% (1)

- List - Parts of Bahay Na Bato - Filipiniana 101Document7 pagesList - Parts of Bahay Na Bato - Filipiniana 101Eriellynn Liza100% (1)

- Champschicken Com Seocheck 2020 12 17Document17 pagesChampschicken Com Seocheck 2020 12 17Dayanand baraNo ratings yet

- Past Tenses ReviewDocument9 pagesPast Tenses ReviewmariaNo ratings yet

- Perfetti Van MelleDocument24 pagesPerfetti Van MelleYahya Niazi100% (1)

- OutputDocument39 pagesOutputRuben Condori Canaviri100% (2)

- Stem Cells InformationDocument2 pagesStem Cells InformationPauline ZwanikkenNo ratings yet

- Wax-Las Vegas Bus TimingsDocument4 pagesWax-Las Vegas Bus TimingsLuvNo ratings yet

- Case Study 1: The London 2012 Olympic Stadium 1. The ProjectDocument15 pagesCase Study 1: The London 2012 Olympic Stadium 1. The ProjectIván Comprés GuzmánNo ratings yet

- Heresite Corrosion ProtectionDocument2 pagesHeresite Corrosion ProtectionDANIEL PEREZNo ratings yet

- OISD ChecklistDocument3 pagesOISD ChecklistLoganathan DharmarNo ratings yet

- CESTARO - Plan-Tonificacion Inicial MujerDocument14 pagesCESTARO - Plan-Tonificacion Inicial MujerLucas Javier VidalNo ratings yet

- Professional Diploma in Marketing: Reading List 2011 - 2012Document6 pagesProfessional Diploma in Marketing: Reading List 2011 - 2012yaqub19799141100% (1)

- Ni Based Superalloy: Casting Technology, Metallurgy, Development, Properties and ApplicationsDocument46 pagesNi Based Superalloy: Casting Technology, Metallurgy, Development, Properties and ApplicationsffazlaliNo ratings yet

- Group Assignment 2Document2 pagesGroup Assignment 2zinilNo ratings yet

- Chapter 123 Final Na!!!Document34 pagesChapter 123 Final Na!!!Ricell Joy RocamoraNo ratings yet

- PANASONIC sdr-h100-h101Document73 pagesPANASONIC sdr-h100-h101Marco RamosNo ratings yet