Professional Documents

Culture Documents

Testing & Testability

Testing & Testability

Uploaded by

SVCET SVCET0 ratings0% found this document useful (0 votes)

962 views1 pageThis document outlines the objectives, outcomes, and content of a course on Testing and Testability. The course covers modeling digital circuits, fault modeling, testing for single stuck faults, design for testability techniques like scan architectures, built-in self-test concepts, and memory BIST. It aims to introduce different modeling styles, fault detection fundamentals, test vector generation principles, and boundary scan standards. Students will learn about fault types, testing architectures, and identifying faulty components.

Original Description:

Copyright

© © All Rights Reserved

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document outlines the objectives, outcomes, and content of a course on Testing and Testability. The course covers modeling digital circuits, fault modeling, testing for single stuck faults, design for testability techniques like scan architectures, built-in self-test concepts, and memory BIST. It aims to introduce different modeling styles, fault detection fundamentals, test vector generation principles, and boundary scan standards. Students will learn about fault types, testing architectures, and identifying faulty components.

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

Download as doc, pdf, or txt

0 ratings0% found this document useful (0 votes)

962 views1 pageTesting & Testability

Testing & Testability

Uploaded by

SVCET SVCETThis document outlines the objectives, outcomes, and content of a course on Testing and Testability. The course covers modeling digital circuits, fault modeling, testing for single stuck faults, design for testability techniques like scan architectures, built-in self-test concepts, and memory BIST. It aims to introduce different modeling styles, fault detection fundamentals, test vector generation principles, and boundary scan standards. Students will learn about fault types, testing architectures, and identifying faulty components.

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

Download as doc, pdf, or txt

You are on page 1of 1

Sri Venkateswara College of Engineering and Technology, Chittoor.

(Autonomous)

L T P C

M.Tech- II Semester-VLSI Design 3 1 0 3

(15BVL13) TESTING & TESTABILITY

Objectives:

1. To introduce the different modeling styles in digital circuits.

2. To understand the fundamentals of fault detection in digital circuits.

3. To know the basic principles of test vector generation.

4. To understand the principle of boundary scan standards.

Outcomes:

After completion of the course, the student will be able to:

1. Describe the levels of modeling in digital circuits.

2. Get knowledge on single stuck faults and multiple stuck faults.

3. Understand the different testing architectures.

4. Identify faulty components with in a circuit.

UNIT I

INTRODUCTION TO TEST AND DESIGN FOR TESTABILITY (DFT)

FUNDAMENTALS: Modeling: Modeling Digital Circuits at Logic Level, Register Level

and Structural Models. Levels of Modeling. Logic Simulation: Types of Simulation,

Delay Models, Element Evaluation, Hazard Detection, Gate Level Event Driven

Simulation.

UNIT II

FAULT MODELING: Logic Fault Models, Fault Detection and Redundancy, Fault

Equivalence and Fault Location. Single Stuck and Multiple Stuck – Fault Models. Fault

Simulation Applications, General Techniques for Combinational Circuits.

TESTING FOR SINGLE STUCK FAULTS (SSF): Automated Test Pattern Generation

(ATPG/ATG) For Ssfs in Combinational and Sequential Circuits, Functional Testing

With Specific Fault Models

UNIT III

DESIGN FOR TESTABILITY: Testability Trade-Offs, Techniques. Scan Architectures

and Testing – Controllability and Absorbability, Generic Boundary Scan, Full

Integrated Scan, Storage Cells for Scan Design. Board Level and System Level DFT

Approaches. Boundary Scans Standards. Compression Techniques – Different

Techniques, Syndrome Test and Signature Analysis.

UNIT IV

BUILT-IN SELF-TEST (BIST): BIST Concepts and Test Pattern Generation. Specific

BIST Architectures – CSBL, BEST, RTS, LOCST, STUMPS, CBIST, CEBS, RTD, SST,

CATS, CSTP, BILBO. Brief Ideas on Some Advanced BIST Concepts and Design for

Self-Test at Board Level.

UNIT V

MEMORY BIST (MBIST): Memory Test Architectures and Techniques – Introduction

to Memory Test, Types of Memories and Integration, Embedded Memory Testing

Model. Memory Test Requirements for MBIST.

BRIEF IDEAS ON EMBEDDED CORE TESTING: Introduction to Automatic in

Circuit Testing (ICT), JTAG Testing Features.

TEXT BOOKS:

1.Miron Abramovici, Melvin A. Breur, Arthur D.Friedman, Digital Systems Testing and

Testable Design, Jaico Publishing House, 2001.

2.Alfred Crouch, Design for Test for Digital ICs & Embedded Core Systems, Prentice

Hall.

REFERENCES:

1.Robert J.Feugate, Jr., Steven M.Mentyn, Introduction to VLSI Testing, Prentice

Hall, Englehood Cliffs, 1998.

2.Essentials of Electronic Testing for Digital, Memory and Mixed Signal VLSI Circuits

- M.L. Bushnell, V. D. Agrawal, Kluwer Academic Pulishers.

3. Digital Circuits Testing and Testability - P.K. Lala, Academic Press.

You might also like

- Fault Tolerant & Fault Testable Hardware DesignFrom EverandFault Tolerant & Fault Testable Hardware DesignRating: 5 out of 5 stars5/5 (2)

- IEEE Standard For Three-Phase, Manually Operated Subsurface Load Interrupting Switches For Alternating-Current SystemsDocument33 pagesIEEE Standard For Three-Phase, Manually Operated Subsurface Load Interrupting Switches For Alternating-Current SystemsukritNo ratings yet

- JTAG TutorialDocument6 pagesJTAG Tutorialmrunal1729No ratings yet

- Digital Systems Testing and Testable DesignDocument3 pagesDigital Systems Testing and Testable DesignSebastin SureshNo ratings yet

- Design For Test by Alfred L CrouchDocument117 pagesDesign For Test by Alfred L CrouchEdwin Singh100% (1)

- Vlsi/Fpga Design and Test CAD Tool Flow in Mentor Graphics: Victor P. NelsonDocument44 pagesVlsi/Fpga Design and Test CAD Tool Flow in Mentor Graphics: Victor P. NelsonAvinash B RajNo ratings yet

- Controllability and ObservabilityDocument15 pagesControllability and ObservabilityaashishscribdNo ratings yet

- Lab4 TT PDFDocument7 pagesLab4 TT PDFAjay NaikNo ratings yet

- Table of Contents: The IDDQ MysteryDocument9 pagesTable of Contents: The IDDQ MysteryShweta SinhaNo ratings yet

- A Built-In Redundancy-Analysis Scheme For Self-Repairable Rams With Two-Level RedundancyDocument9 pagesA Built-In Redundancy-Analysis Scheme For Self-Repairable Rams With Two-Level RedundancyAman TyagiNo ratings yet

- Hierarchical Scan and Atpg For Two StageDocument24 pagesHierarchical Scan and Atpg For Two StageNeusilica school of VLSINo ratings yet

- Fastscan Tutorial v02Document55 pagesFastscan Tutorial v02Raghavendra MatturNo ratings yet

- BSDL-Boundary Scan PDFDocument17 pagesBSDL-Boundary Scan PDFChinmayNo ratings yet

- Ch3.Fault ModelingDocument47 pagesCh3.Fault ModelingMuhammad RizwanNo ratings yet

- What Are The Differences Between SIMULATION and SYNTHESISDocument12 pagesWhat Are The Differences Between SIMULATION and SYNTHESISiyanduraiNo ratings yet

- Vlsi Nit Asic Designer Vinay NvidiaDocument18 pagesVlsi Nit Asic Designer Vinay NvidiaMohan GillellaNo ratings yet

- Notes3 PDFDocument97 pagesNotes3 PDFrahulsportyNo ratings yet

- Jtag - AN IEEE 1149.1 STDDocument42 pagesJtag - AN IEEE 1149.1 STDkanchanstiwariNo ratings yet

- TSB DFT 006 AppnoteDocument45 pagesTSB DFT 006 AppnoteNitish KumarNo ratings yet

- VLSI Design Verification and Testing: Fault SimulationDocument5 pagesVLSI Design Verification and Testing: Fault Simulationnishantsoni90No ratings yet

- DFT - Design For Testability - Verified With Hardware EmulationDocument3 pagesDFT - Design For Testability - Verified With Hardware EmulationRod SbNo ratings yet

- Testing and Design-for-Testability (DFT) For Digital Integrated CircuitsDocument95 pagesTesting and Design-for-Testability (DFT) For Digital Integrated Circuitsnagabhairu anusha100% (1)

- Gate SimulationDocument10 pagesGate SimulationMahmoud WafaNo ratings yet

- Unit Viii Cmos Testing: DefinitionDocument22 pagesUnit Viii Cmos Testing: DefinitionlokeshwarrvrjcNo ratings yet

- Podem AlgorithmDocument4 pagesPodem AlgorithmPraveen Kumar ReddyNo ratings yet

- Vlsi TestingDocument79 pagesVlsi Testingkarnika143No ratings yet

- Lecture 1. Introduction PDFDocument112 pagesLecture 1. Introduction PDFAmandeep VaishNo ratings yet

- Io MultiplexingDocument19 pagesIo Multiplexingsubramanyam62No ratings yet

- Fault SimulationDocument65 pagesFault SimulationPrasanth MangipudiNo ratings yet

- System Verilog BasicsDocument82 pagesSystem Verilog BasicsTiger Gangappa AngadiNo ratings yet

- Tessent Glossary: Software Version 2016.3 September 2016Document34 pagesTessent Glossary: Software Version 2016.3 September 2016yaminiNo ratings yet

- L02 FaultModelingDocument15 pagesL02 FaultModelingAmit RohillaNo ratings yet

- SoC Verification Flow and Methodologies by Sivakumar PRDocument6 pagesSoC Verification Flow and Methodologies by Sivakumar PRAsvNo ratings yet

- Electronic Syatem Design PPT - Design For TestabilityDocument9 pagesElectronic Syatem Design PPT - Design For TestabilityAnoop Mathew0% (1)

- DFTDocument13 pagesDFTvishalbharate123No ratings yet

- SOC DFT Verification With Static Analysis and Formal Methods PDFDocument7 pagesSOC DFT Verification With Static Analysis and Formal Methods PDFSujit TikekarNo ratings yet

- Scan Through TAPDocument10 pagesScan Through TAPajayg_lmgNo ratings yet

- Stuck at FaultDocument6 pagesStuck at Faultamy2chang_1No ratings yet

- Tessent Memorybist and LogicbistDocument11 pagesTessent Memorybist and Logicbistshashindra KGNo ratings yet

- Structural Data Types: Wire and RegDocument25 pagesStructural Data Types: Wire and RegRAGUL RAJ SNo ratings yet

- Timing Paths: Timing Analysis Is Performed by Splitting The Design Into Different Paths Based OnDocument3 pagesTiming Paths: Timing Analysis Is Performed by Splitting The Design Into Different Paths Based OnNandaNo ratings yet

- Test PointsDocument21 pagesTest Pointsanusha killariNo ratings yet

- Scan Insertion Lab Observations: Vlsiguru DFT TrainingDocument2 pagesScan Insertion Lab Observations: Vlsiguru DFT TrainingsenthilkumarNo ratings yet

- Delay TestDocument49 pagesDelay TestAnonymous Tcj0QUNo ratings yet

- Systemverilog Advanced Verification Using Uvm: Engineer Explorer SeriesDocument52 pagesSystemverilog Advanced Verification Using Uvm: Engineer Explorer SeriesmadhukirNo ratings yet

- Adding Spare CellsDocument4 pagesAdding Spare CellsmanojkumarNo ratings yet

- Design For Test - DFT Q & A - Part 1Document3 pagesDesign For Test - DFT Q & A - Part 1Veeranjaneyulu Dhikonda0% (1)

- Texas Instruments Placement Paper May 2011Document5 pagesTexas Instruments Placement Paper May 2011Shayendra RajuNo ratings yet

- Week 3Document34 pagesWeek 3apoorvaNo ratings yet

- Cell-Aware: ImproveDocument5 pagesCell-Aware: ImproveSiva SreeramdasNo ratings yet

- DFT Insertion FlowDocument3 pagesDFT Insertion FlowamitwangooNo ratings yet

- Thesis On LFSRDocument104 pagesThesis On LFSRKaran RoyNo ratings yet

- VLSI Basics - VLSI Design FlowDocument5 pagesVLSI Basics - VLSI Design Flowsrinivas525No ratings yet

- Scan InsertionDocument40 pagesScan InsertionAmena FarhatNo ratings yet

- Scan Insertion Lab ObservationsDocument3 pagesScan Insertion Lab ObservationssenthilkumarNo ratings yet

- Sequential Logic Design Using VerilogDocument8 pagesSequential Logic Design Using Verilogsft007No ratings yet

- SDCDocument28 pagesSDCprabhakar reddyNo ratings yet

- Vcs /vcsi™ User Guide: Version F-2011.12-Sp1 May 2012Document1,322 pagesVcs /vcsi™ User Guide: Version F-2011.12-Sp1 May 2012paras_gangwal9757No ratings yet

- Application-Specific Integrated Circuit ASIC A Complete GuideFrom EverandApplication-Specific Integrated Circuit ASIC A Complete GuideNo ratings yet

- SPD Characteristics For Equipment Protection: ICLP 2010Document8 pagesSPD Characteristics For Equipment Protection: ICLP 2010Zainal KadirNo ratings yet

- En 025 - 055 - 120Document22 pagesEn 025 - 055 - 120ulvi ganjaliNo ratings yet

- TESA Security Door LocksDocument34 pagesTESA Security Door LockscapoNo ratings yet

- Manual RF LinkDocument2 pagesManual RF LinkDanielNo ratings yet

- Technical Data Sheet: Acrylic Removable CoatingDocument5 pagesTechnical Data Sheet: Acrylic Removable CoatingsidwalNo ratings yet

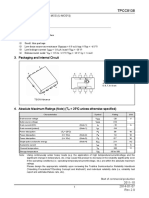

- TPCC8138 Datasheet en 20140107Document9 pagesTPCC8138 Datasheet en 20140107Henrique PinheiroNo ratings yet

- Skiip 23Nab126V10: Converter, Inverter, BrakeDocument4 pagesSkiip 23Nab126V10: Converter, Inverter, BrakepserednickiNo ratings yet

- Lab 6 BJT DC and Ac Analysis BBN 10205 (Done)Document6 pagesLab 6 BJT DC and Ac Analysis BBN 10205 (Done)Zhamir ZhakwanNo ratings yet

- TG9 Temporary Roof StructuresDocument40 pagesTG9 Temporary Roof StructuresDerek ReddinNo ratings yet

- Unit 3 NotesDocument17 pagesUnit 3 Notesanks202No ratings yet

- CV - Jamil Ahmad Civil Site EngineerDocument4 pagesCV - Jamil Ahmad Civil Site EngineerRahat SiddiquiNo ratings yet

- Chapter 1 - AC Power AnalysisDocument20 pagesChapter 1 - AC Power AnalysisandersonNo ratings yet

- ET1006 Chapter 19 Part 3 Voltage RegulatorDocument16 pagesET1006 Chapter 19 Part 3 Voltage RegulatorfastNo ratings yet

- Ece 255 Electronic Circuit Analysis and Design Fall 2017: Division 2: Chew TR 1:30PM - 2:45PM ECE 170Document3 pagesEce 255 Electronic Circuit Analysis and Design Fall 2017: Division 2: Chew TR 1:30PM - 2:45PM ECE 170Dildar Khan BhatiNo ratings yet

- Dec50143 PW4 (M.adam F1126)Document5 pagesDec50143 PW4 (M.adam F1126)iskandardaniel0063No ratings yet

- Resistance (R), Inductance (L), and Capacitance (C) CircuitsDocument10 pagesResistance (R), Inductance (L), and Capacitance (C) Circuitszed cozNo ratings yet

- Check Short Circuit: - How To Troubleshoot Ecu Controlled SystemsDocument1 pageCheck Short Circuit: - How To Troubleshoot Ecu Controlled SystemsClodoaldo BiassioNo ratings yet

- Professional Speaker Systems Catalogue ENDocument64 pagesProfessional Speaker Systems Catalogue ENDaniel FernandezNo ratings yet

- Eskom Servitude GuidelineDocument96 pagesEskom Servitude GuidelineTafadzwa MurwiraNo ratings yet

- 3D Printed Flying Wing PRANDTLDocument6 pages3D Printed Flying Wing PRANDTLPARTH PATEL (RA1911019010020)No ratings yet

- T300 MANUAL (Update)Document20 pagesT300 MANUAL (Update)Paul Chiriacescu100% (1)

- Unit 2.1 - Basics of Building ConstructionDocument29 pagesUnit 2.1 - Basics of Building ConstructionHugh G. RectionNo ratings yet

- Global Radiometers: "C511R, C102R, C502R Special Band Radiometers: "C502LUX, C502UVA, C502UVB, C502PAR, C502VIR" Instructions ManualDocument16 pagesGlobal Radiometers: "C511R, C102R, C502R Special Band Radiometers: "C502LUX, C502UVA, C502UVB, C502PAR, C502VIR" Instructions ManualGilmar RibeiroNo ratings yet

- 1VCF339752S4918Document3 pages1VCF339752S4918narminaNo ratings yet

- Valvulas AlivioDocument64 pagesValvulas AlivioJose Andres Jimenez CasallasNo ratings yet

- Ac & DC DriveDocument6 pagesAc & DC DriveAlagar Tharun100% (2)

- SD6701Document7 pagesSD6701Carlos ChuekeNo ratings yet

- A320-25-1BWX R00 Dt. 12.03.21Document81 pagesA320-25-1BWX R00 Dt. 12.03.21Pradeep K sNo ratings yet

- Gamma Net Model - Technical Data - 2023Document12 pagesGamma Net Model - Technical Data - 2023Faraz Ahmed WaseemNo ratings yet