Professional Documents

Culture Documents

U1 U2 U3 U11: VCC VCC VCC

U1 U2 U3 U11: VCC VCC VCC

Uploaded by

Sergio Ricardo LuizCopyright:

Available Formats

You might also like

- HW3Solutions PDFDocument6 pagesHW3Solutions PDFDavid LeeNo ratings yet

- Assignment Academic Year 2021-22: BM565 Digital Business & New Technologies DR Muhammad HaqueDocument8 pagesAssignment Academic Year 2021-22: BM565 Digital Business & New Technologies DR Muhammad HaqueRahul SarkarNo ratings yet

- Toyota RAV4 2013-2018 Diagrama Eléctrico de MotorDocument469 pagesToyota RAV4 2013-2018 Diagrama Eléctrico de MotorLuis Adolfo Egaña DíazNo ratings yet

- 10 Watt PLL Exciter Instruction PacketDocument3 pages10 Watt PLL Exciter Instruction PacketStephen Dunifer100% (6)

- Schematic Z80-Playground V 1 2Document4 pagesSchematic Z80-Playground V 1 2Matias Nicolas Romero Romero100% (1)

- MT5C2568 MxturvtDocument16 pagesMT5C2568 MxturvtEduFerNo ratings yet

- Half-Bridge Analog ControllerDocument1 pageHalf-Bridge Analog Controllersami karadağNo ratings yet

- Evens Audio CA-208Document1 pageEvens Audio CA-208Daniel OfoeNo ratings yet

- GND GND: Ja Amp-230Document1 pageGND GND: Ja Amp-230Daniel OfoeNo ratings yet

- Just Two /CS, in Addition To The Memory Chips, Are Required For This RAM ExpansionDocument1 pageJust Two /CS, in Addition To The Memory Chips, Are Required For This RAM ExpansionHernan BenitesNo ratings yet

- Laboratory #3 ECE 2022 1Document4 pagesLaboratory #3 ECE 2022 1pedro aparicioNo ratings yet

- General DescriptionDocument11 pagesGeneral Descriptionpuh1967No ratings yet

- Testador ULN2003 (Gerador PWM)Document1 pageTestador ULN2003 (Gerador PWM)GSM EletronicosNo ratings yet

- MX27C1000A: PreliminaryDocument15 pagesMX27C1000A: PreliminaryVictor TruccoNo ratings yet

- Schematic 0G 00005516 SAMD21 MINIDocument1 pageSchematic 0G 00005516 SAMD21 MINIAnonymous Kti5jq5EJINo ratings yet

- 8259 Programmable Interrupt Controller Application: Experiment #10Document10 pages8259 Programmable Interrupt Controller Application: Experiment #10Asaad HalayqaNo ratings yet

- Schematic PDFDocument1 pageSchematic PDFJavier RamirezNo ratings yet

- RG 88Document1 pageRG 88api-3711045100% (2)

- A51 A43 A34 A23 A22 A26 A24 A25 A32 A45: Position of Parts in Engine CompartmentDocument4 pagesA51 A43 A34 A23 A22 A26 A24 A25 A32 A45: Position of Parts in Engine CompartmentApril MckeeNo ratings yet

- AmpliTuwiter Ver.1Document1 pageAmpliTuwiter Ver.1Rahmat Destia HidayantoNo ratings yet

- 8086-Based Frequency Meter: Dr. Essam QarallehDocument13 pages8086-Based Frequency Meter: Dr. Essam QarallehrahafNo ratings yet

- Placa Auxiliar Sheet 1Document1 pagePlaca Auxiliar Sheet 1oskr.bstNo ratings yet

- DesignDocument3 pagesDesigntesfayetlh_400418456No ratings yet

- D:/Mydata/Ltspice/Simetri Oitpc Bs - Asc - : - 1/ (1-1/ (2 (I (Vi) @1 V (X) @2-V (X) @1 I (Vi) @2) +V (X) @1+I (Vi) @2) )Document1 pageD:/Mydata/Ltspice/Simetri Oitpc Bs - Asc - : - 1/ (1-1/ (2 (I (Vi) @1 V (X) @2-V (X) @1 I (Vi) @2) +V (X) @1+I (Vi) @2) )Supratman Dtt WtdaNo ratings yet

- Features: 4M-BIT (512K x8) CMOS EPROMDocument15 pagesFeatures: 4M-BIT (512K x8) CMOS EPROMDecerebradoNo ratings yet

- Schematic - d32k FB v1 SMD Copy - 2020-05-22 - 23-05-10Document1 pageSchematic - d32k FB v1 SMD Copy - 2020-05-22 - 23-05-10Valmir MorschheiserNo ratings yet

- Wahyu Aditiya Input Sap2000Document7 pagesWahyu Aditiya Input Sap2000Rizaldi AkhmadNo ratings yet

- Ac Amp02Document1 pageAc Amp02twifosNo ratings yet

- Schematic Full Adder 2022-09-11Document1 pageSchematic Full Adder 2022-09-11Shabari PrakashNo ratings yet

- 13tr40m1wft8sch (Ok)Document1 page13tr40m1wft8sch (Ok)fox7878No ratings yet

- 512K (64K X 8) One-Time Programmable, Read-Only Memory: FeaturesDocument14 pages512K (64K X 8) One-Time Programmable, Read-Only Memory: FeaturesArdhy IskandarNo ratings yet

- Schematic - Chorus Super Overdrive - Chorus Super Overdrive - 20190902222158Document1 pageSchematic - Chorus Super Overdrive - Chorus Super Overdrive - 20190902222158Marcus Feil100% (1)

- Megmeet Mp113-w Led Power Supply SCHDocument1 pageMegmeet Mp113-w Led Power Supply SCHPa3lo Pa3loNo ratings yet

- Megmeet Mp113-w Led Power Supply SCHDocument1 pageMegmeet Mp113-w Led Power Supply SCHPaulo SérgioNo ratings yet

- Led+mp113 W PsuDocument1 pageLed+mp113 W PsuRogerio E. SantoNo ratings yet

- Led+mp113 W Psu PDFDocument1 pageLed+mp113 W Psu PDFnego20100% (1)

- Led+mp113 W PsuDocument1 pageLed+mp113 W PsuautreraNo ratings yet

- Staner TEF AmpDocument1 pageStaner TEF AmpMamad SoheNo ratings yet

- Downloaded From Manuals Search EngineDocument25 pagesDownloaded From Manuals Search EngineRuslan BoianNo ratings yet

- CN-901HP3 SchematicDocument1 pageCN-901HP3 SchematicFlávio MaieloNo ratings yet

- VCC 12 +IN 1 1 - IN 1 2 3 C1 8 E1 9 11 Ref Out 14Document1 pageVCC 12 +IN 1 1 - IN 1 2 3 C1 8 E1 9 11 Ref Out 14Jhon Hermes Mulato MarriagaNo ratings yet

- ESQUEMATICOINVERSORDocument1 pageESQUEMATICOINVERSORJhoan Andrey Gomez HernandezNo ratings yet

- Eeprom 29c040Document13 pagesEeprom 29c040api-3710567No ratings yet

- Ponciango AmpDocument10 pagesPonciango AmpMond Timpog LagmanNo ratings yet

- PC10Document1 pagePC10margono akurasi100% (2)

- MK5PFC-II Schematic Main - D: Filter BoardDocument1 pageMK5PFC-II Schematic Main - D: Filter BoardJdedios66No ratings yet

- National Instruments: 801-111 Peter Street Toronto, ON M5V 2H1 (416) 977-5550Document4 pagesNational Instruments: 801-111 Peter Street Toronto, ON M5V 2H1 (416) 977-5550Cesar MartínezNo ratings yet

- 30A Speaker Protector Technical MrigankaDocument2 pages30A Speaker Protector Technical Mrigankakingcooldued1234No ratings yet

- Interfacing A Hantronix 320 X 240 Graphics Module To An 8-Bit MicrocontrollerDocument8 pagesInterfacing A Hantronix 320 X 240 Graphics Module To An 8-Bit MicrocontrollerAnonymous roFhLslwIFNo ratings yet

- R6x 100 R8x 1K: 3 4 Out1 IN2 Out2Document1 pageR6x 100 R8x 1K: 3 4 Out1 IN2 Out2Nguyễn Hữu BáchNo ratings yet

- Control Remoto 27 MHZ - SchematicDocument1 pageControl Remoto 27 MHZ - SchematicDenis J. Cabrera FuchsNo ratings yet

- GEN Chines - ACDocument80 pagesGEN Chines - ACYasmin QuintelaNo ratings yet

- 2.1 2SC5200 & 2SA1943 Pow AmplifierDocument2 pages2.1 2SC5200 & 2SA1943 Pow AmplifierAPLCTNNo ratings yet

- Schematic Keypad 2023-04-10Document1 pageSchematic Keypad 2023-04-10Alfredo Meurer JuniorNo ratings yet

- 2020 06 30 - 20 57 53 - 958102Document1 page2020 06 30 - 20 57 53 - 958102Daniel OfoeNo ratings yet

- Home Automation PCB PDFDocument1 pageHome Automation PCB PDFArish MalikNo ratings yet

- Circuito de Controle Do Display TV Samsung Ln-26A330J: (PLACA T-CON V260-B1-C04)Document2 pagesCircuito de Controle Do Display TV Samsung Ln-26A330J: (PLACA T-CON V260-B1-C04)Beto HtNo ratings yet

- Circuito de Controle Do Display TV Samsung Ln-26A330J: (PLACA T-CON V260-B1-C04)Document2 pagesCircuito de Controle Do Display TV Samsung Ln-26A330J: (PLACA T-CON V260-B1-C04)ELECTRONICA J Y CENTRO ELECTRONICO67% (3)

- Esquema TCON TV LCD Samsung LN26A330 1 PDFDocument2 pagesEsquema TCON TV LCD Samsung LN26A330 1 PDFfreeschematics100% (3)

- T-CON Samsung LN26A330-1Document2 pagesT-CON Samsung LN26A330-1MindSet MarcosNo ratings yet

- One Bold Move a Day: Meaningful Actions Women Can Take to Fulfill Their Leadership and Career PotentialFrom EverandOne Bold Move a Day: Meaningful Actions Women Can Take to Fulfill Their Leadership and Career PotentialNo ratings yet

- Fonte Schaffer K623Document5 pagesFonte Schaffer K623Sergio Ricardo LuizNo ratings yet

- Line Scan CamerasDocument3 pagesLine Scan CamerasSergio Ricardo LuizNo ratings yet

- DB GB Ibs Ip 400 Me VFD 3a Fo 6552a GBDocument58 pagesDB GB Ibs Ip 400 Me VFD 3a Fo 6552a GBSergio Ricardo LuizNo ratings yet

- Demoboard For The Bga2001 (900 and 1800 MHZ) : Application InformationDocument8 pagesDemoboard For The Bga2001 (900 and 1800 MHZ) : Application InformationSergio Ricardo LuizNo ratings yet

- A Complete FM Radio On A ChipDocument14 pagesA Complete FM Radio On A ChipSergio Ricardo LuizNo ratings yet

- Dumping N and Tutorial V 1Document6 pagesDumping N and Tutorial V 1Sergio Ricardo LuizNo ratings yet

- 12 To 18vdcDocument4 pages12 To 18vdcSergio Ricardo LuizNo ratings yet

- DD Series Guide Rod Diesel Pile Hammer D Series Diesel Pile HammerDocument7 pagesDD Series Guide Rod Diesel Pile Hammer D Series Diesel Pile HammerMuqorobinNo ratings yet

- 1LCA000003-LTE SinglePh Overhead 10kVA 167kVA Rev01Document4 pages1LCA000003-LTE SinglePh Overhead 10kVA 167kVA Rev01thapa786mNo ratings yet

- Stability ChecksDocument5 pagesStability Checksshobhit mohtaNo ratings yet

- Career Development Framework: Supporting Learners To Improve Their Career Development SkillsDocument12 pagesCareer Development Framework: Supporting Learners To Improve Their Career Development SkillsTalent Management HCBPNo ratings yet

- I Conservation and RestorationDocument9 pagesI Conservation and RestorationKylaNo ratings yet

- Bomba de Agua SubaruDocument2 pagesBomba de Agua Subarurodrigo dubonNo ratings yet

- Emotion Focused CopingDocument8 pagesEmotion Focused CopingMahrukh KhalidNo ratings yet

- Sample Paper at 2324 Class V p1 At+pcbmDocument23 pagesSample Paper at 2324 Class V p1 At+pcbmSandhya KatiyarNo ratings yet

- S006 - Suicide in An Airpla PDFDocument19 pagesS006 - Suicide in An Airpla PDFruso1900No ratings yet

- Commissioning Methodology For Boiler-1Document17 pagesCommissioning Methodology For Boiler-1Subhankar ChaudhuriNo ratings yet

- Usb Cam LogDocument2 pagesUsb Cam LogDami NaimuniNo ratings yet

- 3 - RioualD - Pumped Storage Hydropower Status PDFDocument21 pages3 - RioualD - Pumped Storage Hydropower Status PDFSsewan Jovial100% (1)

- Hongleong StatementDocument43 pagesHongleong StatementHaziq “AjiBoy” MhnBzNo ratings yet

- Electrical Machines DC MotorDocument5 pagesElectrical Machines DC MotorKitkay NivramNo ratings yet

- 5 - Workforce DiversityDocument19 pages5 - Workforce DiversityValorant SmurfNo ratings yet

- Comparison Between Scheduling Algorithms in Rtlinux and VxworksDocument9 pagesComparison Between Scheduling Algorithms in Rtlinux and VxworksRajesh GandlaNo ratings yet

- Executive Summary: With A Foreword by Theodore R. Sizer and Deborah MeierDocument8 pagesExecutive Summary: With A Foreword by Theodore R. Sizer and Deborah Meierapi-325016775No ratings yet

- Instruction Manual: FVR-E11S-7EN FVR-E11S-4ENDocument116 pagesInstruction Manual: FVR-E11S-7EN FVR-E11S-4ENminh đạo nguyễnNo ratings yet

- Lab3 Remote SensingDocument1 pageLab3 Remote SensingSiti HajarNo ratings yet

- Gce 204 Practise QuestionsDocument6 pagesGce 204 Practise Questionsfjohnbull390No ratings yet

- Aqa A Level History Coursework Mark SchemeDocument6 pagesAqa A Level History Coursework Mark Schemesyn0wok0pym3100% (2)

- Reflective EssayDocument5 pagesReflective Essayapi-673517017No ratings yet

- Network Analysis of Chaotic Dynamics inDocument5 pagesNetwork Analysis of Chaotic Dynamics inansam.moh2016No ratings yet

- 語音學及語音聲學實作考試2021 Praat final examDocument6 pages語音學及語音聲學實作考試2021 Praat final examJingnaNo ratings yet

- Declaration of Principles Concerning Activities Following The Detection of Extraterrestrial IntelligenceDocument5 pagesDeclaration of Principles Concerning Activities Following The Detection of Extraterrestrial IntelligenceCRAS-SARCNo ratings yet

- ExhibitorlistDocument8 pagesExhibitorlistHDSC ChemicalsNo ratings yet

- Dip Lab ReportDocument23 pagesDip Lab Reportfawadnuml1No ratings yet

- PROJECT WORK SubstationDocument91 pagesPROJECT WORK SubstationSai Royals100% (1)

U1 U2 U3 U11: VCC VCC VCC

U1 U2 U3 U11: VCC VCC VCC

Uploaded by

Sergio Ricardo LuizOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

U1 U2 U3 U11: VCC VCC VCC

U1 U2 U3 U11: VCC VCC VCC

Uploaded by

Sergio Ricardo LuizCopyright:

Available Formats

1 2 3 4 5

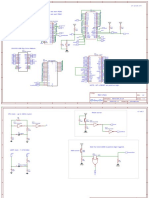

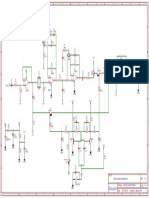

u1 u2 u3 u11

U1

When /romEnable is low we want ROM. Z80 CPU

1 40 a10

A11 A10

A When /ramEnable is low we want RAM. a11 2

A12 A9

39 a9

A

a12 3 38 a8

A13 A8

a13 4 37 a7

A14 A7

a14 5 36 a6

A15 A6

a15 6 35 a5

U2 CLK A5

clk 7 34 a4

UM61512 64k RAM D4 A4

d4 8 33 a3

D3 A3 VCC VCC

1 32 VCC d3 9 32 a2

NC VCC D5 A2

2 31 a15

VCC d5 10 31 a1

NC A15 D6 A1

3 30VCC VCC d6 11 30 a0

A14 CE2 VCC A0

a14 4 29 VCC 12 29 GND

A12 /WE /wr D2 GND R13 R14

a12 5 28 a13 d2 13 28 /m1

A7 A13 D7 /RFSH 10k 10k

a7 6 27 a8 R15 d7 14 27

A6 A8 D0 /M1

a6 7 26 a9 10k d0 15 26 /reset

A5 A9 D1 /RESET

a5 8 25 a11 d1 16 25 /busrq

A4 A11 /rd /INT /BUSRQ

a4 9 24 17 24

A3 /OE /NMI /WAIT /wait

a3 10 23 a10 /int 18 23

A2 A10 /ramEnable /HALT /BUSAK

a2 11 22 19 22

A1 /CE /MREQ /WR

a1 12 21 d7 20 21 /busak

A0 IO8 /nmi /IORQ /RD

a0 13 20 d6 /wr

IO1 IO7

B d0 14 19 d5 B

IO2 IO6 /halt /rd

d1 15 18 d4

IO3 IO5

d2 16 17 d3 /mreq

GND IO4

GND

/ioreq

CH376S USB Pen-Drive Module

U10

CH376S_Module

1 2 U11

d0 DO GND GND 16C550 - UART

3 D1 GND 4

d1 GND

5 D2 VCC 6 1 40

d2 VCC d0 D0 VCC VCC

7 D3 /INT 8 2 39

d3 d1 D1 /RI VCC

9 D4 A0 10 3 38

d4 a0 U3 d2 D2 /CD GND

11 D5 /CS 12 4 37

d5 /csUsb 28C256 - 32K EEPROM d3 D3 /DSR GND

13 14 5 36

28

10 11 d0

d6 D6 /RD /rd A0 D0 d4 D4 /CTS uartCts

VCC

15 D7 /WR 16 a0 9 12 d1 6 35

d7 /wr A1 D1 d5 D5 RESET uartReset

C d2 7 34 C

a1 8

romON goes high on reset

13

A2 D2 d6 D6 /OP1 romOn

17 17 18 18 a2 7 15 d3 8 33

A3 D3 d7 D7 /DTR uartDtr

19 GND TX 20 a3 6 16 d4 9 32

A4 D4 RCLK /RTS

21 RX 22 22 a4 5 17 d5 10 31

A5 D5 uartRx RX /OP2 user

a5 4 18 d6 11 30

A6 D6 uartTx TX INT

a6 3 19 d7 12 29

A7 D7 a3 CS0 /RXRDY

a7 25 13 28

A8 /m1 CS1 A0 a0

a8 24 14 27

A9 /ioreq /CS2 A1 a1

a9 21 15 26

A10 /BAUDOUT A2 a2

a10 23 16 25

A11 xtal1 XTAL1 /AS GND

a11 2 17 24

A12 xtal2 XTAL2 /TXRDY

a12 26 18 23

A13 /wr /IOW /DDIS

a13 1 19 22

A14 GND IOW IOR GND

a14 20 21

GND GND /IOR /rd

27

VCC 22

/WE

GND

/rd /OE

NOTE: INT & RESET are positive-logic.

20

/romEnable /CS

14

D D

TITLE:

Main chips REV: 1.1

Company: 8bitstack.co.uk Sheet: 1/1

Date: 2020-05-11 Drawn By: johnsquires

1 2 3 4 5

1 2 3 4 5

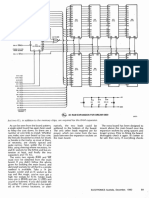

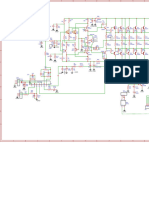

CPU clock - up to 20MHz crystal u7 u8.1

R5

1M ohm

A A

U7.1 U7.2 Reset button

74HC14 inverter 14

74HC14 inverter VCC

14

clk

VCC

VCC

1 2 3 4

GND

GND

7

7

R6

1K ohm C1 SW1

10uF Reset U7.6

74HC14 inverter

X1

14

CPU XTAL

VCC

4 3 13 12 /reset

GND

7

R8

10k U7.4

C5 74HC14 inverter

22pF C6

22pF

14

VCC

9 8

uartReset

GND

GND

7

B B

VCC VCC

UART clock - 1.8432 MHz

xtal1 xtal2 U8.4

R4

NMI button SW2 74HC02 - NOR

10k

7

/NMI

GND

11 /externalNmi

13

U8.2 12

VCC

74HC02 - NOR

14

R7

6

1.5K ohm

7 14

R9 GND VCC

X2 10k

UART 7.3728MHz

4 3

GND

C C18

C17 C

4

22pF

47pF

/nmi

D D

TITLE:

Clock and reset REV: 1.0

Company: 8bitstack.co.uk Sheet: 1/1

Date: 2020-05-11 Drawn By: johnsquires

1 2 3 4 5

1 2 3 4 5

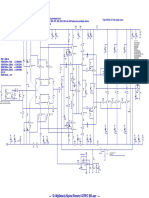

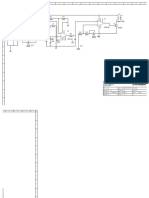

Assuming /MREQ is low, we want ROM when: u5 u6

(1) A15 is low

(2) A14J is low (this is the jumpered version of a14)

VCC

U5.1

14

74HC32 - OR

VCC

A (3) /FFJ is low (this is the jumpered version of the FF) 1 U5.2

A

14

a15 3 74HC32 - OR

VCC

(4) /RD is low 2 4 U5.3

14

a14j 6 74HC32 - OR

5 9

Otherwise we want RAM.

7

P2 P3 /romOnj

GND

P1 rom jumper power jumper 8

a14 jumper 10 /wantROM

7

/rd

GND

/wantROM = 1 or 2 or 3 or 4 a14 1 /romOn 1 externalVCC 1

/romOnj 2 VCC 2

2

7

GND

a14j GND 3 ftdiVCC 3

/romEnable = /MREQ or /wantROM GND 3 U8.3

VCC

74HC02 - NOR

U6.1

14

14

/ramEnable = /MREQ or NOT /wantROM

VCC

9 74HC32 - OR

/wantROM 10 1

8 3

GND

2 /ramEnable

7

VCC

U5.4 /mreq

14

7

74HC32 - OR

GND

12

B /wantROM B

11

13 /romEnable

/mreq

7

U7.5

GND

74HC14 inverter

14

VCC

11 10

romOn /romOn

GND

VCC

7

U6.4

14

74HC32 - OR

/ioreq 12

VCC

U8.1

11 U6.2

14

74HC02 - NOR U7.3

13 74HC32 - OR

14

74HC14 inverter

VCC

3 4

1 6

14

/m1

VCC

/csUsb 5 6

7

GND

2 5 user /user

GND

GND

a4

7

7

7

GND

C C

For I/O for UART we want: For I/O for USB we want:

(1) /IOREQ is low (1) /IOREQ is low

(2) /M1 is high (2) /M1 is high

(3) a3 is high (3) a3 is low

(4) a4 is high (4) a4 is low

base uart port = 00011000 = 24 base USB port = 00000000 = 0

VCC

U6.3

14

74HC32 - OR

9

GND 8

10

GND

D D

7

GND

TITLE:

ROM / RAM / IO select logic REV: 1.0

Company: 8bitstack.co.uk Sheet: 1/1

Date: 2020-06-11 Drawn By: johnsquires

1 2 3 4 5

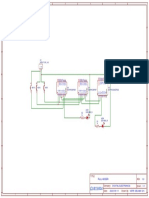

1 2 3 4 5

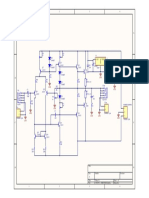

H1

externalVCC FTDI serial

A uartDtr 1 DTR A

J2 uartTx 2 TX

2.1mm 5v uartRx 3 RX

+ 1 ftdiVCC 4 VCC

2 uartCts 5 CTS

3 GND 6 GND

GND

H2

Header-Female-2.54_1x36 VCC VCC VCC VCC

B B

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

1

2

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

R1 R2 R3 R16

Resistor 0.25W Resistor 0.25W Resistor 0.25W Resistor 0.25W

GND

/mreq

a15

a13

a11

a14

a12

a10

/busak

(out) /reset

/rd

d7

d6

d5

d4

d3

d2

d1

d0

a9

a8

a7

a6

a5

a4

a3

a2

a1

a0

/wr

LED6 LED1 LED2 LED3

VCC

/externalNmi

/busrq

/m1

/ioreq

/wait

halt /ROM /user power

/halt /romOn /user GND

VCC

C C

C13 C12 C10 C3 C4 C7 C8 C9 C11

1uF 1uF 1uF 1uF 1uF 1uF 1uF 1uF 47uf

GND

D D

TITLE:

Connectors REV: 1.0

Company: 8bitstack.co.uk Sheet: 1/1

Date: 2020-05-04 Drawn By: johnsquires

1 2 3 4 5

You might also like

- HW3Solutions PDFDocument6 pagesHW3Solutions PDFDavid LeeNo ratings yet

- Assignment Academic Year 2021-22: BM565 Digital Business & New Technologies DR Muhammad HaqueDocument8 pagesAssignment Academic Year 2021-22: BM565 Digital Business & New Technologies DR Muhammad HaqueRahul SarkarNo ratings yet

- Toyota RAV4 2013-2018 Diagrama Eléctrico de MotorDocument469 pagesToyota RAV4 2013-2018 Diagrama Eléctrico de MotorLuis Adolfo Egaña DíazNo ratings yet

- 10 Watt PLL Exciter Instruction PacketDocument3 pages10 Watt PLL Exciter Instruction PacketStephen Dunifer100% (6)

- Schematic Z80-Playground V 1 2Document4 pagesSchematic Z80-Playground V 1 2Matias Nicolas Romero Romero100% (1)

- MT5C2568 MxturvtDocument16 pagesMT5C2568 MxturvtEduFerNo ratings yet

- Half-Bridge Analog ControllerDocument1 pageHalf-Bridge Analog Controllersami karadağNo ratings yet

- Evens Audio CA-208Document1 pageEvens Audio CA-208Daniel OfoeNo ratings yet

- GND GND: Ja Amp-230Document1 pageGND GND: Ja Amp-230Daniel OfoeNo ratings yet

- Just Two /CS, in Addition To The Memory Chips, Are Required For This RAM ExpansionDocument1 pageJust Two /CS, in Addition To The Memory Chips, Are Required For This RAM ExpansionHernan BenitesNo ratings yet

- Laboratory #3 ECE 2022 1Document4 pagesLaboratory #3 ECE 2022 1pedro aparicioNo ratings yet

- General DescriptionDocument11 pagesGeneral Descriptionpuh1967No ratings yet

- Testador ULN2003 (Gerador PWM)Document1 pageTestador ULN2003 (Gerador PWM)GSM EletronicosNo ratings yet

- MX27C1000A: PreliminaryDocument15 pagesMX27C1000A: PreliminaryVictor TruccoNo ratings yet

- Schematic 0G 00005516 SAMD21 MINIDocument1 pageSchematic 0G 00005516 SAMD21 MINIAnonymous Kti5jq5EJINo ratings yet

- 8259 Programmable Interrupt Controller Application: Experiment #10Document10 pages8259 Programmable Interrupt Controller Application: Experiment #10Asaad HalayqaNo ratings yet

- Schematic PDFDocument1 pageSchematic PDFJavier RamirezNo ratings yet

- RG 88Document1 pageRG 88api-3711045100% (2)

- A51 A43 A34 A23 A22 A26 A24 A25 A32 A45: Position of Parts in Engine CompartmentDocument4 pagesA51 A43 A34 A23 A22 A26 A24 A25 A32 A45: Position of Parts in Engine CompartmentApril MckeeNo ratings yet

- AmpliTuwiter Ver.1Document1 pageAmpliTuwiter Ver.1Rahmat Destia HidayantoNo ratings yet

- 8086-Based Frequency Meter: Dr. Essam QarallehDocument13 pages8086-Based Frequency Meter: Dr. Essam QarallehrahafNo ratings yet

- Placa Auxiliar Sheet 1Document1 pagePlaca Auxiliar Sheet 1oskr.bstNo ratings yet

- DesignDocument3 pagesDesigntesfayetlh_400418456No ratings yet

- D:/Mydata/Ltspice/Simetri Oitpc Bs - Asc - : - 1/ (1-1/ (2 (I (Vi) @1 V (X) @2-V (X) @1 I (Vi) @2) +V (X) @1+I (Vi) @2) )Document1 pageD:/Mydata/Ltspice/Simetri Oitpc Bs - Asc - : - 1/ (1-1/ (2 (I (Vi) @1 V (X) @2-V (X) @1 I (Vi) @2) +V (X) @1+I (Vi) @2) )Supratman Dtt WtdaNo ratings yet

- Features: 4M-BIT (512K x8) CMOS EPROMDocument15 pagesFeatures: 4M-BIT (512K x8) CMOS EPROMDecerebradoNo ratings yet

- Schematic - d32k FB v1 SMD Copy - 2020-05-22 - 23-05-10Document1 pageSchematic - d32k FB v1 SMD Copy - 2020-05-22 - 23-05-10Valmir MorschheiserNo ratings yet

- Wahyu Aditiya Input Sap2000Document7 pagesWahyu Aditiya Input Sap2000Rizaldi AkhmadNo ratings yet

- Ac Amp02Document1 pageAc Amp02twifosNo ratings yet

- Schematic Full Adder 2022-09-11Document1 pageSchematic Full Adder 2022-09-11Shabari PrakashNo ratings yet

- 13tr40m1wft8sch (Ok)Document1 page13tr40m1wft8sch (Ok)fox7878No ratings yet

- 512K (64K X 8) One-Time Programmable, Read-Only Memory: FeaturesDocument14 pages512K (64K X 8) One-Time Programmable, Read-Only Memory: FeaturesArdhy IskandarNo ratings yet

- Schematic - Chorus Super Overdrive - Chorus Super Overdrive - 20190902222158Document1 pageSchematic - Chorus Super Overdrive - Chorus Super Overdrive - 20190902222158Marcus Feil100% (1)

- Megmeet Mp113-w Led Power Supply SCHDocument1 pageMegmeet Mp113-w Led Power Supply SCHPa3lo Pa3loNo ratings yet

- Megmeet Mp113-w Led Power Supply SCHDocument1 pageMegmeet Mp113-w Led Power Supply SCHPaulo SérgioNo ratings yet

- Led+mp113 W PsuDocument1 pageLed+mp113 W PsuRogerio E. SantoNo ratings yet

- Led+mp113 W Psu PDFDocument1 pageLed+mp113 W Psu PDFnego20100% (1)

- Led+mp113 W PsuDocument1 pageLed+mp113 W PsuautreraNo ratings yet

- Staner TEF AmpDocument1 pageStaner TEF AmpMamad SoheNo ratings yet

- Downloaded From Manuals Search EngineDocument25 pagesDownloaded From Manuals Search EngineRuslan BoianNo ratings yet

- CN-901HP3 SchematicDocument1 pageCN-901HP3 SchematicFlávio MaieloNo ratings yet

- VCC 12 +IN 1 1 - IN 1 2 3 C1 8 E1 9 11 Ref Out 14Document1 pageVCC 12 +IN 1 1 - IN 1 2 3 C1 8 E1 9 11 Ref Out 14Jhon Hermes Mulato MarriagaNo ratings yet

- ESQUEMATICOINVERSORDocument1 pageESQUEMATICOINVERSORJhoan Andrey Gomez HernandezNo ratings yet

- Eeprom 29c040Document13 pagesEeprom 29c040api-3710567No ratings yet

- Ponciango AmpDocument10 pagesPonciango AmpMond Timpog LagmanNo ratings yet

- PC10Document1 pagePC10margono akurasi100% (2)

- MK5PFC-II Schematic Main - D: Filter BoardDocument1 pageMK5PFC-II Schematic Main - D: Filter BoardJdedios66No ratings yet

- National Instruments: 801-111 Peter Street Toronto, ON M5V 2H1 (416) 977-5550Document4 pagesNational Instruments: 801-111 Peter Street Toronto, ON M5V 2H1 (416) 977-5550Cesar MartínezNo ratings yet

- 30A Speaker Protector Technical MrigankaDocument2 pages30A Speaker Protector Technical Mrigankakingcooldued1234No ratings yet

- Interfacing A Hantronix 320 X 240 Graphics Module To An 8-Bit MicrocontrollerDocument8 pagesInterfacing A Hantronix 320 X 240 Graphics Module To An 8-Bit MicrocontrollerAnonymous roFhLslwIFNo ratings yet

- R6x 100 R8x 1K: 3 4 Out1 IN2 Out2Document1 pageR6x 100 R8x 1K: 3 4 Out1 IN2 Out2Nguyễn Hữu BáchNo ratings yet

- Control Remoto 27 MHZ - SchematicDocument1 pageControl Remoto 27 MHZ - SchematicDenis J. Cabrera FuchsNo ratings yet

- GEN Chines - ACDocument80 pagesGEN Chines - ACYasmin QuintelaNo ratings yet

- 2.1 2SC5200 & 2SA1943 Pow AmplifierDocument2 pages2.1 2SC5200 & 2SA1943 Pow AmplifierAPLCTNNo ratings yet

- Schematic Keypad 2023-04-10Document1 pageSchematic Keypad 2023-04-10Alfredo Meurer JuniorNo ratings yet

- 2020 06 30 - 20 57 53 - 958102Document1 page2020 06 30 - 20 57 53 - 958102Daniel OfoeNo ratings yet

- Home Automation PCB PDFDocument1 pageHome Automation PCB PDFArish MalikNo ratings yet

- Circuito de Controle Do Display TV Samsung Ln-26A330J: (PLACA T-CON V260-B1-C04)Document2 pagesCircuito de Controle Do Display TV Samsung Ln-26A330J: (PLACA T-CON V260-B1-C04)Beto HtNo ratings yet

- Circuito de Controle Do Display TV Samsung Ln-26A330J: (PLACA T-CON V260-B1-C04)Document2 pagesCircuito de Controle Do Display TV Samsung Ln-26A330J: (PLACA T-CON V260-B1-C04)ELECTRONICA J Y CENTRO ELECTRONICO67% (3)

- Esquema TCON TV LCD Samsung LN26A330 1 PDFDocument2 pagesEsquema TCON TV LCD Samsung LN26A330 1 PDFfreeschematics100% (3)

- T-CON Samsung LN26A330-1Document2 pagesT-CON Samsung LN26A330-1MindSet MarcosNo ratings yet

- One Bold Move a Day: Meaningful Actions Women Can Take to Fulfill Their Leadership and Career PotentialFrom EverandOne Bold Move a Day: Meaningful Actions Women Can Take to Fulfill Their Leadership and Career PotentialNo ratings yet

- Fonte Schaffer K623Document5 pagesFonte Schaffer K623Sergio Ricardo LuizNo ratings yet

- Line Scan CamerasDocument3 pagesLine Scan CamerasSergio Ricardo LuizNo ratings yet

- DB GB Ibs Ip 400 Me VFD 3a Fo 6552a GBDocument58 pagesDB GB Ibs Ip 400 Me VFD 3a Fo 6552a GBSergio Ricardo LuizNo ratings yet

- Demoboard For The Bga2001 (900 and 1800 MHZ) : Application InformationDocument8 pagesDemoboard For The Bga2001 (900 and 1800 MHZ) : Application InformationSergio Ricardo LuizNo ratings yet

- A Complete FM Radio On A ChipDocument14 pagesA Complete FM Radio On A ChipSergio Ricardo LuizNo ratings yet

- Dumping N and Tutorial V 1Document6 pagesDumping N and Tutorial V 1Sergio Ricardo LuizNo ratings yet

- 12 To 18vdcDocument4 pages12 To 18vdcSergio Ricardo LuizNo ratings yet

- DD Series Guide Rod Diesel Pile Hammer D Series Diesel Pile HammerDocument7 pagesDD Series Guide Rod Diesel Pile Hammer D Series Diesel Pile HammerMuqorobinNo ratings yet

- 1LCA000003-LTE SinglePh Overhead 10kVA 167kVA Rev01Document4 pages1LCA000003-LTE SinglePh Overhead 10kVA 167kVA Rev01thapa786mNo ratings yet

- Stability ChecksDocument5 pagesStability Checksshobhit mohtaNo ratings yet

- Career Development Framework: Supporting Learners To Improve Their Career Development SkillsDocument12 pagesCareer Development Framework: Supporting Learners To Improve Their Career Development SkillsTalent Management HCBPNo ratings yet

- I Conservation and RestorationDocument9 pagesI Conservation and RestorationKylaNo ratings yet

- Bomba de Agua SubaruDocument2 pagesBomba de Agua Subarurodrigo dubonNo ratings yet

- Emotion Focused CopingDocument8 pagesEmotion Focused CopingMahrukh KhalidNo ratings yet

- Sample Paper at 2324 Class V p1 At+pcbmDocument23 pagesSample Paper at 2324 Class V p1 At+pcbmSandhya KatiyarNo ratings yet

- S006 - Suicide in An Airpla PDFDocument19 pagesS006 - Suicide in An Airpla PDFruso1900No ratings yet

- Commissioning Methodology For Boiler-1Document17 pagesCommissioning Methodology For Boiler-1Subhankar ChaudhuriNo ratings yet

- Usb Cam LogDocument2 pagesUsb Cam LogDami NaimuniNo ratings yet

- 3 - RioualD - Pumped Storage Hydropower Status PDFDocument21 pages3 - RioualD - Pumped Storage Hydropower Status PDFSsewan Jovial100% (1)

- Hongleong StatementDocument43 pagesHongleong StatementHaziq “AjiBoy” MhnBzNo ratings yet

- Electrical Machines DC MotorDocument5 pagesElectrical Machines DC MotorKitkay NivramNo ratings yet

- 5 - Workforce DiversityDocument19 pages5 - Workforce DiversityValorant SmurfNo ratings yet

- Comparison Between Scheduling Algorithms in Rtlinux and VxworksDocument9 pagesComparison Between Scheduling Algorithms in Rtlinux and VxworksRajesh GandlaNo ratings yet

- Executive Summary: With A Foreword by Theodore R. Sizer and Deborah MeierDocument8 pagesExecutive Summary: With A Foreword by Theodore R. Sizer and Deborah Meierapi-325016775No ratings yet

- Instruction Manual: FVR-E11S-7EN FVR-E11S-4ENDocument116 pagesInstruction Manual: FVR-E11S-7EN FVR-E11S-4ENminh đạo nguyễnNo ratings yet

- Lab3 Remote SensingDocument1 pageLab3 Remote SensingSiti HajarNo ratings yet

- Gce 204 Practise QuestionsDocument6 pagesGce 204 Practise Questionsfjohnbull390No ratings yet

- Aqa A Level History Coursework Mark SchemeDocument6 pagesAqa A Level History Coursework Mark Schemesyn0wok0pym3100% (2)

- Reflective EssayDocument5 pagesReflective Essayapi-673517017No ratings yet

- Network Analysis of Chaotic Dynamics inDocument5 pagesNetwork Analysis of Chaotic Dynamics inansam.moh2016No ratings yet

- 語音學及語音聲學實作考試2021 Praat final examDocument6 pages語音學及語音聲學實作考試2021 Praat final examJingnaNo ratings yet

- Declaration of Principles Concerning Activities Following The Detection of Extraterrestrial IntelligenceDocument5 pagesDeclaration of Principles Concerning Activities Following The Detection of Extraterrestrial IntelligenceCRAS-SARCNo ratings yet

- ExhibitorlistDocument8 pagesExhibitorlistHDSC ChemicalsNo ratings yet

- Dip Lab ReportDocument23 pagesDip Lab Reportfawadnuml1No ratings yet

- PROJECT WORK SubstationDocument91 pagesPROJECT WORK SubstationSai Royals100% (1)