Professional Documents

Culture Documents

EE16A Spring 2020 MT2

EE16A Spring 2020 MT2

Uploaded by

Annabel YauCopyright:

Available Formats

You might also like

- Grade 1 Sses ScienceDocument7 pagesGrade 1 Sses ScienceDorothy Manalang100% (3)

- Lab Report 2Document6 pagesLab Report 2Abdul Aziz ZulkifliNo ratings yet

- Joseph J. WEED - A Rosicrucian Speaks-Chatsworth Press (1965) PDFDocument179 pagesJoseph J. WEED - A Rosicrucian Speaks-Chatsworth Press (1965) PDFDewdman42No ratings yet

- Student WorkDocument12 pagesStudent Workapi-36422456048% (42)

- Magnetic Compass PDFDocument19 pagesMagnetic Compass PDFHashil Naseer100% (1)

- Type KAVR 130: Auto-Reclose and Check Synchronism RelayDocument120 pagesType KAVR 130: Auto-Reclose and Check Synchronism RelayThai Dang VuNo ratings yet

- Samsung Le26 32 37 Le40r73 Le40r74bdr Xeu Chassis Gly26 32 37 40keDocument274 pagesSamsung Le26 32 37 Le40r73 Le40r74bdr Xeu Chassis Gly26 32 37 40keVenancio Luis Amor PerezNo ratings yet

- Test I: 'Xnh8QlyhuvlwDocument6 pagesTest I: 'Xnh8QlyhuvlwJustino LorenzoNo ratings yet

- Answers Should Be Written in QCAB Format Only.: InstructionsDocument92 pagesAnswers Should Be Written in QCAB Format Only.: InstructionsAkash yadavNo ratings yet

- Test I: 'Xnh8QlyhuvlwDocument13 pagesTest I: 'Xnh8QlyhuvlwJustino LorenzoNo ratings yet

- Test I: 'Xnh8QlyhuvlwDocument6 pagesTest I: 'Xnh8QlyhuvlwJustino LorenzoNo ratings yet

- CS2020 1516 Semester 2Document24 pagesCS2020 1516 Semester 2Eunice LimNo ratings yet

- CS302 Collection of Old PapersDocument48 pagesCS302 Collection of Old Paperscs619finalproject.comNo ratings yet

- Mid ExamDocument2 pagesMid ExamHuzaifaNo ratings yet

- 2017S FE AM QuestionDocument28 pages2017S FE AM Questionfqnguyen8No ratings yet

- Answers Should Be Written in QCAB Format Only.: InstructionsDocument82 pagesAnswers Should Be Written in QCAB Format Only.: InstructionsCaraNo ratings yet

- CS2020 1516 Semester 2 AnsDocument27 pagesCS2020 1516 Semester 2 AnsEunice LimNo ratings yet

- Test I: 'Xnh8QlyhuvlwDocument6 pagesTest I: 'Xnh8QlyhuvlwJustino LorenzoNo ratings yet

- Comparch Answers and QuestionsDocument7 pagesComparch Answers and QuestionsAngela KasekeNo ratings yet

- Arduino GuideDocument11 pagesArduino Guidesindhu bhargaviNo ratings yet

- Final Exam EE303 Microprocessor Interfacing & Programming: Total Time: 3 Hour Total Marks: 120 Course InstructorDocument14 pagesFinal Exam EE303 Microprocessor Interfacing & Programming: Total Time: 3 Hour Total Marks: 120 Course InstructorMuneeb Ahmad NasirNo ratings yet

- Circuits and Signals I Exam Question PaperDocument8 pagesCircuits and Signals I Exam Question PaperMrmouzinhoNo ratings yet

- Experiment 5 Series & Parallel Circuits Voltage Divider & Current Divider RulesDocument5 pagesExperiment 5 Series & Parallel Circuits Voltage Divider & Current Divider RulesPrincess Lheakyrie CasilaoNo ratings yet

- Digital Logic Design - CS302 Spring 2005 Mid Term PaperDocument4 pagesDigital Logic Design - CS302 Spring 2005 Mid Term PaperRameen QureshiNo ratings yet

- 1.5.10 Packet Tracer - Verify Directly Connected NetworksDocument4 pages1.5.10 Packet Tracer - Verify Directly Connected NetworksHạnhNo ratings yet

- EEE2211 Lab ManualDocument30 pagesEEE2211 Lab ManualMuhammed AslamNo ratings yet

- Experiment 05Document5 pagesExperiment 05ehtishamNo ratings yet

- Weekly Test-30 Sankalp2325s1, T1 & P1 Paper & Answer Key (Xii)Document23 pagesWeekly Test-30 Sankalp2325s1, T1 & P1 Paper & Answer Key (Xii)agnit.dgNo ratings yet

- Circuit Simulation With SpiceDocument6 pagesCircuit Simulation With SpicejmdelacruzNo ratings yet

- Section Classification 1 Mark 2 Marks Total Number of QuestionsDocument3 pagesSection Classification 1 Mark 2 Marks Total Number of QuestionsSaurav GoyalNo ratings yet

- Elektor BusDocument6 pagesElektor BusFernando VidalNo ratings yet

- Packet Tracer - Verify Directly Connected Networks: Addressing TableDocument3 pagesPacket Tracer - Verify Directly Connected Networks: Addressing TableBrayan EsneiderNo ratings yet

- National Standard Examination in Junior Science (Nsejs) Ijso Stage-IDocument11 pagesNational Standard Examination in Junior Science (Nsejs) Ijso Stage-IRashad AlamNo ratings yet

- s4623970 - Abhishekkumar PatelDocument17 pagess4623970 - Abhishekkumar Patelmuhammad iftikharNo ratings yet

- ECE 3144 Lecture 8: Dr. Rose Q. Hu Electrical and Computer Engineering Department Mississippi State UniversityDocument10 pagesECE 3144 Lecture 8: Dr. Rose Q. Hu Electrical and Computer Engineering Department Mississippi State UniversityGopakumar G NairNo ratings yet

- EE Afternoon New1 PDFDocument5 pagesEE Afternoon New1 PDFanon_12881478No ratings yet

- PDFDocument9 pagesPDFDennis KorirNo ratings yet

- NIT5110 2018 Exam SampleDocument20 pagesNIT5110 2018 Exam SamplePartha Sarathi NandiNo ratings yet

- Microprocessor Interfacing and System Design QuestionDocument4 pagesMicroprocessor Interfacing and System Design QuestionSharif Shah NewazNo ratings yet

- Faculty of Engineering: Circuits and Signals EEL 2186 TRIMESTER 1 (2014/2015)Document7 pagesFaculty of Engineering: Circuits and Signals EEL 2186 TRIMESTER 1 (2014/2015)Rameshkumar JayaramanNo ratings yet

- Exp 3 - IED - Lab Group 7Document10 pagesExp 3 - IED - Lab Group 7Kazi ShahadatNo ratings yet

- Final Dec 2003Document6 pagesFinal Dec 2003api-3755462No ratings yet

- EECS 489: Final Exam, Fall 2018: Duration: 70 MinutesDocument7 pagesEECS 489: Final Exam, Fall 2018: Duration: 70 MinutesTayyaba AsifNo ratings yet

- Project 1 Power SupplyDocument4 pagesProject 1 Power Supplyajnabi313No ratings yet

- Exam DM 071214 AnsDocument7 pagesExam DM 071214 AnsEyad GoudaaNo ratings yet

- Digital Logic and Circuits: Assignment For CO AchievementDocument2 pagesDigital Logic and Circuits: Assignment For CO Achievementanon_776365175No ratings yet

- ACS133 Assignment 2 - Briefing 2023-2024Document6 pagesACS133 Assignment 2 - Briefing 2023-2024Joash MacentonNo ratings yet

- IT5551ComputerNetworks Test2 Dec2022Document8 pagesIT5551ComputerNetworks Test2 Dec2022gauthamNo ratings yet

- R1 6Ω R4 4Ω R5 6Ω V1 10 VDocument63 pagesR1 6Ω R4 4Ω R5 6Ω V1 10 Vď èNo ratings yet

- Lab 11.1 - Use Ping and Traceroute To Test Network ConnectivityDocument4 pagesLab 11.1 - Use Ping and Traceroute To Test Network ConnectivityRecky JimmyNo ratings yet

- JEE Advanced Sample Papers 2 (Paper 1 & 2) by FIITJEEDocument71 pagesJEE Advanced Sample Papers 2 (Paper 1 & 2) by FIITJEEAvneesh GautamNo ratings yet

- Class: Be Eee Iv Sem (Aicte) Faculty: Mr. Praveen Reddy Maali Sub: Digital Electronics and Logic Design Total Marks: 20 1Document5 pagesClass: Be Eee Iv Sem (Aicte) Faculty: Mr. Praveen Reddy Maali Sub: Digital Electronics and Logic Design Total Marks: 20 1PRAVEEN REDDYNo ratings yet

- Midterm Spring Answer 2020Document6 pagesMidterm Spring Answer 2020p227738930No ratings yet

- R R R R R R V R I: Instructions: Fill in Each Blank With The Appropriate Answer. If Explanation Is RequiredDocument5 pagesR R R R R R V R I: Instructions: Fill in Each Blank With The Appropriate Answer. If Explanation Is RequiredEarl Cris RiggsNo ratings yet

- Finalterm Examination: Please Read The Following Instructions Carefully Before Attempting Any of The QuestionsDocument4 pagesFinalterm Examination: Please Read The Following Instructions Carefully Before Attempting Any of The QuestionsRai Abdul Waheed AhmadNo ratings yet

- 2017A FE AM QuestionDocument30 pages2017A FE AM QuestionShah AlamNo ratings yet

- CPSC 213, Winter 2013, Term 2 - Sample Midterm Questions: Date: February 2014 Instructor: Mike FeeleyDocument8 pagesCPSC 213, Winter 2013, Term 2 - Sample Midterm Questions: Date: February 2014 Instructor: Mike FeeleyDanielle SimpsonNo ratings yet

- Bölüm Soruları - 5th-EditionDocument14 pagesBölüm Soruları - 5th-EditionBee MiteNo ratings yet

- Ec: Electronics and Communication Engineering: Duration: Three HoursDocument24 pagesEc: Electronics and Communication Engineering: Duration: Three HoursMarshall LeeNo ratings yet

- BN208-Networked Applications - T1 2020 - Assessment PaperDocument9 pagesBN208-Networked Applications - T1 2020 - Assessment PaperMuhammad YousafNo ratings yet

- 04 30067 Electronic Engineering January 2022 Exam PaperDocument10 pages04 30067 Electronic Engineering January 2022 Exam PaperCharlie CoxNo ratings yet

- Digital Logic Design - CS302 Spring 2006 Final Term PaperDocument4 pagesDigital Logic Design - CS302 Spring 2006 Final Term PaperNamal No OorNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- EE16A Spring 2019 MT1Document23 pagesEE16A Spring 2019 MT1Annabel YauNo ratings yet

- Eecs 16A Designing Information Devices and Systems I Spring 2019 Exam Location: Cory 144MA (DSP)Document46 pagesEecs 16A Designing Information Devices and Systems I Spring 2019 Exam Location: Cory 144MA (DSP)Annabel YauNo ratings yet

- EE16A Spring 2019 MT2Document26 pagesEE16A Spring 2019 MT2Annabel YauNo ratings yet

- EE16A Spring 2020 MT1Document18 pagesEE16A Spring 2020 MT1Annabel YauNo ratings yet

- Engineering Mechanics DynamicsDocument2 pagesEngineering Mechanics DynamicsMallene EhurangoNo ratings yet

- Contactor by EE Controls PDFDocument10 pagesContactor by EE Controls PDFPaul MendozaNo ratings yet

- Users Guide FMG Series Electromagnetic FlowmeterDocument44 pagesUsers Guide FMG Series Electromagnetic Flowmeterdhan210No ratings yet

- Presentation of The Lesson:: (Self / Subject ..)Document3 pagesPresentation of The Lesson:: (Self / Subject ..)Lady Amor Telompros PeroteNo ratings yet

- 1 Soalan 1Document7 pages1 Soalan 1Radziah MohamedNo ratings yet

- Exam Style Answers P1 Asal Physics CBDocument2 pagesExam Style Answers P1 Asal Physics CBAnshul ShahNo ratings yet

- WWW - Manaresults.Co - In: II B. Tech I Semester Regular/Supplementary Examinations, Dec - 2015 Electrical Machiens-IDocument5 pagesWWW - Manaresults.Co - In: II B. Tech I Semester Regular/Supplementary Examinations, Dec - 2015 Electrical Machiens-IniharikaNo ratings yet

- Atoms and Static Electricity: Fun FactDocument3 pagesAtoms and Static Electricity: Fun FactXavier McCulloughNo ratings yet

- SIOP Lesson Plan (3) 3-14-13Document4 pagesSIOP Lesson Plan (3) 3-14-13ksal78No ratings yet

- PH1 ProbSet 5Document2 pagesPH1 ProbSet 5akshat shNo ratings yet

- EE301 Power Generation Transmission and Protection PDFDocument3 pagesEE301 Power Generation Transmission and Protection PDFMalavika SNo ratings yet

- 2 Ece II Engineering Physics (14phy22) NotesDocument138 pages2 Ece II Engineering Physics (14phy22) NotesSGSNo ratings yet

- DTCDocument18 pagesDTCVenkatesh TomNo ratings yet

- Mechanics: A̅ W MGDocument5 pagesMechanics: A̅ W MGfarujoyNo ratings yet

- Load Flow Analysis Of132/11Kv Substation Using Etap: A Case StudyDocument10 pagesLoad Flow Analysis Of132/11Kv Substation Using Etap: A Case Studydsanmi1234No ratings yet

- Hydraulic System 994K Wheel Loader: Mrk1-UpDocument14 pagesHydraulic System 994K Wheel Loader: Mrk1-Upfernando7jose7alcantNo ratings yet

- Types of SubstationDocument3 pagesTypes of SubstationJesudhason Prince100% (2)

- AC MotorDocument71 pagesAC Motorstallone21No ratings yet

- PDA Measurements and Quantities PDA Measurements and Quantities PDA Measurements and Quantities PDA Measurements and QuantitiesDocument32 pagesPDA Measurements and Quantities PDA Measurements and Quantities PDA Measurements and Quantities PDA Measurements and QuantitiesShyanakaNo ratings yet

- Lectures 4-5 Chapter 4 Fall 2009Document27 pagesLectures 4-5 Chapter 4 Fall 2009tewari_skNo ratings yet

- SHM & Elasticity: Ba C BC A Ba CDocument13 pagesSHM & Elasticity: Ba C BC A Ba CKrithikaNo ratings yet

- CH 22 FDocument21 pagesCH 22 FaklothNo ratings yet

- Module 1 Dynamics of MachinesDocument15 pagesModule 1 Dynamics of MachinesShubham kutteNo ratings yet

- CH 12 Physics AnswersDocument21 pagesCH 12 Physics AnswersSam Likes HamNo ratings yet

EE16A Spring 2020 MT2

EE16A Spring 2020 MT2

Uploaded by

Annabel YauOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

EE16A Spring 2020 MT2

EE16A Spring 2020 MT2

Uploaded by

Annabel YauCopyright:

Available Formats

EECS 16A Designing Information Devices and Systems I

Spring 2020 Midterm 2 Instructions

Read the following instructions before the exam.

Format & How to Submit Answers

There are 13 problems (4 introductory questions, and 9 exam questions, comprising 34 subparts total)

of varying numbers of points. The problems are of varying difficulty, so pace yourself accordingly and

avoid spending too much time on any one question until you have gotten all of the other points you can.

Don’t get bogged down in calculations; if you are having trouble with one problem, there may be easier

points available later in the exam!

All answers will be submitted to the Gradescope "Midterm 2" Assignment (https://www.gradescope.

com/courses/83747/assignments/427941). All questions, except introductory questions, are

multiple choice and are worth 4 points each. There are 125 points possible on the exam, but your final

score will be taken out of 100 points. This means that a score of 75/125, normally 60%, will be bumped

up to 75/100, or 75%. You cannot score more than 100% on this exam.

Partial credit may be given for certain incorrect answer choices for some problems. There is no penalty for

incorrect answers.

Post any content or clarifying questions privately on Piazza. There will be no exam clarifications; if we find

a bug on the exam, that sub-question will be omitted from grading.

Timing & Penalties

You have 120 minutes for the exam, with a 5 minute grace period. After the 5 minute grace period ends,

exam scores will be penalized exponentially as follows: an exam that is submitted N minutes after the end

of the grace period will lose 2N points. The exam will become available at your personalized link at 8:10

pm PT; the grace period will expire at 10:15 pm PT. If your submission is timestamped at 10:16 pm PT,

you will lose 2 points; if it is timestamped at 10:18 pm PT, you will lose 8 points.

We will count the latest time at which you submit any question as your exam timestamp. Do NOT edit

or resubmit your answers after the deadline. We recommend having all of your answers input and submitted

by 10:10 pm; it is your responsibility to submit the exam on time.

If you cannot access your exam at your link by 8:15 pm, please email eecs16a@berkeley.edu. If you are

having technical difficulties submitting your exam, you can email your answers (either typed or scanned) to

eecs16a@berkeley.edu.

Academic Honesty

EECS 16A, Spring 2020, Midterm 2 Instructions

This is an open-note, open-book, open-internet, and closed-neighbor exam. You may use any calculator

or calculation software that you wish, including Wolfram-Alpha and Mathematica. No collaboration is

allowed, and do not attempt to cheat in any way. Cheating will not be tolerated.

We have zero tolerance against violation of the Berkeley Honor Code. Given supporting evidence

of cheating, we reserve the right to automatically fail all students involved and report the instance

to the student conduct committee. Feel free to report suspicious activity through this form. (https:

//forms.gle/akhBsHVr1WG29Ufg9).

Our advice to you: if you can’t solve a particular problem, move on to another, or state and solve a simpler

one that captures at least some of its essence. You will perhaps find yourself on a path to the solution.

Good luck!

EECS 16A, Spring 2020, Midterm 2 Instructions

SID: 123456789, Calnet ID: eecs16a

EECS 16A Designing Information Devices and Systems I

Spring 2020 Midterm 2

1. Pledge of Academic Integrity (2 points)

By my honor, I affirm that:

(1) this document, which I will produce for the evaluation of my performance, will reflect my original,

bona fide work;

(2) as a member of the UC Berkeley community, I have acted and will act with honesty, integrity, and

respect for others;

(3) I have not violated—nor aided or abetted anyone else to violate—nor will I—the instructions for this

exam given by the course staff, including, but not limited to, those on the cover page of this document;

and

(4) I have not committed, nor will I commit, any act that violates—nor aided or abetted anyone else to

violate—the UC Berkeley Code of Student Conduct.

Write your name and the current date as an acknowledgement of the above. (See Gradescope)

2. Administrivia (1 point)

I know that I will lose 2n points for every n minutes I submit after the exam submission grace period is over.

For example, if the exam becomes available at my personalized link at 8:10 p.m. PT; the grace period will

expire at 10:15 p.m. PT. If my submission is timestamped at 10:16 p.m. PT, I will lose 2 points; if it is

timestamped at 10:18 p.m. PT, I will lose 8 points.

# Yes

3. What is one of your hobbies? (1 point)

4. Tell us about something you’re proud of this semester. (1 point)

EECS 16A, Spring 2020, Midterm 2 3

SID: 123456789, Calnet ID: eecs16a

5. Fun with Resistors (12 points)

(a) Your partner hands you an old beat-up four-band resistor, Rmystery where the second band has been worn

off with time. You can see that the first band is orange, the third band is yellow, and the fourth band is

gold. Which of the following ranges does the nominal value of this unknown resistance, Rmystery , fall

in? Do not consider the range allowed by the tolerance.

There is a resistor color code chart below:

Figure 1: Resistor Color Chart.

Figure 2: Rmystery .

EECS 16A, Spring 2020, Midterm 2 4

SID: 123456789, Calnet ID: eecs16a

For the rest of this problem, assume that you have an infinite supply of 5Ω and 20Ω resistors.

(b) What is the minimum number of resistors you need to create a resistor network with an equivalent

resistance equal to 4Ω?

(c) What is the minimum number of resistors you need to create a resistor network with an equivalent

resistance equal to 9Ω?

EECS 16A, Spring 2020, Midterm 2 5

SID: 123456789, Calnet ID: eecs16a

6. (16 points) Analyzing a Resistor Network

Consider the following circuit.

A R4 D

− +

V4

R1 R2

B I1 R7 I2

I7

I5 R5 −

R3 V3

C R6 + E

− +

V6

(a) Each branch in the circuit is either labelled with a branch current direction or a branch voltage polarity,

but not both. For the branches corresponding to R1 and R2 , label the missing quantity according to

passive sign convention.

(b) All resistors have a value of 72R. Find the equivalent resistance between terminals C and E, RCE ,

in terms of R, and also find the equivalent resistance between terminals A and B, RAB , in terms of R.

Assume that when finding the equivalent resistance between two terminals, all the other terminals are

left as is, with nothing attached to them.

EECS 16A, Spring 2020, Midterm 2 6

SID: 123456789, Calnet ID: eecs16a

The circuit has been duplicated again here for your convenience for parts (c) and (d). The labels 1 ,

2 , and 3 correspond to locations in the circuit schematic.

A R4 1 D

− +

V4

R1 R2

B I1 2 R7 I2

I7

I5 R5 −

R3 V3

C R6 + E

− +

V6 3

(c) Write the KVL equation equation for the loop A - 1 - D - E - 3 - 2 - B - A in terms of V1 to V7

using passive sign convention.

(d) Write the KCL equation for the node associated with terminal E in terms of the currents I1 to I7 using

passive sign convention.

EECS 16A, Spring 2020, Midterm 2 7

SID: 123456789, Calnet ID: eecs16a

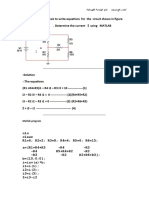

7. (8 points) Linearity of circuits

Consider the following circuit with resistor values R1 = 9Ω, R2 = 1Ω, R3 = 6Ω, and R4 = 4Ω.

R1

V1 V2 I3

I1

R2 R3

I2

Vs + V3

−

Is

V4

I4 R4

(a) In order to analyze this circuit, Nirmaan wrote down a system of equations for the circuit and then cast

it into matrix-vector form. However, some of the entries of the matrix were smudged, and Nirmaan

needs your help filling in the missing entries. Fill in the missing values in the matrix below. Hint:

Rows (2)-(4) correspond to KCL equations. Rows (5) - (8) correspond to Ohm’s Law equations.

0 0 0 0 (C1 ) 0 0 0 I1 Vs

1 1 1 0 0 0 0 0 I2 0

0 0 0 0 0 0 I3 Is

(C2 ) (C2 )

0 0 0 1 0 0 0 0 I4 = −Is

0 0 0 1 −1 0 0 V1 0

(C3 )

0 0 0 0 −1 1 0

(C4 ) V2 0

0 0 (C5 ) 0 0 −1 1 0 V3 0

0 0 0 (C6 ) 0 0 0 −1 V4 0

EECS 16A, Spring 2020, Midterm 2 8

SID: 123456789, Calnet ID: eecs16a

(b) Now consider the same circuit, except with different resistor values.

R1

V1 V2 I3

I1

R2 R3

I2

Vs + V3

−

Is

V4

I4 R4

When Vs = 15V , Is = −8A, and R1 = R2 = R3 = R4 = 4 Ω, we have that the solution to the above

system of equations is the vector:

I1 −8

I2 4

I3 4

I4 8

=

V1 15

V2 −17

V3 −33

V4 32

What is the power dissipated across the voltage source, Vs ? What is the power dissipated across the

resistor R3 ?

EECS 16A, Spring 2020, Midterm 2 9

SID: 123456789, Calnet ID: eecs16a

8. Superposition (12 points)

Consider the following circuit:

R1 R2

Is R3 Vs +

−

IR3

Let R1 = 15.0Ω, R2 = 25.0Ω, R3 = 35.0Ω, Is = 1.0A, and Vs = 4.0V.

(a) With the current source turned on and the voltage source turned off, find the current IR3 .

(b) With the voltage source turned on and the current source turned off, find the voltage drop across R3 ,

VR3 .

(c) With both sources turned on, find the power dissipated across R3 .

EECS 16A, Spring 2020, Midterm 2 10

SID: 123456789, Calnet ID: eecs16a

9. Thévenin Equivalence (12 points)

(a) Find the Thévenin resistance Rth of the circuit shown below, with respect to its terminals A and B.

Assume that R1 = 4R, R2 = R and R3 = 9R.

R2

+ Vs R1

− A

R3

(b) Now a load resistor, RL = 9R, is connected across terminals A and B as shown in the circuit below.

Find the supply voltage, Vs , such that 1 mW is dissipated across the load resistor. Let R = 36kΩ.

R2

+ Vs R1

− A

R3 RL

EECS 16A, Spring 2020, Midterm 2 11

SID: 123456789, Calnet ID: eecs16a

(c) We modify the circuit as shown below:

R2 g(VA −Vout )

+ Vs R1

− A

+ +

R3 VA Vout RL R0

− −

B

Find a symbolic expression for Vout as a function of Vs .

EECS 16A, Spring 2020, Midterm 2 12

SID: 123456789, Calnet ID: eecs16a

10. Capacitive Charge Sharing (16 points)

φ1 u1 φ2 φ1

+ Vs1 C1 C2 + Vs2

− −

(a) Consider the circuit above with C1 = 6µF and C2 = 9µF. Suppose that initially the φ1 switches are

closed and the φ2 switch is open such that C1 and C2 are charged through the corresponding voltage

sources Vs1 = 6V and Vs2 = 17V. How much charge is on C1 and C2 ?

(b) Now suppose that some time later, the φ1 switches open and the φ2 switch closes. What is the value of

voltage u1 at steady state?

(c) Now let’s look at the following circuit. Once again, let C1 = 6 µF and C2 = 9 µF. Let Vs = 7V.

φ1 φ1 Vout

+ Vs φ2 C1 φ2 C2

−

φ1 φ1

Suppose that initially the φ1 switches are closed and the φ2 switches are open. How much charge is on

C1 and C2 ?

EECS 16A, Spring 2020, Midterm 2 13

SID: 123456789, Calnet ID: eecs16a

(d) Now suppose that some time later, the φ1 switches open and the φ2 switches close. What is the value

of voltage Vout at steady state?

EECS 16A, Spring 2020, Midterm 2 14

SID: 123456789, Calnet ID: eecs16a

11. Flash Memory (16 points)

Solid state drives depend on charge to store information. In several integrated circuit applications, the charge

is stored on a floating node of a transistor. A cartoon of such a transistor and its corresponding circuit model

are shown below. Note: You do not need to understand transistors in order to do this problem.

Gate

Vin + RL

− Floating Gate

Source Drain

Figure 3: Transistor schematic for flash memory.

Vout

CG

Vin + QT VFG gmVFG RL

−

CS

Figure 4: Corresponding circuit model for flash memory transistor from Figure 3.

Depending on the amount of charge on the floating node, the transistor is either storing a “0” bit or a “1”

bit. In order to write a bit, electrons are added or removed from the “floating gate node" (labelled by VFG

in Figure 4), which is capacitively coupled to the gate and the source of the transistor as shown in Figure 3.

Therefore, during transistor operation, there can be a net charge QT at the node VFG .1

In each part of the problem, the values of each parameter do not change, and are given in the table below:

Component Parameters

Vin 2.0V

CG 35.0pF

CS 3.0pF

gm 300.0µA V−1

RL 35.0kΩ

1 The method through which charge is added or removed from the floating gate is known as Fowler-Nordheim tunneling, where

electrons are quantum mechanically tunnelled to the floating gate. In this problem, we will not worry about how the net charge is

added to the floating gate node at the circuit level.

EECS 16A, Spring 2020, Midterm 2 15

SID: 123456789, Calnet ID: eecs16a

(a) Assuming that the floating gate node (VFG ) has no net charge (QT = 0). Find VFG in terms of Vin , CG ,

and CS , and then plug in values from the table.

(b) Now let’s assume there is a net charge of QT = −20.0pC on the floating gate node. Find VFG as a func-

tion of CG , CS , Vin , and QT and then plug in the numerical values. (Hint: Use conservation of charge.)

(c) Now, in order to read which bit the transistor is storing, we measure the value of Vout , which is the volt-

age drop across RL , as shown in Figure 4. Assuming that the threshold for reading a “1” bit is Vout ≤

−1 V, what condition must VFG satisfy? (Note: This part is independent of the previous two subparts.)

(d) Regardless of the answer you got in part (c), assume that the threshold for reading a “1” is VFG ≥

1 V. How much net charge, QT do you need on the floating gate node in order to read a “1”?

EECS 16A, Spring 2020, Midterm 2 16

SID: 123456789, Calnet ID: eecs16a

12. A Versatile Opamp Circuit (12 points)

The following circuit is a commonly used integrated circuit (IC) that can be configured in a variety of ways

to achieve different functionalities. The main advantage of this IC is that it provides precise circuit functions

without the need of a high precision resistor network.

25 kΩ 25 kΩ

A C

O

−

B D

25 kΩ 25 kΩ

In order to see this circuit’s versatility, we will configure this circuit in different ways to achieve different

functionalities. For each subpart, let v1 = 1.2V and v2 = 1.8V

(a) Determine the voltage at O for the following configuration.

25 kΩ 25 kΩ

C

A

+ v1 + v2

− + −

O

−

B D

25 kΩ 25 kΩ

EECS 16A, Spring 2020, Midterm 2 17

SID: 123456789, Calnet ID: eecs16a

(b) Determine the voltage at O for the following configuration.

25 kΩ 25 kΩ

A C

+ v1

− +

O

−

B D

25 kΩ 25 kΩ

+ v2

−

(c) Determine the voltage at O for the following configuration.

25 kΩ 25 kΩ

C

A

+ v1 + v2

− + −

O

−

B D

25 kΩ 25 kΩ

EECS 16A, Spring 2020, Midterm 2 18

SID: 123456789, Calnet ID: eecs16a

EECS 16A, Spring 2020, Midterm 2 19

SID: 123456789, Calnet ID: eecs16a

13. Odometer (16 points)

You are designing a circuit for an car odometer, which measures the distance the car has travelled. The main

circuit element that you have is a resistor, whose resistance changes as a function of car velocity, which

varies with time:

4.0αR0

Rcar (t) =

v(t)

where R0 = 100.0kΩ, α = 60.0 ms , and v is the velocity of the car in m

s. Throughout the problem, assume

that the capacitor is initially uncharged.

(a) Not knowing where to start, you ask a senior member of the design team, who went to Berkeley, and

he gives you the following circuit to get you started.

C

Rcar VDD

−

+

+

Vin + Vout

−

− VSS

As a first step, determine Vout in terms of t,Vin , α, R0 , v(t), and C. (Hint: Apply KCL and use the fact

that I = C dV

dt .)

(b) Regardless of the answer to part (a), the output of the above circuit is given by: Vout (t) = − αR10C 0t Vin v(τ)dτ.

R

Now, you decide to set Vin = 1 V. Your odometer increases its distance reading by 1 when the voltage,

Vout , decreases by 0.1 V.

If you want the odometer to change its distance reading by 1 when the car travels 1 kilometer, what

should C be? Hint: The distance travelled by the car is given by 0t v(τ) dτ.

R

EECS 16A, Spring 2020, Midterm 2 20

SID: 123456789, Calnet ID: eecs16a

(c) Your car has the following velocity versus time graph. How much energy is dissipated through the car

resistor, Rcar (t) = 4.0αR

v(t) ? Assume that Vin for the circuit given in part (a) is still 1 V.

0

40

30

v(t) [ ms ]

20

10

t [s]

30 60 90

EECS 16A, Spring 2020, Midterm 2 21

SID: 123456789, Calnet ID: eecs16a

(d) In order to add functionality, you want to add a comparator that will alert the driver when a certain

number of kilometers has passed, using the odometer you designed in part (b). You do this with the

following circuit:

VDD

Vout, ckt1 +

Vout

−

Rle f t Rright VSS

-20 V +

−

Vout, ckt1 = − αR10C 0t Vin v(τ)dτ is the output of odometer circuit shown in part (a). If you want the

R

comparator to change states after the car has driven 180.0km, given that we require Rle f t + Rright =

70.0kΩ, what should the value of Rle f t be?

EECS 16A, Spring 2020, Midterm 2 22

You might also like

- Grade 1 Sses ScienceDocument7 pagesGrade 1 Sses ScienceDorothy Manalang100% (3)

- Lab Report 2Document6 pagesLab Report 2Abdul Aziz ZulkifliNo ratings yet

- Joseph J. WEED - A Rosicrucian Speaks-Chatsworth Press (1965) PDFDocument179 pagesJoseph J. WEED - A Rosicrucian Speaks-Chatsworth Press (1965) PDFDewdman42No ratings yet

- Student WorkDocument12 pagesStudent Workapi-36422456048% (42)

- Magnetic Compass PDFDocument19 pagesMagnetic Compass PDFHashil Naseer100% (1)

- Type KAVR 130: Auto-Reclose and Check Synchronism RelayDocument120 pagesType KAVR 130: Auto-Reclose and Check Synchronism RelayThai Dang VuNo ratings yet

- Samsung Le26 32 37 Le40r73 Le40r74bdr Xeu Chassis Gly26 32 37 40keDocument274 pagesSamsung Le26 32 37 Le40r73 Le40r74bdr Xeu Chassis Gly26 32 37 40keVenancio Luis Amor PerezNo ratings yet

- Test I: 'Xnh8QlyhuvlwDocument6 pagesTest I: 'Xnh8QlyhuvlwJustino LorenzoNo ratings yet

- Answers Should Be Written in QCAB Format Only.: InstructionsDocument92 pagesAnswers Should Be Written in QCAB Format Only.: InstructionsAkash yadavNo ratings yet

- Test I: 'Xnh8QlyhuvlwDocument13 pagesTest I: 'Xnh8QlyhuvlwJustino LorenzoNo ratings yet

- Test I: 'Xnh8QlyhuvlwDocument6 pagesTest I: 'Xnh8QlyhuvlwJustino LorenzoNo ratings yet

- CS2020 1516 Semester 2Document24 pagesCS2020 1516 Semester 2Eunice LimNo ratings yet

- CS302 Collection of Old PapersDocument48 pagesCS302 Collection of Old Paperscs619finalproject.comNo ratings yet

- Mid ExamDocument2 pagesMid ExamHuzaifaNo ratings yet

- 2017S FE AM QuestionDocument28 pages2017S FE AM Questionfqnguyen8No ratings yet

- Answers Should Be Written in QCAB Format Only.: InstructionsDocument82 pagesAnswers Should Be Written in QCAB Format Only.: InstructionsCaraNo ratings yet

- CS2020 1516 Semester 2 AnsDocument27 pagesCS2020 1516 Semester 2 AnsEunice LimNo ratings yet

- Test I: 'Xnh8QlyhuvlwDocument6 pagesTest I: 'Xnh8QlyhuvlwJustino LorenzoNo ratings yet

- Comparch Answers and QuestionsDocument7 pagesComparch Answers and QuestionsAngela KasekeNo ratings yet

- Arduino GuideDocument11 pagesArduino Guidesindhu bhargaviNo ratings yet

- Final Exam EE303 Microprocessor Interfacing & Programming: Total Time: 3 Hour Total Marks: 120 Course InstructorDocument14 pagesFinal Exam EE303 Microprocessor Interfacing & Programming: Total Time: 3 Hour Total Marks: 120 Course InstructorMuneeb Ahmad NasirNo ratings yet

- Circuits and Signals I Exam Question PaperDocument8 pagesCircuits and Signals I Exam Question PaperMrmouzinhoNo ratings yet

- Experiment 5 Series & Parallel Circuits Voltage Divider & Current Divider RulesDocument5 pagesExperiment 5 Series & Parallel Circuits Voltage Divider & Current Divider RulesPrincess Lheakyrie CasilaoNo ratings yet

- Digital Logic Design - CS302 Spring 2005 Mid Term PaperDocument4 pagesDigital Logic Design - CS302 Spring 2005 Mid Term PaperRameen QureshiNo ratings yet

- 1.5.10 Packet Tracer - Verify Directly Connected NetworksDocument4 pages1.5.10 Packet Tracer - Verify Directly Connected NetworksHạnhNo ratings yet

- EEE2211 Lab ManualDocument30 pagesEEE2211 Lab ManualMuhammed AslamNo ratings yet

- Experiment 05Document5 pagesExperiment 05ehtishamNo ratings yet

- Weekly Test-30 Sankalp2325s1, T1 & P1 Paper & Answer Key (Xii)Document23 pagesWeekly Test-30 Sankalp2325s1, T1 & P1 Paper & Answer Key (Xii)agnit.dgNo ratings yet

- Circuit Simulation With SpiceDocument6 pagesCircuit Simulation With SpicejmdelacruzNo ratings yet

- Section Classification 1 Mark 2 Marks Total Number of QuestionsDocument3 pagesSection Classification 1 Mark 2 Marks Total Number of QuestionsSaurav GoyalNo ratings yet

- Elektor BusDocument6 pagesElektor BusFernando VidalNo ratings yet

- Packet Tracer - Verify Directly Connected Networks: Addressing TableDocument3 pagesPacket Tracer - Verify Directly Connected Networks: Addressing TableBrayan EsneiderNo ratings yet

- National Standard Examination in Junior Science (Nsejs) Ijso Stage-IDocument11 pagesNational Standard Examination in Junior Science (Nsejs) Ijso Stage-IRashad AlamNo ratings yet

- s4623970 - Abhishekkumar PatelDocument17 pagess4623970 - Abhishekkumar Patelmuhammad iftikharNo ratings yet

- ECE 3144 Lecture 8: Dr. Rose Q. Hu Electrical and Computer Engineering Department Mississippi State UniversityDocument10 pagesECE 3144 Lecture 8: Dr. Rose Q. Hu Electrical and Computer Engineering Department Mississippi State UniversityGopakumar G NairNo ratings yet

- EE Afternoon New1 PDFDocument5 pagesEE Afternoon New1 PDFanon_12881478No ratings yet

- PDFDocument9 pagesPDFDennis KorirNo ratings yet

- NIT5110 2018 Exam SampleDocument20 pagesNIT5110 2018 Exam SamplePartha Sarathi NandiNo ratings yet

- Microprocessor Interfacing and System Design QuestionDocument4 pagesMicroprocessor Interfacing and System Design QuestionSharif Shah NewazNo ratings yet

- Faculty of Engineering: Circuits and Signals EEL 2186 TRIMESTER 1 (2014/2015)Document7 pagesFaculty of Engineering: Circuits and Signals EEL 2186 TRIMESTER 1 (2014/2015)Rameshkumar JayaramanNo ratings yet

- Exp 3 - IED - Lab Group 7Document10 pagesExp 3 - IED - Lab Group 7Kazi ShahadatNo ratings yet

- Final Dec 2003Document6 pagesFinal Dec 2003api-3755462No ratings yet

- EECS 489: Final Exam, Fall 2018: Duration: 70 MinutesDocument7 pagesEECS 489: Final Exam, Fall 2018: Duration: 70 MinutesTayyaba AsifNo ratings yet

- Project 1 Power SupplyDocument4 pagesProject 1 Power Supplyajnabi313No ratings yet

- Exam DM 071214 AnsDocument7 pagesExam DM 071214 AnsEyad GoudaaNo ratings yet

- Digital Logic and Circuits: Assignment For CO AchievementDocument2 pagesDigital Logic and Circuits: Assignment For CO Achievementanon_776365175No ratings yet

- ACS133 Assignment 2 - Briefing 2023-2024Document6 pagesACS133 Assignment 2 - Briefing 2023-2024Joash MacentonNo ratings yet

- IT5551ComputerNetworks Test2 Dec2022Document8 pagesIT5551ComputerNetworks Test2 Dec2022gauthamNo ratings yet

- R1 6Ω R4 4Ω R5 6Ω V1 10 VDocument63 pagesR1 6Ω R4 4Ω R5 6Ω V1 10 Vď èNo ratings yet

- Lab 11.1 - Use Ping and Traceroute To Test Network ConnectivityDocument4 pagesLab 11.1 - Use Ping and Traceroute To Test Network ConnectivityRecky JimmyNo ratings yet

- JEE Advanced Sample Papers 2 (Paper 1 & 2) by FIITJEEDocument71 pagesJEE Advanced Sample Papers 2 (Paper 1 & 2) by FIITJEEAvneesh GautamNo ratings yet

- Class: Be Eee Iv Sem (Aicte) Faculty: Mr. Praveen Reddy Maali Sub: Digital Electronics and Logic Design Total Marks: 20 1Document5 pagesClass: Be Eee Iv Sem (Aicte) Faculty: Mr. Praveen Reddy Maali Sub: Digital Electronics and Logic Design Total Marks: 20 1PRAVEEN REDDYNo ratings yet

- Midterm Spring Answer 2020Document6 pagesMidterm Spring Answer 2020p227738930No ratings yet

- R R R R R R V R I: Instructions: Fill in Each Blank With The Appropriate Answer. If Explanation Is RequiredDocument5 pagesR R R R R R V R I: Instructions: Fill in Each Blank With The Appropriate Answer. If Explanation Is RequiredEarl Cris RiggsNo ratings yet

- Finalterm Examination: Please Read The Following Instructions Carefully Before Attempting Any of The QuestionsDocument4 pagesFinalterm Examination: Please Read The Following Instructions Carefully Before Attempting Any of The QuestionsRai Abdul Waheed AhmadNo ratings yet

- 2017A FE AM QuestionDocument30 pages2017A FE AM QuestionShah AlamNo ratings yet

- CPSC 213, Winter 2013, Term 2 - Sample Midterm Questions: Date: February 2014 Instructor: Mike FeeleyDocument8 pagesCPSC 213, Winter 2013, Term 2 - Sample Midterm Questions: Date: February 2014 Instructor: Mike FeeleyDanielle SimpsonNo ratings yet

- Bölüm Soruları - 5th-EditionDocument14 pagesBölüm Soruları - 5th-EditionBee MiteNo ratings yet

- Ec: Electronics and Communication Engineering: Duration: Three HoursDocument24 pagesEc: Electronics and Communication Engineering: Duration: Three HoursMarshall LeeNo ratings yet

- BN208-Networked Applications - T1 2020 - Assessment PaperDocument9 pagesBN208-Networked Applications - T1 2020 - Assessment PaperMuhammad YousafNo ratings yet

- 04 30067 Electronic Engineering January 2022 Exam PaperDocument10 pages04 30067 Electronic Engineering January 2022 Exam PaperCharlie CoxNo ratings yet

- Digital Logic Design - CS302 Spring 2006 Final Term PaperDocument4 pagesDigital Logic Design - CS302 Spring 2006 Final Term PaperNamal No OorNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- EE16A Spring 2019 MT1Document23 pagesEE16A Spring 2019 MT1Annabel YauNo ratings yet

- Eecs 16A Designing Information Devices and Systems I Spring 2019 Exam Location: Cory 144MA (DSP)Document46 pagesEecs 16A Designing Information Devices and Systems I Spring 2019 Exam Location: Cory 144MA (DSP)Annabel YauNo ratings yet

- EE16A Spring 2019 MT2Document26 pagesEE16A Spring 2019 MT2Annabel YauNo ratings yet

- EE16A Spring 2020 MT1Document18 pagesEE16A Spring 2020 MT1Annabel YauNo ratings yet

- Engineering Mechanics DynamicsDocument2 pagesEngineering Mechanics DynamicsMallene EhurangoNo ratings yet

- Contactor by EE Controls PDFDocument10 pagesContactor by EE Controls PDFPaul MendozaNo ratings yet

- Users Guide FMG Series Electromagnetic FlowmeterDocument44 pagesUsers Guide FMG Series Electromagnetic Flowmeterdhan210No ratings yet

- Presentation of The Lesson:: (Self / Subject ..)Document3 pagesPresentation of The Lesson:: (Self / Subject ..)Lady Amor Telompros PeroteNo ratings yet

- 1 Soalan 1Document7 pages1 Soalan 1Radziah MohamedNo ratings yet

- Exam Style Answers P1 Asal Physics CBDocument2 pagesExam Style Answers P1 Asal Physics CBAnshul ShahNo ratings yet

- WWW - Manaresults.Co - In: II B. Tech I Semester Regular/Supplementary Examinations, Dec - 2015 Electrical Machiens-IDocument5 pagesWWW - Manaresults.Co - In: II B. Tech I Semester Regular/Supplementary Examinations, Dec - 2015 Electrical Machiens-IniharikaNo ratings yet

- Atoms and Static Electricity: Fun FactDocument3 pagesAtoms and Static Electricity: Fun FactXavier McCulloughNo ratings yet

- SIOP Lesson Plan (3) 3-14-13Document4 pagesSIOP Lesson Plan (3) 3-14-13ksal78No ratings yet

- PH1 ProbSet 5Document2 pagesPH1 ProbSet 5akshat shNo ratings yet

- EE301 Power Generation Transmission and Protection PDFDocument3 pagesEE301 Power Generation Transmission and Protection PDFMalavika SNo ratings yet

- 2 Ece II Engineering Physics (14phy22) NotesDocument138 pages2 Ece II Engineering Physics (14phy22) NotesSGSNo ratings yet

- DTCDocument18 pagesDTCVenkatesh TomNo ratings yet

- Mechanics: A̅ W MGDocument5 pagesMechanics: A̅ W MGfarujoyNo ratings yet

- Load Flow Analysis Of132/11Kv Substation Using Etap: A Case StudyDocument10 pagesLoad Flow Analysis Of132/11Kv Substation Using Etap: A Case Studydsanmi1234No ratings yet

- Hydraulic System 994K Wheel Loader: Mrk1-UpDocument14 pagesHydraulic System 994K Wheel Loader: Mrk1-Upfernando7jose7alcantNo ratings yet

- Types of SubstationDocument3 pagesTypes of SubstationJesudhason Prince100% (2)

- AC MotorDocument71 pagesAC Motorstallone21No ratings yet

- PDA Measurements and Quantities PDA Measurements and Quantities PDA Measurements and Quantities PDA Measurements and QuantitiesDocument32 pagesPDA Measurements and Quantities PDA Measurements and Quantities PDA Measurements and Quantities PDA Measurements and QuantitiesShyanakaNo ratings yet

- Lectures 4-5 Chapter 4 Fall 2009Document27 pagesLectures 4-5 Chapter 4 Fall 2009tewari_skNo ratings yet

- SHM & Elasticity: Ba C BC A Ba CDocument13 pagesSHM & Elasticity: Ba C BC A Ba CKrithikaNo ratings yet

- CH 22 FDocument21 pagesCH 22 FaklothNo ratings yet

- Module 1 Dynamics of MachinesDocument15 pagesModule 1 Dynamics of MachinesShubham kutteNo ratings yet

- CH 12 Physics AnswersDocument21 pagesCH 12 Physics AnswersSam Likes HamNo ratings yet