Professional Documents

Culture Documents

Schematics Devboard: (I.Mx8M Customer Board)

Schematics Devboard: (I.Mx8M Customer Board)

Uploaded by

hdsetanhdsetaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Schematics Devboard: (I.Mx8M Customer Board)

Schematics Devboard: (I.Mx8M Customer Board)

Uploaded by

hdsetanhdsetaCopyright:

Available Formats

5 4 3 2 1

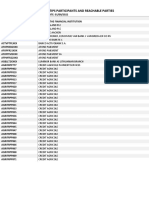

MCIMX8M-EVKB (i.MX8M Customer Board) Schematics DevBoard

Table of Content Revision History

Page 1 Cover

D Rev. Code Date By Description D

Page 2 Block Diagram A 2018-09-06 Javen 1 Revision preliminary version

Page 3 PWR TREE A1 2019-03-12 Javen 1 Replace PTN5110DHQ with PTN5110NHQZ for U907

Replace PTN36043BX with PTN36043ABX for U901

Page 4 CPU PWR DNP R905,R909,R910,R911

DNP 280-76498(BH1401-BH1404)

Update U101 with new PN MIMX8MQ6DVAJZAB

Page 5 LPDDR4 Update U1602 to IRM-V538M3/TR1

Page 6 CPU IO

Page 7 CPU PHY

Page 8 CPU MISC

Page 9 eMMC/NAND/TF/QSPI

Page 10 PMIC

C C

Page 11 BOOT CFG

Page 12 USB

Page 13 HDMI

Page 14 CODEC

Page 15 Ethernet

Page 16 WiFi/BT

Page 17 PCIe

Page 18 MIPI/DSI/CSI

Page 19 MicroSD/IR/LED/BTN

B Page 20 Debug B

Page 21 EXP CN

Page 22 NOTE

Page 23 IOMUX

Page 24

Page 25

Page 26

Page 27

Page 28

Page 29

A

3. Device type number is for reference only. The Microcontroller Product Group

A

number varies with the manufacturer. Preliminary - Subject to Change without Notice!

1. Unless Otherwise Specified: 6501 William Cannon Drive West

Austin, TX 78735-8598

All resistors are in ohms, 10%, 1/8 Watt,0603 4. Special signal usage: This board was designed for maximum flexibility in This document contains information proprietary to NXP and shall not be used for engineering design,

procurement or manufacture in whole or in part without the express written permission of NXP Semiconductors.

All capacitors are in uF, 20%, 50V,0603 _B Denotes - Active-Low Signal software development and demonstrates multiple ICAP Classification: CP: ___ IUO: _X_ PUBI: ___

All voltages are DC <> or [] Denotes - Vectored Signals functions possible with i.MX processors. Although best Designer: Drawing Title:

design practices have been applied, some areas may <JW>

MCIMX8M-EVKB

All polarized capacitors are aluminum electrolytic not be suitable for a mass-production design.

5. Interpret diagram in accordance with American Drawn by:

<JW>

Page Title:

Title and Rev History

2. Interrupted lines coded with the same letter or letter National Standards Institute specifications, current Approved: Size Document Number Rev

combinations are electrically connected. revision, with the exception of logic block symbology. <Approver> C SCH-38820 PDF: SPF-38820 A1

Date: Thursday, April 25, 2019 Sheet 1 of 23

5 4 3 2 1

5 4 3 2 1

i.MX8M EVK BLOCK DIAGRAM

D

##### MCIMX8M-EVKB ##### SoC: MIMX8MQ6DVAJZAA D

MIPI DSI MIPI CSI JTAG Infrared

/ LED

mini-SAS CN x2 mini-SAS CN 10 PIN Header

# SOM Board

LANE x4 LANE x4 JTAG GPIO/PWM

MIPI DSI MIPI CSI UART PWM 2.4/5GHz

USB TYPE-C (5-20V) USB TYPE-C USB 2.0/3.0 OTG

USB OTG1 SDIO/UART/PCM

COB WiFi/BT

DRP IEEE802.11b/g/n/ac

BT4.1

C C

PMIC

NXP

POWER NANDF QSPI

NXP PF4210 NAND/QSPI Micron QSPI 256Gb:

MT25QL256ABA1EW9

DC IN 12V

DRAM Audio DAC

3.5mm POLE

Micron LPDDR4

x32 bits

DRAM i.MX8M SAI

I2S

Cirrus Logic WM8524 HSL HSR MIC GND

MT53B768M32D4NQ-062 WT:B ARM CORTEX A53 1.5GHz

4x A53 + M4

Ethernet

RGMII RJ45

Flash eMMC x8 bits

SDIO

Gigabit:

Qualcomm: AR8031

eMMC 5.0: 16GB

B

USB HOST B

MicroSD x4 bits

SDIO

USB OTG2

USB 2.0/3.0

SD3.0 Support

Button

1. ONOFF

ONOFF/GPIO x2 UART(A53/M4) DBG UART

2. Reset GPIO/UART SAI/I2C PCIe UART->USB CP2105

GPIO/UART... GPIO/SAI/I2C... PCIe/SDIO/UART/PCM...

HDMI 2.0a Audio Card M.2 NGFF

TYPE-A SAI/GPIO/I2C... KEY-E:WiFi/BT...

A A

Microcontroller Product Group

6501 William Cannon Drive West

Austin, TX 78735-8598

This document contains information proprietary to NXP and shall not be used for engineering design,

procurement or manufacture in whole or in part without the express written permission of NXP Semiconductors.

ICAP Classification: CP: ___ IUO: _X_ PUBI: ___

Designer: Drawing Title:

<JW>

MCIMX8M-EVKB

Drawn by: Page Title:

<JW> Block Diagram

Approved: Size Document Number Rev

<Approver> C SCH-38820 PDF: SPF-38820 A1

Date: Thursday, April 25, 2019 Sheet 2 of 23

5 4 3 2 1

5 4 3 2 1

DC IN (12V)

VSYS

DCDC BUCK

MPS MP8759GD

3.3V/8A

USB TYPE-C

LDO

PMIC: PF4210 AP7343D CPU: i.MX8M

0.9V/300mA

SEQ PWR TYP Curr(mA) SEQ PWR TYP Curr(mA)

1 NVCC_SNVS 3.3 2

2 VDD_SNVS 0.9 2 2 VDD_SNVS 0.9 2

RTC_RESET_B

3 VDD_SOC/VDDA_0P9 0.9 3600

D D

4 VDD_ARM 0.9/1.0 4000

4 SW1A/B 0.9 2500 4 VDD_GPU 0.9/1.0 2000

4 SW1C 0.9 2000 4 VDD_VPU 0.9/1.0 1000

4 SW3A/B 1.0 3000 4 VDD_DRAM 1.0 2500

5 VGEN4 1.8 350 5 VDDA_1P8_xxx 1.8 250

5 VDDA_DRAM 1.8 50

6 NVCC_3V3 3.3 150

6 SW4 1.8 1000 6 NVCC_1V8 1.8 100

6 SW2 1.1 2500 6 NVCC_DRAM 1.1/1.2/1.35 700

6 NVCC_SD2 1.8/3.3

7 VGEN3 1.8 100 7 1.8V PHY 1.8 50

7 VGEN2 0.9 250 7 0.9V PHY 0.9 250

7 VGEN5 3.3 100 7 3.3V PHY 3.3 100

7 VGEN1 1.5 100 POR_B

7 VGEN6 2.8 200

LPDDR4

DCDC BUCK VDD1

MPS MP2147

VDD2/VDDQ

0.9V/4A

DCDC BUCK QSPI

MPS MP2147

C 0.9V/4A VCC C

LdSW

3.3V

eMMC/MicroSD

LDO

LDCL015MR VCCQ

1.8/3.3V/150mA VCC

DCDC BUCK

MPS MP2263

Ethernet AR8031

5V/3A

AVDD33

WiFi/BT

VBAT

M850-AUDIO BOARD VIO

Audio DAC

AVDD/LINE VDD

B B

MicroSD

VCC

HDMI

5V

mini-SAS

(MIPI CSI/DSI)

1.8V

3.3V

5V

M.2 PCIe

3.3V

USB Host/Type-C

A

VBUS A

PTN36043

MCIMX8M-EVK Board PWR TREE Microcontroller Product Group

6501 William Cannon Drive West

Austin, TX 78735-8598

This document contains information proprietary to NXP and shall not be used for engineering design,

procurement or manufacture in whole or in part without the express written permission of NXP Semiconductors.

ICAP Classification: CP: ___ IUO: _X_ PUBI: ___

Designer: Drawing Title:

<JW>

MCIMX8M-EVKB

Drawn by: Page Title:

<JW> Power Tree

Approved: Size Document Number Rev

<Approver> Custom SCH-38820 PDF: SPF-38820 A1

Date: Thursday, April 25, 2019 Sheet 3 of 23

5 4 3 2 1

5 4 3 2 1

U101M

i.MX8M PWR

W18 W4

NVCC_SNVS_3V3 R18 NVCC_SNVS NVCC_JTAG L18 NVCC_3V3 VDD_3V3 NVCC_3V3

VDD_SNVS_0V9 VDD_SNVS NVCC_NAND1 M18 C193 C194 C195 C196 C197 C198 C199 C1 C2 NVCC_JTAG_3V3

D

C101 C102 R8 NVCC_NAND2 L3 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF NVCC_GPIO_3V3 D

1uF 0.1uF R9 VDD_SOC1 NVCC_SAI1_1 K3 10V 10V 10V 10V 10V 10V 10V 10V 10V NVCC_UART_3V3

6.3V 10V R10 VDD_SOC2 NVCC_SAI1_2 J7 NVCC_NAND_3V3

R11 VDD_SOC3 NVCC_SAI2 E3 NVCC_SAI1_3V3

R12 VDD_SOC4 NVCC_SAI3 M3 NVCC_SAI2_3V3

R13 VDD_SOC5 NVCC_SAI5 R5 GND NVCC_SAI3_3V3

GND R14 VDD_SOC6 NVCC_GPIO1 R6 NVCC_SAI5_3V3

VDD_SOC_0V9 R15 VDD_SOC7 NVCC_GPIO2 H7 NVCC_I2C_3V3

C13 C104 C105 C106 C107 C109 C111 R16 VDD_SOC8 NVCC_I2C D8 NVCC_ECSPI_3V3

22uF 1uF 1uF 1uF 1uF 1uF 1uF T8 VDD_SOC9 NVCC_UART F5

10V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V K12 VDD_SOC10 NVCC_ECSPI M23 R101 0 5% DNP

L12 VDD_SOC11 NVCC_SD1_1 L23 NVCC_SD2

M12 VDD_SOC12 NVCC_SD1_2 N23 NVCC_SD1_1V8

P16 VDD_SOC13 NVCC_SD2 T18 NVCC_SD2

GND P12 VDD_SOC14 NVCC_ENET NVCC_ENET_2V5

P15 VDD_SOC15 C192 C191 C3

VDD_SOC16

1

L13 0.1uF 0.1uF 0.1uF

C116 C173 C112 C113 C145 C144 L104 M13 VDD_SOC17 10V 10V 10V

22uF 22uF 1uF 1uF 1uF 1uF N13 VDD_SOC18

240 OHM VDD_SOC19

10V 10V 6.3V 6.3V 6.3V 6.3V C146 P13

VDD_SOC20

2

T17

VDD_SOC21 G12 GND

1uF 6.3V V18 USB1_VDD33 G11 VDD_PHY_3V3

GND VDDA_0P9 USB2_VDD33 F12 C178 C8 C4

USB1_VPH F11 0.1uF 0.1uF 2.2uF

G15 USB2_VPH C12 10V 10V 10V

VDD_ARM_0V9 H15 VDD_ARM1 USB1_VPTX C11

C14 C165 C166 C121 C120 C122 C118 C119 J15 VDD_ARM2 USB2_VPTX D12

22uF 22uF 22uF 1uF 1uF 1uF 1uF 1uF K15 VDD_ARM3 USB1_VP D11 VDD_PHY_0V9

10V 10V 10V 6.3V 6.3V 6.3V 6.3V 6.3V L15 VDD_ARM4 USB2_VP E12 C179 C180 C5 GND U101N

M15 VDD_ARM5 USB1_DVDD E11 0.1uF 0.1uF 2.2uF V23 K13

G16 VDD_ARM6 USB2_DVDD 10V 10V 10V W22 VSSA_XTAL_25M VSSA_FPLL_ARM U16

H16 VDD_ARM7 VSSA_XTAL_27M VSSA_FPLL N12

GND J16 VDD_ARM8 VSSA_SPLL_VIDEO2 V17

C27 C28 C23 C24 K16 VDD_ARM9 VSSA_SPLL T14

1uF 1uF 1uF 1uF L16 VDD_ARM10 GND B25 VSSA_SPLL_DRAM

6.3V 6.3V 6.3V 6.3V M16 VDD_ARM11 C8 VSS1 AE2

G14 VDD_ARM12 C10 VSS2 VSS141 AD25

C C

H14 VDD_ARM13 H23 C13 VSS3 VSS140 AD16

VDD_ARM14 PCIE_VPH1 J23 VDD_PHY_3V3 C15 VSS4 VSS139 AD13

GND PCIE_VPH2 G23 C181 C6 A24 VSS5 VSS138 AD11

N8 PCIE_VPTX1 F23 VDD_PHY_0V9 0.1uF 2.2uF C24 VSS6 VSS137 AD9

N9 VDD_VPU1 PCIE_VPTX2 G22 C182 C183 C7 10V 10V D10 VSS7 VSS136 AD7

VDD_VPU_0V9 N10 VDD_VPU2 PCIE_VP1 F22 0.1uF 0.1uF 2.2uF D13 VSS8 VSS135 AD1

C15 C168 C167 C123 C125 C124 C29 P9 VDD_VPU3 PCIE_VP2 10V 10V 10V D15 VSS9 VSS134 AC22

22uF 22uF 22uF 1uF 1uF 1uF 1uF P10 VDD_VPU4 D23 VSS10 VSS133 AC19

10V 10V 10V 6.3V 6.3V 6.3V 6.3V VDD_VPU5 GND A2 VSS11 VSS132 AC4

J9 E4 VSS12 VSS131 AB24

K9 VDD_GPU1 GND E10 VSS13 VSS130 AB18

L9 VDD_GPU2 E13 VSS14 VSS129 AB11

GND M9 VDD_GPU3 P2 E14 VSS15 VSS128 AB9

J10 VDD_GPU4 HDMI_AVDDIO V3 VDD_PHY_1V8 E20 VSS16 VSS127 AB2

K10 VDD_GPU5 HDMI_AVDDCLK U3 VDD_PHY_0V9 C184 C9 E16 VSS17 VSS126 AA21

VDD_GPU_0V9 L10 VDD_GPU6 HDMI_AVDDCORE2 U4 C185 C186 C10 0.1uF 2.2uF E19 VSS18 VSS125 AA16

C16 C170 C169 C126 C128 C127 C21 C22 C31 C32 M10 VDD_GPU7 HDMI_AVDDCORE1 0.1uF 0.1uF 2.2uF 10V 10V E21 VSS19 VSS124 AA5

22uF 22uF 22uF 1uF 1uF 1uF 1uF 1uF 1uF 1uF VDD_GPU8 10V 10V 10V E22 VSS20 VSS123 Y24

10V 10V 10V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V E23 VSS21 VSS122 Y23

V9 F10 VSS22 VSS121 Y22

V15 VDD_DRAM1 GND F13 VSS23 VSS120 Y21

V14 VDD_DRAM2 GND F14 VSS24 VSS119 Y19

GND V13 VDD_DRAM3 C18 F20 VSS25 VSS118 Y17

V12 VDD_DRAM4 MIPI_VDDHA1 D17 VDD_PHY_1V8 F16 VSS26 VSS117 Y15

V11 VDD_DRAM5 MIPI_VDDHA2 D18 C187 C11 G9 VSS27 VSS116 Y13

VDD_DRAM_0V9 V10 VDD_DRAM6 MIPI_VDDHA3 E17 0.1uF 2.2uF G10 VSS28 VSS115 Y11

C17 C171 C131 C132 C134 C34 C130 C117 C129 C33 U11 VDD_DRAM7 MIPI_VDDA1 E18 10V 10V G13 VSS29 VSS114 Y9

22uF 22uF 1uF 1uF 1uF 1uF 0.01UF 0.01UF 4700PF 4700PF U14 VDD_DRAM8 MIPI_VDDA2 F17 G17 VSS30 VSS113 Y7

10V 10V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 10V 10V U12 VDD_DRAM9 MIPI_VDDA3 F18 L101 VDD_PHY_0V9 G18 VSS31 VSS112 Y5

U10 VDD_DRAM10 MIPI_VDDA4 E15 1 2 C188 C189 C190 C12 G24 VSS32 VSS111 Y4

U13 VDD_DRAM11 MIPI_VDD1 F15 0.1uF 0.1uF 0.1uF 2.2uF GND H8 VSS33 VSS110 Y3

Y6 VDD_DRAM12 MIPI_VDD2 F19 C19 C20 120OHM 10V 10V 10V 10V H9 VSS34 VSS109 Y2

GND Y8 VDD_DRAM13 MIPI_VDDPLL 0.1uF 0.1uF H10 VSS35 VSS108 W25

Y20 VDD_DRAM14 10V 10V H11 VSS36 VSS107 W16

C172 C110 C115 C108 C114 C135 C136 C133 C137 C138 Y18 VDD_DRAM15 H12 VSS37 VSS106 W15

22uF 4700PF 4700PF 4700PF 4700PF 4700PF 4700PF 4700PF 4700PF 4700PF Y16 VDD_DRAM16 GND H13 VSS38 VSS105 W14

10V 10V 10V 10V 10V 10V 10V 10V 10V 10V Y10 VDD_DRAM17 H17 VSS39 VSS104 W13

B VDD_DRAM18 GND H18 VSS40 VSS103 W12 B

J3 VSS41 VSS102 W11

B1 VSS42 VSS101 W10

GND J8 VSS43 VSS100 W8

AA11 J11 VSS44 VSS99 W7

K14 VDDA_DRAM J12 VSS45 VSS98 W1

U17 VDDA_1P8_FPLL_ARM J13 VSS46 VSS97 AE24

VDDA_1V8 W17 VDDA_1P8_FPLL J14 VSS47 VSS96 V16

C174 C149 C151 C150 C152 C147 C148 N11 VDDA_1P8_SPLL J17 VSS48 VSS95 V8

22uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF T15 VDDA_1P8_SPLL_VIDEO2 J18 VSS49 VSS94 V4

10V 10V 10V 10V 10V 10V 10V VDDA_1P8_SPLL_DRAM J19 VSS50 VSS93 U18

U23 K8 VSS51 VSS92 U15

T16 VDDA_1P8_LVDS K11 VSS52 VSS91 U9

W23 VDDA_1P8_TSENSOR N18 VSS53 VSS90 U8

GND W24 VDDA_1P8_XTAL_27M K17 VSS54 VSS89 AE21

VDDA_1P8_XTAL_25M K18 VSS55 VSS88 AE5

R17 K23 VSS56 VSS87 T13

EFUSE_VQPS L8 VSS57 VSS86 T12

AB23 L11 VSS58 VSS85 T11

AA10 NVCC_DRAM1 L14 VSS59 VSS84 T10

NVCC_DRAM_1V1 AB17 NVCC_DRAM2 L17 VSS60 VSS83 T9

C18 C175 C157 C156 C158 C153 C154 C139 C155 C140 AA15 NVCC_DRAM3 M8 VSS61 VSS82 T4

22uF 22uF 1uF 1uF 1uF 1uF 1uF 1uF 1uF 1uF AB8 NVCC_DRAM4 M11 VSS62 VSS81 T3

10V 10V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V AB3 NVCC_DRAM5 M14 VSS63 VSS80 W9

AC14 NVCC_DRAM6 M17 VSS64 VSS79 R7

AC17 NVCC_DRAM7 N3 VSS65 VSS78 P23

AC20 NVCC_DRAM8 N17 VSS66 VSS77 P18

GND AC3 NVCC_DRAM9 N14 VSS67 VSS76 P17

AC23 NVCC_DRAM10 P6 VSS68 VSS75 N15

AC8 NVCC_DRAM11 P8 VSS69 VSS74 N16

AC6 NVCC_DRAM12 P11 VSS70 VSS73 P14

AD21 NVCC_DRAM13 VSS71 VSS72

C176 C161 C103 C160 C177 C35 C36 C163 C162 C164 C159 AD18 NVCC_DRAM14

22uF 1uF 1uF 1uF 1uF 1uF 1uF 1uF 1uF 1uF 1uF AD5 NVCC_DRAM15 GND MIMX8MQ6DVAJZAB + MBF25004-15W/2.0P+T725 A1 GND

10V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V Y14 NVCC_DRAM16

Y12 NVCC_DRAM17

NVCC_DRAM18

A A

GND MIMX8MQ6DVAJZAB + MBF25004-15W/2.0P+T725 A1 Microcontroller Product Group

6501 William Cannon Drive West

Austin, TX 78735-8598

This document contains information proprietary to NXP and shall not be used for engineering design,

procurement or manufacture in whole or in part without the express written permission of NXP Semiconductors.

ICAP Classification: CP: ___ IUO: _X_ PUBI: ___

Designer: Drawing Title:

<JW>

MCIMX8M-EVKB

Drawn by: Page Title:

<JW> CPU PWR

Approved: Size Document Number Rev

<Approver> C SCH-38820 PDF: SPF-38820 A1

Date: Thursday, April 25, 2019 Sheet 4 of 23

5 4 3 2 1

5 4 3 2 1

DRAM_CA0_A

DRAM_CA1_A

DRAM_CA2_A

DRAM_CA3_A

AD17

AE16

AD20

AE20

U101A

CA1_A / A11 / A11

CA2_A / A7 / A7

i.MX8M - DDR

(LPDDR4/DDR4/DDR3)

CA0_A / A12 / A12(BC#) DRAM_DQ00

DRAM_DQ01

DRAM_DQ02

AE23

AD24

AE22

AD22

DRAM_DATA0_A

DRAM_DATA1_A

DRAM_DATA2_A

DRAM_DATA3_A

DRAM_nCS0_A

DRAM_nCS1_A

H4

H3

U201A

CS0_A

DMI0_A

DQ0_A

DQ1_A

DQ2_A

C3

B2

C2

E2

F2

DRAM_DMI0_A

DRAM_DATA0_A

DRAM_DATA1_A

DRAM_DATA2_A

DRAM_DATA3_A

LPDDR4

DRAM_CA4_A AD19 CA3_A / A8 / A8 DRAM_DQ03 AA24 DRAM_DATA4_A K5 CS1_A DQ3_A F4 DRAM_DATA4_A

DRAM_CA5_A AE19 CA4_A / A6 / A6 DRAM_DQ04 Y25 DRAM_DATA5_A NC_K5 DQ4_A E4 DRAM_DATA5_A

CA5_A / A5 / A5 DRAM_DQ05 AA25 DRAM_DATA6_A DRAM_CKE0_A J4 DQ5_A C4 DRAM_DATA6_A

DRAM_nCS0_A AE18 DRAM_DQ06 AB25 DRAM_DATA7_A DRAM_CKE1_A J5 CKE0_A DQ6_A B4 DRAM_DATA7_A

DRAM_nCS1_A AC18 CS0_A / CS0_n / CS0# DRAM_DQ07 AB22 DRAM_DATA8_A K8 CKE1_A DQ7_A

CS1_A / C0 / -- DRAM_DQ08 AA22 DRAM_DATA9_A NC_K8 D3 DRAM_SDQS0_T_A

DRAM_CKE0_A AC16 DRAM_DQ09 AA23 DRAM_DATA10_A DRAM_CK_T_A J8 DQS0_t_A E3 DRAM_SDQS0_C_A

DRAM_CKE1_A AE17 CKE0_A / CKE0 / CKE0 DRAM_DQ10 AA20 DRAM_DATA11_A NVCC_DRAM_1V1 DRAM_CK_C_A J9 CK_t_A DQS0_c_A

D CKE1_A / CKE1 / CKE1 DRAM_DQ11 AA18 DRAM_DATA12_A CK_c_A C10 DRAM_DMI1_A D

DRAM_CK_T_A AD14 DRAM_DQ12 AB19 DRAM_DATA13_A DRAM_CA0_A H2 DMI1_A

DRAM_CK_C_A AE14 CK_t_A / BG0 / BA2 DRAM_DQ13 AA19 DRAM_DATA14_A DRAM_CA1_A J2 CA0_A B11 DRAM_DATA8_A

CK_c_A / BG1 / A14 DRAM_DQ14 AA17 DRAM_DATA15_A DRAM_CA2_A H9 CA1_A DQ8_A C11 DRAM_DATA9_A

DRAM_DQ15 R206 DRAM_CA3_A H10 CA2_A DQ9_A E11 DRAM_DATA10_A

AB16 AD23 DRAM_DMI0_A 10K DRAM_CA4_A H11 CA3_A DQ10_A F11 DRAM_DATA11_A

-- / A4 / A4 DRAM_DM0 AB20 DRAM_DMI1_A 5% DRAM_CA5_A J11 CA4_A DQ11_A F9 DRAM_DATA12_A

DRAM_DM1 CA5_A DQ12_A E9 DRAM_DATA13_A

DRAM_CA0_B AE8 AC24 DRAM_SDQS0_T_A ODT_CA_A G2 DQ13_A C9 DRAM_DATA14_A

DRAM_CA1_B AE9 CA0_B / C2 / -- DRAM_DQS0_P AC25 DRAM_SDQS0_C_A ODT_CA_A DQ14_A B9 DRAM_DATA15_A

DRAM_CA2_B AC7 CA1_B / CAS_n(A15) / CAS# DRAM_DQS0_N DQ15_A

DRAM_CA3_B AE7 CA2_B / A13 / A13 AB21 DRAM_SDQS1_T_A D10 DRAM_SDQS1_T_A

DRAM_CA4_B AE6 CA3_B / BA0 / BA0 DRAM_DQS1_P AC21 DRAM_SDQS1_C_A DQS1_t_A E10 DRAM_SDQS1_C_A

DRAM_CA5_B AD6 CA4_B / A10(AP) / A10(AP) DRAM_DQS1_N DQS1_c_A

CA5_B / A0 / A0 Y3 DRAM_DMI0_B

DRAM_nCS0_B AC9 AE3 DRAM_DATA0_B DMI0_B

DRAM_nCS1_B AD8 CS0_B / -- / -- DRAM_DQ16 AD2 DRAM_DATA1_B AA2 DRAM_DATA0_B

CS1_B / -- / -- DRAM_DQ17 AE4 DRAM_DATA2_B DRAM_nCS0_B R4 DQ0_B Y2 DRAM_DATA1_B

DRAM_CKE0_B AD10 DRAM_DQ18 AD4 DRAM_DATA3_B DRAM_nCS1_B R3 CS0_B DQ1_B V2 DRAM_DATA2_B

DRAM_CKE1_B AE10 CKE0_B / CK_t_B / CK_B DRAM_DQ19 AA2 DRAM_DATA4_B N5 CS1_B DQ2_B U2 DRAM_DATA3_B

CKE1_B / CK_c_B / CK#_B DRAM_DQ20 Y1 DRAM_DATA5_B NC_N5 DQ3_B U4 DRAM_DATA4_B

DRAM_CK_T_B AD12 DRAM_DQ21 AA1 DRAM_DATA6_B DRAM_CKE0_B P4 DQ4_B V4 DRAM_DATA5_B

DRAM_CK_C_B AE12 CK_t_B / A2 / A2 DRAM_DQ22 AB1 DRAM_DATA7_B DRAM_CKE1_B P5 CKE0_B DQ5_B Y4 DRAM_DATA6_B

CK_c_B / A1 / A1 DRAM_DQ23 AB4 DRAM_DATA8_B N8 CKE1_B DQ6_B AA4 DRAM_DATA7_B

DRAM_DQ24 AA4 DRAM_DATA9_B NC_N8 DQ7_B

AC10 DRAM_DQ25 AA3 DRAM_DATA10_B DRAM_CK_T_B P8 W3 DRAM_SDQS0_T_B

-- / WE_n(A14) / WE# DRAM_DQ26 AA6 DRAM_DATA11_B NVCC_DRAM_1V1 DRAM_CK_C_B P9 CK_t_B DQS0_t_B V3 DRAM_SDQS0_C_B

DRAM_DQ27 AA8 DRAM_DATA12_B CK_c_B DQS0_c_B

DRAM_DQ28 AB7 DRAM_DATA13_B DRAM_CA0_B R2 Y10 DRAM_DMI1_B

AD15 DRAM_DQ29 AA7 DRAM_DATA14_B DRAM_CA1_B P2 CA0_B DMI1_B

AE15 -- / CK_c_A / CK#_A DRAM_DQ30 AA9 DRAM_DATA15_B DRAM_CA2_B R9 CA1_B AA11 DRAM_DATA8_B

AC12 -- / CK_t_A / CK_A DRAM_DQ31 R207 DRAM_CA3_B R10 CA2_B DQ8_B Y11 DRAM_DATA9_B

AE11 -- / ODT0 / ODT0 AD3 DRAM_DMI0_B 10K DRAM_CA4_B R11 CA3_B DQ9_B V11 DRAM_DATA10_B

AC15 -- / ODT1 / ODT1 DRAM_DM2 AB6 DRAM_DMI1_B 5% DRAM_CA5_B P11 CA4_B DQ10_B U11 DRAM_DATA11_B

AB15 -- / A3 / A3 DRAM_DM3 CA5_B DQ11_B U9 DRAM_DATA12_B

AE13 -- / A9 / A9 AC2 DRAM_SDQS0_T_B ODT_CA_B T2 DQ12_B V9 DRAM_DATA13_B

AC11 -- / ACT_n / A15 DRAM_DQS2_P AC1 DRAM_SDQS0_C_B ODT_CA_B DQ13_B Y9 DRAM_DATA14_B

AB10 -- / CS1_n / CS1# DRAM_DQS2_N DQ14_B AA9 DRAM_DATA15_B

C C

AB12 -- / RAS_n(A16) / RAS# AB5 DRAM_SDQS1_T_B DQ15_B

AA12 -- / BA1 / BA1 DRAM_DQS3_P AC5 DRAM_SDQS1_C_B W10 DRAM_SDQS1_T_B

-- / PARITY / -- DRAM_DQS3_N DQS1_t_B V10 DRAM_SDQS1_C_B

DQS1_c_B

GND R208 10K 5% DRAM_nRESET AB13 NVCC_DRAM_1V1

RESET_n / RESET_n / RESET# AB12

AA14 DRAM_nRESET T11 DNU_AB12 AB11

DRAM_VREF VREF / VREF / VREF RESET_N DNU_AB11 AB2

R205 240 1% AA13 DNU_AB2 AB1

C216 ZQ / ZQ / ZQ R203 240 1% DRAM_ZQ0 A5 DNU_AB1 AA12

0.1uF AB14 ZQ0 DNU_AA12 AA1

TP201 MTEST / MTEST / MTEST DNU_AA1

50V TP202 AC13 B12

MTEST1 / MTEST1(ALERT_n) / MTEST1 R204 240 1% DRAM_ZQ1 A8 DNU_B12 B1

ZQ1 DNU_B1 A12

MIMX8MQ6DVAJZAB + MBF25004-15W/2.0P+T725 A1 DNU_A12 A11

GND GND G11 DNU_A11 A2

NC_G11 DNU_A2 A1

DNU_A1

MT53B768M32D4NQ-062 WT:B

U201B

1.70-1.95V F1 A3

VDD_1V8 F12 VDD1_F1 VSS_A3 A10

C201 C202 C203 G4 VDD1_F12 VSS_A10 C1

DRAM_CK_T_A DRAM_CK_T_B 22uF 4.7uF 4.7uF G9 VDD1_G4 VSS_C1 C5

10V 6.3V 6.3V T4 VDD1_G9 VSS_C5 C8

T9 VDD1_T4 VSS_C8 C12

R201 R202 U1 VDD1_T9 VSS_C12 D2

150 150 U12 VDD1_U1 VSS_D2 D4

1% 1% GND VDD1_U12 VSS_D4 D9

C204 C205 VSS_D9 D11

DRAM_CK_C_A DRAM_CK_C_B 4.7uF 4.7uF VSS_D11 E1

6.3V 6.3V 1.06-1.17V A4 VSS_E1 E5

A9 VDD2_A4 VSS_E5 E8

F5 VDD2_A9 VSS_E8 E12

B

F8 VDD2_F5 VSS_E12 G1 B

GND H1 VDD2_F8 VSS_G1 G3

H5 VDD2_H1 VSS_G3 G5

H8 VDD2_H5 VSS_G5 G8

H12 VDD2_H8 VSS_G8 G10

NVCC_DRAM_1V1 K1 VDD2_H12 VSS_G10 G12

C206 C207 C208 K3 VDD2_K1 VSS_G12 J1

22uF 4.7uF 4.7uF K10 VDD2_K3 VSS_J1 J3

10V 6.3V 6.3V K12 VDD2_K10 VSS_J3 J10

N1 VDD2_K12 VSS_J10 J12

NVCC_DRAM_1V1 N3 VDD2_N1 VSS_J12 K2

N10 VDD2_N3 VSS_K2 K4

DRAM VREF GND N12 VDD2_N10

VDD2_N12

VSS_K4

VSS_K9

K9

R1 K11

C209 C210 R5 VDD2_R1 VSS_K11 N2

4.7uF 4.7uF R8 VDD2_R5 VSS_N2 N4

6.3V 6.3V R12 VDD2_R8 VSS_N4 N9

U5 VDD2_R12 VSS_N9 N11

R209 C218 U8 VDD2_U5 VSS_N11 P1

1.5k 0.1uF AB4 VDD2_U8 VSS_P1 P3

0.1% 50V GND AB9 VDD2_AB4 VSS_P3 P10

DNP DNP VDD2_AB9 VSS_P10 P12

VSS_P12 T1

C217 VSS_T1 T3

4.7uF 1.06-1.17V B3 VSS_T3 T5

6.3V DRAM_VREF NVCC_DRAM_1V1 B5 VDDQ_B3 VSS_T5 T8

C211 C212 C213 B8 VDDQ_B5 VSS_T8 T10

22uF 4.7uF 4.7uF B10 VDDQ_B8 VSS_T10 T12

10V 6.3V 6.3V D1 VDDQ_B10 VSS_T12 V1

R210 C219 D5 VDDQ_D1 VSS_V1 V5

1.5k 0.1uF D8 VDDQ_D5 VSS_V5 V8

0.1% 50V D12 VDDQ_D8 VSS_V8 V12

DNP DNP R215 GND F3 VDDQ_D12 VSS_V12 W2

0 F10 VDDQ_F3 VSS_W2 W4

U3 VDDQ_F10 VSS_W4 W9

U10 VDDQ_U3 VSS_W9 W11

W1 VDDQ_U10 VSS_W11 Y1

C214 C215 W5 VDDQ_W1 VSS_Y1 Y5

A A

GND GND GND 4.7uF 4.7uF W8 VDDQ_W5 VSS_Y5 Y8

6.3V 6.3V W12 VDDQ_W8 VSS_Y8 Y12

Microcontroller Product Group

AA3 VDDQ_W12 VSS_Y12 AB3 6501 William Cannon Drive West

LPDDR4 Power supply voltage ramp:

AA5 VDDQ_AA3 VSS_AB3 AB5 Austin, TX 78735-8598

RESET_n is held LOW. AA8 VDDQ_AA5 VSS_AB5 AB8 This document contains information proprietary to NXP and shall not be used for engineering design,

VREFDDR VDD1 >= VDD2 GND AA10 VDDQ_AA8 VSS_AB8 AB10 procurement or manufacture in whole or in part without the express written permission of NXP Semiconductors.

VDD2 >= VDDQ VDDQ_AA10 VSS_AB10

ICAP Classification: CP: ___ IUO: _X_ PUBI: ___

MT53B768M32D4NQ-062 WT:B Designer: Drawing Title:

GND <JW>

MCIMX8M-EVKB

Drawn by: Page Title:

<JW> LPDDR4

Approved: Size Document Number Rev

<Approver> C SCH-38820 PDF: SPF-38820 A1

Date: Thursday, April 25, 2019 Sheet 5 of 23

5 4 3 2 1

5 4 3 2 1

-Internal pullup resistors 27 kOhm;

-Internal pulldown resistor of 90kOhm is always enabled

D MIMX8MQ6DVAJZAA U101G

D

U101H

# NAND/QSPI i.MX8M - SAI

i.MX8M - NAND 21 SAI5_MCLK

SAI5_MCLK K4 A3 SAI1_MCLK

SAI1_MCLK 21

H19 NAND_nCE0 SAI5_MCLK SAI1_MCLK

NAND_CE0_B NAND_nCE1 QSPIA_nSS0 9 SAI5_RXFS SAI1_TXFS

G21 N4 H1

NAND_CE1_B NAND_nCE2 BT_DEV_WAKE 16,17 21 SAI5_RXFS SAI5_RXC SAI5_RXFS SAI1_TXFS SAI1_TXC SAI1_TXFS 21

F21 L5 E1

NVCC_SAI5

NAND_CE2_B NAND_nCE3 TCPC_nINT 12 21 SAI5_RXC SAI5_RXC SAI1_TXC SAI1_TXC 21

H20 NAND_nCE3 21

NAND_CE3_B SAI5_RXD0 M5 F2 SAI1_TXD0

NAND_ALE 21 SAI5_RXD0 SAI5_RXD1 SAI5_RXD0 SAI1_TXD0 SAI1_TXD1 SAI1_TXD0 11,21

G19 QSPIA_SCLK 9 R309 0 5% BT_REG_ON 16,17 21 SAI5_RXD1 L4 E2 SAI1_TXD1 11,21

NAND_ALE H21 NAND_CLE R310 0 5% DNP SAI5_RXD2 M4 SAI5_RXD1 SAI1_TXD1 B2 SAI1_TXD2

NAND_CLE NAND_nRE IPOD_nRST 11 21 SAI5_RXD2 SAI5_RXD3 SAI5_RXD2 SAI1_TXD2 SAI1_TXD3 SAI1_TXD2 11,21

K19 K5 D1

NAND_RE_B NAND_nWE USB1_SS_SEL 12 21 SAI5_RXD3 SAI5_RXD3 SAI1_TXD3 SAI1_TXD4 SAI1_TXD3 11,21

K22 NAND_nWE 21 D2 SAI1_TXD4 11,21

NAND_WE_B SAI1_TXD4

NVCC_NAND

K21 NAND_nWP SAI3_MCLK D3 C2 SAI1_TXD5

NAND_WP_B NAND_nREADY NAND_nWP 21 21 SAI3_MCLK SAI3_MCLK SAI1_TXD5 SAI1_TXD6 SAI1_TXD5 11,21

K20 NAND_nREADY 21 B3 SAI1_TXD6 11,21

NAND_READY_B SAI3_TXFS G3 SAI1_TXD6 C1 SAI1_TXD7

NVCC_SAI1

NAND_DQS 16,17 SAI3_TXFS SAI3_TXC SAI3_TXFS SAI1_TXD7 SAI1_TXD7 11,21

M20 C4

NAND_DQS BT_HOST_WAKE 16 16,17 SAI3_TXC SAI3_TXD SAI3_TXC SAI1_RXFS

16,17 SAI3_TXD C3 L1 SAI1_RXFS 21

G20 NAND_DATA0 NAND_DATA0 SAI3_TXD SAI1_RXFS K1 SAI1_RXC

NVCC_SAI3

NAND_DATA00 NAND_DATA1 NAND_DATA1 QSPIA_DATA0 9 SAI3_RXFS SAI1_RXC SAI1_RXC 21

J20 QSPIA_DATA1 9 21 SAI3_RXFS G4

NAND_DATA01 H22 NAND_DATA2 NAND_DATA2 SAI3_RXC F4 SAI3_RXFS K2 SAI1_RXD0

NAND_DATA02 NAND_DATA3 NAND_DATA3 QSPIA_DATA2 9 21 SAI3_RXC SAI3_RXD SAI3_RXC SAI1_RXD0 SAI1_RXD1 SAI1_RXD0 11,21

J21 F3 L2

NAND_DATA03 NAND_DATA4 QSPIA_DATA3 9 16,17,21 SAI3_RXD SAI3_RXD SAI1_RXD1 SAI1_RXD2 SAI1_RXD1 11,21

L20 H2 SAI1_RXD2 11,21

NAND_DATA04 J22 NAND_DATA5 SPDIF_TX F6 SAI1_RXD2 J2 SAI1_RXD3

NAND_DATA05 NAND_DATA6 21 SPDIF_TX SPDIF_RX SPDIF_TX SAI1_RXD3 SAI1_RXD4 SAI1_RXD3 11,21

L19 21 SPDIF_RX G6 J1 SAI1_RXD4 11,21

NAND_DATA06 M19 NAND_DATA7 SPDIF_EXT_CLK E6 SPDIF_RX SAI1_RXD4 F1 SAI1_RXD5

NAND_DATA07 21 SPDIF_EXT_CLK SPDIF_EXT_CLK SAI1_RXD5 SAI1_RXD6 SAI1_RXD5 11,21

G2

SAI1_RXD6 SAI1_RXD7 SAI1_RXD6 11,21

G1 SAI1_RXD7 11,21

MIMX8MQ6DVAJZAB + MBF25004-15W/2.0P+T725 A1 SAI1_RXD7

H5 SAI2_MCLK

SAI2_MCLK SAI2_MCLK 14

H4 SAI2_TXFS

9,21 NAND_DATA[7:0] SAI2_TXFS SAI2_TXC SAI2_TXFS 14

J5

NVCC_SAI2

SAI2_TXC SAI2_TXD SAI2_TXC 14

G5

SAI2_TXD0 SAI2_TXD 14

J4 SAI2_RXFS

SAI2_RXFS SAI2_RXC SAI2_RXFS 16

H3

SAI2_RXC SAI2_RXD SAI2_RXC 16

C H6 SAI2_RXD 16 C

SAI2_RXD0

U101J

i.MX8M - eNET MIMX8MQ6DVAJZAB + MBF25004-15W/2.0P+T725 A1

N20 ENET_MDC

ENET_MDC ENET_MDIO ENET_MDC 15

N19 ENET_MDIO 15

ENET_MDIO

P19 ENET_TX_CTL

ENET_TX_CTL ENET_TXC ENET_TX_CTL 15

T19 ENET_TXC 15 U101K

ENET_TXC R20 ENET_TD0

ENET_TD0 ENET_TD1 ENET_TD0 15 UART1_RXD ECSPI1_SS0

NVCC_ENET

R21 ENET_TD1 15 20 UART1_RXD C7 D4 UART3_RTS 16,17

ENET_TD1 R19 ENET_TD2 UART1_TXD A7 UART1_RXD ECSPI1_SS0 A4 ECSPI1_MOSI

ENET_TD2 ENET_TD3 ENET_TD2 15 20 UART1_TXD UART1_TXD ECSPI1_MOSI ECSPI1_MISO DSI_TS_nINT 18

P20 B4

ENET_TD3 ENET_TD3 15 UART2_RXD ECSPI1_MISO ECSPI1_SCLK UART3_CTS 16,17

20 UART2_RXD B6 D5 DSI_EN 18

T21 ENET_RX_CTL UART2_TXD D6 UART2_RXD ECSPI1_SCLK

NVCC_UART

ENET_RX_CTL 15 20 UART2_TXD

NVCC_ECSPI

ENET_RX_CTL T20 ENET_RXC UART2_TXD A5 ECSPI2_SS0

ENET_RXC ENET_RD0 ENET_RXC 15 UART3_RXD ECSPI2_SS0 ECSPI2_MOSI PCIE_nPME 16

U19 A6 E5

ENET_RD0 ENET_RD1 ENET_RD0 15 16,17 UART3_RXD UART3_TXD UART3_RXD ECSPI2_MOSI ECSPI2_MISO PCIe_nWAKE 17

U21 B7 B5

ENET_RD1 ENET_RD2 ENET_RD1 15 16,17 UART3_TXD UART3_TXD ECSPI2_MISO ECSPI2_SCLK PCIe_nRST 17

U20 ENET_RD2 15 C5 PCIe_nDIS 17

ENET_RD2 V19 ENET_RD3 UART4_RXD C6 ECSPI2_SCLK

ENET_RD3 ENET_RD3 15 16 WL_nPERST UART4_TXD UART4_RXD GPIO1_IO00

16 WL_REG_ON D7 T6 REF_CLK_32K 16,17

UART4_TXD GPIO1_IO00 T7 GPIO1_IO01

I2C1_SCL GPIO1_IO01 GPIO1_IO02 DSI_BL_PWM 18

E7 R4

10,12,18 I2C1_SCL I2C1_SDA I2C1_SCL GPIO1_IO02 GPIO1_IO03 nWDOG 10

MIMX8MQ6DVAJZAB + MBF25004-15W/2.0P+T725 A1 10,12,18 I2C1_SDA E8 P4 CSI_P1_PWDN 18

I2C1_SDA GPIO1_IO03 P5 GPIO1_IO04

I2C2_SCL GPIO1_IO04 GPIO1_IO05 SD2_VSELECT 19

11,16,17,18 I2C2_SCL G7 P7 CSI_P2_PWDN 18

I2C2_SDA F7 I2C2_SCL GPIO1_IO05 N5 GPIO1_IO06

NVCC_I2C

NVCC_GPIO1

11,16,17,18 I2C2_SDA I2C2_SDA GPIO1_IO06 GPIO1_IO07 CSI_nRST 18

N6

I2C3_SCL GPIO1_IO07 GPIO1_IO08 PMIC_nINT 10

18,21 I2C3_SCL G8 N7 AUD_nMUTE 14

I2C3_SDA E9 I2C3_SCL GPIO1_IO08 M6 GPIO1_IO09

18,21 I2C3_SDA I2C3_SDA GPIO1_IO09 GPIO1_IO10 ENET_nRST 15

M7 ENET_WoL 15

I2C4_SCL F8 GPIO1_IO10 L6 GPIO1_IO11

16 PCIE1_nCLKREQ I2C4_SDA I2C4_SCL GPIO1_IO11 GPIO1_IO12 ENET_nINT 15

F9 L7

17 PCIE2_nCLKREQ I2C4_SDA GPIO1_IO12 GPIO1_IO13 IR_CAP 19

K6 PWM_LED 10,19

GPIO1_IO13 K7 GPIO1_IO14

GPIO1_IO14 GPIO1_IO15 CLKO_25MHz 15

J6 CLKO2 18

B

U101I GPIO1_IO15 B

i.MX8M - SD MIMX8MQ6DVAJZAB + MBF25004-15W/2.0P+T725 A1

SD1_CLK L25 L22 SD2_CLK

9 SD1_CLK SD1_CMD SD1_CLK SD2_CLK SD2_CMD SD2_CLK 17,19

9 SD1_CMD L24 M22 SD2_CMD 17,19

SD1_CMD SD2_CMD

SD1_DATA0 M25 N22 SD2_DATA0

9 SD1_DATA0 SD1_DATA0 SD2_DATA0 SD2_DATA0 17,19

SD1_DATA1 M24 N21 SD2_DATA1

9 SD1_DATA1 SD1_DATA1 SD2_DATA1 SD2_DATA1 17,19

SD1_DATA2 N25 P22 SD2_DATA2

NVCC_SD1

NVCC_SD2

9 SD1_DATA2 SD1_DATA2 SD2_DATA2 SD2_DATA2 17,19

SD1_DATA3 P25 P21 SD2_DATA3 R301 4.7K 5% I2C1_SCL

9

9

SD1_DATA3

SD1_DATA4

SD1_DATA4 N24 SD1_DATA3 SD2_DATA3 SD2_DATA3 17,19 NVCC_I2C_3V3 R302 4.7K 5% I2C1_SDA

SD1_DATA5 P24 SD1_DATA4 M21 SD2_WP

9 SD1_DATA5 SD1_DATA5 SD2_WP SDIO_WAKE 17,18

SD1_DATA6 R25 L21 SD2_nCD R303 4.7K 5% I2C2_SCL

9 SD1_DATA6 SD1_DATA6 SD2_CD_B SD2_nCD 19

SD1_DATA7 T25 R22 SD2_nRST R304 4.7K 5% I2C2_SDA

9 SD1_DATA7 SD1_DATA7 SD2_RESET_B SD2_nRST 17,19

SD1_nRST R24 R305 4.7K 5% I2C3_SCL

9,18 SD1_nRST SD1_STROBE SD1_RESET_B I2C3_SDA

T24 R306 4.7K 5%

9 SD1_STROBE SD1_STROBE

R307 4.7K 5% DNP I2C4_SCL

MIMX8MQ6DVAJZAB + MBF25004-15W/2.0P+T725 A1 R308 4.7K 5% DNP I2C4_SDA

A A

Microcontroller Product Group

6501 William Cannon Drive West

Austin, TX 78735-8598

This document contains information proprietary to NXP and shall not be used for engineering design,

procurement or manufacture in whole or in part without the express written permission of NXP Semiconductors.

ICAP Classification: CP: ___ IUO: _X_ PUBI: ___

Designer: Drawing Title:

<JW>

MCIMX8M-EVKB

Drawn by: Page Title:

<JW> CPU IO

Approved: Size Document Number Rev

<Approver> C SCH-38820 PDF: SPF-38820 A1

Date: Thursday, April 25, 2019 Sheet 6 of 23

5 4 3 2 1

5 4 3 2 1

BOOT_MODE0

7,11,20 BOOT_MODE0 BOOT_MODE1

7,11,20 BOOT_MODE1

ONOFF

7,11,20 ONOFF PMIC_STBY_REQ

JTAG Debug

7,10 PMIC_STBY_REQ PMIC_ON_REQ

7,10 PMIC_ON_REQ

NVCC_JTAG_3V3

A

JTAG_nTRST

D TP402 JTAG_TDI D

D402 TP403

ZLLS400 JTAG_TMS

TP404 JTAG_TCK

TP405 JTAG_TDO

TP406

C

POR_B

TP407

DNP DNP DNP

R402 R403 R404 R405

10K 10K 10K 100

5% 5% 5% 1%

R408

J401 10K

JTAG_TMS TMS 2 1 VCC 5%

JTAG_TCK TCK 4 3 GND

JTAG_TDO TDO 6 5 GND

JTAG_TDI NC/TDI 8 7 R406 0 5% DNP

nRST 10 9 R407 0 5% GND

HDR 2X5 R418 0 5% DNP JTAG_nTRST

GND

D401

A C

7,10,19,20 POR_B

ZLLS400

7,10,19,20 POR_B R401 0 5%

C401

1uF

25 V

C C

NVCC_SNVS_3V3 NVCC_SNVS_3V3

GND

R409 R419

4.7K 100K

5% 1% U101L

i.MX8M - MISC

TP401 PU W21 W6 BOOT_MODE0

7,11,20 ONOFF ONOFF BOOT_MODE0 BOOT_MODE1 BOOT_MODE0 7,11,20

V6

BOOT_MODE1 BOOT_MODE1 7,11,20

PU W20

POR_B V7 TEST_MODE R417 0 5%

TEST_MODE

NVCC_SNVS

NVCC_JTAG

PD V21

7,10 PMIC_STBY_REQ PMIC_STBY_REQ JTAG_TCK

7,10 PMIC_ON_REQ

PU V20 T5 PU

NVCC_SNVS_3V3 PMIC_ON_REQ JTAG_TCK V5 PU JTAG_TMS GND

Y403 JTAG_TMS W5 PU JTAG_TDI

JTAG_TDI U5 PU JTAG_TDO

4 3 RTC_CLK_32K768 TP408 Internal 31.25KHz or External RTC CLK V22 JTAG_TDO U6 PU JTAG_nTRST

VDD OUTPUT TP409 PU W19 RTC JTAG_TRST_B U7 JTAG_MOD R410 10K 5%

1 2 RTC_RESET_B JTAG_MOD

C406 VIO GND R413 100 1% DNP

0.1uF R23 GND

CLK1_P CLK1_P

50V 32.768KHZ T23 input

XTALI_25M CLK1_N CLK1_N

GND U25

XTALO_25M U24 XTALI_25M T22

XTALO_25M CLK2_P CLK2_P 16

U22 CLK2_N 16

output

GND VDDA CLK2_N

XTALI_27M V25 R414 100 1%

R415 1.5K 1% R416 100K 1% XTALO_27M V24 XTALI_27M

NVCC_SNVS_3V3 DNP XTALO_27M

B B

3

U401

R411 1M 1% R412 1M 1% MIMX8MQ6DVAJZAB + MBF25004-15W/2.0P+T725 A1

VCC

DNP DNP

C407 2

0.1uF RESET

GND

50V Y401 Y402

1 4 1 4

UM803RS

1

2 3 2 3

GND 25MHz 27MHz

C402 C403 C404 C405

18PF 18PF 18PF 18PF

GND GND i.MX8M MISC

A A

Microcontroller Product Group

6501 William Cannon Drive West

Austin, TX 78735-8598

This document contains information proprietary to NXP and shall not be used for engineering design,

procurement or manufacture in whole or in part without the express written permission of NXP Semiconductors.

ICAP Classification: CP: ___ IUO: _X_ PUBI: ___

Designer: Drawing Title:

<JW>

MCIMX8M-EVKB

Drawn by: Page Title:

<JW> CPU PERI2

Approved: Size Document Number Rev

<Approver> C SCH-38820 PDF: SPF-38820 A1

Date: Thursday, April 25, 2019 Sheet 7 of 23

5 4 3 2 1

5 4 3 2 1

i.MX8M PHY VDD_PHY_3V3 USB_RESREF: Attach a 200-Ω 1% 100-ppm/C precision resistor-to-ground on the board.

VDD_PHY_3V3 MIPIDSI_REXT: 15K-Ω

VDD_PHY_1V8 PCIE: 200-Ω±1% ± 100 ppm/°C precision resistor to-ground on the board.

VDD_PHY_1V8 HDMI:a 499Ω {±1% tolerance} resistor to-ground on the board

VDD_PHY_0V9

VDD_PHY_0V9

D D

U101E U101C

i.MX8M - CSI i.MX8M - PCIe

A22 CSI_P1_CKN J24 PCIE1_TXM

MIPI_CSI1_CLK_N CSI_P1_CKP CSI_P1_CKN 18 PCIE1_TXN_N PCIE1_TXP PCIE1_TXN 16

B22 J25

MIPI_CSI1_CLK_P CSI_P1_CKP 18 PCIE1_TXN_P PCIE1_TXP 16

CSI_P1_DN0 PCIE1_RXM

PCIE0_VPH

A23 H24

MIPI_CSI1_D0_N CSI_P1_DP0 CSI_P1_DN0 18 PCIE1_RXN_N PCIE1_RXP PCIE1_RXN 16

B23 CSI_P1_DP0 18 H25 PCIE1_RXP 16

MIPI_CSI1_D0_P PCIE1_RXN_P

C22 CSI_P1_DN1 K24 PCIE1_REF_CLKM

CSI_P1_VDDHA

MIPI_CSI1_D1_N CSI_P1_DP1 CSI_P1_DN1 18 PCIE1_REF_PAD_CLK_N PCIE1_REF_CLKP PCIE1_REF_CLKN 16

D22 CSI_P1_DP1 18 K25 PCIE1_REF_CLKP 16

MIPI_CSI1_D1_P PCIE1_REF_PAD_CLK_P

B24 CSI_P1_DN2 G25 R501 200 1%

MIPI_CSI1_D2_N CSI_P1_DP2 CSI_P1_DN2 18 PCIE1_RESREF

C23

MIPI_CSI1_D2_P CSI_P1_DP2 18 PCIE2_TXM

E24

CSI_P1_DN3 PCIE2_TXN_N PCIE2_TXP PCIE2_TXN 17

C21 CSI_P1_DN3 18 E25 PCIE2_TXP 17 GND

MIPI_CSI1_D3_N D21 CSI_P1_DP3 PCIE2_TXN_P

MIPI_CSI1_D3_P CSI_P1_DP3 18 PCIE2_RXM

PCIE1_VPH

D24 PCIE2_RXN 17

PCIE2_RXN_N D25 PCIE2_RXP

PCIE2_RXN_P PCIE2_RXP 17

A19 CSI_P2_CKN F24 PCIE2_REF_CLKM

MIPI_CSI2_CLK_N CSI_P2_CKP CSI_P2_CKN 18 PCIE2_REF_PAD_CLK_N PCIE2_REF_CLKP PCIE2_REF_CLKN 17

B19 F25

MIPI_CSI2_CLK_P CSI_P2_CKP 18 PCIE2_REF_PAD_CLK_P PCIE2_REF_CLKP 17

C20 CSI_P2_DN0 C25 R502 200 1%

MIPI_CSI2_D0_N CSI_P2_DP0 CSI_P2_DN0 18 PCIE2_RESREF

D20

MIPI_CSI2_D0_P CSI_P2_DP0 18

A20 CSI_P2_DN1 GND

CSI_P2_VDDHA

MIPI_CSI2_D1_N CSI_P2_DP1 CSI_P2_DN1 18

B20 CSI_P2_DP1 18 MIMX8MQ6DVAJZAB + MBF25004-15W/2.0P+T725 A1

MIPI_CSI2_D1_P

A21 CSI_P2_DN2

MIPI_CSI2_D2_N CSI_P2_DP2 CSI_P2_DN2 18

B21 CSI_P2_DP2 18

MIPI_CSI2_D2_P

C19 CSI_P2_DN3

MIPI_CSI2_D3_N CSI_P2_DP3 CSI_P2_DN3 18

D19 U101D

MIPI_CSI2_D3_P CSI_P2_DP3 18

C i.MX8M - DSI C

MIMX8MQ6DVAJZAB + MBF25004-15W/2.0P+T725 A1 C16 DSI_CKN

MIPI_DSI_CLK_N DSI_CKP DSI_CKN 18

D16 DSI_CKP 18

MIPI_DSI_CLK_P

A17 DSI_DN0

MIPI_DSI_D0_N DSI_DP0 DSI_DN0 18

B17 DSI_DP0 18

MIPI_DSI_D0_P

DSI_VDDHA

A16 DSI_DN1

MIPI_DSI_D1_N DSI_DP1 DSI_DN1 18

B16

MIPI_DSI_D1_P DSI_DP1 18

A18 DSI_DN2

MIPI_DSI_D2_N DSI_DP2 DSI_DN2 18

U101F B18

MIPI_DSI_D2_P DSI_DP2 18

i.MX8M - HDMI A15 DSI_DN3

DSI_DN3 18

R3 HDMI_DDC_SCL MIPI_DSI_D3_N B15 DSI_DP3

HDMI_DDC_SCL HDMI_DDC_SDA HDMI_DDC_SCL 13 MIPI_DSI_D3_P DSI_DP3 18

P3 HDMI_DDC_SDA 13

HDMI_DDC_SDA C17 R505 15K 1%

W2 HDMI_HPD MIPI_DSI_REXT

HDMI_HPD HDMI_HPD 13

W3 HDMI_CEC GND

HDMI_CEC HDMI_CEC 13

AC coupled differential low swing clock (HCSL levels) MIMX8MQ6DVAJZAB + MBF25004-15W/2.0P+T725 A1

R1 HDMI_REFCLKN

HDMI_REFCLK_N R2 HDMI_REFCLKP

HDMI_REFCLK_P

HDMI_AVDDIO

T2 HDMI_TXN0

HDMI_TX_M_LN_0 HDMI_TXP0 HDMI_TXN0 13

T1 U101B

HDMI_TX_P_LN_0 HDMI_TXP0 13

U1 HDMI_TXN1

HDMI_TXN1 13

i.MX8M - USB

HDMI_TX_M_LN_1 U2 HDMI_TXP1 D14 USB1_VBUS

HDMI_TX_P_LN_1 HDMI_TXP1 13 USB1_VBUS USB1_DN USB1_VBUS 12

B14

USB_P0_VDD33

HDMI_TXN2 USB1_DN USB1_DP USB1_DN 12,20

N1 A14

HDMI_TX_M_LN_2 HDMI_TXP2 HDMI_TXN2 13 USB1_DP USB1_ID USB1_DP 12,20 USB1_ID

N2 HDMI_TXP2 13 C14 USB1_ID TP501

HDMI_TX_P_LN_2 USB1_ID

M2 HDMI_TXN3

HDMI_TX_M_LN_3 HDMI_TXP3 HDMI_CLKN 13 USB1_TXP

M1 HDMI_CLKP 13 A13 USB1_TXP 12

HDMI_TX_P_LN_3 USB1_TX_P B13 USB1_TXN

HDMI_AUXN USB1_TX_N USB1_TXN 12

V2

USB_P0_VPH

B HDMI_AUX_N HDMI_AUXP HDMI_AUXN 13 USB1_RXP B

V1 A12

HDMI_AUX_P HDMI_AUXP 13 USB1_RX_P USB1_RXN USB1_RXP 12

B12

USB1_RX_N USB1_RXN 12

P1 R503 499 1%

HDMI_REXT A11 R504 200 1%

USB1_RESREF

MIMX8MQ6DVAJZAB + MBF25004-15W/2.0P+T725 A1 GND

GND

D9 USB2_VBUS

USB2_VBUS USB2_DN USB2_VBUS 12

B10

USB_P1_VDD33

USB2_DN USB2_DP USB2_DN 12,17

A10 USB2_DP 12,17

USB2_DP C9 USB2_ID USB2_ID

USB2_ID USB2_ID TP502

VDD_3V3 VDD_3V3

A9 USB2_TXP

USB2_TX_P USB2_TXN USB2_TXP 12

B9 USB2_TXN 12

USB2_TX_N

USB_P1_VPH

A8 USB2_RXP

USB2_RX_P USB2_RXN USB2_RXP 12

C501 B8

USB2_RX_N USB2_RXN 12

0.1uF

R509 R508 10V B11 R506 200 1%

100K 100K USB2_RESREF

1% 1%

Y501 GND GND

MIMX8MQ6DVAJZAB + MBF25004-15W/2.0P+T725 A1

1 6

OE HCSL VCC

2 4 R510 0 5% HDMI_REFCLKP

NC Q

3 5 R511 0 5% HDMI_REFCLKN

GND Q

27MHz R512 R513

49.9 49.9

AC coupled differential low swing clock (HCSL levels) 1% 1%

A DNP DNP A

DIODES: NX5427001Z 5032 3.3V

Microcontroller Product Group

6501 William Cannon Drive West

Austin, TX 78735-8598

This document contains information proprietary to NXP and shall not be used for engineering design,

procurement or manufacture in whole or in part without the express written permission of NXP Semiconductors.

GND

ICAP Classification: CP: ___ IUO: _X_ PUBI: ___

Designer: Drawing Title:

GND <JW>

MCIMX8M-EVKB

Drawn by: Page Title:

<JW> CPU PHY

Approved: Size Document Number Rev

<Approver> C SCH-38820 PDF: SPF-38820 A1

Date: Thursday, April 25, 2019 Sheet 8 of 23

5 4 3 2 1

5 4 3 2 1

D

eMMC 5.0 Footprint D

VDD_3V3

# eMMC/TF co-Layout

NVCC_SD1_1V8

C601

4.7uF

6.3V

C602

0.1uF

50V

C603

0.1uF

50V

MTFC16GAKAECN-2M WT

MT53B1024M32D4NQ-062

MT25QL256ABA1EW9-0SIT Hinge Type MicroSD

# eMMC/TF co-Layout

R601 R602 R603 GND # Stitching CAP for Layout J601 DNP

4.7K 4.7K 4.7K # Hinge TYPE

J10

5% 5% 5%

E6

K9

F5

Via/TP U601A NVCC_SD1_1V8 P1

DAT2 SD1_DATA2 6,9

C606 C604 C607 C605 P2 SD1_DATA3 6,9

VCC1

VCC2

VCC3

VCC4

0.1uF 0.1uF 0.1uF 4.7uF CD/DAT3 P3

CMD SD1_CMD 6,9

A3 C6 50V 50V 50V 6.3V P4

6,9 SD1_DATA0

A4 DAT0 VCCQ1 M4 VDD P5 eMMC_CLK VDD_3V3

6,9 SD1_DATA1 DAT1 VCCQ2 CLK

A5 N4 P6 C617 C618

6,9 SD1_DATA2 DAT2 VCCQ3 VSS

B2 eMMC P3 P7 0.1uF 22uF

6,9 SD1_DATA3 DAT3 VCCQ4 DAT0 SD1_DATA0 6,9

B3 16GB P5 GND P8 50V 6.3V

6 SD1_DATA4 DAT4 VCCQ5 DAT1 SD1_DATA1 6,9

B4

S4

S3

S2

S1

6 SD1_DATA5 DAT5 eMMC_VDDIM

6 SD1_DATA6 B5 SDINBDG4-16G-I C2

B6 DAT6 VDDI CAH11-08163-S107

6 SD1_DATA7 DAT7

S4

S3

S2

S1

C4 C610 C611 GND

eMMC_CMD M5 VSSQ1 N2 0.1uF 1uF

6,9 SD1_CMD CMD VSSQ2 N5 50V 25 V

R616 0 5% eMMC_CLK M6 VSSQ3 P4

6 SD1_CLK CLK VSSQ4 P6

R621 0 5% DNP eMMC_nRST K5 VSSQ5

6,18 SD1_nRST RST eMMC_DQS

H5 GND R617 0 5% GND

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

RCLK SD1_STROBE 6

C C

H10

A6

E7

G5

J5

K8

GND

P10

P11

P12

P13

P14

E10

K10

F10

P1

P2

P7

P8

P9

E9

NC_P1

NC_P2

NC_P7

NC_P8

NC_P9

NC_P10

NC_P11

NC_P12

NC_P13

NC_P14

VSF1

VSF2

VSF3

VSF4

A1

A2 NC_A1 N14

A7 NC_A2 NC_N14 N13

A8 NC_A7 NC_N13 N12

A9 NC_A8 NC_N12 N11

A10 NC_A9 NC_N11 N10 NVCC_NAND_3V3

A11 NC_A10 NC_N10 N9

QSPI-A

A12 NC_A11 NC_N9 N8

A13 NC_A12 NC_N8 N7 VDD_3V3

A14 NC_A13 NC_N7 N6 C613 C614

B1 NC_A14 NC_N6 N3 0.1uF 4.7uF

B7 NC_B1 NC_N3 N1 50V 6.3V

B8 NC_B7 NC_N1 M14 R620

B9 NC_B8 NC_M14 M13 10K

B10 NC_B9 NC_M13 M12 5%

B11 NC_B10 NC_M12 M11 GND

NC_B11 NC_M11

8

B12 M10 U603

B13 NC_B12 NC_M10 M9 5 2

U601B 6 QSPIA_DATA0 TP602 QSPIA_DATA1 6

VCC

B14 NC_B13 NC_M9 M8 DQ0 DQ1

B

C1 NC_B14 NC_M8 M7 6 B

C3

C5

NC_C1

NC_C3

SDINBDG4-16G-I NC_M7

NC_M3

M3

M2

6 QSPIA_SCLK TP603

1

C

NC_C5 NC_M2 6 QSPIA_nSS0 S

C7 M1

C8 NC_C7 NC_M1 L14 3

NC_C8 NC_L14 6 QSPIA_DATA2 W/DQ2

C9 L13

C10 NC_C9 NC_L13 L12 7

NC_C10 NC_L12 6 QSPIA_DATA3 HOLD/DQ3

C11 L3

NC_C11 NC_L3

VSS

C12 L2

EP

C13 NC_C12 NC_L2 L1

C14 NC_C13 NC_L1 K14 MT25QL256ABA1EW9

NC_C14 NC_K14

9

4

D1 K13

D2 NC_D1 NC_K13 K12

D3 NC_D2 NC_K12 K7

D4 NC_D3 NC_K7 K6 GND

D12 NC_D4 NC_K6 K3

D13 NC_D12 NC_K3 K2

D14 NC_D13 NC_K2 K1

NC_D14 NC_K1

NC_G10

NC_G12

NC_G13

NC_G14

NC_H12

NC_H13

NC_H14

NC_E12

NC_E13

NC_E14

NC_F12

NC_F13

NC_F14

NC_J12

NC_J13

NC_J14

NC_G1

NC_G2

NC_G3

NC_H1

NC_H2

NC_H3

NC_E1

NC_E2

NC_E3

NC_E5

NC_E8

NC_F1

NC_F2

NC_F3

NC_J1

NC_J2

NC_J3

E1

E2

E3

E5

E8

H12

H13

H14

J1

J2

J3

E12

E13

E14

F1

F2

F3

G1

G2

G3

F12

F13

F14

G10

G12

G13

G14

H1

H2

H3

J12

J13

J14

A A

Microcontroller Product Group

6501 William Cannon Drive West

Austin, TX 78735-8598

This document contains information proprietary to NXP and shall not be used for engineering design,

procurement or manufacture in whole or in part without the express written permission of NXP Semiconductors.

ICAP Classification: CP: ___ IUO: _X_ PUBI: ___

Designer: Drawing Title:

<JW>

MCIMX8M-EVKB

Drawn by: Page Title:

<JW> Flash

Approved: Size Document Number Rev

<Approver> C SCH-38820 PDF: SPF-38820 A1

Date: Thursday, April 25, 2019 Sheet 9 of 23

5 4 3 2 1

5 4 3 2 1

SYS PMIC/PWR Main PWR (5-20V-->3.3V)

R755 0

NVCC_SNVS_3V3

DCDC 5V

R704 3.3 1%

C705 Q701 DCDC_3V3 R743 0 C787

0.22uF IRLML6401 1uF

10

8

1

U701

5 # 3.38V/8A 2 3 2

U706

9 1

L709

2

VSYS VDD_3V3 VSYS DCDC_5V

BST

BST

VIN VOUT VIN SW 4.7uH

C701 C702 C703 C704 4 7 L701 1.5uH C779 + C706 C707 C708 C709 C713 R712 C799 C781 C771 C772 C773 C774 R748 C790 C791 C792

22uF 22uF 22uF 0.1uF R708 NC SW 220uF 0.1uF 22uF 22uF 22uF 22uF 44.2K 1uF 0.022UF 10uF 10uF 0.1uF VCC_5V 11 10.0 22uF 22uF 0.1uF

VCC

1

35V 50V 1.5M R703 DNP C712 DNP R702 10V 50V 10V 10V 10V 10V 1% 25 V 35V 35V 50V MP2263GD 1% 10V 10V 50V

44.2K 1uF 25 V R732 10.0K 6 C789 5.6PF

MP8759GD 1% PG 25V

12 499K 300PF 100V GND 14 R744 0 R745 1M

GND VCC_3V6 9 EN R705 499 DNP GND R761 GND R731 0 4 FB 1% GND

VCC 10K VDD_3V3 EN 1 1.55M PD TP704

PGND1

PGND2

SW701 MODE

C

PG_SEQ0

PGND

AGND

AGND

3 11 600mv 5% 15 7 R749 0 DCDC_5V

D

B 3 C798 D706 R706 100K 6 PG FB 13 FREQ BIAS 5 D

0.1uF BZX585-B2V4 MODE SS NC

3

2 50V DNP R709 DNP

3

8

10

12

C711 R707 9.53K Q702 R747 C793 C788 R746

A

1 1uF 100K 1% 2SK3018 27K 0.012uF 1uF 191K

A 25 V DNP R715 10K 2 1% 25 V 1% Mode selection. Pull MODE low or float

VDDA_1V8 5% MODE to set auto PFM/PWM mode; pull

SW SPDT C727 MODE to VCC to set forced PWM mode.

0.1uF MODE is pulled down internally.

GND GND GND GND GND 50V DNP GND GND GND GND GND

1

SYS PWR SW

GND

U707 VDD_ARM_0V9

U703 L706 Change to support ARM OD mode: 0.9/1.0V!!! SH709

1 5 8 1 1 2

DCDC_3V3 IN OUT VDD_SNVS_0V9 DCDC_3V3 11 VIN1 SW1 9 0.47uH

NVCC_SNVS_3V3 C715 C716 3 R758 6.98K C717 C718 C775 C776 VIN2 SW2 R710 C714 R764 C725 C778 C769

D701 1uF 0.1uF EN 4 R759 56K 1uF 0.1uF 22uF 0.1uF 2 240K 1000pF 715K 22uF 22uF 0.1uF

ZLLS400 25 V 50V 2 ADJ 25 V 50V 10V 50V OUT 1% 50V 1% 10V 10V 50V

R713 100 1% C A R760 GND Vfb=0.8V MP2147GD

20 SYS_nRST

C720 100K LDCL015MR 1 3

# Reset Button C721 0.1uF GND GND

1000pF 50V GND GND PMIC_ON R714 10K 5% GND 5 3 FB=0.6V Q704 GND

50V PWR_MODE 6 EN FB 4 RYU002N05

MODE/VCON RAMP

4

U704 PG_SEQ0 R762 0

GND 7 10

TP701

VCC

PG GND

2

# GPIO/WDOG PWR OFF->ON GND D702 PWM_LED 6,19

ZLLS400 2

C726 1uF 25 V C A nRST 3 RESET GND PWM_LED: H: 0.9V; L:1.0V

6 nWDOG MR R711 R763 C780

GND

360K 100K 1000pF

R717 1% DNP 50V

1M UM805RE

1

1%

C U705 L710 SH708 C

DCDC_3V3 GND 8 1 1 2

DCDC_3V3 11 VIN1 SW1 9 0.47uH VDD_SOC_0V9 GND

GND C710 C719 VIN2 SW2 C722 C723 C724

nRST R716 0 5% 22uF 0.1uF 2 R752 22uF 22uF 0.1uF NVCC_SNVS_3V3

DNP 25V 50V OUT 180K 10V 10V 50V

R701 MP2147GD 1%

10K R718 10K 5% PMIC_ON_REQ 7,10

5% DNP

R754 10K 5% GND 5 3 FB=0.6V GND C777

7,10 PMIC_ON_REQ PWR_MODE EN FB

6 4 1uF DNP

MODE/VCON RAMP R723 25 V

3

7 10 100K

PG GND

R753 U702A GND

7,10 PMIC_STBY_REQ 2 360K

GND 1% 55 56 PMIC_ON

Q703 D703 NVCC_3V3 VDDIO PWRON

2SK3018 ZLLS400 3

PMIC_ON PMIC_VCOREDIG51 RESETMCU POR_B 7,19,20

C A C728 1uF 25 V

GND VCOREDIG

1

GND 4 R724 0 5% PMIC_STBY_REQ 7,10

STANDBY

GND C730 0.22uF 50V PMIC_VCOREREF52 2

VCOREREF SDWN

DCDC_3V3 Control 1

PMIC_nINT 6

C735 1uF 25 V PMIC_VCORE 49 INT

VCORE

U702C RSV for Curr Measure

DCDC PMIC_VDDOTP 47

L702 1uH SH701 R720 10.0K 1%

C729 4.7uF 10V 7 8 1 2 VDDOTP

SW1AIN SW1ALX 6 VDD_GPU_0V9 53 R719 0 5%

SW1FB SDA I2C1_SDA 6,12,18

C731 C732 C733 C734 48 54 R721 0 5%

GNDREF SCL I2C1_SCL 6,12,18

SW1A/B 22uF 22uF 22uF 22uF 15

10V 10V 10V 10V 57 GNDREF1 5 R722 0 5%

GND EPGND ICTEST

GND

C736 4.7uF 10V 10 9

SW1BIN SW1BLX MC34PF4210A1ES GND

L703 1uH SH702

B B

C737 4.7uF 10V 12 11 1 2

SW1CIN

SW1C

SW1CLX 13 VDD_VPU_0V9

SW1CFB C738 C739 C794

14 22uF 22uF 22UF

SW1VSSSNS 10V 10V DCDC_3V3

L704 1uH GND SH703 U702B

C740 4.7uF 10V 23 22 1 2 LDO

24 SW2IN_1

SW2

SW2LX 25 NVCC_DRAM_1V1 16 R725 0 5%

SW2IN_2 SW2FB C741 C742 C795 C746 0.47uF 17 VGEN1 C747 4.7uF 10V VCAM_1V5

GND VIN1

22uF 22uF 22UF 18

10V 10V VGEN2 C749 4.7uF 10V VDD_PHY_0V9

L705 1uH SH704 26

C743 4.7uF 10V 37 36 1 2

GND

C750 0.47uF 27 VGEN3 C751 4.7uF 10V VDD_PHY_1V8

SW3AIN SW3ALX 38 VDD_DRAM_0V9 VIN2 28

SW3AFB C744 C745 C752 C753 R756 0 5% VGEN4 C754 4.7uF 10V VDDA_1V8

SW3A/B 22uF 22uF 22uF 22uF VDD_DRAM Change to 1.0V to DCDC_3V3 39

10V 10V 10V 10V support 1.6GHz by default!!! D705 D704 C756 0.47uF 40 VGEN5 C757 4.7uF 10V VDD_PHY_3V3

1N4148WS 1N4148WS VIN3 41

C748 4.7uF 10V 34 35

GND

A C A C VGEN6 C759 4.7uF 10V VCAM_2V8

SW3BIN SW3BLX 33 DCDC_5V C762 1uF 25 V 50

SW3BFB VIN 43 R757 56 DNP

DNP

32 C763 0.1uF 50V 42 VSNVS C764 0.47uF VDD_SNVS_0V9

SW3VSSSNS LICELL

L707 1uH SH706 30 31

C755 4.7uF 10V 20 21 1 2 NVCC_DRAM_1V1 C767 0.1uF 50V VINREFDDR VREFDDR C768 1uF 25 V VREFDDR

SW4IN

SW4

SW4LX 19 VDD_1V8 29

C758 0.1uF 50V SW4FB C760 C761 C797 NVCC_1V8 VHALF

22uF 22uF 22UF NVCC_SD1_1V8 C770 0.1uF 50V

10V 10V MC34PF4210A1ES

GND GND

45 46

C765 10uF 25V

SWBSTIN SWBSTLX 44 i.MX8M PWR GND

C766 0.1uF 50V SWBSTFB

SWBST SEQ PWR MIN TYP MAX Curr(mA)

1 NVCC_SNVS 3 3.3 3.6 2

MC34PF4210A1ES 2 VDD_SNVS 0.81 0.9 0.99 2

A GND RTC_RESET_B A

3 VDD_SOC/VDDA_0P9 0.81 0.9 0.99 3600 Microcontroller Product Group

4 VDD_GPU 0.81 0.9/1.0 1.1 2000 6501 William Cannon Drive West

4 VDD_VPU 0.81 0.9/1.0 1.1 1000 Austin, TX 78735-8598

4 VDD_DRAM 0.81 1.0 1.05 2500 This document contains information proprietary to NXP and shall not be used for engineering design,

4 VDD_ARM 0.81 0.9/1.0 1.1 4000 procurement or manufacture in whole or in part without the express written permission of NXP Semiconductors.

5 VDDA_1P8_xxx 1.62 1.8 1.89 250

5 VDDA_DRAM 1.71 1.8 1.89 50 ICAP Classification: CP: ___ IUO: _X_ PUBI: ___

6 NVCC_DRAM 1.1/1.2/1.35 2170 Designer: Drawing Title:

6 NVCC_3V3 3 3.3 3.6 100 <JW>

6 NVCC_1V8 1.65 1.8 1.95 450 MCIMX8M-EVKB

Drawn by: Page Title:

7 3.3V PHY 3.069 3.3 3.63 100 <JW> PMIC

7 1.8V PHY 1.674 1.8 1.98 50

Approved: Size Document Number Rev

7 0.9V PHY 0.837 0.9 0.99 250 <Approver> C SCH-38820 PDF: SPF-38820 A1

POR_B

Date: Thursday, April 25, 2019 Sheet 10 of 23

5 4 3 2 1

5 4 3 2 1

Boot ROM Fuse <Default: eMMC BOOT>, QSPI boot is not supported by ROM

Address 7 6 5 4 3 2 1 0

0x470[15:8] BOOT_CFG[15] BOOT_CFG[14] BOOT_CFG[13] BOOT_CFG[12] BOOT_CFG[11] BOOT_CFG[10] BOOT_CFG[9] BOOT_CFG[8]

0x470[15:8] 001 - SD/eSD Port Select: Power Cycle Enable SD Loopback Clock

00 - eSDHC1 '0' - No power cycle Source Sel (for SDR50 BMODE[1:0] BOOT TYPE

01 - eSDHC2 '1' - Enabled via and SDR104 only)

0x470[15:8] 010 - MMC/eMMC '0' - through SD pad 00 Boot From Fuses

D

'1' - direct D

01 Serial Downloader

Pages In Block: Nand_Row_address_bytes: 10 Internal Boot (Development)

00 - 128 00 - 3

0x470[15:8] Infinit-Loop 011 - NAND 01 - 64 01 - 2 11 Reserved

(Debug USE only) 10 - 32 10 - 4

0 - Disable 11 - 256 11 - 5

1 - Enable # Boot Device: eMMC/MicroSD

QSPI Instance SDR SMP: NVCC_SAI1_3V3

0x470[15:8] 100 - QSPI 0 - QuadSPI0 "000" : Default

1 - Reserved "001-111" -Internal pullup resistors only support 1 PU res of 27 kOhm;

-Internal pulldown resistor of 90kOhm is always enabled

Port Select: SPI Addressing:

0x470[15:8] 110 - SPI NOR 000 - eCSPI1 0 - 3-bytes (24-bit)

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

001 - eCSPI2 1 - 2-bytes (16-bit)

10K

10K

10K

10K

10K

10K

10K

10K

10K

10K

10K

10K

0x470[15:8] Others - Reserved for future use

1K

1K

1K

1K

BOOT_CFG[7] BOOT_CFG[6] BOOT_CFG[5] BOOT_CFG[4] BOOT_CFG[3] BOOT_CFG[2] BOOT_CFG[1] BOOT_CFG[0]

R801

R802

R803

R804

R805

R806

R807

R808

R809

R810

R811

R812

R813

R814

R815

R816

0x470[7:0] Reserved Reserved Bus Width: Speed Reserved

0 - 1-bit 000 - Normal/SDR12

1 - 4-bit 001 - High/SDR25

SD/eSD 010 - SDR50

DNP

DNP

DNP

DNP

011 - SDR104

101 - Reserved for DDR50

8

7

6

5

Fast Boot: Others - Reserved

0

0

0

0

SW801

C

0 - Regular DHN-04F-T-V-T/R

C

1 - Fast Boot

0x470[7:0] Bus Width: Speed USDHC1 IO VOLTAGE USDHC2 IO VOLTAGE

000 - 1-bit 00 - Normal SELECTION SELECTION

R820

R821

R819

R822

001 - 4-bit 01 - High 0 - 3.3V 0 - 3.3V

1

2

3

4

MMC/eMMC 010 - 8-bit 10 - Reserved for HS200 1 - 1.8V 1 - 1.8V

101 - 4-bit DDR (MMC 4.4) 11 - Reserved

110 - 8-bit DDR (MMC 4.4)

Else - reserved.

R825 1K BT_CFG0

BT_CFG1 SAI1_RXD0 6,21

BOOT_SEARCH_COUNT: Toggle Mode 33MHz Preamble Delay, Read Latency: Reserved R826 1K DNP

BT_CFG2 SAI1_RXD1 6,21

0x470[7:0] 00 - 2 '000' - 16 GPMICLK cycles. R827

R828

1K

1K BT_CFG3 SAI1_RXD2 6,21

01 - 2 '001' - 1 GPMICLK cycles. R829 1K BT_CFG4 SAI1_RXD3 6,21

10 - 4 '010' - 2 GPMICLK cycles. BT_CFG5 SAI1_RXD4 6,21

R830 1K SAI1_RXD5 6,21

NAND BT_TOGGLEMODE 11 - 8 '011' - 3 GPMICLK cycles. R831 1K BT_CFG6

SAI1_RXD6 6,21

'100' - 4 GPMICLK cycles. R832 1K BT_CFG7

SAI1_RXD7 6,21

'101' - 5 GPMICLK cycles.

'110' - 6 GPMICLK cycles. R833 1K BT_CFG8

'111' - 7 GPMICLK cycles. R834 1K BT_CFG9 SAI1_TXD0 6,21

'1111'- 15 GPMICLK cycles. BT_CFG10 SAI1_TXD1 6,21

R835 4.7K SAI1_TXD2 6,21

R836 1K BT_CFG11

BT_CFG12 SAI1_TXD3 6,21

R837 4.7K SAI1_TXD4 6,21

BT_CFG13

0x470[7:0] HSPHS: Half Speed HSDLY: Half Speed FSPHS: Full Speed FSDLY: Full Speed Reserved Reserved Reserved Reserved R838 4.7K

BT_CFG14 SAI1_TXD5 6,21

R839 4.7K

Phase Selection Delay selection Phase Selection Delay selection R840 1K BT_CFG15 SAI1_TXD6 6,21

0 : select sampling 0 : one clock delay 0 : select sampling 0 : one clock delay SAI1_TXD7 6,21

QSPI at non-inverted 1: two clock delay at non-inverted 1: two clock delay

clock clock

1: select sampling 1: select sampling # For TO A0, keep R825~R840 installation

at inverted clock at inverted clock # For TO B0, R825~R840 can be DNP due to the internal PD

GND

B 0x470[7:0] CS select (SPI only): Reserved Reserved Reserved Reserved Reserved Reserved B

00 - CS#0 (default)

SPINOR 01 - CS#1

10 - CS#2 NVCC_SNVS_3V3

11 - CS#3

NVCC_JTAG_3V3

item Power state ONOFF RST OE DIP SW BM1 BM0 Note Description C801

0.1uF GND

1 During Power Up H (No press) L H 1-4 : OFF; 2-3 : ON 0 1 Serial Downloader item 1/2 for system development 50V

2 During Power Up H (No press) L H 1-4 : ON; 2-3 : OFF 1 0 Internal Boot item 2/3 for system upgrade R845 DNP R823

8

3 During Power Up L (Press) L L 1-4 : ON; 2-3 : OFF 0 1 Serial Downloader U802 100K 10K

4 After Power Up H (No press) H H / / / No power key event Normal power key function GND 5% 5%

VCC

5 After Power Up L (Short Press) H H / / / Power key event

6 After Power Up L (Long Press) H H / / / System power down

R817 0 5% DNP

2 1A 1Y 6

D801 BOOT_MODE1 7,20

DCDC_5V ZLLS400

1OE

SW802

A C GND 1 1 ON 4 DHN-02F-T-V

1

7,20 ONOFF

2 3

2

D802

VDD_3V3 ZLLS400 R842 5 2A 2Y 3

A C 1M NVCC_JTAG_3V3 R818 0 5% DNP BOOT_MODE0 7,20

R843 1%

10 7 2OE

FAN PWR R846 DNP R824

GND

GND NVCC_SNVS_3V3 100K 10K

J801 5% 5%

6,16,17,18 I2C2_SCL

1 2 J802 GND 74LVC2G125 NVCC_JTAG_3V3

4

6,16,17,18 I2C2_SDA 3 4 1

5 6 2 1

7 8 3 2 C802 GND

IPOD_nRST 6 3

9 10 0.1uF

HDR 1X3 50V R847 GND

3

A C804 CON 2X5 R844 U801 10K A

0.1uF 10K Part Number: MOLEX 0022272031 5% t>POR_B to latch BOOT_MODE Microcontroller Product Group

VCC

50V 5% GND

2 R841 10K 5% 6501 William Cannon Drive West

RESET Austin, TX 78735-8598

GND

C803 This document contains information proprietary to NXP and shall not be used for engineering design,

0.1uF procurement or manufacture in whole or in part without the express written permission of NXP Semiconductors.

GND GND GND UM803RS 50V

1

ICAP Classification: CP: ___ IUO: _X_ PUBI: ___

Designer: Drawing Title:

<JW>

GND GND MCIMX8M-EVKB

Drawn by: Page Title:

<JW> BOOT_CFG

Approved: Size Document Number Rev

<Approver> C SCH-38820 PDF: SPF-38820 A1

Date: Thursday, April 25, 2019 Sheet 11 of 23

5 4 3 2 1

5 4 3 2 1

DCDC_5V DCDC_5V USB_VBUS

8,20 USB1_DP

USB3.0/2.0 TYPE-C/HOST

8,20 USB1_DN

C

C903 C904 C926 D908

10uF 0.1uF 0.01UF

VDD_1V8 R934 R902 R903 35V 50V 50V PTVS24VS1UR

C901 C902 1K 1.2M 1M

4.7uF 0.1uF U909 1% 1%

A

5

10V 50V SGM8709YN5G

4

GND

V+

- 0.86V USB TYPE-C

8 USB1_VBUS 1 GND

GND J901

3 4.3V-20V

D

U902 V- + A4 D

B3

B2

B1

U901 PCMF3USB3S A9 VBUS1

active switch/redriver

VBUS2

2

C6 A6 USB_DP R939 TLV3201AIDBVR R933 R904 B9

5 C5

B1,B2,B3

A5 USB_DN 19.6K 249K 249K B4 VBUS3

19 VDD1V8 1% 1% VBUS4

GND

CMF+ESD

6 C907 0.1uF 50V C4 A4 SSTXP1 DNP A6

TX_CON_1+ 7 C905 0.1uF 50V C3 A3 SSTXN1 A7 DP1

C917 0.1uF 50V GND 15 TX_CON_1- C2,4,6 A2,4,6 DN1

8 USB1_TXP TX_AP_+ USB_DP

C918 0.1uF 50V 14 12 C906 0.1uF 50V C2 A2 SSTXP2 B6

8 USB1_TXN TX_AP_- TX_CON_2+ USB_DN DP2

11 C908 0.1uF 50V C1 A1 SSTXN2 GND GND B7

TX_CON_2- C1,3,5 A1,3,5 DN2

SSTXP1 A2

USB TYPE-C

SSTXN1 A3 SSTXP1

2 C1 A1 SSRXP1 SSTXN1

C919 0.1uF 50V 18 RX_CON_1+ 3 C2 A2 SSRXN1 SSRXP1 B11

8 USB1_RXP RX_AP_+ RX_CON_1- SSRXP1

C920 0.1uF 50V 17 SSRXN1 B10

8 USB1_RXN RX_AP_- SSRXN1

9 C3 A3 SSRXP2

D901 RX_CON_2+ 8 C4 A4 SSRXN2 SSTXP2 B2

RX_CON_2- B3 SSTXP2

ZLLS400 CMF+ESD SSTXN2

SSTXN2

6 USB1_SS_SEL C A 16

R901 4.7K SEL SSRXP2 A11

R905 4.7K DNP 1 SSRXN2 A10 SSRXP2

VDD_1V8 R906 4.7K DNP 4 CH1_SET1/RXDE U903 SSRXN2

CH1_SET2/TXEQ

B2

B1

R907 4.7K DNP 13 PCMF2USB3S CC1 A5

R908 4.7K DNP 10 CH2_SET1/TXDE CC2 B5 CC1

CH2_SET2/RXEQ CC2

PTN36043ABX

4.7K DNP

4.7K DNP

4.7K DNP

4.7K DNP

SBU1 A8

GND SBU2 B8 SBU1

SBU2

TVS902 ESD5B5.0ST1G

TVS903 ESD5B5.0ST1G

TVS904 ESD5B5.0ST1G

TVS905 ESD5B5.0ST1G

A1 SH1

GND1 SH1

2

A12 SH2

D907 B12 GND2 SH2 SH3

B330A B1 GND3 SH3 SH4

R909

R910

R911

R912

A C GND4 SH4

Q910

AON7405 Q901 AON7405 23K20101#LCP-582RF

# 12V

DNP1

DNP1

F901

1 2 3 5 GND 5 3 VBUS / DCDC Path VSYS_IN R928 0 5%

C

DC_IN 2 D902 R947 2 R929 0 5% VSYS C

7A 1 A C 3.3K 1 R913 C935 C923 C924 C925 C929 C931

DC_IN

5

R948 C936 44.2K 0.022uF 22uF 22uF 0.1uF 100UF 100UF

2

1M C937 0.022uF A C 1% 50V Q908 50V 16V 16V

USB_VBUS C

4

4

1% 0.47UF 50V 1 R942 10.0K 1% PWR_PATH_EN AON7405 GND

50V D903 D910 C933 R944 4 C930 C932

R935 BZX585-B3V3 1000pF 44.2K Q902 100UF 100UF

J902 91K 1% BSS84LT1 R943 GND 16V 16V

1 44.2K

1

2

3

A

3 R949 1%

2 220K R918

R916 R919 10.0K GND

C

PJ1-021 D909 R946 GND 10K 1%

44.2K 5% 1K 5% DCDC_5V

6

3

PTVS24VS1UR 1% U910 U905 L901

1

2

3

- + GND

4

Vs+ SGM8710YN6G/TR

R914 Q903 B1

NX5P3090UK

C2

120OHM

1 2

- VINT1 VBUS1

A

1 OD GND EN_SNK 2 2SK3018 4 DNP B2 D1

ESD5B5.0ST1G

VINT2 VBUS2

2

DC IN: 12V/5A VREF_1V2 3 C909 C910 R932 D904 C1 D2

DC IN>4.9V, Power Path Change R936

+ 10K 5% AON7405 47uF 0.1uF 10K ZLLS400 VINT3 VBUS3 C911 C912

44.2K Vs- Vref Q909 50V 5% A C A2 A3 4.7uF 0.1uF

TVS907

1% FAULT ILIM 10V 50V

2

5

VREF_1V2 A1

GND1

GND2

GND3

GND C934 EN R937

1

4700pF GND

50V

2.1A 24.3K

1%

B3

C3

D3

F902 GND GND GND

1 2 GND

USB_VBUS D905 PMEG6030ELP R917 10K 5%

7A C A VDD_3V3 GND

U906 GND

C1

B2

B1

NX5P3290 USB_HOST_VBUS

USB 3.0 HOST

VCP3

VCP2

VCP1

C2 A1

D2 VBUS3 VIN1 A2 DCDC_5V Receptacle, Upright 90°, Type A S1

J903

S3

B

D1 VBUS2 VIN2 C927 C928 G1 G3 9 B

VBUS1 A4 47uF 0.1uF 1 SSTX+

FLT C4 1M OHM PD FRS_EN 50V VBUS 8

9

FO SSTX-

1

A3 2

GND1

GND2

GND3

OD ILIM

8

ILIM D-

CAP

7

EN

2

VDD_3V3 GND_DRAIN

7

GND 3

3

R924 GND D+ 6

6

SSRX+

B3

1M OHM PD B4

D4

C3

D3

4

R931 10K 5% 23.2K 4

5

C913 DNP 1% DCDC_5V GND 5 GND

1000pF S2 SSRX- S4

50V 3 2 EN_SRC Q905 R920 G2 G4

3

2SK3018 Curr Ltd: 1A/3.3A 10K USB_TYPE_A

Q906 R930 R925 5%

GND IRLML6401 100K 53.6K R921 R938 GND

1

1% 1% 2 ILIM_5V_VBUS USB_LD_nFLT 1K 19.6K GND

1%

3

DNP

8 USB2_VBUS

Only DC_IN valid will enable DCDC_5V Q907

1

output to USB TYPE-C VBUS 2 2SK3018

U908

GND GND PCMF3USB3S

R926 0 5% C1 C1,3,5 A1,3,5 A1 USB_HOST_DN

8,17 USB2_DN USB_HOST_DP

R927 0 5% C2 A2

8,17 USB2_DP

1

16

2

U907 GND C3 C2,4,6 A2,4,6 A3 USB_HOST_RXN

8 USB2_RXN USB_HOST_RXP

C4 A4

8 USB2_RXP

EN_SNK1

EN_SRC

15 CMF+ESD

VBUS VBUS LDO USB_HOST_TXN

C921 0.1uF 50V C5 A5

8 USB2_TXN USB_HOST_TXP

INTERNAL LDO

8 USB2_TXP C922 0.1uF 50V C6 B1,B2,B3 A6

C914 2.2uF 4

10V BYPASS 11 OD USB_LD_nFLT

FAULT_N

B3

B2

B1

3 1 FRS_EN

VDD_3V3 VDD VBAT LDO FRS_EN DEBUG_ACCESS

BYPASS RAIL

9

C915 4.7uF DBG_ACC

10V GND

A A

CC1 13 6 ILIM_5V_VBUS default "L"

CC2 14 CC1 ILIM_5V_VBUS 5

Microcontroller Product Group

CC2 SLV_ADDR 6501 William Cannon Drive West

Austin, TX 78735-8598

10 OD GND TP901 TCPC_nINT 6 This document contains information proprietary to NXP and shall not be used for engineering design,

12 ALERT_N procurement or manufacture in whole or in part without the express written permission of NXP Semiconductors.

DCDC_5V VCONN_IN

BAT

C916 0.1uF 8 R940 0 5% ICAP Classification: CP: ___ IUO: _X_ PUBI: ___

I2C_SCL I2C1_SCL 6,10,18

50V 17 7 R941 0 5% Designer: Drawing Title:

GND I2C_SDA I2C1_SDA 6,10,18

<JW>

MCIMX8M-EVKB

GND PTN5110NHQZ Drawn by: Page Title:

default "UFP" mode <JW> USB

Approved: Size Document Number Rev

<Approver> C SCH-38820 PDF: SPF-38820 A1

Date: Thursday, April 25, 2019 Sheet 12 of 23

5 4 3 2 1

5 4 3 2 1

HDMI 2.0a TX

D D

HDMI data EMI/ESD

U1001

PCMF3HDMI2S

HDMI_AUXP C1011 1uF 25 V HDMI_AUXP_C C1 A1 HDMI_Utility/HEAC+_CN

8 HDMI_AUXP HDMI_AUXN HDMI_AUXN_C HDMI_HPD/HEAC-_CN

8 HDMI_AUXN C1012 1uF 25 V C2 A2

HDMI_TXP0 C1003 0.1uF 10V HDMI_TXP0_C C3 A3 HDMI_TXP0_CN

8 HDMI_TXP0

8 HDMI_TXN0

HDMI_TXN0 C1004 0.1uF 10V HDMI_TXN0_C C4 A4 HDMI_TXN0_CN VDD_3V3

CMF+ESD F1001 D1001

HDMI_CLKP C1005 0.1uF 10V HDMI_CLKP_C C5 A5 HDMI_CLKP_CN PICOSMDC035S ZLLS400

8 HDMI_CLKP HDMI_CLKN HDMI_CLKN_C HDMI_CLKN_CN DCDC_5V_CN

C1006 0.1uF 10V C6 A6 1 2 A C

8 HDMI_CLKN DCDC_5V DNP

A

C1001 C1002 R1011 0 5%

B3

B2

B1

R1013 R1012 R1015 R1014 10uF 0.1uF DNP D1003

RC0201FR-07604RL 604 604 604 604 25V 50V ZLLS400

1% 1% 1% 1%

C

C C

6

3

Q1001A Q1001B Q1002A Q1002B GND

NX3020NAKS NX3020NAKS NX3020NAKS NX3020NAKS R1004 R1009 R1007 J1001

HDMI TYPEA

1.5K 1.5K 27K CON HDMI 1X19

1% 1% 1%

2 5 2 5

TYPE A

HDMI_TXP2_CN HDMI_D2P 1 D2P

2 G_D2

HDMI_TXN2_CN HDMI_D2N 3 D2N

HDMI_TXP1_CN HDMI_D1P 4

1

4

D1P

5 G_D1

HDMI_TXN1_CN HDMI_D1N 6

VDD_PHY_1V8 HDMI_TXP0_CN HDMI_D0P 7 D0P

D1N

GND 8 G_D0

HDMI_TXN0_CN HDMI_D0N 9 D0N

HDMI_CLKP_CN HDMI_CLKP 10 CLKP

U1002 11 G_CLK

PCMF2HDMI2S HDMI_CLKN_CN HDMI_CLKN 12 CLKN

HDMI_TXP2 C1007 0.1uF 10V HDMI_TXP2_C C1 A1 HDMI_TXP2_CN HDMI_CEC_CN HDMI_CEC 13

8 HDMI_TXP2 HDMI_TXN2 HDMI_TXN2_C HDMI_TXN2_CN 8 HDMI_CEC HDMI_Utility/HEAC+_CN

CEC

8 HDMI_TXN2 C1008 0.1uF 10V C2 A2 14 Utility

HDMI_DDC_SCL_CN HDMI_DDC_SCL 15

HDMI_TXP1 HDMI_TXP1_C HDMI_TXP1_CN 8 HDMI_DDC_SCL HDMI_DDC_SDA_CN

SCL

8 HDMI_TXP1 C1009 0.1uF 10V C3 A3 8 HDMI_DDC_SDA HDMI_DDC_SDA 16 SDA

HDMI_TXN1 C1010 0.1uF 10V HDMI_TXN1_C C4 A4 HDMI_TXN1_CN 17

8 HDMI_TXN1 DCDC_5V_CN

G_DDC

CMF+ESD HDMI_5V 18 +5V

HDMI_HPD/HEAC-_CN HPD 19

8 HDMI_HPD HPD

R1017 R1016 R1019 R1018

604 604 604 604

1% 1% 1% 1% B2 GND

B1

G1

6

Q1003A Q1003B Q1004A Q1004B G2

2

NX3020NAKS NX3020NAKS NX3020NAKS NX3020NAKS G3

G4

ESD5B5.0ST1G

ESD5B5.0ST1G

ESD5B5.0ST1G

ESD5B5.0ST1G

R1002

2 5 2 5 1M

1%

TVS1002 1

TVS1003 1

TVS1004 1

TVS1005 1

B B

1

VDD_PHY_1V8

GND

GND

A A

Microcontroller Product Group

6501 William Cannon Drive West

Austin, TX 78735-8598

This document contains information proprietary to NXP and shall not be used for engineering design,

procurement or manufacture in whole or in part without the express written permission of NXP Semiconductors.

ICAP Classification: CP: ___ IUO: _X_ PUBI: ___

Designer: Drawing Title:

<JW>

MCIMX8M-EVKB

Drawn by: Page Title:

<JW> HDMI

Approved: Size Document Number Rev

<Approver> C SCH-38820 PDF: SPF-38820 A1

Date: Thursday, April 25, 2019 Sheet 13 of 23

5 4 3 2 1

5 4 3 2 1

Audio DAC

D D

24-bit 192kHz Stereo DAC 2Vrms Line Out

U1101

L1104

15 AVDD

AVDD 6 LINEVDD 1 2 VDD_3V3

R1103 0 5% 10 LINEVDD 2

6 SAI2_MCLK MCLK CPVOUTN

C 6 SAI2_TXC R1104 0 5% 9 C1110 C1101 C1104 120OHM C

8 BCLK 1uF 4.7uF 4.7uF

6 SAI2_TXFS LRCLK

6 SAI2_TXD 7 25 V 10V 10V

DACDAT 4

LINEGND 13

AGND GND

WM8524CGEDT C1111

2.2uF GND

14 10V

VMID

5 C1103

CPCA C1109 2700pF GND

1uF 50V J1101

3 25 V 1

11 CPCB 4

6 AUD_nMUTE MUTE 2Vrms Line Out, not for Headset!

16 R1101 560 5% 3

12 LINEVOUTR 6

AIFMODE 5

1 R1102 560 5% 2

R1108 LINEVOUTL

TVS1101 ESD5B5.0ST1G

TVS1103 ESD5B5.0ST1G

10K PJ31360-I

2

5% C1102

HP JACK 3.5mm

2700pF

R1109 50V

10K VDD_3V3

5% 3.5mm POLE

1

GND

GND

HSL HSR GND GND

GND

B B

A A

Microcontroller Product Group

6501 William Cannon Drive West

Austin, TX 78735-8598

This document contains information proprietary to NXP and shall not be used for engineering design,

procurement or manufacture in whole or in part without the express written permission of NXP Semiconductors.

ICAP Classification: CP: ___ IUO: _X_ PUBI: ___

Designer: Drawing Title:

<JW>

MCIMX8M-EVKB

Drawn by: Page Title:

<JW> CODEC

Approved: Size Document Number Rev

<Approver> C SCH-38820 PDF: SPF-38820 A1

Date: Thursday, April 25, 2019 Sheet 14 of 23

5 4 3 2 1

5 4 3 2 1

RGMII 10/100/1000 Ethernet

J1201

Inside RJ45 Jack

ENET_VDDIO_2V5 R1201 0 5% ETH_TRX3_N 4 1CT:1CT

D NVCC_ENET_2V5 J8 D- D

C1202 C1203 0.1uF X4

0.22uF 1uF

R1222 50V 25 V

L1201 0

1 2 ENET_AVDD33 5% ETH_TRX3_P 3 J7 D+

VDD_3V3

120OHM C1201 C1204 GND

1uF 0.22uF ENET_VDDH_2V5

25 V 50V ENET_VDDH_2V5 ETH_TRX2_N 6 1CT:1CT

C1205 J6 B-

1uF

25 V

GND ENET_VDD33

C1206 C1207 GND ETH_TRX2_P 5 J5 C-

10uF

25V

0.22uF

50V ENET_LX 1

L1202

2 1.1 V

4.7UH

ENET_DVDDL_1V1

C1208 C1209 ETH_TRX1_N 8

UTP Side

10uF 0.22uF J4 C+

GND 25V 50V

16

29

10

4

3

VDD33

AVDD33

VDDIO_REG

VDDH_REG

LX

GND ETH_TRX1_P 7 J3 B+

GTX_CLK / RX_CLK 125 MHz at 1000 Mbps, 25 MHz at 47

100 Mbps, and 2.5 MHz at 10 Mbps digital clock input DVDDL

35 ETH_TRX0_N 10

6,15 ENET_TXC GTX_CLK J2 A-

L1203

36 8 ENET_AVDDL_1V1 1 2

6,15 ENET_TD0 TXD0 AVDDL1

37 44

6,15 ENET_TD1 38 TXD1 AVDDL2 13 C1211 C1212 C1213 C1214 120OHM

6,15 ENET_TD2 TXD2 AVDDL3

39 19 0.22uF 0.22uF 0.22uF 0.22uF

6,15 ENET_TD3 TXD3 AVDDL4 ETH_TRX0_P

50V 50V 50V 50V 9 J1 A+

34

6,15 ENET_TX_CTL TX_EN

RGMII I/O

C C

GND 1

MODE[2] 33 # 100-Ohm differential pairs

6,15 ENET_RXC RX_CLK

PHYADDRESS0 31 11 ETH_TRX0_P ENET_VDDIO_2V5 R1227 0 5% 2

6,15 ENET_RD0 30 RXD0 TRXP0 12 ETH_TRX0_N

PHYADDRESS1 DNP

VDD_3V3 ENET_VDDH_2V5

6,15 ENET_RD1

MODE[1] 28 RXD1 TRXN0 14 ETH_TRX1_P GND

6,15

6,15

ENET_RD2

ENET_RD3

MODE[3] 27 RXD2

RXD3 U1201 TRXP1

TRXN1

15

17

ETH_TRX1_N

ETH_TRX2_P

1000pF

2KV 4x75 ohms

MODE[0] 32 TRXP2 18 ETH_TRX2_N 15 Shield

6,15 ENET_RX_CTL RX_DV

AR8031 TRXN2

TRXP3

TRXN3

20

21

ETH_TRX3_P

ETH_TRX3_N

16

46 GND_CHASSIS

45 SIP LED_ACT R1202 270 5% LINKACT 11 Green LED

G

ENET_DVDDL_1V1 SIN

R1205 R1206 R1223 R1224 R1204 43 Y

10K 10K 10K 10K 1.5K 42 SOP 12 Yellow LED

5% 5% 5% 5% 1% SON

R1207 10K 5% ENET_SD 41

SD GND

R1209 0 5% MDC 1 LED_LINK1000 R1203 270 5% Link / Active 13 G Green LED

6,15 ENET_MDC MDC

R1210 0 5% MDIO 48 1 Gb/s Link / Active

HR851178C

6,15 ENET_MDIO MDIO 2.5 V (3.3 V tolerant)

C A 2 Y

6,15 ENET_nRST RST LED_LINK10_100 14 Yellow LED

D1201 ZLLS400 100Mb/s Link / Active

OD WOL_INT 40

6,15 ENET_WoL WOL_INT

6,15 ENET_nINT

OD 5 OD

INT

6 CLKO_25MHz LED_LINK10_100

PPS/GPIO 22 26

R1225 DNP TP1201 PHY_CLKOUT 25 PPS VDDH_REG LED_LINK10_100

TP1202 CLK_25M

2.49K Support external 24 LED_LINK1000

1% 25 MHz 1.2 V swing clock input through this pin. ENET_XTLO 6 LED_LINK1000 R1208 1M

XTLO 23 PHYADDRESS2 LED_ACT

ENET_XTLI 7 LED_ACT

XTLI C1216 1000pf 2KV

Y1201 9 C1217 C1218 C1219

GND

B

R1226 DNP 1 4 RBIAS 470PF 470PF 470PF

B

1.2K 50V 50V 50V GND GND_CHASSIS

1% DNP DNP DNP

49

R1211

2 3 2.37K

Low Profile Tab-UP RJ45 with Magnetics / LED

1%

GND 25MHz EMI Filter Reserved

C1220 C1221 GND GND

22PF 22PF 470pF for LED

50V 50V

GND GND

ENET_TX_CTL ENET_nRST

6,15 ENET_TX_CTL ENET_TXC 6,15 ENET_nRST ENET_WoL

6,15 ENET_TXC ENET_TD0 6,15 ENET_WoL ENET_nINT

Power-on Strapping Pins Power-on Strapping Pins CFG 6,15

6,15

ENET_TD0

ENET_TD1

ENET_TD1

ENET_TD2

6,15

6,15

ENET_nINT

ENET_MDC

ENET_MDC

ENET_MDIO

6,15 ENET_TD2 ENET_TD3 6,15 ENET_MDIO

R1212 10K 5% DNP

PHYADDRESS0 ENET_VDDIO_2V5 6,15 ENET_TD3

PHY PIN PHY CFG Default Definition R1213 10K 5%

ENET_RX_CTL

6,15 ENET_RX_CTL ENET_RXC

6,15 ENET_RXC ENET_RD0

RXD0 PHYADDRESS0 0 LED_ACT and RXD1-0 set the lower three bits of the

physical address. The upper two bits of the physical

PHYADDRESS1 R1214 10K 5% 6,15 ENET_RD0 ENET_RD1

address are set to the default, “00”. 6,15 ENET_RD1 ENET_RD2

RXD1 PHYADDRESS1 0 R1215 10K 5% DNP

ENET_VDDH_2V5 6,15 ENET_RD2

PHYADDRESS2 R1216 10K 5% ENET_RD3

6,15 ENET_RD3

LED_ACT PHYADDRESS2 1

MODE[0] R1217 10K 5%

RX_DV MODE[0] 0 0000

0001

1000 Base-T, RGMII;

1000 Base-T, SGMII;

0010 1000 Base-X, RGMII, 50Ω;

RXD2 MODE[1] 0 0011

0100

1000 Base-X, RGMII, 75Ω;

1000 Base-X/T, TRANS, 50Ω;

MODE[1] R1218 10K 5%

0101 1000 Base-X/T, TRANS, 75Ω;

A RX_CLK MODE[2] 0 0110

0111

100 Base-FX, RGMII, 50Ω;

100 Base-FX/TX, TRANS, 50Ω;

A

1011 RMII, copper fiber auto-detection; MODE[2] R1219 10K 5% Microcontroller Product Group

RXD3 MODE[3] 0 1110

1111

100 Base-FX, RGMII, 75Ω;

100 Base-FX/TX, TRANS, 75Ω; 6501 William Cannon Drive West

Others Reserved

MODE[3] R1220 10K 5% Austin, TX 78735-8598

This document contains information proprietary to NXP and shall not be used for engineering design,

LED_LINK1000 INT_SELECT 1 0: INT ; 1:GPIO procurement or manufacture in whole or in part without the express written permission of NXP Semiconductors.

LED_LINK1000 R1221 10K 5%

ICAP Classification: CP: ___ IUO: _X_ PUBI: ___

Designer: Drawing Title:

<JW>

GND MCIMX8M-EVKB

Drawn by: Page Title:

<JW> Ethernet

Approved: Size Document Number Rev

<Approver> C SCH-38820 PDF: SPF-38820 A1

Date: Thursday, April 25, 2019 Sheet 15 of 23

5 4 3 2 1

5 4 3 2 1

WiFi/BT 802.11a/b/g/n/ac + Bluetooth 4.1/ EDR

U1301A E1301

1 GND R1307 0 5%

D WIFI_PCIE_CLKP C1301 100pF 50V 27 57 ANT0 R1348 0 5% ANT0_OUT R1306 0 5% 3 GND_1 D

WIFI_PCIE_CLKN C1302 100pF 50V 28 PCIE_REFCLKP ANT_CORE0 FEED_1 2 GND R1308 0 5%

PCIE_REFCLKN GND_2 GND

1

C1311 0.1uF 50V 31 ACM3-5036-A1-CC-S

8 PCIE1_RXP PCIE_TDP

8 PCIE1_RXN C1312 0.1uF 50V 30 L1302 L1303 J1301

PCIE_TDN 1nH 1nH MXC3N2001

C1304 0.1uF 50V 34 DNP DNP 2

8 PCIE1_TXP PCIE_RDP

8 PCIE1_TXN C1305 0.1uF 50V 33 R1302 0 5% 1

PCIE_RDN 3

2

R1312 0 DO 60 GND

6,17 UART3_RTS BT_UART_RTS

R1313 0 DI 61

6,17 UART3_CTS BT_UART_CTS

6,17 UART3_TXD R1314 0 DI 62 GND

R1315 0 DO 63 BT_UART_RXD

6,17 UART3_RXD BT_UART_TXD E1302

1 GND R1310 0 5%

R1335 0 R1316 0 42 71 ANT1 R1349 0 5% ANT1_OUT R1304 0 5% R1309 0 5% 3 GND_1

6 SAI2_RXFS 6,17 SAI3_TXD BT_PCM_IN ANT_CORE1 FEED_1

6,17 SAI3_TXFS R1317 0 43 2 GND R1311 0 5%

R1337 0 44 BT_PCM_SYNC GND_2 GND

6 SAI2_RXD BT_PCM_OUT

1

6,17,21 SAI3_RXD R1318 0 DNP 45 ACM3-5036-A1-CC-S

R1336 0 BT_PCM_CLK L1304 L1305

6 SAI2_RXC

6,17 SAI3_TXC R1319 0 1nH 1nH J1302

6,17 REF_CLK_32K R1305 0 25 DNP DNP MXC3N2001

LPO 2

6 WL_nPERST 41 1

PERST_L

2

R1320 0 23 7 3

6 WL_REG_ON WL_REG_ON JTAG_SEL

WIFI_PCIE_nCLKREQ OD 39 5 GND

OD 40 PCIE_CLKREQ_L GPIO_6 3 GND

6 PCIE_nPME PCIE_PME_L GPIO_5 4

PD 10 GPIO_4 2

6,17 BT_REG_ON BT_REG_ON GPIO_3

R1321 0 54 6

6 BT_HOST_WAKE BT_HOST_WAKE GPIO_2

6,17 BT_DEV_WAKE 53 8

BT_DEV_WAKE GPIO_0

LBEH5UL1CX-TEMP-D

C C

NOTE:

VDD_3V3 This component share PCB package

When use 9FGV0241 PIN5: GND;PIN7:1.8V

When use PI6CFGL201BZDIEX PIN5:1.8V;PIN7:3.3V

PCIe MEMS OSC

DNP

R1346 0

R1347 0

VDD_1V8

C1315 C1316

1uF 0.01UF L1307

25 V 50V 1 2

VDD_1V8

C1320 C1321 C1322 120OHM

1uF 0.01UF 0.01UF

D1301 D1302 L1306 GND 25 V 50V 50V

1N4148WS 1N4148WS U1301B 1 2

A C A C VBAT:3.35-4.2V 15 1

DCDC_5V 16 VBAT_LDO1 GND1 49 120OHM C1317 C1318 C1319

C1307 C1308 17 VBAT_LDO2 GND2 73 1uF 0.01UF 0.01UF GND

4.7uF 4.7uF VBAT_SR GND3 26 25 V 50V 50V

10V 10V Confirm with Murata to support 3.3V 37 GND4 50

11

20

16

VIO GND5

3

74

L1301 GND6 75

VDD1.8_1

VDD1.8_2

VDDDIG1.8

VDDA1.8

VDDXTAL1.8

1 2 SR_VLX 22 GND7 52 GND CPU CLK

GND 2.2uH SR_VLX GND8 76 PCIE1_REF_CLKP

VDD_CBUCK_1P5 19 GND9 PCIE1_REF_CLKP 8

29

B

21 VDD_CBUCK_1P5 GND10 77 1 PCIE1_REF_CLKN B

SR_PVSS2 GND11 X1_25 PCIE1_REF_CLKN 8

20 78 2 13 R1331 0

SR_PVSS1 GND12 X2 DIF0

VDD_3V3

C1309

GND13

55 Y1301 U1302

4.7uF 79 1 4 14 R1332 0