Professional Documents

Culture Documents

DLD Lab General

DLD Lab General

Uploaded by

Muhammad Abdullah0 ratings0% found this document useful (0 votes)

18 views37 pagesCopyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

Download as pdf

0 ratings0% found this document useful (0 votes)

18 views37 pagesDLD Lab General

DLD Lab General

Uploaded by

Muhammad AbdullahCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

Download as pdf

You are on page 1of 37

TUF EASACABAD ceansbintal tonic Orin

Title:

Objective:

1

Theory:

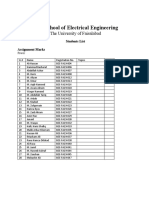

Department of Electrical Engineering | The University of Faisalabad

Introduction to Basic Logic Gate le’s on Digit

tal Logic Trainer.

‘The objective of the first lab is to get familiarize

«To know about the basic logic gates, their truth tables, input-output characteristics, and analyzing

their functionality.

«Introduction to logi

vate IC's, Integrated Circuits pin configurations, and their use.

heory:

«The Digital Logie Circuits can be represented in the form of

+ Boolean Functions,

> Truth Tables,

> Logie Diagram:

«Digital Logic Circuits may be practically implemented by using electronic gates. The following

points are important (o understand.

> Electronic gates are available in the form of Integrated Circuits (IC's) and they require power.

> Supply Gate INPUTS are driven by voltages having two nominal values, e.g. 0V and 5, 12v,

representing logic 0 and logic 1 respectively.

‘The OUTPUT of a gate provides two nominal values of voltage only, e.g. OV and 5, 12V

representing logic 0 and logic 1 respectively. In general, there is only one output to a logic

gate except in some special cases.

> Truth tables are used to help show the function of a logic gate in terms of input values

combined with the desired output.

Diagram is used to represent the Digital Logic Circuit in the form of symbols connected.

+ Digital Logic Circuits can be simulated on the virtual environment called simulation software.

‘© The basic operations are described below with the aid of Boolean function, logic symbol, and

truth table.

-

AND gate:

+ The AND gate is an electronic circuit that gives a high output (1) only if all its inputs are high.

«A dot (,)is used to show the AND operation ie. A.B.

© Bear in mind that this dot is sometimes omitted i.e, AB

12

Scanned with CamScanner

TUF [EASALABAD

Departme: EE-226 Digital Logic Design

MOF Electrical Engineering | the University of Fatalabad

o>

. o OR gate is an electronic circuit that gives a high ouput (1) if one or more ofits inputs are

«Aplus (+) is used to show the OR operation,

Figg

A| BT] A+B

Ol;ol o

0 1 1

1 0 1

1 1 1

Tablet>

NOT gate:

+ The NOT gate is an electronic circuit that produces an inverted version of the input at its output.

* Itisalso known as an inverter.

Figure 1.3

NOT Gate

ALA

(Ey

Lo

TableT3

Scanned with CamScanner

THE UNIVERSITY OF

{Fl FAISALABAD

, ThisisaNOT-AND gate which is equal oan AND gate followed by a NOT gate.

+ The outputs of ll NAND gates are high ifany ofthe inputeare Ion

‘The symbol is an AND gate with a :

\ : Small citcle on the output.

The small circle represents inversion,

bD EE-226 Digital Logic Design

‘partment of Electrical Engineering I The University of Faisalabad

A

<> =

NAND

Figure 1.4

|

5

ut NAND gate

BT (ABy

| Jofo/>|

0

i

0

1

co) ns asf ms

Table 14

)R gate:

* This isa NCT-OR gate which is ‘equal to an OR gate followed by a NOT gate,

+ The outputs of all NOR gates are low if any of the inputs are high,

* The symbol is an OR gate with a small circle on the output, The small circle represents inversion.

— A®B

EOR

Figure 16

(A®B)

0

—|-lele|>

B

0

1

0

1

1

1

0

Table 16

he! fe < aa

e 'Exclusive-NOR' gate circuit does the opposite to the EOR gate.

It will give a low output if either, but not

t both, of its two inputs, are high.

«The symbol is gi it

an EXOR gate with a small circle on the output. The small circle represents

inversion.

A \

B

N

>—— ASB

ENOR

S

Tn

it ENXOR gate

Figure 1.7

(A@By"

1

=|-lo}o|>|

—|o|—lo}x|

0

0

1

Table 17

«Digital systems are said to be constructed by using logic gates.

© These gates are the ‘AND, OR, NOT, NAND,

cages and technologies. Two main classifications are as below:

are available in different pac

co 74Series TTL Logic IC’s

© 4000 series (CMOS Logic IC’s

© 7Aseries are TTL (Transistor-Transistor

The power rating for 74 series is

© This circuitry has fast speed but requires

+ The Pin configuration of basic

gates 2-input IC's

NOR, EXOR, and EXNOR gates. Logic gate IC's

Logic) based integrated circuits family.

5 to 5.5Volts.

more power than later families.

for 74 Series is given in figure 1.8:

Scanned with CamScanner

|

THE UI

TUF | FAISALABAD

‘© Figure 1.9 shows the 4000 series is CMOS (complementary metal-oxide semiconductors) based

integrated circuits. Power ratings are 3V to 15 Volts.

© CMOS circuitry consumes low power but it is not fast as compared to TTL.

inp sate 1 [7]

££-226 Digital Logic Design|

Department of Electrical Engineering | The University of Faisalabad

Z

afin Tl vee | #

2] » fe

Z| o« in [=

TZ] m0 ove |

2] n [2

@| ox fod

7 | 6x0 ou [a

Figure 1.8

inpur gato 1 [2] 4001 fry

4011

out osm 1 [3] 430 (2

ouput gate2 [3] 4070 [ft

input gate 2 [5] 4071 fq

=| 4077

ing gato 2 [6] aggy

9

uad 2-input gates:

ov [7] 4093 FB] put aoa ov

(Z| 4093 |

+3to+15V input gate 1 [1] 1a] +310 +15V

input gate 4 output ga‘e 1 [2

input gate 4 input gate 2

output gate 4 output gate 2

‘output gate 3 input gate 3

input gate3 output gate 3

z 73] input gate 6

3 12] output gate 6

4 11] input gate 5

5 TO] output gate

é

7

9] input gate 4

@] output gate 4

Figure 1.9

© The IC’s available in Lab to perform the Tasks are listed below:

Part 1: Basie Logic Gate Integrated Circuits (IC's)

# Logic gates IC’s

‘© 4001 quad 2-input NOR

4011 quad 2-input NAND

e000

16

Scanned with CamScanner

TIE

THE UNIVERSITY OF

FAISALABAD

© 4081 quad 2-input AND

© 4069 Six Inverting Bester NOT.

Experiment Procedui

Place the IC on the Breadboard as shown in figure 1.10;

£E-226 Digital Logic Design

Department of Electrical Engineering | The University of Fatsalabad

Using the power supply available at KL-31001 Digital Logie Lab, connect pin7 (Ground) and

pinl4 (Vcc) to power up IC,

Give several possible combinations of inputs using the slide switches SW0-SW3 (as shown in

table 1.1 & 1.2) and note down the output with help of LED for all gates.

Figure 1.10

Verify all gates using their ICs on KL-31001 Digital Logic Lab.

INPUTS

OUTPUTS

‘AND

NAND

‘OR

EXOR

EXNOR

|=|-|o}e}>|

]e}=|o]e

Table 18

Make a list of logic gate IC's of the TTL family and CMOS family along with the IC’s names.

Scanned with CamScanner

{i FI THE UNIVERSITY OF 66-226 Digital Loxte Desi

AT VEAISALABAD —— pepanment of tectetcat fnglneering | The University of Falsalabas

Sr.No, | 7400 Series { 4000 Sertes

Fable 19

18,

Scanned with CamScanner

TUF TAISATABAD czzue piston sin

Department of Electrical Engineering | The University of Falsalabad

| Experiment #2 ours

itle: :

To implement Boolean expression through logic gates equation and verification of ‘De-Morgan’s

law.

Objective:

«To leam how to directly convert a Boolean expression to a circuit.

* Verify De-Morgan’s Law.

+ Leam how to simplify Boolean logic equations using De Morgan’s theory.

Theory:

# Aswell asa standard Boolean Expression, the input and output information of any Logie Gate or

ircuit can be plotted into a standard table to give a visual representation of the switching function

of the system.

The table used to represent the Boolean expression of a logie gate function is commonly called a

Truth Table.

Apparatus:

© L-Logie Probe

© 2-Connecting Wire

« 34C’s (7402, 7404, 7404, 7408).

Experiment Procedure:

«First ofall, we check all 1C’s with the IC tester. Then we set it on breadboard wt. the order of

the pins.

* Connect the all IC as shown in fig below.

«Now connect the input volts to the input pins then find the output results and draw the truth table.

‘© Note all the inputs and outputs readings in the table below.

Cire:

© Given the following circuit.

Scanned with CamScanner

Department of Electrical Engineering | The Univer

+ The Boolean expression that represents the above circuit is as follows:

AsEC

ReEC

w

AB

We can simplify the above Boolean expression as follows,

E> aC + AB

| Breaking longest bar

ae By

‘Applying identity & = a

| wMletever doutse bars ot

_ equal length are found

Ar a (AB)

Distributive property

aaB 4 pcad

ying dently an =

tet tm, Spang ently

2K = Oto andB in right

term)

Applying identity A + 0 = A

‘This means that the above circuit ean be replaced by the following one

TUF I FAISALABAD i soe Ect tasted

je Design

{— Input A Input B A’ B A+B? (A.BY

1 1 0 0 0 0

1 0 0 1 1 0

0 1 1 0 1 | 0

0 0 1 1 1 \ 1

20

Scanned with CamScanner

TuF| FAISALABAD EE-226 Digital Logic Design

Department of Electrical Engineering | The University of Faisalabad

periment HS

Title: 4

‘To implement XOR and XNOR using NAND gate.

Objective:

¢ Study the implementation of XOR, NOR, and NAND gates.

How to use the gates?

Apparatus:

* Logic Probe

© Connecting Wire

© IC's (7400, 7400, 7486)

Theory

© The XOR gate (sometimes EOR gate, or EXOR gate and pronounced as Exclusive OR gate) is a

digital logic gate that implements an exclusive or; that is, a true output (1/HIGH) results if one,

and only one, of the inputs to the gate is true.

© If both inputs are false (0/LOW) and both are true or false output results.

XOR represents the inequality function, i.c., the output is true if the inputs are not alike otherwise

the output is false.

© A way to remember XOR is “one or the other but not both".

‘The XNOR gate (sometimes spelled "exon" or “enroll” and rarely written NXOR) is a digital logic

gate whose function is the logical complement of the exclusive OR (XOR) gate.

The two input - version implements logical equality, behaving according to the truth table to the

right. A HIGH output (1) results if both of the inputs to the gate are the same.

© [fone but not both inputs are HIGH (1), a LOW output (0) results.

Experiment Procedure:

© First of all, we check all IC’s with the IC tester. Then we set it on breadboard w.r.. the order of

the pins.

‘* Connect the all IC as shown in fig below.

Now connect the input volts to the input a pin then finds the output results and draw the truth

table.

© Note all the inputs and outputs readings in the table below.

Scanned with CamScanner

THE UNIVER:

TUF | EAISALABAD

Dia;

EE-226 Digital Logic Design

Department of Electrical Engineering | The University of Faisalabad

A|B || Output

ope |e

of1 |} o

to j} o

t|1 fo

Exclusive NOR (XNOR) A| 8 [Joutput

ojo 1

oft |] o

t]o }o

stay

Taput A Input B XOR XNOR

1 1 0 1

1 0 1 0

0 1 1 0

0 0 0 1

a

Scanned with CamScanner

TOP ITAISALABAD, Bene |

Department of Electrical Engineering | The University of Faisalabad

Experiment #4

tle:

‘To write a truth table for half adder

adder using NAND gate only,

Objective:

from truth table design a logic circuit that will act as half

‘The objective of this session is to learn the Half-Adder,

Apparatus:

© Logic Probe

© Connecting Wire

+ IC's (7400, 7400, 7486)

Theory:

* Adders are digital circuits that earry out the addition of numbers.

* Adders are a key component of the Arithmetic Logic Unit.

‘© Adders can be constructed for most of the numerical representations like Binary Coded Decimal

(BDC), Excess ~ 3, Gray code, Binary, etc. out of these, binary addition is the most frequently

performed task by most common adders.

© Apart from addition, adders are also used in certain digital applications like table index

calculation, address decoding, ete.

‘+ Binary addition is similar to that of decimal addition, Some basic binary additions are shown

below.

0 0 1 1

20 td +0 #8

0 1 1 (carry) 10

The adder that performs simple binary addition must have two inputs (augend and addend) and

two outputs (sum and carry), The device which performs the above task is called a Half Adder.

Experiment Procedur

+ First of all, we check all IC’s with an IC tester. Then we set it on breadboard w.

the pins.

* Connect the all IC as shown in fig below.

* Now connect the input volts to the input pins then find the output results and draw the truth table.

‘© Note all the inputs and outputs readings in the table below.

. the order of

a

Scanned with CamScanner

Circuit Diagram:

Truth Table:

Result:

© The Half Adder circuit using NAND gate was implemented using discrete IC and the outputs of

TUF LEAISATABAD

Half Adder Using only NANI

AB

E22 ic Design

Department of Electrical Engineering | The University of Faisalabad

Carry = AB

Truth Table

Input] Output

‘A |B [Sum | Carry |

oto; o | 0

oti To

1fol1 | o

tito tt

ID Gates

sum and carry out were observed on Led’s.

24

Scanned with CamScanner

TE LSE

Dey ‘i

partment of Electrical Engineering | The University of Faisalabad

el

Title:

To implement full adder using two half adders,

Objective:

The objective of this lab is to study the implementation of Full Adder.

Apparatus:

Logic Probe

Connecting Wire

IC’s (7400, 7400, 7486, 7486, 7432)

Theory:

Experiment Procedure:

Circuit Diagram:

We can implement a full adder cireuit with the help of two half adder circuts.

‘At first, a half adder will be used to add A and B to produce a partial Sum and @ second-half adder

logic can be used to add C-IN to the Sum produced by the first halfadder to get the final S output

Ifany of the half adder logic produces a cary, there will be an output cary.

So, COUT will be an OR function of the half-adder Carry outputs:

Take a look at the implementation of the full adder circuit shown below.

Implementation of larger logic diagrams is possible ‘vith the above full adder logic a simpler

symbol is mostly used to represent the operation,

Given below is a simpler schematic representation of aone-bit full adder.

ent Procedurs

First of all, we check all 1C’s with the IC tester- ‘Then we set it on breadboard wt. the order of

the pins.

{ the all IC as shown in fig below.

ae ds the output results and draw the truth

Now connect the input volts to the input a pin then fine

table.

Note all the inputs

below.

and outputs readings in the table

Scanned with CamScanner

UF liar

uth Table:

_EF-226 Digital Logie Design

Department of Electrical Engineering | The University of Faisalabad

sult:

+ The Full Adder circuit was implemented using discrete IC and the outputs of sum and carry out

were observed on Led’s.

Scanned with CamScanner

TUF | FAISAL ABA

Departms F£-226 Digital Logic Design

ont of Electrical Engineering | The Unversity of Fatslabad

2A minimum number of gates,

+The objective ofthe lab to obtain the imp

«Also, design a logic diagram,

‘Apparatus:

+ Logic Probe

* Connecting Wi

«IC's (7400, 7400, 7486, 7486, 7432)

‘Theory:

* Generally, the

* Itisa basi

Subtraction of two binary numbers.

«Inthe earlier article, y

i cle, already we have given the basi theory of a half adder & a full adder which

uses the binary digits for the computation,

+ Likewise, the fullsubtractor uses binary digits ike 6

‘The circuit of the full subtractor can be built with lo

+ The inputs of this subtractor are A,B, Bin and outputs are D, Bout.

+ A full subtractor is formed by two half subtractors, which involves three inputs such as minuend,

suburahend, and borrow, borrow bit among the inpuls is cliained fom the subtraction of two

binary digits and is subtracted from the next higher-order pair of bits, outputs as difference and

borrow.

4 for the subtraction.

Bic gates such as OR, Ex-OR, NAND gate.

Experiment Procedure:

+ First of all, we check all 1C’s with an IC tester. Then we set it on breadboard wrt. the order of

the pins,

* Connect the all IC as shown in fig below.

Now connect the input volts to the input a pin then finds the output results and draw the truth

table.

‘Note all the inputs and outputs readings in the table below.

Scanned with CamScanner

Department of Electrical Engineering |

‘The University of Faisalabad

Truth Table:

Input |" Output

Bis | YX Difference | Bax

[ojtojtol o 0

ojo 1 0

ote 1 1

oti o 0

1yoloy 4 1

itor 0 0

1jijoTo 1

ayaty 1 1

Result:

The Full Subtractor circuit was implemented using discrete IC and the outputs of sum and carry

out were observed on Led’s.

Scanned with CamScanner

jective:

'

BS

‘Theor

Experiment Procedure:

Devertment of Bectrical Engineering | the Uroversy of Paisze?

Ex 7

‘To understand the operation of the BCD to 7

The objective of the lab is to the operation of BCD,

Application of BCD on 7 segment decoder eigen,

atus:

Logic Probe

Connecting Wire

IC's (7ALS47) Decoder Circuit

‘Astandard T-segment LED display generelly hy

and one that acts as a common terminal or con

ction for a

Some single displays have also had an ditional ing

ight or left-hand comer.

‘A Digital Decoder IC is a device that convens one

commonly used deviees for d

Display Decoder.

T-segment LED (Light

avery convenient

even alpha-numeri

iting Diode) or LCD (Liquid Crystal Dispi

1y of displaying information or digital data in the

| characters,

Typically, 7-segment displays consist of seven indi

within one single display package.

wal color LED's (celled the sez

‘Yo produce the required numbers or HEX characters from 0 to 9 and A to F respect

display the correct combination of LED segments need to be illuminated and BCD to 7:

Display Decoders such as the 74LS47 does just that.

A standard 7-segment LED display generally has eight (8) input connections.

segment and one that acts as a common terminal or connection for all

segments.

each LED

internal

Some single displays have also had an additional input pin to display a decimal point

lower-right or lefi-hand corner.

rst of all, we check all IC's with the IC tester. Then we set it on breadboard wr. the order of

the pins.

Scanned with CamScanner

THE UNIVERSITY oF

UF | FAISALABAD

Departmes

nt of Electrical Engi EE-226 Digital Logic Design

Connect the all IC as shown in fj .

‘The University of Faisalabad

3 ig below,

Now connect the input volts to the in

table. 'Pul a pin then fj

inds the-output results and draw the truth

«Note all the inputs and outputs Teadings in the table bel

low.

BRIERE TOofojojojn

ap

lOO)

ofofojofojo

lofofH}Hfofofe|efofo}a:

JopHfoHfofHfofHfofp

Resul

+ The BCD to 7 segment decoder circuit was implemented using discrete IC and the outputs of sum

and carry out were observed on 7 segment display.

30

Scanned with CamScanner

THE UNIVERSITY OF jc Design

qe | FAISALABAD __ epartment of tectrical Engineering | ct Sot of Faisalabad

Ex

eriment # 8

five?

ject

pis’ :

“me objective ofthe lb sto study the implementation of 4

Frasould enable the students How to draw it opie diagram,

grattSt

Logic Probe

{connecting Wire

c's (74.883)

eo

|, Another common and very useful combinational logic circuit which can be constructed using just

4 few basic logic gates allowing it to add together two ot more binary numbers is the Binary

Adder.

4, A basic Binary Adder circuit ean be made from standard AND and Ex-OR gates allowing us 1°

sada” together (wo single bit binary numbers, A and B.

«The addition ofthese two digits produces an output called the SUM of the addition and a second

output called the CARRY or Carry-out, (Cour) bit according to the rules for binary addition.

«One of the main uses for the Binary Adder is in arithmetic and counting circuits. Consider the

simple addition of the two denary (base 10) numbers below.

«From our math’s lessons at school, we learnt that each number column is added together starting

from the right hand side and that each digit has a weighted value depending upon its position

within the columns.

4 When each column is added together a carry is generated ifthe result is greater or equal to 10; the

base number.

«This carry is then added to the result of the addition of the next column to the left and so on

simple schoo! math’s addition, add the numbers and carry.

of binary numbers is exactly the same idea as that for adding together decimal numbers

but this time a carry is only generated when the result in any column is greater or equal to “2”, the

base number of binary.

« Inother words, 1 + 1 creates a carry.

Experiment Procedure:

+ First ofall, we check the IC with IC tester. Then we set it on trainer w.r.t. the order of the pins.

Scanned with CamScanner

- LUVERSITY OF

THe UNIVER a

iF [FAISALABAD —oepanmentet etic agineeng 17 of raisalabad

connect the UP A3, A2, Al, AO with IC pins (1,3,8,10) respectively and also connect the I/P B3.

eT, BO with IC pins (164711) especie,

Be jeanne te pit S with input SV spy

Now cones he pins OFC (15,2, 6, and 9)

53,82, S1,S0.—

Now [eomect pin 14 with 3300 resistance nd LED with C4 eam

rally, {draw all the inputs and oupus and earyin the able,

and pin (12 and 13) are connect with ground. .

With cach of them of 3300 resistance and LED w

ATA nots

———— ns

Yoo AS 2 aay 7)

83 ACB ASO ASO ASR ARD ACB OND

baa coe eee APS) ADS

OUT cASCADNG WmUTS OUTPUTS

‘7ALS83 4-bit Binary Full Adder TTL IC

‘Truth Tables

Input Data A Input Data B Addition

A4 | A3 | A2| Al | B4] B3] B2 [BI | C[S4 | 83 [S2] ST

1}olfolovovTol[ifofofifolilfo

1/ovlovovTifolololijolofolo

O|o|iloytivoyvolofolrfolifo

oOlololifovitiryi [oli sofofo

1}olifotifoliti{ifofoli[o

1 1 2 ee eee)

1}olijotiftifotifiyofi yi ti

Result:

# The 74LS83 4-bit Binary Full Adder TTL IC circuit was implemented using discrete IC and the

outputs of sum and carry out were observed on Leds.

Scanned with CamScanner

IVERSITY OF

ee UES ec22604

a al Logic Desige

qui Les / Department of Electrical Engineering | The University Of

f Faisalabad

Experiment #9

n 4*2 encoder and 2*4 decoder using AND, OR, & NOT Gate.

‘te objective ofthe lab is to implement

pe obi

neoder and decoder,

ogi Probe

connecting Wire

c's (7ALS83)

gosencolle oe

alike a multiplexer that selects one individual data input line and then sends that data to a single

jurput fine oF switch, a Digital Encoder more commonly called a Binary Encoder takes ALL

orp anputs one a ime and then converts them into

ngle encoded output

go we can say that a binary encoder is a multi-input combinational logic eireuit that converts the

fogic level “I” data at its inputs into an eq

alent binary code at its output.

eddecorter

The Binary Decoder is another combinational logic circuit constructed from indi

and is the exact opposite to that of an “Encoder” we looked at in the last tutorial.

The name “Decoder” means to translate or decode coded information from one format into

another, so a digital decoder transforms a set of digit

code at its output.

idual logic gates

al input signals into an equivalent decimal

Experiment Procedur

«First of all, we check the IC with IC tester, Then we set it on trainer w.

+ Connect the circuit of encoder first and then the circuit of decoder.

+ Now apply the input to the encoder first and decoder secondly.

+ Now find the output table and draw it in the truth table.

+ Now we construct the circuit and truth table of required encoder and decoder.

1. the order of the pins.

Scanned with CamScanner

UNIVERSITY OF

[MSALABAD

: sign

' EE-226 Digital Logic Des

Department of Electrical Engineering |

‘The University of Faisalabad

Outputs

DO; —> q i Outputs

7

paa © >| 4x2 Q i Q

r Encoder to4

Inputs D; —v} Zt a

Ds —> Decoder |—» Q:

t—> Q3

sh

a Inputs Outputs

Ds D2 [Di] De Qi 1 Qo

oTototitore

ool ToTo

OM olor to

1Tofotorimy

ooo ToTxtTx

PTencoder

Inputs. Outputs

ALB | Qo] Or QT Os

LOlotifofoto

Olifoti toto

1folotoi to

i{ifotofoti

decoder

Results

«The "2

ee of

oder and 2*4 decoder circuit was implemented using discrete IC and the outputs

sum and carry out were observed on Led’s,

34

Scanned with CamScanner

3 Fl UNIVERSITY OF —

Tu FAISALABAD Departmey -£E-226 Digital Logic Design

—— - int of Elect ‘The University of Faisalabad

Toanalyze the RS Hip Nop using NAND AND

Objectives

1 The objective of the lab is unde

1OR gates,

tstanding the i

«Draw the diagram by using NAND incr ao Of R-S flip flop.

‘Apparatus:

«Logic Probe

© Connecting Wire

«IC (74LS00, 74.802)

Theory:

«A flip-flop circuit consists of two in

« Across coupled conn

ae itching function hereby a pulse on one input line of the flip flop sets

the circuit in one state,

+ Further pulses on this line have no effect until the R-S flip flop is reset. This is accomplished by

a pulse on the other input line,

In this way the RS flip flop is toggled between two states by pulses on different lines.

¢ Although chips are available with R-S functions in them,

flop from spare gates that may already be available on the

achip that may be to hand,

© Tomake an R S$ flip flop,

Using two NAND gates

it is often easier to create an R-S flip

board, or on a breadboard circuit using

it simple neither requires either two NAND gates or two NOR gates.

and active low R S flip flop is produced.

In other words, low going pulses active the flip flop.

As it can be seen from the circuit below, the two incoming lines are applied, one to each gate.

‘The other inputs to each of the NAND gates are taken from the output of the other NAND gate.

It can be seen from the waveform diagram that a low going pulse on input A of the flip flop forces

the outputs to change, C, going high and D going low.

A low going pulse on input B then changes the state, with C going low and D going high.

Experiment Procedure:

© First of all, construct the circuit with the use of NOR gates.

Scanned with CamScanner

qn THE UNIVERSITY oF

UF | EAISALABAD

‘Then find it outputs and drayy ig

{Then Construct the circuit with

{Now find the outputs and drayy

Department of ey EE-226 Digital Logic Design

“ctrlcal Engineering | The University of Falsalabad

truth table,

Pe Ws OfNAND gates,

itin the uth table,

jagram:

STL Reweey

Qa

SL St ©

() Logie diagram

9 foer So, ag)

(eter, Rat)

(©) Truth table

Basic flip-flop circuit with NOR gates

S1F Stay —, a

SL Rterey —] 7

(@) Logic diagram

SR

To, or

V1] 01 (aterSe1,A-0)

o1fio

V1] 10 (alterSu0,Re1)

oolay

(b) Truth table

Basic flip-flop circuit with NAND gates

Result:

© The RS flip flop circuit was implemented and observed on Led’s.

36

Scanned with CamScanner

THE UNIVERSITY OF

“YUP LEAISALABAD

«Logic Probe

« Connecting Wire

+ IC (7ALS08, 741802, 741808, 741 502)

to logic level “I”. Due to this additional clocked | i are equal

combinations, “logic 1”, “logic 0°, eked input, a JK flip-flop has four possible input

tf “no change” and “toggle”.

: te Flop westeieeaed fundamental design problems with the SR flip-flop design, the JK

* This simple 1K Mip Flop is the most widely used of all the flip-flop designs and is considered to

be a universal flip-flop circuit. The two inputs labeled “J” and “K" is not shortened abbreviated

letters of other words, such as “S" for Set and “R” for Reset, butis themselves autonomous letters

chosen by its inventor Jack Kirby to distinguish the flip-flop design from other types,

+ The sequential operation of the JK flip flop is exactly the same as for the previous SR flip-flop

with the same “Set” and “Reset” inputs. The difference this time is that the “JK flip flop” has no

invalid or forbidden input states of the SR. Latch even when S and R are both at logic “1”.

+ The JK flip flop is basically a gated SR Mip-flop with the addition ofa clock input circuitry that

Prevents the illegal or invalid output condition that can occur when both inputs 8 and R are equal

to logic level “1”, Due to this additional clocked input, a JK flip-flop has four possible input

combinations, “logic 1”, “logic 0", “no change” and “togele”.

Experiment Procedure:

«First of all, construct the circuit with the use of NOR gates,

Then construct the circuit with the use of AND gates.

* Now find the outputs and draw it in the truth table.

Scanned with CamScanner

THE UNIVERSITY oF

TUF FAISALABAD

EE-226 Digital Logic Design

The University of Faisalabad

‘Truth Table:

No Change

Reset

Set

Toggle

=|—JeJe[=

Result

+ The JK Mp Mop using D pop cru ws implemented

38

Scanned with CamScanner

VERSITY OF

(| FAISALABAD

EE-226 Digital Logic Design

University of Faisalabad

> ea

§ connecting Wire

© pip Flop Trainer

pot

rv

By connecting the CLK input of the second JK fi "

¥ ae ip Nop to Q of the first JK FF, we obtain a2 bit

The output is at both Q of the flip flops,

The count sequence for Q1Q0 is 00, 01, 10,11,00,01 .. is Signi

Bit) and QO (Least Significant Bit) is the LSB. "hse QU is the MSW (Most Signifean

On the other hand, connecting CLK to Q, we obtain a bit Down Counter,

The count sequence for Q1Q0 is 00, 11, 10,01,00,11... ,

This simple JK flip Flop is the most widely used of all the flip-f i i i

ieee ip-flop designs and is considered to

The two inputs Iabeled “J” and “K” are not shortened abbreviated letters of other words, such as

“S" for Set and “R” for Reset, but are themselves autonomous letters chosen by its inventor Jack

Kirby to distinguish the flip-flop design from other

pes.

The sequential operation of the JK flip flop is exact!

ly the same as for the previous SR flip-flop

with the same “Set” and “Reset” inputs,

The difference this time is that the “IK flip flop” has no invalid or forbidden input states of the

SR Latch even when S and R are both at logic “1”,

The JK flip flop is basically a gated SR flip-lop with the addition ofa clock input circuitry that

prevents the illegal or invalid output condition that ean occur when both inputs S and R are equal

to logic level “1”.

Due to this additional clocked input, a JK

1°, “logic 0”, “no change” and “toggle”.

ip-flop has four possible input combinations, “logic

Experiment Procedure:

First of all construct the circuit using flip flop trainer.

Scanned with CamScanner

JHE UNIVERSITY OF

TF | FAISALABAD Department of Electrical Engineering | 7 etal Loni

he University of Faisalabad

‘Then supply the trainer and clock pulse tothe trainer.

Now find the outputs and draw iti the ruth table

2-BIT ASYNCHRONOUS UP COUNTER

HIGH

‘ruth Tabl

Decimal | 1 Bit | 2" Bit

alta] =f}

Result:

+ The 2-bit binary counter using JK Flip Flop circuit was implemented.

Scanned with CamScanner

a UNIVERSITY OF

TAISALABAD

Department of Electrical Enginee ring |e 2 Dial Lorie Desen

The University of Faisalabad

ive ofthe lab isto lear about the 4-bt synchronous de ide count

decade counter,

0

SS

Bit . :

desde counter is binary counter that is designed to out o 10108 imal 10),

{an ordinary four-stage counter ean be easily modified to deca counter by adding a NAND

* Jae as inthe schematic tothe right,

2

7 8 9 46

sees | 6

Puls | PL

ee! tise

eee Ea

at i

+ ' r t \

' ' | : !

'

as!

t t

ac}

' 1

a0 |

Couto 1 2 3

oe oe oo

+ Notice that FF2 and FF4 provide the inputs to the NAND gate.

+ The NAND gate outputs are connected to the CLR input of each of the FFs."

+ A decade counter is one that counts in decimal digits, rather than binary

+ Itcounts from 0 to 9 and then resets to zero,

+ However, with the Synchronous Counter, the external clock signal is connected to the clock input

of EVERY individual flip-flop within the counter so that all of the flip-flops are clocked together

simultaneously (in parallel) at the same time giving a fixed time relationship.

Scanned with CamScanner

7 UNIVERSE AD

if |fAIS ALA! Department of Electrical Engineering |The Goto asin

Iniversity of Faisalabad

nehronization” with the clock signal

procedure:

sien oe

y 11, construct the circuit using flip flop trainer.

git all

"pny the trainer andl clock pulse fo the rine.

une outputs and draw iin the truth table,

— Output Bit P:

utput Bit Pattern

Clock Count | Os Pos [Or | Or

0 o0fofoto

1 ofofolt

2 ofolifo

3 ofo|iyt

4 o[1 foto

5 02/2/2081

6 of1ft|o

7 (ala |e

8 | sa) 2080

9 1005,

Results

+ By using the same idea of truncating counter output sequences, the above circuit could easily be

adapted to other counting cycles be simply changing the connections to the inputs of the NAND gate

orby using other logic gate combinations.

a2

——

Scanned with CamScanner

UNIVERSITY OF

Tur | {AISALABAD i226 pial Loe ese

Department of Electrica Engineering | The Univorsity of Falealaba

-—_—

4-bit asynchronous decade counter:

Yo Ana

tthe objective of the lab isto Team about the 4-bit

. ynchronous decade counter.

jpparstus:

Logic Probe

«Connecting Wire

«Flip Flop Trainer

Cheory

‘pit asynchronous decade Counter:

«A decade counter is a binary counter that is designed to count to 1010b (decimal 10).

« Anordinary four-stage counter can be easily modified to a decade counter by adding a NAND

gate as in the schematic to the right,

+ Notice that FF2 and FF4 provide the inputs to the NAND gate. The NAND gate outputs are

connected to the CLR input of each of the FFs."

+ Addecade counter is one that counts in decimal digits, rather than binary. It counts from 0 to 9 and

then resets to zero.

Paoungnus %

* An Asynchronous counter can have 2n-1 possible counting states e.g. MOD-16 for a 4-bit counter,

(0-15) making it ideal for use in Frequency Division applications.

* But it is also possible to use the basic asynchronous counter configuration to construct special

counters with counting states less than their maximum output number.

+ For example, modulo or MOD counters.

Scanned with CamScanner

THE UNIVERSITY OF

{UE [FAISALABAD

ig is achieved by forcing the counter to reset i

4. Thisis achieved by eset itself to zero at a pre-determined v; producing,

a type of asynchronous counter that has truncated sequences, nuned Value producin

bit counter that counts upto its maxi J

eae : ‘aximum modulus (2") is call si

anda n-bit counter whose modulus is less than the manimmury ) salted a fll equence counter

:

|

be EE-226 Digital Logic Design

Partment of Electrical Engineering | The University of Faisalabad

periment Procedure:

s

First ofall, construct the circuit using flip flop trainer.

«then supply the trainer and clock pulse to the trainer,

{Now find the outputs and draw it in the truth table,

|

|

|

| circuit Diagram:

|

|

/

Once . :

veces ° a Oe s08)

truth Table:

Ou

Clock Count ‘on foc on te Decimal Value

I otolfoto 0

2 a H

a ofoltto 2

| 4 ofolriti 3

| 3 oft fo po 4

6 oft pom 5

7 o}ttifo 6

8 ofitti 7

9 t[o[o lo 8

10 ie 9

11 | Counter Resets its Outputs back to Zero

Results

* Itis capable of counting numbers from 0 to 15. The clock inputs of all flip flops are cascaded and

the D input (DATA input) of each flip flop is connected to a state output of the flip flop.

Scanned with CamScanner

Department of Electrical Engl

ine

26 Digital Logic Des n

eri =

: 8

8 |The University of Faisataes

pe pp aesrition for a 2-bit counter.

vil

lit

‘ '

cotive of the lab is to learn VHI crit

Pes jctve of IDL description fora 2-bit counter

it

¥ scription fr 2-bit Counter:

q is contained ina VHDL ‘

iosTy OT TA VHDL process with the inj -

‘ - tensity Ts Ths supplies clock of about 16a ak ivded by 8 (CLK_ rv

(2) "130Hz (as supplied by the AVR). 2 when using an input clock of

pout

‘i ter works exactly the same w.

inary COU ay as the clock divider, b

but consists of eight bit

ight bits.

‘ iT register contains the binary count i

COUNT register unter value and is increr

: Cae 's incremented on every rising clock

age of the a

ee the COUNT register is displayed it

he value of t played on the LEDs with the code LE

ED <= not COUNT;

= the count value to compensate fo inverti

hich inverts Ps for the inverting LED out

iputs on the home built

pip board.

; Id also have been impl i

spebinry counter cul plemented using an 11-bit regi :

ap its ofthe register tothe LEDs. a

ve ould then run the eounter atthe same speed asthe above counter wih clock dvdr

* THDLiscommonly used fo write ext modes tha desribe a og cre :

+ Sacha model is processed by a synthesis program, only if it is part of the logic design.

‘simulation program is used fo tet the logic design using simulation modesto represen the

ise cruits that interface tothe design.

+ This collection. of simulation models is commonly called a test bench.

{oxriment Procedure:

| When using VHDL to create a counter, we can take different approaches.

* Weem encode the Boolean equations of the counter diretly with concurrent signal asignment

satements; we can use VHDL code to describe the behavior of the counter; we ean use CASE

sutement to implement the state diagram of the counter; or we may be able to use a predefined

‘ounterin the software package available to you. Using concurrent signa.

4 Here are some useful terms for your reference:

+ Abinary counter is a counter that generates a binary sequence.

1 Theimaximum modulus ofa counters the largest number ofthe counter states hat canbe

represented by n bits, which is 2".

Scanned with CamScanner

qHEUNIVERSITY OF

FAISALABAD _ bepartment ee:

ete enn

Faisalabad

ie ic

(m= 2" for an n-bit counter), ‘modulus is the same

«A Truncated

modulus (

is @ counter whose

22 fe f 10se modulus

m2" foran n-bit counter) modulus is less than its maximum

sTD_LOGIC_ARITH.all;

se IEEE.STD_LOGIC_UNSIGNED all;

cemity counter_2bit is

port (

clk sin STD_LOGIC;

reset : in STD_LOGIC;

dout out STD_LOGIC_VECTOR(1 downto 0)

)

end counter_2bit;

architecture counter_2bit_are of counter

counting: process (clk,reset) is

variable m: std_logie_vector (1 downto 0)

"00"; begin

if (reset='1') then

= "00";

elsif (rising_edge (clk)) then

m:=m-+ 15

end ify

dout <= m;

end process counting;

end counter_2bit_are;

46

Scanned with CamScanner

UNIVERSITY OF

F | FAISALABAD

Departs coer 7

iment of Electrical Engineering 1 The unr te sn

Experiment# 16

le

a VHDL description fora full adder,

>

study the HDL implementation of a full adder,

Thee

E yADL (WHSIC Hardware Deseription Language) is a hard

electronic design automation to describe digital and mi

programmable gate arrays and integrated circ:

VHDL can also be used as a general purpose parallel Programming language,

Full adders are a basic building block for new digital designer

« Lots of introductory courses in digital design Present full

+ Once you understand how a full adder works, you can see how more complicated circuits can be

built using only simple gates,

ware description |

x

language used in

ed-signal_ systems such as. field.

adders to beginners,

«+ Ljust want to make it clear to someone new that in realty,

adders by hand.

«The tools are adv.

FPGA designe

are not coding full

ed enough to know how to add two nu

+ Itsstill a good exercise, which is why it is presented here,

+ Asingle full-adder has two one-bit inputs, a carrysin in

«Many of them can be used together to create a ripple

numbers together.

imbers together.

!pUL, a sum output, and a carry-out output,

carry adder which can be used to add large

Experiment Procedure

+ The procedure is a form of subprograms. It contains local declarations and a sequence of

statements. Procedure can be called in any place of the architecture. The procedure definition

consists of two parts:

+ The procedure declaration, which contains the procedure

when the procedure is called VHDL.

+ The procedure body,

the procedure.

name and the parameter list required

which consists of the local declarations and statements tequired to execute

Code:

library IEEE;

use IEEE.std_logic_1164.all;

~ this is the entity entity ANDGATE is port (

Scanned with CamScanner

THE UNIVERSITY OF

UE HAISALABAD

Deparment of eta egnenng | {Eze al Lonic Des,

sity of Faisalabad

Ir cinstd_logies

std_logies

end entity ANDGA

this isthe architecture architecture RTL. of ANDGA

ose UL and [25

engl architecture RTL;

48

Scanned with CamScanner

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5835)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (350)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (824)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (405)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Class Wise Time Table Fall 2021Document8 pagesClass Wise Time Table Fall 2021Muhammad AbdullahNo ratings yet

- Lecture 3 - Microprocessor Based SystemsDocument46 pagesLecture 3 - Microprocessor Based SystemsMuhammad AbdullahNo ratings yet

- New Text DocumentDocument1 pageNew Text DocumentMuhammad AbdullahNo ratings yet

- Book 1Document389 pagesBook 1Muhammad AbdullahNo ratings yet

- (B) Superposition TheoremDocument4 pages(B) Superposition TheoremMuhammad AbdullahNo ratings yet

- (C) Maximum Power TransformarDocument4 pages(C) Maximum Power TransformarMuhammad AbdullahNo ratings yet

- What Will Cover in This Lab?: Thevenin TheoremDocument5 pagesWhat Will Cover in This Lab?: Thevenin TheoremMuhammad AbdullahNo ratings yet

- Cource OutlineDocument1 pageCource OutlineMuhammad AbdullahNo ratings yet

- Lab Manual: School of Electrical EngineeringDocument13 pagesLab Manual: School of Electrical EngineeringMuhammad AbdullahNo ratings yet

- Assignment No 2 MATLABDocument6 pagesAssignment No 2 MATLABMuhammad AbdullahNo ratings yet

- The University of Faisalabad: School of Electrical EngineeringDocument3 pagesThe University of Faisalabad: School of Electrical EngineeringMuhammad AbdullahNo ratings yet

- School of Electrical Engineering: The University of FaisalabadDocument1 pageSchool of Electrical Engineering: The University of FaisalabadMuhammad AbdullahNo ratings yet

- 2.electronic Devices & CircuitsDocument93 pages2.electronic Devices & CircuitsMuhammad AbdullahNo ratings yet

- 676/chapter 10 Problem 102 1173203Document1 page676/chapter 10 Problem 102 1173203Muhammad AbdullahNo ratings yet

- School of Electrical Engineering: The University of FaisalabadDocument1 pageSchool of Electrical Engineering: The University of FaisalabadMuhammad AbdullahNo ratings yet

- 676/chapter 10 Problem 102 1173203Document1 page676/chapter 10 Problem 102 1173203Muhammad AbdullahNo ratings yet

- English Basic GrammarDocument1 pageEnglish Basic GrammarMuhammad AbdullahNo ratings yet

- Question Example 3.2Document5 pagesQuestion Example 3.2Muhammad AbdullahNo ratings yet

- 676/chapter 10 Problem 102 1173203Document1 page676/chapter 10 Problem 102 1173203Muhammad AbdullahNo ratings yet