Professional Documents

Culture Documents

1 LOS and LOC in Vlsi Conference-Proceeding

1 LOS and LOC in Vlsi Conference-Proceeding

Uploaded by

bharghav saiCopyright:

Available Formats

You might also like

- Scan Insertion - Week2&3Document48 pagesScan Insertion - Week2&3VENKATRAMAN100% (1)

- Tips For Simulation Debug PDFDocument21 pagesTips For Simulation Debug PDFSaurin Shah100% (1)

- Basic ScanDocument20 pagesBasic Scansaikumar bhavana100% (1)

- Split Capture Cycle: During Scan Insertion - During SimulationDocument1 pageSplit Capture Cycle: During Scan Insertion - During Simulationsrikanth0% (1)

- Tessent ATPG Simulation Mismatch Debug: 2016 Mentor Graphics CorporationDocument13 pagesTessent ATPG Simulation Mismatch Debug: 2016 Mentor Graphics Corporationpoojithas acharyaNo ratings yet

- Edt Insertion Lab Observations Test Case 1: - Problem Definition: - InputsDocument42 pagesEdt Insertion Lab Observations Test Case 1: - Problem Definition: - Inputspoojithas acharyaNo ratings yet

- On DFTDocument16 pagesOn DFTAman TyagiNo ratings yet

- A Practical Clock Control Circuit Design & Example Tessent ATPG Test CaseDocument22 pagesA Practical Clock Control Circuit Design & Example Tessent ATPG Test CaseSiva Sreeramdas100% (1)

- MG580225 ATPG Clock Control Logic Appnote v2013 3 LPCT OCCDocument44 pagesMG580225 ATPG Clock Control Logic Appnote v2013 3 LPCT OCCchaitanyaNo ratings yet

- Edt Deterministic Test GuideDocument264 pagesEdt Deterministic Test GuideN Nanda Ganesh100% (4)

- RAM Sequential ATPGDocument14 pagesRAM Sequential ATPGUmesh ParasharNo ratings yet

- ATPG Methodology FlowDocument37 pagesATPG Methodology FlowaanbalanNo ratings yet

- DFT Interview Questions1Document34 pagesDFT Interview Questions1rajkumar gunjaNo ratings yet

- Frequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimeDocument15 pagesFrequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimedeepaNo ratings yet

- Some DFT Related QuestionsDocument5 pagesSome DFT Related QuestionsAdhi SuruliNo ratings yet

- Training On EDT (1) - Copy (1) (3) 1Document52 pagesTraining On EDT (1) - Copy (1) (3) 1veena100% (1)

- Compression AssignmentDocument7 pagesCompression Assignmentpoojithas acharya100% (1)

- DFT DocumentationDocument20 pagesDFT Documentationyamini100% (1)

- Simulation Mismatches Can Foul Up Test-Pattern VerificationDocument6 pagesSimulation Mismatches Can Foul Up Test-Pattern VerificationAdhi SuruliNo ratings yet

- Atpg Question Answer: Name: Meet ZankatDocument7 pagesAtpg Question Answer: Name: Meet ZankatMeet Zankat100% (2)

- Occ CompleteDocument25 pagesOcc CompleteMayur Mestry100% (1)

- COMPRESSION PPT by HK - OdpDocument23 pagesCOMPRESSION PPT by HK - Odpsuneetha100% (6)

- Post-Silicon SOC: Keywords: DFT (Design For Testability), ATPG (Automatic Test Pattern Generation)Document10 pagesPost-Silicon SOC: Keywords: DFT (Design For Testability), ATPG (Automatic Test Pattern Generation)Amena FarhatNo ratings yet

- Scan Insertion FlowDocument9 pagesScan Insertion Flowsharath ANo ratings yet

- DFTDocument21 pagesDFTMuhsin Nk100% (1)

- Timing SimulationDocument3 pagesTiming SimulationKarthik Sharma100% (1)

- Why Boundary Scan Needed?Document39 pagesWhy Boundary Scan Needed?srikanth100% (1)

- Debugging Simulation MismatchesDocument4 pagesDebugging Simulation Mismatcheselectro123eNo ratings yet

- Why Masking Is Needed: Scan Chain Masking in The AcompactorDocument6 pagesWhy Masking Is Needed: Scan Chain Masking in The AcompactorIlaiyaveni IyanduraiNo ratings yet

- EDTDocument47 pagesEDTRaghavendra MatturNo ratings yet

- ATPGDocument54 pagesATPGsrikanth100% (1)

- Few Important QuestionsDocument7 pagesFew Important QuestionsShankhadeep DasNo ratings yet

- Scan PDFDocument49 pagesScan PDFferoz100% (1)

- Streaming Scan NetworkDocument51 pagesStreaming Scan NetworkVENKATRAMAN100% (1)

- Tracing CoverageDocument2 pagesTracing CoverageSrinath M S100% (1)

- Morequestion On DFTDocument4 pagesMorequestion On DFTsenthilkumar100% (1)

- DFT QuestionsDocument8 pagesDFT QuestionsNaga NitheshNo ratings yet

- Q-A's On ATPG & SCAN.Document21 pagesQ-A's On ATPG & SCAN.Hitesh Pradhan0% (1)

- Assignment Section-1 1. What Is DFT?Document18 pagesAssignment Section-1 1. What Is DFT?PAVAN KUMAR TAVADABOINA100% (1)

- Full and Fast SequentialDocument4 pagesFull and Fast SequentialdeepaNo ratings yet

- Assignment 1 Poovika.tDocument12 pagesAssignment 1 Poovika.tsenthilkumarNo ratings yet

- High Test CoverageDocument58 pagesHigh Test CoverageAdhi SuruliNo ratings yet

- Lab2 Block Level SSN Insertion On Processor CoreDocument33 pagesLab2 Block Level SSN Insertion On Processor Corezys WdNo ratings yet

- DFT (Design For Testability)Document21 pagesDFT (Design For Testability)lavanyaNo ratings yet

- ATPG Srivatsa PPTDocument37 pagesATPG Srivatsa PPTMayur Mestry100% (1)

- ATPG Tool FlowDocument12 pagesATPG Tool FlowAdhi SuruliNo ratings yet

- 10 Tips For Successful Scan Design Part OneDocument6 pages10 Tips For Successful Scan Design Part Onebesha1987No ratings yet

- Embedded Deterministic Test: by M. BalakrishnaDocument28 pagesEmbedded Deterministic Test: by M. Balakrishnasuryatejamula0% (1)

- Scan Insertion Lab Observations: Vlsiguru DFT TrainingDocument3 pagesScan Insertion Lab Observations: Vlsiguru DFT Trainingsenthilkumar100% (1)

- SCAN DRC Violation Solutions: Add - Cell - Models Report - DFT - CheckDocument3 pagesSCAN DRC Violation Solutions: Add - Cell - Models Report - DFT - CheckJayesh Popat100% (2)

- Design Clock Controllers For Hierarchical TestDocument2 pagesDesign Clock Controllers For Hierarchical Testneelalohith100% (1)

- MBISTDocument12 pagesMBISTChiranjeevi ChiruNo ratings yet

- Wrapper p1500Document8 pagesWrapper p1500srikanth100% (1)

- Debugging Low Test-Coverage SituationsDocument6 pagesDebugging Low Test-Coverage SituationsBrijesh S D100% (2)

- Scan Insertion Lab ObservationsDocument2 pagesScan Insertion Lab ObservationssenthilkumarNo ratings yet

- What Is DFT in VLSIDocument22 pagesWhat Is DFT in VLSINaga Nithesh100% (4)

- Named Capture ProcedureDocument2 pagesNamed Capture Proceduresenthilkumar50% (4)

- Atpg Lab Notes PDFDocument11 pagesAtpg Lab Notes PDFrajkumar gunja100% (1)

- Basic Interview Questions On DFTDocument5 pagesBasic Interview Questions On DFTHardik TrivediNo ratings yet

- History Rediscovered: Augmented Reality at Museums: By: Hannah WallisDocument12 pagesHistory Rediscovered: Augmented Reality at Museums: By: Hannah Wallisbharghav saiNo ratings yet

- The Ethics of Realism in Virtual and Augmented Reality: Opinion Published: 03 March 2020 Doi: 10.3389/frvir.2020.00001Document13 pagesThe Ethics of Realism in Virtual and Augmented Reality: Opinion Published: 03 March 2020 Doi: 10.3389/frvir.2020.00001bharghav saiNo ratings yet

- Dyslexia Alphabet Using Augmented RealityDocument46 pagesDyslexia Alphabet Using Augmented Realitybharghav saiNo ratings yet

- Grayscale Image Enhancement For Enhancing Features Detection in Marker-Less Augmented Reality TechnologyDocument14 pagesGrayscale Image Enhancement For Enhancing Features Detection in Marker-Less Augmented Reality Technologybharghav saiNo ratings yet

- Assessing Accuracy and Precision of 3D Augmented Reality Holographic Models Derived From DICOM DataDocument12 pagesAssessing Accuracy and Precision of 3D Augmented Reality Holographic Models Derived From DICOM Databharghav saiNo ratings yet

- Multipath Computation of Oading For Mobile Augmented RealityDocument11 pagesMultipath Computation of Oading For Mobile Augmented Realitybharghav saiNo ratings yet

- MARIN: An Open-Source Mobile Augmented Reality Interactive Neuronavigation SystemDocument16 pagesMARIN: An Open-Source Mobile Augmented Reality Interactive Neuronavigation Systembharghav saiNo ratings yet

- Use of Augmented Reality in Reconstructive Microsurgery: A Systematic Review and Development of The Augmented Reality Microsurgery ScoreDocument11 pagesUse of Augmented Reality in Reconstructive Microsurgery: A Systematic Review and Development of The Augmented Reality Microsurgery Scorebharghav saiNo ratings yet

- End-Of-life - Notice For 6500 Sup2Document16 pagesEnd-Of-life - Notice For 6500 Sup2Gazawino1No ratings yet

- Fybcom Sem-I Assignment - Unit - VDocument3 pagesFybcom Sem-I Assignment - Unit - VSufiyan MominNo ratings yet

- 3GTurboCharger Installer Update 3 RC11 Test 1.ShDocument13 pages3GTurboCharger Installer Update 3 RC11 Test 1.ShMoh. FakhrudinNo ratings yet

- Big Data Analytics and Business Process InnovationDocument9 pagesBig Data Analytics and Business Process InnovationAbdulGhaffarNo ratings yet

- p174 Wireless Application Pro To CalDocument9 pagesp174 Wireless Application Pro To Caljnanesh582No ratings yet

- SubNetting Practice LabDocument3 pagesSubNetting Practice LabOdoch HerbertNo ratings yet

- Irb 260Document2 pagesIrb 260ANDRENo ratings yet

- L6 - Information Systems SecurityDocument17 pagesL6 - Information Systems Securityhieubot1111No ratings yet

- Autodesk Ecotect Analysis 2011 Brochure PDFDocument4 pagesAutodesk Ecotect Analysis 2011 Brochure PDFGevionNo ratings yet

- Training Msi MS-5Document23 pagesTraining Msi MS-5adaofisicoNo ratings yet

- Applicant Form PDFDocument5 pagesApplicant Form PDFDaniela ManNo ratings yet

- Management Interface For SFP+: Published SFF-8472 Rev 12.4Document43 pagesManagement Interface For SFP+: Published SFF-8472 Rev 12.4Антон ЛузгинNo ratings yet

- Addl Guidelines Digital BillboardDocument7 pagesAddl Guidelines Digital BillboardrxNo ratings yet

- Tesco SS App Faq 22022020 PDFDocument2 pagesTesco SS App Faq 22022020 PDFairinNo ratings yet

- Harish - Resume QA PCSDocument5 pagesHarish - Resume QA PCSResumeGarageNo ratings yet

- Vip System Base I Processing SpecsDocument206 pagesVip System Base I Processing SpecsMohamed LahlouNo ratings yet

- Class 10 Number Systems Assignment 1Document5 pagesClass 10 Number Systems Assignment 1manojmathewNo ratings yet

- Management Information Systems 16e: Stuxnet and CyberwarfareDocument4 pagesManagement Information Systems 16e: Stuxnet and CyberwarfareBasit BandayNo ratings yet

- Unit 1 - Basic Instrumentation and Measurement Techniques PPT Notes Material For Sem II Uploaded by Navdeep RaghavDocument144 pagesUnit 1 - Basic Instrumentation and Measurement Techniques PPT Notes Material For Sem II Uploaded by Navdeep Raghavavikool1708No ratings yet

- 24051Document3 pages24051bhuvi2312100% (1)

- Variable and Verbal Expressions PDFDocument4 pagesVariable and Verbal Expressions PDFJudgementDay150No ratings yet

- Experiment-2: Quires Using Operators in SQLDocument6 pagesExperiment-2: Quires Using Operators in SQLPhani Kumar SolletiNo ratings yet

- Manual WM Security Routers V2.04 enDocument127 pagesManual WM Security Routers V2.04 enOscar TamayoNo ratings yet

- Tutorial 0 - Part B Modelling Groundwater Flow Using FreewatDocument50 pagesTutorial 0 - Part B Modelling Groundwater Flow Using FreewatУрошМилићNo ratings yet

- PeelDocument4 pagesPeelSaurabh Bansal100% (1)

- Afosi Exp22 Word Ch04 ML1 DesignDocument5 pagesAfosi Exp22 Word Ch04 ML1 Designw215019229No ratings yet

- Filter 777777Document35 pagesFilter 777777Mr BinNo ratings yet

- Design of A Hamming Neural Network BasedDocument9 pagesDesign of A Hamming Neural Network BasedPhạm Minh NhậtNo ratings yet

- Part A Entity Relationship ModelingDocument8 pagesPart A Entity Relationship Modelinghaha huhuNo ratings yet

- GC Buffer BusyDocument19 pagesGC Buffer BusySaeed MeethalNo ratings yet

1 LOS and LOC in Vlsi Conference-Proceeding

1 LOS and LOC in Vlsi Conference-Proceeding

Uploaded by

bharghav saiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

1 LOS and LOC in Vlsi Conference-Proceeding

1 LOS and LOC in Vlsi Conference-Proceeding

Uploaded by

bharghav saiCopyright:

Available Formats

Launch-on-Shift-Capture Transition Tests

Intaik Park and Edward J. McCluskey

Center for Reliable Computing, Stanford University, Stanford, USA

places timing requirements on the routing of scan-enable

Abstract signal.

The two most popular transition tests are launch-on-shift

(LOS) test and launch-on-capture (LOC) test. The LOS

and LOC tests differ in their launch mechanisms, creating

their own pros and cons. In this paper, new hybrids of

LOS and LOC tests that launch transitions using both

launch mechanisms are introduced. The new transition

tests improved fault coverage without significant test

length penalty. This paper presents the concepts and

pattern generation methods of these new transition tests

as well as experimental results that demonstrate the

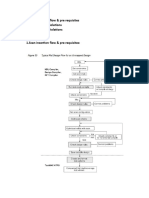

benefits of these tests. Figure 1. The concept and waveforms of LOS

1. Introduction

The transition test [Waicukauski 87] is one of the most

widely used techniques to ensure the correct temporal

behavior of the manufactured integrated circuits (ICs). It

consists of a pair of vectors (V1,V2). The first vector, V1,

initializes a logic value at a fault site (a node in a network).

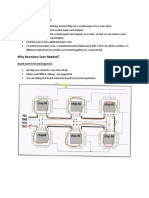

Then, the second vector, V2, launches a transition of logic Figure 2. The concept and waveforms of LOC

values (0Æ1 or 1Æ0) at the fault site and propagates the

Several methods exist to mitigate the timing requirements

transition to an observable point (a scan flip-flop or a

on the scan-enable signal of LOS testing. Level Sensitive

primary output).

Scan Design (LSSD) requires two fast clock signals that

Transition tests are categorized by how they launch could be used to launch and capture transitions

transitions: launch-on-shift (LOS), launch-on-capture [Eichelberger 77]. Another method involves locally

(LOC), and enhanced-scan transition tests. LOS and LOC generating fast scan-enable signals for LOS testing

tests do not require any additional hardware while the [Ahmed 06, Wang 04]. For the rest of the paper, we

enhanced-scan transition test requires special types of assume that the designs considered in this work have

scan flip-flops to apply the test vectors [Dasgupta 81]. capabilities to apply LOS test.

The enhanced-scan transition is not considered in this

The launch-on-capture (LOC) transition test launches a

paper; the focus is only on the first two types of transition

transition through a logic network which is controlled by

tests.

system clock pulses [Eichelberger 91, Savir 94]. In LOC

The launch-on-shift (LOS) test launches a transition of a testing, both launch and capture vectors are initiated by

logic value by the last clock pulse of the scan shift system clock pulses. The concept and waveforms of the

operation [Eichelberger 91, Savir 92], followed by a LOC test are described in Fig. 2.

system clock pulse that captures the transition. Figure 1

In Fig.s 1 and 2, it should be noticed that the second clock

illustrates the concept of LOS testing along with the

pulse (cp2) of LOS and both clock pulses (cp1 and cp2) of

waveforms of clock signal (clk) and scan-enable signal

LOC are system clock pulses. In addition, the LOC test

(SE).

procedure also requires the scan shift operations and

The time period between the launch clock pulse (cp1) and inherently contains the last scan shift clock pulse.

the capture clock pulses (cp2) determines the test However, unlike LOS test, the last shift of LOC need not

application frequency. Note that the scan-enable signal be applied at fast speed.

must fully transition during this time period, and this

Paper 35.3 INTERNATIONAL TEST CONFERENCE 1

1-4244-4203-0/08/$20.00 ©2008 IEEE

Therefore, if an additional system clock pulse is appended transition tests and previous works on the hybrids of LOS

to the LOS test and the last shift clock of the LOC test is and LOC. Section 3 describes the test generation methods.

applied at fast speed, the test applications of both tests are Section 4 presents the experimental setup and results on

identical. This introduces the mix of these two test benchmark circuits. Section 5 discusses the benefits and

methods, or hybrids of LOS and LOC: launch-on-shift- limitations. Finally, Sec. 6 concludes the paper.

capture (LOSC) test and launch-on-capture-shift (LOCS)

test. 2. Previous works

The launch-on-shift-capture (launch-on-capture-shift) test In this section, possible problems related to the two

is a three-pattern test for transition faults that launches transition test approaches as well as previous researches to

transitions by both launch-on-shift and launch-on-capture alleviate these problems are introduced.

mechanisms. The concepts of LOSC and LOCS tests and

their signal waveforms are illustrated in Fig. 3. LOSC 2.1. Untestable faults

(LOCS) tests consist of three vectors (V1,V2,V3). The first LOC test usually achieve lower fault coverages than LOS

vector (V1) initializes a logic value at a fault site as in test. In many cases, it is due to functionally

LOS. Then the second vector (V2) launches a transition unsensitizable faults that are not tested by LOC [Savir 94,

and propagates it. At the same time, V2 also initializes a Rearick 01]. Many of these faults can be tested under

logic value at a different fault site in a way the first vector LOS since it does not launch transitions through a

of LOC does. Finally, the third vector (V3) performs two functional logic network. The detection of these faults by

things; 1) it propagates the fault effect launched by vector LOS methods is suspected to cause over-testing (rejecting

pair (V1,V2), and 2) it launches a transition initialized by good devices by falsely testing under environments that

V2 and propagates it. would not happen in functional mode). Nevertheless, it is

also shown that some of these faults are testable by LOC

when more than two clock pulses are used for fault

activation and propagation [Abraham 06, Zhang 06].

On the other hand, LOS test does not always achieve

100% fault coverage. There are also untestable faults in

LOS testing as described in [Zhang 07]. Some of these

faults are untestable due to shift-dependency, but may

Figure 3. The concept and waveforms of LOCS and LOSC actually fail the system operation if present. To reduce

the number of LOS untestable faults, scan chain

LOSC and LOCS are identical in terms of test application reordering or test-point insertion techniques were

(last shift clock pulse followed by two system clock developed [Li 05, Gupta 03, Wang 03]. It is also

pulses), but differ in how they are generated. LOSC test noticeable that some of these faults may be detected under

is made by generating LOS test first with don’t-care bits LOC test approach [Zhang 06].

unspecified. These don’t-care bits are filled with LOC

test. LOCS test is generated in the same way, but the 2.2. Hybrids of LOS and LOC

LOC test is generated first before LOS test is used to fill As discussed above, LOS-untestable faults may be tested

the don’t-care bits. by LOC while LOC-untestable faults may be tested by

The don’t-care bits are exploited in the context of test set LOS. Naturally, there have been efforts to combine the

compaction [Goel 79], test data compression [Hiraide 03], advantages of both testing methods [Ahmed 06, Wang 04,

or power reduction during scan shift operations [Cho 07]. Devtaprasanna 05].

LOSC and LOCS share the same concept with the In [Ahmed 06, Wang 04], circuits are partitioned into two

compaction scheme; they utilize don’t-care bits to detect regions. One region is controlled by slow scan-enable

additional faults. However, LOSC and LOCS differ from signals to be tested by LOC test. The other region is

existing compaction methods. LOSC (LOCS) targets controlled by locally generated fast scan-enable signals

additional faults either by LOC or LOS, whichever is and tested by LOS test.

easier, while compaction uses only one method to test

additional faults. Therefore, in LOSC and LOCS, LOS- These methods partition circuits into many regions by a

untestable faults can be tested by LOC and LOC- controllability measure or a developed cost function. The

untestable faults by LOS. On the other hand, conventional quality of the partitioning determines the effectiveness of

compaction techniques leave untestable faults undetected. the methods. Also, under these methods, portions of

circuits are tested solely by LOS while other parts are

The rest of the paper is organized as the following. tested by LOC only. Therefore, LOS-untestable faults in

Section 2 discusses the limitations of conventional LOS-tested regions and LOC-untestable faults in LOC-

Paper 35.3 INTERNATIONAL TEST CONFERENCE 2

tested regions are still uncovered. On the other hand, primary ATPG produces test that launches transition by

LOSC and LOCS do not depend on partitioning of LOS (LOC) method.

circuits and they can detect faults by either LOC or LOS,

whichever is easier. Test generation flow (pseudo-code)

While ( undetected fault exists )

Another approach was to implement multiple scan-enable {

signals [Devtaprasanna 05]. These scan-enable signals do Primary LOS (LOC) ATPG

not require fast switching capability, but are controlled Extract care bits of LOS (LOC) pattern

separately. Hence, while some scan-enable signals are Secondary LOC (LOS) ATPG

de-asserted to perform LOC test, other scan-enable (with care bits from LOS (LOC) pattern)

signals are kept high, keeping flip-flops in the shift mode. Fault simulate in LOS (LOC) method

Therefore, some flip-flops perform launch and capture (with don’t-care bits filled by LOC (LOS))

while other flip-flops only launch transitions by shift }

operations.

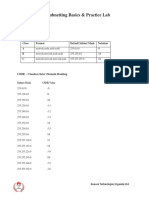

Figure 4. LOSC and LOCS test generation flow

In this method, a fault can be tested either by LOS or

LOC. However, when some faults are tested by one test The secondary ATPG is another ATPG process that

method, other faults in the same scan-enable region have exploits the unspecified bits of the test patterns from the

to be tested by the same method in one test pattern. On primary ATPG to test additional faults. It can be regarded

the other hand, LOSC and LOCS can test faults in as a way to fill don’t-care bits of existing test pattern. To

different methods simultaneously, which may increase the keep the original care bits from the primary ATPG result

efficiency of a test pattern. during the secondary ATPG process, these care bits are

extracted and used as constraints during the secondary

3. Test pattern Generation ATPG. If there are don’t-care bits left after the secondary

To generate LOSC and LOCS tests, Automatic Test ATPG process, they are filled pseudo-randomly. In

Pattern Generator (ATPG) tools for LOS and LOC test LOSC (LOCS) test, the secondary ATPG uses LOC

are required. LOC ATPG can be used directly without (LOS) method.

any modifications, but LOS ATPG requires a slight The resulting test pattern is fault simulated again in LOS

modification. (LOC) method. This is necessary to identify additional

Unlike the conventional LOS test where fault effects are LOS (LOC) detection by the care bits from the secondary

propagated only one time frame, the LOS test for LOSC ATPG.

and LOCS propagates fault effects over two time frames. The iterative network for LOS ATPG would contain twice

However, in this paper, to generate LOS test with two as many faults as in the original network. To prevent

system clocks without modifications to the existing ATPG, falsely testing faults in the second time frame, only faults

the netlists of the circuits were ‘unrolled’ to emulate that belong to the first time frame are considered in LOS

iterative networks of the circuits. The iterative network is ATPG.

a form that emulates multiple time frames of the circuit

operation [McCluskey 58]. Using the unrolled netlists, Table 1. Benchmark circuits

conventional LOS ATPG could be used directly to circuit Gate count FF count No. of Faults

generate LOSC and LOCS. s13207 7,951 625 11,940

The test generation flow is shown in Fig. 4 as a pseudo- s15850 9,772 513 14,738

code. Note that the LOC test generation and fault s38417 22,179 1,564 43,032

simulation in the procedure use regular netlists while the s38584 19,253 1,275 47,074

LOS test generation and fault simulation use unrolled

b17 12,949 1,314 95,328

netlists.

b18 35,884 3,014 263,746

The generation of LOSC and LOCS consists of two b19 69,437 6,030 511,140

ATPG processes: the primary ATPG and the secondary

b20 7,390 430 55,542

ATPG. The primary ATPG is an ATPG process that

generates test patterns without any restrictions. The b21 7,583 430 56,418

patterns generated by the primary ATPG contain don’t- b22 11,135 613 83,664

care bits that are not specified. For LOSC (LOCS), the

Paper 35.3 INTERNATIONAL TEST CONFERENCE 3

Table 2. Test pattern counts and fault coverages of test sets

LOS LOSC LOC LOCS

circuit

length cov Length cov length cov length cov

s13207 179 99.62% 140 99.66% 114 82.85% 98 93.22%

s13580 148 99.73% 137 99.87% 148 71.10% 131 81.12%

s38417 257 98.12% 191 99.76% 293 95.32% 278 95.66%

s38584 171 99.80% 208 99.87% 504 80.97% 384 87.08%

b17 1,305 81.27% 1,264 87.52% 1,584 69.52% 1,579 68.96%

b18 4,521 84.91% 4,404 89.29% 5,002 67.13% 4,910 67.71%

b19 9,602 84.33% 6,400 88.35% 8,365 67.03% 8,223 67.37%

b20 1,240 96.12% 1,446 96.80% 1,484 88.25% 1,490 88.61%

b21 1,199 96.17% 1,475 96.63% 1,464 87.40% 1,329 87.15%

b22 1,413 96.47% 1,692 96.77% 1,583 84.48% 1,604 84.89%

of the test sets. In each row, the shortest test length and

4. Experimental Results the highest fault coverage are bold-faced.

We evaluated the test length and fault coverage of LOSC

Table 2 shows that LOSC tests achieved the highest fault

and LOSC tests on some of ISCAS89 and ITC99

coverage. However, the test length of LOSC was

benchmark circuits shown in Table 1.

comparable to LOS test or shorter than LOS test in some

To attain the most efficient LOSC or LOCS test sets, cases.

single test pattern should be generated by the primary

LOCS performs better than LOC, but worse than LOS and

ATPG and filled by the secondary ATPG before the next

LOSC. That is because the LOCS test generation

pattern is considered. In this way, the primary ATPG for

terminates when the primary LOC ATPG cannot produce

the next pattern would not target faults that could be

any more tests for undetected faults, without invoking the

detected by the secondary ATPG for the previous pattern.

secondary LOS ATPG even though some of these faults

However, the commercial ATPG tool is highly optimized could be tested by LOS.

for compaction. Due to the optimization, when the ATPG

The CPU time required to generate these test sets were not

tool generates one test pattern at a time and repeats until

considered in this experiment. The commercial ATPG

all the faults are tested or tried, the resulting test length

tool is optimized to generate pure LOS or LOC tests, but

was abnormally longer than a test generated at once by the

the generation of LOSC and LOCS tests requires

same ATPG tool. It is unfair to compare our approach

invocations of both LOS and LOC ATPGs. In addition,

with the LOS and LOC generated at once due to the

the implementation of LOSC and LOCS is not integrated

optimization performed on the latter. Thus, we settled

into the ATPG tool, but it is rather an augmented form.

with something in between the two extreme cases.

Therefore, in this work, the qualities of the test sets are

For the purpose of fair comparison, all the test sets in this compared without considering the test generation time.

paper were generated in a group of 32 patterns, so that

both the proposed approach (LOSC and LOCS) and the 4.2. Fault Coverage

base case (LOS and LOC) do not benefit from the LOSC and LOCS tests achieve higher fault coverage

optimization of the ATPG tool. compared to LOS and LOC respectively. These

In addition, all the test patterns were generated with the improvements in fault coverage are due to the

default backtracking limit (abort limit of 10) and the undetectable faults under one method (LOC or LOS)

default compaction option (high compaction). being detected by the other method. Table 3 summarizes

undetected faults in each method. Column 2 shows the

4.1. LOSC and LOCS test sets total number of faults in each circuit. Column 3 and 4

represent undetected faults by LOS and LOC test

LOSC and LOCS test sets were generated as described

respectively. Column 5 shows the number of undetected

above. They are compared with LOS and LOC test sets in

faults after applying both LOS and LOC. Finally, column

terms of test length and fault coverage in Table 2. In this

6 and 7 represents undetected faults of LOSC and LOCS

table, columns under label ‘length’ represent test length

test respectively. In each row, the entries with the fewest

and columns labeled as ‘cov’ represent the fault coverages

undetected faults are bold-faced.

Paper 35.3 INTERNATIONAL TEST CONFERENCE 4

Table 3. Undetected faults of each test method

circuit total faults LOS LOC LOS+LOC LOSC LOCS

s13207 11,940 45 2,047 38 40 810

s15850 14,738 38 4,255 21 20 2,782

s38417 43,032 900 1,926 122 102 1,824

s38584 47,074 94 8,929 63 63 6,082

b17 95,328 17,437 28,726 11,641 11,871 29,592

b18 263,746 40,231 85,672 26,029 28,766 85,158

b19 511,140 81,175 169,142 53,981 54,439 166,789

b20 555,42 2,176 6,484 1,752 1,783 6,328

b21 56,418 2,167 7,067 1,802 1,871 7,249

b22 83,664 2,874 12,872 2,614 2,709 12,642

In most cases, the combination of LOS and LOC had the test set and LOC detection is insignificant in the

fewest undetected faults, or the most detected faults. beginning of the test set. However, at certain points (at

Table 3 shows that some of LOS undetected faults were pattern number 992 in Fig. 5 and at pattern number 1,312

detected by LOC test and the some of LOC undetected in Fig. 6), the number of LOC detected faults increases

faults by LOS test. Hence, when both LOS and LOC tests while additional LOS detection is minimal.

were applied, the number of undetected faults was the

least. However, it should be noticed that LOSC detected % don't-care bits

100.00%

the comparable number of faults to the combination of 95.00%

LOS and LOC. 90.00%

To show the portion of LOS detected faults and LOC 85.00%

detected faults in LOSC test, the numbers of faults in each 80.00%

category of b17 and b18 circuits are plotted in Fig. 5 and 75.00%

Fig. 6 respectively.

8

2

88

84

64

32

12

22

32

41

51

60

70

80

89

99

10

11

12

80,000 Pattern Number

70,000

Figure 7. Don’t-care bit percentages of test patterns (b17)

Detected Faults

60,000

50,000 100.00%

% don't-care bits

40,000

95.00%

30,000 loc detect

90.00%

los detect

20,000

32 192 352 512 672 832 992 1152 1312 1472 85.00%

Pattern Number 80.00%

Figure 5. LOSC test - detected faults by LOS and LOC (b17)

32

288

544

800

1056

1312

1568

1824

2080

2336

2592

2848

3104

3360

3616

3872

4128

4384

225000

Pattern Number

205000

185000

Figure 8. Don’t-care bit percentages of test patterns (b18)

Detected Faults

165000

145000 It is well known that, in the last phase of test pattern

125000 generation, a significant number of patterns is required to

105000

gain the last small portion of fault coverage [McCluskey

85000 LOC detect

65000 89]. The patterns generated at the end are less efficient, or

LOS detect

45000 contain many don’t-care bits, which give the secondary

32 320 608 896 1184 1472 1760 2048 2336 2624 2912 3200 3488 3776 4064 4352

ATPG more freedom to produce tests for additional faults.

Pattern Number

Figure 6. LOSC test - detected faults by LOS and LOC (b18) The percentages of don’t-care bits in scan loads of the

primary ATPG (LOS) generated test patterns in LOSC are

In Fig.s 5 and 6, it is shown that the LOS detected faults plotted in Fig.s 7 and 8. In these figures, each column

are the majority of detected faults throughout the entire shows the average percentage of don’t-care bits of 32 test

Paper 35.3 INTERNATIONAL TEST CONFERENCE 5

patterns, which would be fed to the secondary ATPG to count can be decreased if they are targeted by LOC ATPG

generate additional LOC tests. instead of LOS ATPG.

The test patterns contain many don’t-care bits (over 95% Even though LOSC test achieved higher fault coverage

of a scan load) starting from pattern number 992 in Fig. 7 compared to LOS test, the longer test length is not

and pattern number 1,312 in Fig. 8. Notice the points desirable. To fairly compare the test length and fault

where the percentages of don’t-care bits increase and coverage of LOSC and LOS, the fault coverage of both

where the LOC detection increases (Fig. 5 and Fig. 6) are tests were plotted in Fig. 9 and Fig. 10.

aligned.

90%

4.3. Test Set Length 80%

Fault Coverage

LOCS test were shorter and achieved higher fault 70%

coverage than LOC test. However, the fault coverage of 60%

LOCS test was still lower than LOS or LOSC test. On the 50%

other hand, LOSC test improved fault coverage of LOS LOSC

40%

test, but it sometimes resulted in longer test length. LOS

30%

The increased test length of LOSC over LOS is suspected 32 352 672 992 1312

to be caused by the two-time-frame propagation Pattern Number

requirements of LOS test used in LOSC. To verify this

assumption, LOS test sets generated for original circuits Figure 9. Fault coverage comparison of LOS and LOSC (b17)

and the unrolled circuits (faults propagated over two time

frames) are compared in Table 4. 100%

90%

Table 4. Comparison on LOS of original and unrolled circuit

Fault Coverage

80%

LOS LOS Unroll LOSC 70%

circuit

length fc (%) Length fc (%) Pat fc (%) 60%

50%

s13207 172 99.63 217 99.61 140 99.66 40% LOSC

s13580 152 99.74 184 99.69 137 99.87 30%

LOS

s38417 257 98.08 293 98.24 191 99.76 20%

32 672 1312 1952 2592 3232 3872 4512

s38584 173 99.80 206 99.80 208 99.87

Pattern Number

B17 1,305 81.27 1,654 81.17 1,264 87.52

B18 4,521 84.91 5,773 83.38 4,404 89.29 Figure 10. Fault coverage comparison of LOS and LOSC (b18)

B19 9,602 84.33 11,823 82.76 6,400 88.35

In these figures, the fault coverage of LOS is higher than

B20 1,240 96.12 1,258 95.13 1,446 96.80 LOSC at the first portion of the test set. But, in the later

B21 1,199 96.17 1,218 95.42 1,434 96.69 part of the test set, LOSC achieves higher fault coverage

B22 1,413 96.47 1,617 95.64 1,692 96.77 than LOS. The cross-over points are at pattern number

992 in Fig. 9 and pattern number 1,056 in Fig. 10. These

In Table 4, columns under ‘length’ represent the test points are the same or very close to where the number of

lengths and columns under ‘fc’ show the fault coverages. don’t-care bits (Fig.s 7 and 8) and the LOC fault

The test lengths for the unrolled circuits were always detections are increased (Fig.s 5 and 6).

longer than the tests for the original circuits. However, If the highest possible fault coverage is desired, LOSC

LOSC tests were usually shorter than LOS for unrolled test is better than LOS test. If the test length is the

circuits and sometimes even shorter than LOS for original concern and the test has to be truncated, LOSC has higher

circuits. This is when the additional fault detection by fault coverage as long as the test set is truncated after the

LOC in LOSC test compensated the test length penalties cross-over point (pattern number 992 of b17 LOSC test

from the two-time-frame propagations of unrolled LOS. and pattern number 1,056 of b18 LOSC test).

The test length reduction of LOSC over unrolled LOS can

also be coming from the mixed use of LOS and LOC. As 4.4. Launch-on-shift with Launch-on-capture top-off

discussed above, a significant number of patterns are used We think that LOSC and LOCS tests achieved higher fault

to test hard-to-detect faults at the end of test generations. coverages because they use both LOS and LOC methods.

However, hard-to-detect faults in LOS are not necessarily Hence, it would be natural to compare LOSC tests with

hard-to-detect in LOC. When this is the case, the pattern combinations of LOS and LOC tests.

Paper 35.3 INTERNATIONAL TEST CONFERENCE 6

LOS test achieved higher fault coverage and shorter test Secondly, the more don’t-care bits in a test pattern, the

length than LOC test. However, like all the transition test better the secondary LOC ATPG performed, detecting

generations, LOS test generation becomes inefficient more faults by the LOC method.

when only hard-to-detect faults are left and many patterns

are required to detect these faults to improve the last 5. Discussions

portion of the fault coverage. Therefore, it may be

The benefits of LOSC and LOCS tests are as the

beneficial to switch to LOC test at certain point and

followings. First, they target untestable faults under one

generate top-off LOC patterns, which test hard-to-detect

method (LOS or LOC) using the other method, improving

faults of LOS testing using LOC test.

fault coverage. Secondly, hard-to-detect faults in one

To compare this idea with LOSC test sets, LOS tests were method may be east-to-detect in the other method. Hence,

topped-off with LOC tests at four different points. Each testing each fault using the easier way can improve the

group of 32 patterns were fault simulated during the LOS efficiencies of test patterns, which may decrease test

test generation and when the increase of the fault coverage length. Lastly, they can be implemented on top of

by the last 32 pattern was 1) less than 1%, 2) less than existing ATPG with compaction, leading to more efficient

0.5%, 3) less than 0.2%, and 4) less than 0.1%, the LOS use of don’t-care bits.

test generation stopped and LOC test generation started on

LOSC and LOCS tests also have limitations. First, they

the remaining undetected faults. The resulting test sets

require fast switching scan-enable signals. However, even

are shown in Table 5.

without the fast SE signal, a LOCS test set has an

In Table 5, the test with the highest fault coverage is bold- advantage over a conventional LOC test. The LOS fault

faced. LOSC test always achieved the highest fault activation mechanism initiates transitions of logic values

coverage. LOS tests topped-off with LOC tests achieved at fault sites and propagates the fault effects. This is

comparable fault coverages to LOSC test sets, but with analogous to a test for stuck-open faults when they are not

more test patterns. applied at-speed. Hence, LOCS would have higher stuck-

open fault coverage than LOC.

4.5. Experimental Result Summary

Secondly, the LOS test in LOSC (LOCS) needs to

LOSC and LOCS showed higher fault coverage than LOS propagate fault effects over two time frames rather than

and LOC tests respectively. LOSC test sets were one time frame of the conventional LOS test, which

sometimes longer and sometimes shorter than LOS tests penalizes the test length. However, when combined with

while LOCS achieved more compact test than LOC test in LOC, LOSC and LOCS performed the same or the better

most cases. in terms of fault coverage and/or test length compared to

Given the higher fault coverages of LOSC test set, aspects pure LOS, which justifies the use of two time frames.

that affect the LOSC test length were investigated. First, In this paper, possible improvements of LOS and LOC

when LOS fault coverage is relatively low (or more room transition tests in terms of test length and fault coverage

to improve fault coverage), LOSC test set achieved better were investigated. However, the quality of the test set is

compaction with significant fault coverage improvement. not only measured by these two metrics. Other ways to

Table 5. LOS test topped-off with LOC test

LOS+LOC LOS+LOC LOS+LOC LOS+LOC

LOS (orig) LOSC

(<1%) (<0.5%) (<0.2%) (<0.1%)

circuit length fc (%) length fc (%) length fc (%) length fc (%) length fc (%) length fc (%)

s13207 172 99.63 144 99.47 144 99.47 144 99.47 NA NA 140 99.66

s13580 152 99.74 107 97.21 145 99.46 145 99.46 145 99.46 137 99.87

s38417 257 98.08 189 99.08 231 99.49 231 99.49 NA NA 191 99.76

s38584 173 99.80 177 98.31 238 99.63 238 99.63 238 99.63 208 99.87

b17 1,305 81.27 1,090 83.99 1,330 85.83 1,563 86.90 1,680 87.11 1,264 87.52

b18 4,521 84.91 3,142 84.42 3,518 87.21 3,823 88.20 3,990 88.47 4,404 89.29

b19 9,602 84.33 5,396 81.26 5813 84.53 6,257 86.22 6,382 86.53 6,400 88.35

b20 1,240 96.12 1,103 95.11 1,154 95.30 1,464 96.11 1,830 96.62 1,446 96.80

b21 1,199 96.17 1,065 93.99 1,293 95.15 1,671 96.30 1,795 96.54 1,434 96.69

b22 1,413 96.47 1,070 93.18 1,253 94.43 1,572 95.60 1,867 96.57 1,692 96.77

Paper 35.3 INTERNATIONAL TEST CONFERENCE 7

improve the transition test quality include applying the Using Multiple Scan Enable Signals,” Proc. ICCD, pp.

concept of TARO (Transition fault propagated to All 471-474, 2005.

Reachable Outputs) [Tseng 01, Park 05], N-detect [Ma [Eichelverger 77] Eichelberger, E. B. and T. W. Williams, “A

95] or employing multiple clock cycles [Zhang 06]. Logic Design Structure for LSI Testability,” Proc. Design

Automation Conf., pp. 462-468, 1977.

The idea of mixing two different tests in one test pattern [Eichelberger 91] Eichelberger, E. B., E. Lindbloom, J. A.

should not be limited to the hybrids of LOC and LOS. Waicukauski and T. W. Williams, “Delay-Fault

Previous researchers have shown the importance of using Simulation,” Structured Logic Testing, McCluskey (Ed.),

Prantice-Hall, Inc., Englewood Cliffs, New Jersey, 1991.

multiple test metrics to test manufactured ICs [Maxwell

[Ferhani 06] F.-F. Ferhani and E. J. McCluskey, “Classifying

93, Nigh 97, Ferhani 06]. The hybrid concept of LOSC Bad Chips and Ordering Test Sets,” Proc. Int’l Test Conf.,

can be extended to the mix of different test metrics for this pp. 1-10, 2006.

purpose. As long as don’t-care bits are available in test [Goel 79] P. Goel and B. C. Rosales, “Test Generation &

patterns, they can be exploited to generate additional tests Dynamic Compaction of Tests,” Dig. Papers Test Conf.,

for different metrics. For example, LOC and single stuck- pp. 182-192, 1979.

at fault test or single stuck-at test and bridge fault test can [Gupta 03] P. Gupta, et. al., “Layout-Aware Scan Chain

be combined. Synthesis for improved Path Delay Fault Coverage,” Proc.

ICCAD, pp. 754-759, 2003.

[Hiraide 03] Hiraide, T., et al., “BIST-aided Scan Test – A new

6. Conclusion Method for Test Cost Resutction,” Proc. VLSI Test Symp.,

In this paper, Launch-on-Shift-Capture and Launch-on- pp. 359-364, 2003.

Capture-Shift tests are introduced. These tests exploits [Li 05] W. Li, et. al., “Distance Resticted Scan Chain Reordering

don’t-care bits of existing LOS (LOC) test set to detect to Enhance Delay Fault Coverage,” Proc. Int’l Conf. VLSI

Design, pp. 471-478, 2005.

additional faults by LOC (LOS) launch mechanism, which

[Ma 95] S. C. Ma, P. Franco, and E. J. McCluskey, “An

may be more efficient for some faults. Experimental Experimental Chip to Evaluate Test Techniques

results showed that LOSC test achieved higher fault Experiment Results,” Proc. Int’l. Test Conf., pp. 663-672,

coverage than any other test or mix of test sets. 1995.

[Maxwell 93] P. C. Maxwell and R. C. Aitken, “Test Sets and

7. Acknowledgments Reject Rates: All Fault Coverages are Not Created Equal,”

IEEE Design & Test, pp. 42-51, 1993.

We thank Rohit Kapur of Synopsys, Brion Keller of [McCluskey 58] E. J. McCluskey, “Iterative Combinational

Cadence and Samy Makar of C-Switch for their helpful Switching Networks – General Design Considerations,”

discussions and support. We thank all the members of IRE Trans. Elctron. Comput., Vol. EC-7., pp. 285-291,

CRC for their help. 1958.

[McCluskey 89] E. J. McCluskey and F. Buelow, “IC Quality

and Test Transparency,” Trans. IEEE Industrial

8. References Electronics, vol. 36, no. 2, May, 1989.

[Abraham 06] J. Abraham, U. Goel, A. Kumar, “Multi-Cycle [Nigh 97] P. Nigh, W. Needham, K. Butler, P. Maxwell, R.

Sensitizable Transition Delay Faults,” Proc. VLSI Test Aitken, and W. Maly, “So What is an Optimal Test Mix?

Symp., 2006. A Discussion of the SEMATECH Methods Experiment,”

[Ahmed 06] N. Ahmed, M. Tehranipoor, “ Improving Transition Proc. Int’l Test Conf., pp. 1037-1038, 1997.

Delay Test Using a Hybrid Method,” IEEE Design & Test, [Park 05] I. Park, A. Al-Yamani, E. J. McCluskey, “Effective

vol. 23, issue 5, pp. 402-412, 2006. TARO pattern generation,” Proc. VLSI Test Symp., pp.

[Avramovici 92] M. Abramovici, P. S. Parikh, “Warning: 100% 161-166, 2005.

Fault Coverage May Be Misleasing!,” Proc. Intl. Test. [Rearick 01] J. Rearick, “Too much delay fault coverage is a bad

Conf., pp. 662 – 671, 1992. thing,” Proc. Int’l Test Conf., pp. 624-233, 2001.

[Butler 04] Butler, K. M., et al., “Minimizing Power [Savir 92] J. Savir, “Skewed-Load Transition Test: Part I,

Consumption in Scan Testing: Pattern Generation and Calculus,” Proc. Intl. Test Conf., pp 705-714, 1992.

DFT Techniques,” Proc. Intl. Test Conf., pp. 355-364, [Savir 94] J. Savir and S. Patil, “Broad-side delay test,” IEEE

2004. trans. On CAD of IC and System, vol. 13, pp. 1057-1064,

[Cho 07] K.Y. Cho, S. Mitra, and E. J. McCluskey, “California 1994.

Scan Architecture for High Quality and Low Power [Tseng 01] C. W. Tseng and E. J. McCluskey, “Multiple-output

Testing,” Proc. Int’l Test Conf., 2007. propagatioin transition fault test,” Proc. Int’l. Test Conf.,

[Dasgupta 81] S. Dasgupta, R. G. Walther, T. W. Willams and E. pp. 358-366, 2001.

B. Eichelberger, “An Enhancement to LSSD and Some [Wang 03] S. Wang and S. T. Chakradhar, “Scalable Scan-Path

Applications of LSSD in Reliability, Availability and Test Point Insertion Technique to Enhance Delay Fault

Serviceability”, Proc. FTCS, pp. 880-885, 1981. Coverage for Standard Scan Designs,” Proc. Int’l. Test

[Devtaprasanna 05] N. Devtaprasanna, A. Gunda, P. Conf., pp. 574-583, 2003.

Krishnamurthy, S. M. Reddy and I. Pomeranz, “A Novel [Wang 04] S. Wang, X. Liu, S. T. Chakradhar, “Hybrid delay

Method of Improving Transition Delay Fault Coverage scan: a low hardware overhead scan-based delay test

technique for high fault coverage and compact test sets,”

Paper 35.3 INTERNATIONAL TEST CONFERENCE 8

Proc. Deaign Automation and Test in Europe, vol. 2. pp.

1296-1301, 2004

[Waicukauski 87] J. Waicukauski, et. al., “Transition Fault

Simultaion,” IEEE Design and Test, pp. 32-38, April 1987.

[Zhang 06] Z. Zhang, et. al., “Scan Tests with Multiple Fault

Activation Cycles for Delay Faults,” Proc. VLSI Test

Symp., 2006.

[Zhang 07] Z. Zhang, S.M. Reddy, I. Pomeranz, “Warning:

Launch off Shift tests for Delay Faults May Contribute to

Test Escapes,” Proc. Asia and South Pacific Design

Automation Conf., 2007.

Paper 35.3 INTERNATIONAL TEST CONFERENCE 9

You might also like

- Scan Insertion - Week2&3Document48 pagesScan Insertion - Week2&3VENKATRAMAN100% (1)

- Tips For Simulation Debug PDFDocument21 pagesTips For Simulation Debug PDFSaurin Shah100% (1)

- Basic ScanDocument20 pagesBasic Scansaikumar bhavana100% (1)

- Split Capture Cycle: During Scan Insertion - During SimulationDocument1 pageSplit Capture Cycle: During Scan Insertion - During Simulationsrikanth0% (1)

- Tessent ATPG Simulation Mismatch Debug: 2016 Mentor Graphics CorporationDocument13 pagesTessent ATPG Simulation Mismatch Debug: 2016 Mentor Graphics Corporationpoojithas acharyaNo ratings yet

- Edt Insertion Lab Observations Test Case 1: - Problem Definition: - InputsDocument42 pagesEdt Insertion Lab Observations Test Case 1: - Problem Definition: - Inputspoojithas acharyaNo ratings yet

- On DFTDocument16 pagesOn DFTAman TyagiNo ratings yet

- A Practical Clock Control Circuit Design & Example Tessent ATPG Test CaseDocument22 pagesA Practical Clock Control Circuit Design & Example Tessent ATPG Test CaseSiva Sreeramdas100% (1)

- MG580225 ATPG Clock Control Logic Appnote v2013 3 LPCT OCCDocument44 pagesMG580225 ATPG Clock Control Logic Appnote v2013 3 LPCT OCCchaitanyaNo ratings yet

- Edt Deterministic Test GuideDocument264 pagesEdt Deterministic Test GuideN Nanda Ganesh100% (4)

- RAM Sequential ATPGDocument14 pagesRAM Sequential ATPGUmesh ParasharNo ratings yet

- ATPG Methodology FlowDocument37 pagesATPG Methodology FlowaanbalanNo ratings yet

- DFT Interview Questions1Document34 pagesDFT Interview Questions1rajkumar gunjaNo ratings yet

- Frequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimeDocument15 pagesFrequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimedeepaNo ratings yet

- Some DFT Related QuestionsDocument5 pagesSome DFT Related QuestionsAdhi SuruliNo ratings yet

- Training On EDT (1) - Copy (1) (3) 1Document52 pagesTraining On EDT (1) - Copy (1) (3) 1veena100% (1)

- Compression AssignmentDocument7 pagesCompression Assignmentpoojithas acharya100% (1)

- DFT DocumentationDocument20 pagesDFT Documentationyamini100% (1)

- Simulation Mismatches Can Foul Up Test-Pattern VerificationDocument6 pagesSimulation Mismatches Can Foul Up Test-Pattern VerificationAdhi SuruliNo ratings yet

- Atpg Question Answer: Name: Meet ZankatDocument7 pagesAtpg Question Answer: Name: Meet ZankatMeet Zankat100% (2)

- Occ CompleteDocument25 pagesOcc CompleteMayur Mestry100% (1)

- COMPRESSION PPT by HK - OdpDocument23 pagesCOMPRESSION PPT by HK - Odpsuneetha100% (6)

- Post-Silicon SOC: Keywords: DFT (Design For Testability), ATPG (Automatic Test Pattern Generation)Document10 pagesPost-Silicon SOC: Keywords: DFT (Design For Testability), ATPG (Automatic Test Pattern Generation)Amena FarhatNo ratings yet

- Scan Insertion FlowDocument9 pagesScan Insertion Flowsharath ANo ratings yet

- DFTDocument21 pagesDFTMuhsin Nk100% (1)

- Timing SimulationDocument3 pagesTiming SimulationKarthik Sharma100% (1)

- Why Boundary Scan Needed?Document39 pagesWhy Boundary Scan Needed?srikanth100% (1)

- Debugging Simulation MismatchesDocument4 pagesDebugging Simulation Mismatcheselectro123eNo ratings yet

- Why Masking Is Needed: Scan Chain Masking in The AcompactorDocument6 pagesWhy Masking Is Needed: Scan Chain Masking in The AcompactorIlaiyaveni IyanduraiNo ratings yet

- EDTDocument47 pagesEDTRaghavendra MatturNo ratings yet

- ATPGDocument54 pagesATPGsrikanth100% (1)

- Few Important QuestionsDocument7 pagesFew Important QuestionsShankhadeep DasNo ratings yet

- Scan PDFDocument49 pagesScan PDFferoz100% (1)

- Streaming Scan NetworkDocument51 pagesStreaming Scan NetworkVENKATRAMAN100% (1)

- Tracing CoverageDocument2 pagesTracing CoverageSrinath M S100% (1)

- Morequestion On DFTDocument4 pagesMorequestion On DFTsenthilkumar100% (1)

- DFT QuestionsDocument8 pagesDFT QuestionsNaga NitheshNo ratings yet

- Q-A's On ATPG & SCAN.Document21 pagesQ-A's On ATPG & SCAN.Hitesh Pradhan0% (1)

- Assignment Section-1 1. What Is DFT?Document18 pagesAssignment Section-1 1. What Is DFT?PAVAN KUMAR TAVADABOINA100% (1)

- Full and Fast SequentialDocument4 pagesFull and Fast SequentialdeepaNo ratings yet

- Assignment 1 Poovika.tDocument12 pagesAssignment 1 Poovika.tsenthilkumarNo ratings yet

- High Test CoverageDocument58 pagesHigh Test CoverageAdhi SuruliNo ratings yet

- Lab2 Block Level SSN Insertion On Processor CoreDocument33 pagesLab2 Block Level SSN Insertion On Processor Corezys WdNo ratings yet

- DFT (Design For Testability)Document21 pagesDFT (Design For Testability)lavanyaNo ratings yet

- ATPG Srivatsa PPTDocument37 pagesATPG Srivatsa PPTMayur Mestry100% (1)

- ATPG Tool FlowDocument12 pagesATPG Tool FlowAdhi SuruliNo ratings yet

- 10 Tips For Successful Scan Design Part OneDocument6 pages10 Tips For Successful Scan Design Part Onebesha1987No ratings yet

- Embedded Deterministic Test: by M. BalakrishnaDocument28 pagesEmbedded Deterministic Test: by M. Balakrishnasuryatejamula0% (1)

- Scan Insertion Lab Observations: Vlsiguru DFT TrainingDocument3 pagesScan Insertion Lab Observations: Vlsiguru DFT Trainingsenthilkumar100% (1)

- SCAN DRC Violation Solutions: Add - Cell - Models Report - DFT - CheckDocument3 pagesSCAN DRC Violation Solutions: Add - Cell - Models Report - DFT - CheckJayesh Popat100% (2)

- Design Clock Controllers For Hierarchical TestDocument2 pagesDesign Clock Controllers For Hierarchical Testneelalohith100% (1)

- MBISTDocument12 pagesMBISTChiranjeevi ChiruNo ratings yet

- Wrapper p1500Document8 pagesWrapper p1500srikanth100% (1)

- Debugging Low Test-Coverage SituationsDocument6 pagesDebugging Low Test-Coverage SituationsBrijesh S D100% (2)

- Scan Insertion Lab ObservationsDocument2 pagesScan Insertion Lab ObservationssenthilkumarNo ratings yet

- What Is DFT in VLSIDocument22 pagesWhat Is DFT in VLSINaga Nithesh100% (4)

- Named Capture ProcedureDocument2 pagesNamed Capture Proceduresenthilkumar50% (4)

- Atpg Lab Notes PDFDocument11 pagesAtpg Lab Notes PDFrajkumar gunja100% (1)

- Basic Interview Questions On DFTDocument5 pagesBasic Interview Questions On DFTHardik TrivediNo ratings yet

- History Rediscovered: Augmented Reality at Museums: By: Hannah WallisDocument12 pagesHistory Rediscovered: Augmented Reality at Museums: By: Hannah Wallisbharghav saiNo ratings yet

- The Ethics of Realism in Virtual and Augmented Reality: Opinion Published: 03 March 2020 Doi: 10.3389/frvir.2020.00001Document13 pagesThe Ethics of Realism in Virtual and Augmented Reality: Opinion Published: 03 March 2020 Doi: 10.3389/frvir.2020.00001bharghav saiNo ratings yet

- Dyslexia Alphabet Using Augmented RealityDocument46 pagesDyslexia Alphabet Using Augmented Realitybharghav saiNo ratings yet

- Grayscale Image Enhancement For Enhancing Features Detection in Marker-Less Augmented Reality TechnologyDocument14 pagesGrayscale Image Enhancement For Enhancing Features Detection in Marker-Less Augmented Reality Technologybharghav saiNo ratings yet

- Assessing Accuracy and Precision of 3D Augmented Reality Holographic Models Derived From DICOM DataDocument12 pagesAssessing Accuracy and Precision of 3D Augmented Reality Holographic Models Derived From DICOM Databharghav saiNo ratings yet

- Multipath Computation of Oading For Mobile Augmented RealityDocument11 pagesMultipath Computation of Oading For Mobile Augmented Realitybharghav saiNo ratings yet

- MARIN: An Open-Source Mobile Augmented Reality Interactive Neuronavigation SystemDocument16 pagesMARIN: An Open-Source Mobile Augmented Reality Interactive Neuronavigation Systembharghav saiNo ratings yet

- Use of Augmented Reality in Reconstructive Microsurgery: A Systematic Review and Development of The Augmented Reality Microsurgery ScoreDocument11 pagesUse of Augmented Reality in Reconstructive Microsurgery: A Systematic Review and Development of The Augmented Reality Microsurgery Scorebharghav saiNo ratings yet

- End-Of-life - Notice For 6500 Sup2Document16 pagesEnd-Of-life - Notice For 6500 Sup2Gazawino1No ratings yet

- Fybcom Sem-I Assignment - Unit - VDocument3 pagesFybcom Sem-I Assignment - Unit - VSufiyan MominNo ratings yet

- 3GTurboCharger Installer Update 3 RC11 Test 1.ShDocument13 pages3GTurboCharger Installer Update 3 RC11 Test 1.ShMoh. FakhrudinNo ratings yet

- Big Data Analytics and Business Process InnovationDocument9 pagesBig Data Analytics and Business Process InnovationAbdulGhaffarNo ratings yet

- p174 Wireless Application Pro To CalDocument9 pagesp174 Wireless Application Pro To Caljnanesh582No ratings yet

- SubNetting Practice LabDocument3 pagesSubNetting Practice LabOdoch HerbertNo ratings yet

- Irb 260Document2 pagesIrb 260ANDRENo ratings yet

- L6 - Information Systems SecurityDocument17 pagesL6 - Information Systems Securityhieubot1111No ratings yet

- Autodesk Ecotect Analysis 2011 Brochure PDFDocument4 pagesAutodesk Ecotect Analysis 2011 Brochure PDFGevionNo ratings yet

- Training Msi MS-5Document23 pagesTraining Msi MS-5adaofisicoNo ratings yet

- Applicant Form PDFDocument5 pagesApplicant Form PDFDaniela ManNo ratings yet

- Management Interface For SFP+: Published SFF-8472 Rev 12.4Document43 pagesManagement Interface For SFP+: Published SFF-8472 Rev 12.4Антон ЛузгинNo ratings yet

- Addl Guidelines Digital BillboardDocument7 pagesAddl Guidelines Digital BillboardrxNo ratings yet

- Tesco SS App Faq 22022020 PDFDocument2 pagesTesco SS App Faq 22022020 PDFairinNo ratings yet

- Harish - Resume QA PCSDocument5 pagesHarish - Resume QA PCSResumeGarageNo ratings yet

- Vip System Base I Processing SpecsDocument206 pagesVip System Base I Processing SpecsMohamed LahlouNo ratings yet

- Class 10 Number Systems Assignment 1Document5 pagesClass 10 Number Systems Assignment 1manojmathewNo ratings yet

- Management Information Systems 16e: Stuxnet and CyberwarfareDocument4 pagesManagement Information Systems 16e: Stuxnet and CyberwarfareBasit BandayNo ratings yet

- Unit 1 - Basic Instrumentation and Measurement Techniques PPT Notes Material For Sem II Uploaded by Navdeep RaghavDocument144 pagesUnit 1 - Basic Instrumentation and Measurement Techniques PPT Notes Material For Sem II Uploaded by Navdeep Raghavavikool1708No ratings yet

- 24051Document3 pages24051bhuvi2312100% (1)

- Variable and Verbal Expressions PDFDocument4 pagesVariable and Verbal Expressions PDFJudgementDay150No ratings yet

- Experiment-2: Quires Using Operators in SQLDocument6 pagesExperiment-2: Quires Using Operators in SQLPhani Kumar SolletiNo ratings yet

- Manual WM Security Routers V2.04 enDocument127 pagesManual WM Security Routers V2.04 enOscar TamayoNo ratings yet

- Tutorial 0 - Part B Modelling Groundwater Flow Using FreewatDocument50 pagesTutorial 0 - Part B Modelling Groundwater Flow Using FreewatУрошМилићNo ratings yet

- PeelDocument4 pagesPeelSaurabh Bansal100% (1)

- Afosi Exp22 Word Ch04 ML1 DesignDocument5 pagesAfosi Exp22 Word Ch04 ML1 Designw215019229No ratings yet

- Filter 777777Document35 pagesFilter 777777Mr BinNo ratings yet

- Design of A Hamming Neural Network BasedDocument9 pagesDesign of A Hamming Neural Network BasedPhạm Minh NhậtNo ratings yet

- Part A Entity Relationship ModelingDocument8 pagesPart A Entity Relationship Modelinghaha huhuNo ratings yet

- GC Buffer BusyDocument19 pagesGC Buffer BusySaeed MeethalNo ratings yet