Professional Documents

Culture Documents

YX Technologies Co.,LTD: YX Technology YX Technology YX Technology

YX Technologies Co.,LTD: YX Technology YX Technology YX Technology

Uploaded by

Gustavo DestruelOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

YX Technologies Co.,LTD: YX Technology YX Technology YX Technology

YX Technologies Co.,LTD: YX Technology YX Technology YX Technology

Uploaded by

Gustavo DestruelCopyright:

Available Formats

5 4 3 2 1

YX Confidential

D

YX technologies Co.,LTD D

Board name: Mother Board Schematic 1. System Block Diagram & Schematic page description;

2. Power Block Diagram & Discription;

Project name: N11

3. Annotations & information;

Version: VerA

4. Schematic modify Item and history;

Start Date:11 2,2014 5. Power on & off Sequence;

C 6. ACPI Mode Switch Timings; C

VerA Release Data:

7. Power On Sequence Map;

8. CLOCK Distribution;

B B

Hardware drawing by: Hardware check by: EMI Check by:

Power drawing by: Power check by:

A Manager Sign by: YX Technology A

ZhengWei

Title

<Title>

Size Project Name Rev

A4 N11 A

Date: Thursday, March 06, 2014 Sheet 1 of 30

5 4 3 2 1

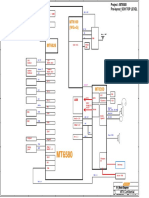

N11 System Block

D Mother Board D

DDR3L

256M X16/128M X16

X4

DDRIII

DDI1 PCIE X1 LAN Controller

TFT RTL8105E RJ45

DDI0 IO Board

HDMI SDIO

TF CARD

C C

BayTrail-M

SDIO1 SOC

eMMC R

I2S Audio Codec

ALC5642

SATA L

NGFF SLOTB

SSD HP Out JACK

SPI Mic In

USB2.0

USB

BIOS Port

LPC BUS

USB2.0

Camera

B B

SPI KB Ctrl & EC

NPCE791L USB2.0/3.0

USB Port

USB2.0 WIFI

EC Code

USB HUB AW-NU147SM

PS/2

KB Matrix

USB CONN

TouchPanel

LED

A A

Touch Pad Board YX Technology ZhengWei

Title

<Title>

Size Project Name Rev

A4 N11 A

Date: Thursday, March 06, 2014 Sheet 2 of 30

5 4 3 2 1

D D

C C

B B

A A

YX Technology ZhengWei

Title

<Title>

Size Project Name Rev

A3 N11 A

Date: Thursday, March 06, 2014 Sheet 3 of 30

5 4 3 2 1

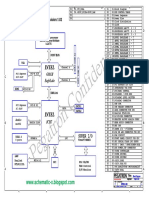

5 4 3 2 1

+V3.3S

+V3.3S {6,7,8,12,13,14,16,17,18,19,23,24,25,26,28,29,30}

+V1.05S

+V1.05S {8,23,24}

+V1.8S

+V1.8S {6,7,8,15,23,24,25,28,30}

+V1.5S

+V1.5S {8,23}

U1C

HDMI

DDI0_TXP0 AV3 AG3 +V1.8S

TMDS TX2 {28} DDI0_TXP0 Out DDI0_TXP_0 DDI1_TXP_0 Out DDI1_TXP0 {14}

DDI0_TXN0 AV2 AG1

{28} DDI0_TXN0 Out DDI0_TXN_0 DDI1_TXN_0 Out DDI1_TXN0 {14}

DDI0_TXP1 AT2 AF3

D TMDS TX1 {28} DDI0_TXP1 Out DDI0_TXP_1 DDI1_TXP_1 Out DDI1_TXP1 {14} D

DDI0_TXN1 AT3 AF2 R1 2.2K DDI0_DDC_SCL

{28} DDI0_TXN1 Out DDI0_TXN_1 DDI1_TXN_1 Out DDI1_TXN1 {14}

DDI0_TXP2 AR3 AD3 R2 2.2K DDI0_DDC_SDA

TMDS TX0 {28} DDI0_TXP2 Out DDI0_TXP_2 DDI1_TXP_2

DDI0_TXN2 AR1 AD2

{28} DDI0_TXN2 Out DDI0_TXN_2 DDI1_TXN_2

DDI0_TXP3 AP3 AC3

TMDS CLK {28} DDI0_TXP3 Out DDI0_TXP_3 DDI1_TXP_3

DDI0_TXN3 AP2 AC1

{28} DDI0_TXN3 Out DDI0_TXN_3 DDI1_TXN_3

AL3 AK3

DDI0_AUXP DDI1_AUXP Out DDI1_AUXP {14}

AL1 AK2

DDI0_AUXN DDI1_AUXN Out DDI1_AUXN {14}

DDI0_HPD D27 K30

{28} DDI0_HPD IN DDI0_HPD DDI1_HPD IN DDI1_HPD {14}

DDI0_DDC_SDA C26 P30 DDI1_DDC_SDA

{28} DDI0_DDC_SDA Out DDI0_DDCDATA DDI1_DDCDATA

DDI0_DDC_SCL C28 G30 DDI1_DDC_SCL

{28} DDI0_DDC_SCL Out DDI0_DDCCLK DDI1_DDCCLK TP3 ns

B28 N30

DDI0_VDDEN DDI1_VDDEN Out DDI1_VDDEN {14}

C27 J30

DDI0_BKLTEN DDI1_BKLTEN Out DDI1_BKLT_EN {14}

B26 M30

DDI0_BKLTCTL DDI1_BKLTCTL Out DDI1_BKLTCTL {14}

R3 402,1% AK13 AH14

AK12 DDI0_RCOMP RESERVED_AH14 AH13

AM14 DDI0_RCOMP_P RESERVED_AH13 AF14

AM13 RESERVED_AM14 RESERVED_AF14 AF13

AM3 RESERVED_AM13 RESERVED_AF13 AH3

AM2 RESERVED_VSS0 RESERVED_VSS2 AH2

RESERVED_VSS1 RESERVED_VSS3

BA3

VGA_RED AY2

VGA_BLUE BA1

C VGA_GREEN C

AW1

VGA_IREF AY3

VGA_IRTN

BD2

VGA_HSYNC BF2

VGA_VSYNC

BC1

VGA_DDCCLK BC2

VGA_DDCDATA

T2 T7

T3 RESERVED_T2 RESERVED_T7 T9

AB3 RESERVED_T3 RESERVED_T9 AB13

AB2 RESERVED_AB3 RESERVED_AB13 AB12

Y3 RESERVED_AB2 RESERVED_AB12 Y12

Y2 RESERVED_Y3 RESERVED_Y12 Y13

W3 RESERVED_Y2 RESERVED_Y13 V10

W1 RESERVED_W3 RESERVED_V10 V9

V2 RESERVED_W1 RESERVED_V9 T12

V3 RESERVED_V2 RESERVED_T12 T10

R3 RESERVED_V3 RESERVED_T10 V14

R1 RESERVED_R3 RESERVED_V14 V13

AD6 RESERVED_R1 RESERVED_V13 T14

AD4 RESERVED_AD6 RESERVED_T14 T13

AB9 RESERVED_AD4 RESERVED_T13 T6

AB7 RESERVED_AB9 RESERVED_T6 T4

Y4 RESERVED_AB7 RESERVED_T4 P14

Y6 RESERVED_Y4 RESERVED_P14

V4 RESERVED_Y6

V6 RESERVED_V4 K34

B B

GPIO_NC13 A29 RESERVED_V6 RESERVED_K34 D32

C29 RESERVED_A29 RESERVED_D32 N32

ns TP4 RESERVED_C29 RESERVED_N32

AB14 J34

B30 RESERVED_AB14 RESERVED_J34 K28

ns TP5 GPIO_S0_NC12 RESERVED_K28

C30 F28

RESERVED_C30 RESERVED_F28 F32

RESERVED_F32 D34

RESERVED_D34 J28

RESERVED_J28 D28

RESERVED_D28 M32

RESERVED_M32 F34

RESERVED_F34

+V1.8S VLV_M_D

R4

R5 R6 R7 R8

1K

10K 10K 10K 10K

ns ns

GPIO_NC13

GPIO_S0_SC_56 {6}

I2S_2_FRM {6,15}

I2S_2_DOUT {6,15}

DDI1_DDC_SDA

A R9 R10 R11 R12 A

10K 10K 10K 10K

ns ns

ns

YX Technology ZhengWei

Title

<Title>

Size Project Name Rev

A3 N11 A

Date: Thursday, March 06, 2014 Sheet 4 of 30

5 4 3 2 1

5 4 3 2 1

+V3.3AUX {7,8,13,14,16,17,18,20,21,22,23,24,25,26}

+V_DDR {8,10,22,23,24}

U1A

M_A_A[15:0]

{10} M_A_A[15:0]

M_A_A0 K45 M36 M_A_DQ0

M_A_A1 H47 DRAM0_MA_00 DRAM0_DQ_00 J36 M_A_DQ1

M_A_A2 L41 DRAM0_MA_11 DRAM0_DQ_11 P40 M_A_DQ2

M_A_A3 H44 DRAM0_MA_22 DRAM0_DQ_22 M40 M_A_DQ3

M_A_A4 H50 DRAM0_MA_33 DRAM0_DQ_33 P36 M_A_DQ4

M_A_A5 G53 DRAM0_MA_44 DRAM0_DQ_44 N36 M_A_DQ5 M_A_DQS[7:0]

DRAM0_MA_55 DRAM0_DQ_55 M_A_DQS[7:0] {10}

M_A_A6 H49 K40 M_A_DQ6

M_A_A7 D50 DRAM0_MA_66 DRAM0_DQ_66 K42 M_A_DQ7 M_A_DQS#[7:0]

DRAM0_MA_77 DRAM0_DQ_77 M_A_DQS#[7:0] {10}

D M_A_A8 G52 B32 M_A_DQ8 D

M_A_A9 E52 DRAM0_MA_88 DRAM0_DQ_88 C32 M_A_DQ9 M_A_DM[7:0]

DRAM0_MA_99 DRAM0_DQ09_C32 M_A_DM[7:0] {10}

M_A_A10 K48 C36 M_A_DQ10

M_A_A11 E51 DRAM0_MA_1010 DRAM0_DQ_1010 A37 M_A_DQ11 M_A_DQ[63:0]

DRAM0_MA_1111 DRAM0_DQ_1111 M_A_DQ[63:0] {10}

M_A_A12 F47 C33 M_A_DQ12

M_A_A13 J51 DRAM0_MA_1212 DRAM0_DQ_1212 A33 M_A_DQ13 U1B

M_A_A14 B49 DRAM0_MA_1313 DRAM0_DQ_1313 C37 M_A_DQ14

M_A_A15 B50 DRAM0_MA_1414 DRAM0_DQ_1414 B38 M_A_DQ15 AY45 BG38

DRAM0_MA_1515 DRAM0_DQ_1515 F36 M_A_DQ16 BB47 DRAM1_MA_00 DRAM1_DQ_00 BC40

M_A_DM0 G36 DRAM0_DQ_1616 G38 M_A_DQ17 AW41 DRAM1_MA_11 DRAM1_DQ_11 BA42

M_A_DM1 B36 DRAM0_DM_00 DRAM0_DQ_1717 F42 M_A_DQ18 BB44 DRAM1_MA_22 DRAM1_DQ_22 BD42

M_A_DM2 F38 DRAM0_DM_11 DRAM0_DQ_1818 J42 M_A_DQ19 BB50 DRAM1_MA_33 DRAM1_DQ_33 BC38

M_A_DM3 B42 DRAM0_DM_22 DRAM0_DQ_1919 G40 M_A_DQ20 BC53 DRAM1_MA_44 DRAM1_DQ_44 BD36

M_A_DM4 P51 DRAM0_DM_33 DRAM0_DQ_2020 C38 M_A_DQ21 BB49 DRAM1_MA_55 DRAM1_DQ_55 BF42

M_A_DM5 V42 DRAM0_DM_44 DRAM0_DQ_2121 G44 M_A_DQ22 BF50 DRAM1_MA_66 DRAM1_DQ_66 BC44

M_A_DM6 Y50 DRAM0_DM_55 DRAM0_DQ_2222 D42 M_A_DQ23 BC52 DRAM1_MA_77 DRAM1_DQ_77 BH32

M_A_DM7 Y52 DRAM0_DM_66 DRAM0_DQ_2323 A41 M_A_DQ24 BE52 DRAM1_MA_88 DRAM1_DQ_88 BG32

DRAM0_DM_77 DRAM0_DQ_2424 C41 M_A_DQ25 AY48 DRAM1_MA_99 DRAM1_DQ_99 BG36

M45 DRAM0_DQ_2525 A45 M_A_DQ26 BE51 DRAM1_MA_1010 DRAM1_DQ_1010 BJ37

{10} M_A_RAS# Out

M44 DRAM0_RAS DRAM0_DQ_2626 B46 BD47 DRAM1_MA_1111 DRAM1_DQ_1111 BG33

M_A_DQ27

{10} M_A_CAS# Out

H51 DRAM0_CAS DRAM0_DQ_2727 C40 BA51 DRAM1_MA_1212 DRAM1_DQ_1212 BJ33

M_A_DQ28

{10} M_A_WE# Out DRAM0_WE DRAM0_DQ_2828 B40 BH49 DRAM1_MA_1313 DRAM1_DQ_1313 BG37

M_A_DQ29

K47 DRAM0_DQ_2929 B48 M_A_DQ30 BH50 DRAM1_MA_1414 DRAM1_DQ_1414 BH38

{10} M_A_BS0 Out

K44 DRAM0_BS_00 DRAM0_DQ_3030 B47 M_A_DQ31 DRAM1_MA_1515 DRAM1_DQ_1515 AU36

{10} M_A_BS1 Out

D52 DRAM0_BS_11 DRAM0_DQ_3131 K52 BD38 DRAM1_DQ_1616 AT36

M_A_DQ32

{10} M_A_BS2 Out DRAM0_BS_22 DRAM0_DQ_3232 K51 BH36 DRAM1_DM_00 DRAM1_DQ_1717 AV40

M_A_DQ33

P44 DRAM0_DQ_3333 T52 M_A_DQ34 BC36 DRAM1_DM_11 DRAM1_DQ_1818 AT40

{10} M_CS#0 Out DRAM0_CS_0 DRAM0_DQ_3434 T51 BH42 DRAM1_DM_22 DRAM1_DQ_1919 BA36

M_A_DQ35

P45 DRAM0_DQ_3535 L51 M_A_DQ36 AT51 DRAM1_DM_33 DRAM1_DQ_2020 AV36

M_CS#1 Out DRAM0_CS_2 DRAM0_DQ_3636 L53 AM42 DRAM1_DM_44 DRAM1_DQ_2121 AY42

M_A_DQ37

ns TP14 DRAM0_DQ_3737 R51 M_A_DQ38 AK50 DRAM1_DM_55 DRAM1_DQ_2222 AY40

C47 DRAM0_DQ_3838 R53 M_A_DQ39 AK52 DRAM1_DM_66 DRAM1_DQ_2323 BJ41

{10} M_CKE0 Out

D48 DRAM0_CKE_00 DRAM0_DQ_3939 T47 DRAM1_DM_77 DRAM1_DQ_2424 BG41

M_A_DQ40

F44 RESERVED_D48 DRAM0_DQ_4040 T45 M_A_DQ41 AV45 DRAM1_DQ_2525 BJ45

M_CKE1 Out

E46 DRAM0_CKE_22 DRAM0_DQ_4141 Y40 AV44 DRAM1_RAS DRAM1_DQ_2626 BH46

M_A_DQ42

ns TP52 RESERVED_E46 DRAM0_DQ_4242 V41 BB51 DRAM1_CAS DRAM1_DQ_2727 BG40

M_A_DQ43

T41 DRAM0_DQ_4343 T48 M_A_DQ44 DRAM1_WE DRAM1_DQ_2828 BH40

{10} M_ODT0 Out DRAM0_ODT_0 DRAM0_DQ_4444 T50 AY47 DRAM1_DQ_2929 BH48

M_A_DQ45

P42 DRAM0_DQ_4545 Y42 M_A_DQ46 AY44 DRAM1_BS_00 DRAM1_DQ_3030 BH47

M_ODT1 Out DRAM0_ODT_2 DRAM0_DQ_4646 AB40 M_A_DQ47 BF52 DRAM1_BS_11 DRAM1_DQ_3131 AY52

DRAM0_DQ_4747 V45 M_A_DQ48 DRAM1_BS_22 DRAM1_DQ_3232 AY51

M50 DRAM0_DQ_4848 V47 M_A_DQ49 AT44 DRAM1_DQ_3333 AP52

C C

{10,11} M_CLK_DDR0 Out

M48 DRAM0_CKP_0 DRAM0_DQ_4949 AD48 DRAM1_CS_0 DRAM1_DQ_3434 AP51

M_A_DQ50

{10,11} M_CLK_DDR0# Out DRAM0_CKN_0 DRAM0_DQ_5050 AD50 AT45 DRAM1_DQ_3535 AW51

M_A_DQ51

DRAM0_DQ_5151 V48 M_A_DQ52 DRAM1_CS_2 DRAM1_DQ_3636 AW53

P50 DRAM0_DQ_5252 V50 M_A_DQ53 DRAM1_DQ_3737 AR51

M_CLK_DDR1 Out

P48 DRAM0_CKP_2 DRAM0_DQ_5353 AB44 M_A_DQ54 BG47 DRAM1_DQ_3838 AR53

M_CLK_DDR1# Out DRAM0_CKN_2 DRAM0_DQ_5454 Y45 M_A_DQ55 BE46 DRAM1_CKE_00 DRAM1_DQ_3939 AP47

DRAM0_DQ_5555 V52 M_A_DQ56 BD44 RESERVED_BE46 DRAM1_DQ_4040 AP45

DRAM0_DQ_5656 W51 M_A_DQ57 BF48 DRAM1_CKE_22 DRAM1_DQ_4141 AK40

R14 0 DRAMRST# P41 DRAM0_DQ_5757 AC53 M_A_DQ58 RESERVED_BF48 DRAM1_DQ_4242 AM41

{10} DDR3_DRAMRST# Out DRAM0_DRAMRST DRAM0_DQ_5858 AC51 AP41 DRAM1_DQ_4343 AP48

M_A_DQ59

DRAM0_DQ_5959 W53 M_A_DQ60 DRAM1_ODT_0 DRAM1_DQ_4444 AP50

DRAM0_DQ_6060 Y51 M_A_DQ61 AT42 DRAM1_DQ_4545 AK42

MCH_VREF AF44 DRAM0_DQ_6161 AD52 M_A_DQ62 DRAM1_ODT_2 DRAM1_DQ_4646 AH40

DRAM_VREF DRAM0_DQ_6262 AD51 M_A_DQ63 DRAM1_DQ_4747 AM45

DRAM0_DQ_6363 AV50 DRAM1_DQ_4848 AM47

J38 M_A_DQS0 AV48 DRAM1_CKP_0 DRAM1_DQ_4949 AF48

R15 100K AH42 DRAM0_DQSP_00 K38 M_A_DQS#0 DRAM1_CKN_0 DRAM1_DQ_5050 AF50

R16 100K AF42 ICLK_DRAM_TERM_1 DRAM0_DQSN_00 C35 M_A_DQS1 DRAM1_DQ_5151 AM48

ICLK_DRAM_TERMN_AF42 DRAM0_DQSP_11 B34 M_A_DQS#1 DRAM1_DQ_5252 AM50

DRAM0_DQSN_11 D40 M_A_DQS2 AT50 DRAM1_DQ_5353 AH44

DDR3_DRAM_PWROK AD42 DRAM0_DQSP_22 F40 M_A_DQS#2 AT48 DRAM1_CKP_2 DRAM1_DQ_5454 AK45

{10} DRAM_PWROK IN

AB42 DRAM_VDD_S4_PWROK DRAM0_DQSN_22 B44 DRAM1_CKN_2 DRAM1_DQ_5555 AM52

DDR3_VCCA_PWROK M_A_DQS3

DRAM_CORE_PWROK DRAM0_DQSP_33 C43 M_A_DQS#3 DRAM1_DQ_5656 AL51

DRAM0_DQSN_33 N53 M_A_DQS4 DRAM1_DQ_5757 AG53

DDR3_RCOMP_0 AD44 DRAM0_DQSP_44 M52 M_A_DQS#4 AT41 DRAM1_DQ_5858 AG51

DDR3_RCOMP_1 AF45 DRAM_RCOMP_00 DRAM0_DQSN_44 T42 M_A_DQS5 DRAM1_DRAMRST DRAM1_DQ_5959 AL53

DDR3_RCOMP_2 AD45 DRAM_RCOMP_11 DRAM0_DQSP_55 T44 M_A_DQS#5 DRAM1_DQ_6060 AK51

DRAM_RCOMP_22 DRAM0_DQSN_55 Y47 M_A_DQS6 DRAM1_DQ_6161 AF52

DRAM0_DQSP_66 Y48 M_A_DQS#6 DRAM1_DQ_6262 AF51

AF40 DRAM0_DQSN_66 AB52 M_A_DQS7 DRAM1_DQ_6363

AF41 RESERVED_AF40 DRAM0_DQSP_77 AA51 M_A_DQS#7 BF40

AD40 RESERVED_AF41 DRAM0_DQSN_77 DRAM1_DQSP_00 BD40

AD41 RESERVED_AD40 DRAM1_DQSN_00 BG35

RESERVED_AD41 DRAM1_DQSP_11 BH34

+V_DDR DRAM1_DQSN_11 BA38

DRAM1_DQSP_22 AY38

VLV_M_D DRAM1_DQSN_22 BH44

DRAM1_DQSP_33 BG43

R17 DRAM1_DQSN_33 AU53

4.7K,1% DRAM1_DQSP_44 AV52

B DRAM1_DQSN_44 AP42 B

MCH_VREF DRAM1_DQSP_55 AP44

DRAM1_DQSN_55 AK47

DRAM1_DQSP_66 AK48

0.1uF/16V,X7R

DDR3_RCOMP_0 R19 23.2,1% DRAM1_DQSN_66 AH52

DRAM1_DQSP_77

C2

R18 DDR3_RCOMP_1 R20 29.4,1% AJ51

4.7K,1% DDR3_RCOMP_2 R21 162,1% DRAM1_DQSN_77

VLV_M_D

{14,18,25} DELAY_ALL_PWROK IN

R26

10K,1%

DDR3_VCCA_PWROK

R27

6.19K,1%

A A

YX Technology ZhengWei

Title

<Title>

Size Project Name Rev

A2 N11 A

Date: Thursday, March 06, 2014 Sheet 5 of 30

5 4 3 2 1

5 4 3 2 1

SATA_RCOMP_DP +V3.3S

+V5S +V3.3S {7,8,12,13,14,16,17,18,19,23,24,25,26,28,29,30}

+V5S {14,15,16,17,18,24,26,28}

R36 +V3.3AUX

+V1.05S +V3.3AUX {7,8,13,14,16,17,18,20,21,22,23,24,25,26}

+V1.05S {8,23,24}

+V1.5S

402,1% U1D +V1.5S {8,23}

SATA_RCOMP_DN +V1.8AUX {7,8,21}

0.01uF/25V,X7R C5 BF6 AY7 C6 0.1uF/16V,X7R +V1.0S {8,23,24,25,26}

{19} SATA_TXP0 BG7 SATA_TXP_0 PCIE_TXP_0 AY6 PCIE_TXP1_LAN {13}

0.01uF/25V,X7R C3 C7 0.1uF/16V,X7R +V1.8S {4,7,8,15,23,24,25,28,30}

{19} SATA_TXN0 SATA_TXN_0 PCIE_TXN_0 PCIE_TXN1_LAN {13}

+V1.8S

SATA_RXP0 AU16 AT14

{19} SATA_RXP0 AV16 SATA_RXP_0 PCIE_RXP_0 AT13 PCIE_RXP1_LAN {13}

SATA_RXN0

{19} SATA_RXN0 SATA_RXN_0 PCIE_RXN_0 PCIE_RXN1_LAN {13}

BD10 AV6

R28 BF10 SATA_TXP1 PCIE_TXP_1 AV4

10K SATA_TXN_1 PCIE_TXN_1

AY16 AT10

BA16 SATA_RXP_1 PCIE_RXP_1 AT9

SATA_RXN_1 PCIE_RXN_1

D BB10 AT7 D

RESERVED_VSS4 PCIE_TXP_2 PCIE_RCOMP_DP

BC10 AT6

SATA_LED#_R RESERVED_VSS5 PCIE_TXN_2

1.8V

BA12 AP12 R40

{7} SOC_SCI# AY14 SATA_GP0 PCIE_RXP_2 AP10

ns TP6 AY12 SATA_GP1 PCIE_RXN_2

SATA_LED#_R 402,1%

{16} SATA_LED# SATA_LED AP6 PCIE_RCOMP_DN

SATA_RCOMP_DP AU18 PCIE_TXP_3 AP4 +V1.8S

SATA_RCOMP_DN AT18 SATA_RCOMP_P_AU18 PCIE_TXN_3

SATA_RCOMP_N_AT18 AP9

PCIE_RXP_3 AP7

AT22 PCIE_RXN_3 R31 R32 R33 R34

EMMC_CLK

{30} EMMC_CLK MMC1_CLK BB5 R41

0 R30

AV20 RESERVED_VSS6 BB7 100K U1F

EMMC_DATA_0 0 R35

{30} EMMC_DATA_0 AU22 MMC1_D0 RESERVED_VSS7 10K 10K 10K 10K ns

EMMC_DATA_1 G2 M10

{30} EMMC_DATA_1 AV22 MMC1_D1 BG3

EMMC_DATA_2 GPIO_S5_31 RESERVED_M10

{30} EMMC_DATA_2 MMC1_D2 PCIE_CLKREQ_0 LAN_CLKREQ# {13} M9

EMMC_DATA_3 AT20 BD7 RESERVED_M9

{30} EMMC_DATA_3 AY24 MMC1_D3 PCIE_CLKREQ_1 BG5 MINICARD_CLKREQ#

EMMC_DATA_4

{30} EMMC_DATA_4 MMC1_D4 PCIE_CLKREQ_2 P7

EMMC_DATA_5 AU26 BE3 M3 RESERVED_P7

{30} EMMC_DATA_5 MMC1_D5 PCIE_CLKREQ_3 GPIO_S5_32 P6

EMMC_DATA_6 AT26 BD5 SD3_WP L1 RESERVED_P6

{30} EMMC_DATA_6 AU20 MMC1_D6 SD3_WP_BD5 K2 GPIO_S5_33

EMMC_DATA_7

{30} EMMC_DATA_7 MMC1_D7 AP14 PCIE_RCOMP_DP K3 GPIO_S5_34

PCIE_RCOMP_P_AP14_AP14 GPIO_S5_35 M7 1.24K,1% R42

EMMC_CMD AV26 AP13 PCIE_RCOMP_DN M2 RESERVED_M7

{30} EMMC_CMD MMC1_CMD PCIE_RCOMP_N_AP13_AP13 GPIO_S5_36 M12 1.24K,1% R37

EMMC_RESET BA24 N3 USB3_REXT0

{30} EMMC_RESET MMC1_RST BB4 P2 GPIO_S5_37

RESERVED_BB4 GPIO_S5_38 P10

R38 49.9,1% AY18 BB3 L3 RESERVED_P10

MMC1_RCOMP RESERVED_BB3 GPIO_S5_39 P12

AV10 RESERVED_P12

RESERVED_AV10 AV9

RESERVED_AV9 M4

BA18 RESERVED_M4

SD2_CLK M6

AY20 J3 RESERVED_M6

BD20 SD2_D0 BF20 49.9,1% R39 P3 GPIO_S5_40

SD2_D1 HDA_LPE_RCOMP GPIO_S5_41 D4

BA20 BG22 I2S_0_CLK H3 USB3_RXP0 USB3_RXP0 {17}

SD2_D2 HDA_RST I2S_0_CLK {15} GPIO_S5_42 E3

BD18 BH20 I2S_0_FS B12 USB3_RXN0 USB3_RXN0 {17}

BC18 SD2_D3_CD HDA_SYNC BJ21 I2S_0_FS {15} GPIO_S5_43

I2S_0_TXD

SD2_CMD HDA_CLK I2S_0_TXD {15} K6

BG20 I2S_0_RXD USB3_TXP0 USB3_TXP0 {17}

HDA_SDO I2S_0_RXD {15} K7

BG19 M16 USB3_TXN0 USB3_TXN0 {17}

HDA_SDI0 TP17 ns {17} USB_PP0 USB_DP0

BG21 K16

AY26 HDA_SDI1 BH18 {17} USB_PN0 USB_DN0

{29} SD3_CLK AT28 SD3_CLK GPIO_S0_SC_14 BG18 J14

{29} SD3_D0 BD26 SD3_D0 GPIO_S0_SC_15 {17} USB_PP1 G14 USB_DP1

{29} SD3_D1 AU28 SD3_D1 BF28 {17} USB_PN1 USB_DN1

I2S_2_CLK

C {29} SD3_D2 SD3_D2 LPE_I2S2_CLK I2S_2_CLK {15} C

BA26 BA30 K12

{29} SD3_D3 BC24 SD3_D3 LPE_I2S2_FRM BC30 I2S_2_FRM {4,15} {14} USB_PP2 J12 USB_DP2

{29} SD3_CD# AV28 SD3_CD# LPE_I2S2_DATAOUT BD28 I2S_2_DOUT {4,15} {14} USB_PN2 USB_DN2

I2S_2_RXD

{29} SD3_CMD SD3_CMD LPE_I2S2_DATAIN I2S_2_RXD {15} H8

BF22 K10 RESERVED_H8

ns TP38 SD3_1P8EN {12} USB_PP3 USB_DP3 H7

BD22 P34 H10 RESERVED_H7

{29} SD3_PWREN# SD3_PWREN RESERVED_P34 {12} USB_PN3 USB_DN3

N34

R45 49.9,1% BF26 RESERVED_N34

SD3_RCOMP H5

AK9 R46 1K,1% D10 RESERVED_H5

RESERVED_AK9 ICLK_USB_TERM_1 H4

AK7 R47 1K,1% F10 RESERVED_H4

RESERVED_AK7 ICLK_USB_TERMN

SD3_WP

{29} SD3_WP C24 PROCHOT# R48

PROCHOT +V1.0S

75 USB_OC# C20

USB_OC0# B20 USB_OC_00

USB_OC_11

VLV_M_D H_PROCHOT# {26} +V1.8AUX

BD12 CODEC_RESET_N

D6 GPIO_S0_SC_55 CODEC_RESET_N {15}

USB_RCOMPO BC12

USB_OC# R49 10K R50 45.3,1% C7 GPIO_S0_SC_56 GPIO_S0_SC_56 {4}

USB_RCOMPI BD14 UART3_DEBUG_TXD

GPIO_S0_SC_57 BC14 TP67 ns

GPIO_S0_SC_58 BF14 TOUCH_ENABLE

USB_OC0# R51 10K R59 0 ns M13 GPIO_S0_SC_59 TP68 ns

USB_PLL_MON BD16 TOUCH_RESET_N

GPIO_S0_SC_60 BC16 TP69 ns

UART3_DEBUG_RXD

GPIO_S0_SC_61 TP70 ns

B4

USB_HSIC0_DATA BH12 TOUCH_INT_N

B5 ILB_8254_SPKR TP39 ns

USB_HSIC0_STROBE

E2

D2 USB_HSIC1_DATA

USB_HSIC1_STROBE BH22

SIO_I2C0_DATA BG23

SIO_I2C0_CLK

R57 45.3,1% A7

USB_HSIC_RCOMP

BG24 I2C_CODEC_SDA

SIO_I2C1_DATA BH24 I2C_CODEC_SCL I2C_CODEC_SDA {15}

SIO_I2C1_CLK I2C_CODEC_SCL {15}

R58 49.9,1% BF18

BH16 LPC_RCOMP

{16,18} LPC_AD0 IN ILB_LPC_AD_00 BG25

BJ17 SIO_I2C2_DATA

{16,18} LPC_AD1 IN ILB_LPC_AD_11 BJ25

BJ13 SIO_I2C2_CLK

{16,18} LPC_AD2 IN ILB_LPC_AD_22

B

BG14 B

{16,18} LPC_AD3 IN

BG17 ILB_LPC_AD_33

{16,18} LPC_FRAME# Out ILB_LPC_FRAME BG26

BG15 SIO_I2C3_DATA

{16,18} PCICLK_KBC ILB_LPC_CLK_00 BH26

BH14 SIO_I2C3_CLK

{13} CLK_25M_LPC BG16 ILB_LPC_CLK_11

{18} PM_CLKRUN# IN ILB_LPC_CLKRUN

SERIRQ_V18 BG13

ILB_LPC_SERIRQ BF27

SIO_I2C4_DATA BG27

SIO_I2C4_CLK

BH28 I2C_TOUCH_SDA

SMB_DATA_A BG12 SIO_I2C5_DATA BG28 I2C_TOUCH_SCL TP71 ns

ns TP42 BH10 PCU_SMB_DATA SIO_I2C5_CLK TP72 ns

SMB_CLK_A

ns TP43 BG11 PCU_SMB_CLK

SMB_ALERT#

ns TP44 PCU_SMB_ALERT BJ29

SIO_I2C6_DATA BG29

SIO_I2C6_CLK

BH30

GPIO_S0_SC_092 BG30

GPIO_S0_SC_093

VLV_M_D

+V1.8S +V3.3S

+V1.8S

+V3.3S

C17

R90

1

0.1uF/16V,X7R Q81

10K

ns ns

C18 2 3

UART3_DEBUG_TXD

1

R88 U4 0.1uF/16V,X7R TX1 ns

10K TPC60

VCCA

VCCB

5 BSS138

SERIRQ_V18 3 OE 4

GND

A B SERIRQ {16,18}

R97 33

A A

2

+V1.8S +V3.3S

R95

1

TXB0101DCK 10K

Q82

SC70_6 ns ns

UART3_DEBUG_RXD 2 3

RX1 ns

TPC60

BSS138

YX Technology ZhengWei

R96 33 Title

<Title>

GND1 ns Size Project Name Rev

TPC60 A2 N11 A

Date: Thursday, March 06, 2014 Sheet 6 of 30

5 4 3 2 1

5 4 3 2 1

+V1.05S

+V1.05S {8,23,24}

+V3.3S

+V3.3AUX +V3.3S {6,8,12,13,14,16,17,18,19,23,24,25,26,28,29,30}

+V3.3AUX {8,13,14,16,17,18,20,21,22,23,24,25,26}

+V3.3A_RTC

+V3.3A_RTC {8}

+V1.8AUX {6,8,21}

+V1.8S {4,6,8,15,23,24,25,28,30}

U1E

AH12 AU34

Y1 AH10 ICLK_OSCIN SIO_UART1_RXD AV34

ICLK_OSCOUT SIO_UART1_TXD BA34

+V1.8AUX 4 25MHz,20pF

3 AD9 SIO_UART1_RTS AY34

RESERVED_AD9 SIO_UART1_CTS

1 2 R61 4.02K,1% AD14 BF34

D R62 47.5,1% AD13 ICLK_ICOMP SIO_UART2_RXD BD34 D

X4S32X25 ICLK_RCOMP SIO_UART2_TXD

Y2 BD32

H_TDI R63 4 3 AD10 SIO_UART2_RTS BF32

51 AD12 RESERVED_AD10 SIO_UART2_CTS

H_TMS R60 1 2 RESERVED_AD12 T4 ns

51 AF6 +V1.8AUX

25MHz,20pF {13} CLK_PCIE_LAN# PCIE_CLKN_00

H_TDO R64 AF4 D26 SUSPWRDNACK

X4S50X32 {13} CLK_PCIE_LAN PCIE_CLKP_00 PMC_SUSPWRDNACK

51 G24 SUSCLK

R65 1M AF9 PMC_SUSCLK0_G24 F18

Out SUSCLK {18}

AF7 PCIE_CLKN_11 PMC_SLP_S0IX F22 T5 ns

C9 ns C10 PCIE_CLKP_11 PMC_SLP_S4 D22

Out PM_SLP_S4#_V18 {7}

H_TCK R66

22pF/50V,NPO PMC_SLP_S3 J20

Out PM_SLP_S3#_V18 {7}

51 PCIE_WAKE#_V18

22pF/50V,NPO AK4 GPIO_S5_14 D20 T6 ns R68 10K

H_TRST# R67 PM_ACPRESENT_V18

AK6 PCIE_CLKN_22 PMC_ACPRESENT F26 PM_BATLOW#_V18 R69 10K

51 PCIE_WAKE#_V18 R444 0 ns

PCIE_CLKP_22 PMC_WAKE_PCIE_0 IN PCIE_WAKE# {13} SUSPWRDNACK R200 10K

K26 PM_BATLOW#_V18

PMC_BATLOW PM_ACPRESENT_V18 R438 10K

Design Note: AM4 J26

Place TCK/TDI/TMS PCIE_CLKN_33 PMC_PWRBTN IN PM_PWRBTN#_V18 {7}

AM6 BG9 RST_BTN# +V1.8S

termination near CPU PCIE_CLKP_33 PMC_RSTBTN F20 PLTRST#_V18

AM10 PMC_PLTRST J24

AM9 RESERVED_AM10 GPIO_S5_17 G18 T13 ns

RESERVED_AM9 PMC_SUS_STAT T12 ns R70

100K,1%

RST_BTN# R483 10K

C11 RTC_TEST_N

BH7 ILB_RTC_TEST

{13} CLK_25M BH5 PMC_PLT_CLK_00

ns TP27 PMC_PLT_CLK_11

I2S_IRQ_N BH4

{15} I2S_IRQ_N PLT_CLK3_I2SMCLK BH8 PMC_PLT_CLK_22 B10

{15} PLT_CLK3_I2SMCLK BH6 PMC_PLT_CLK_33 PMC_RSMRST B7

IN PM_RSMRST# {18,21}

BJ9 PMC_PLT_CLK_44 PMC_CORE_PWROK IN PM_ALL_PWROK {25}

RTC_RST# C12 PMC_PLT_CLK_55 C11

ILB_RTC_RST C9 RTC_X1

H_TCK D14 ILB_RTC_X1 A9 RTC_X2

ns TP7 G12 TAP_TCK ILB_RTC_X2 B8

H_TRST#

ns TP8 TAP_TRST ILB_RTC_EXTPAD

3

H_TMS F14 C12 0.1uF/16V,X7R 15pF/50V,NPO

ns TP9 F12 TAP_TMS

H_TDI R71 Y3

ns TP10 TAP_TDI

H_TDO G16 10M 32.768kHz,10ppm,12.5pF

ns TP11 D18 TAP_TDO

ns TP12 X4S67X15

2

F16 TAP_PRDY B24 R72 20,1%

ns TP13 AT34 TAP_PREQ SVID_ALERT A25 VR_SVID_ALERT# {26} C13

R73 16.9,1%

RESERVED SVID_DATA C25 R74 20,1% VR_SVID_DATA {26}

C

SPICS# C23 SVID_CLK VR_SVID_CLK {26} C

C21 PCU_SPI_CS_00 15pF/50V,NPO

SPIMISO R75 33 B22 PCU_SPI_CS_11 AU32

SPIMOSI R76 33 A21 PCU_SPI_MISO SIO_PWM_00 AT32

SPICLK_N C22 PCU_SPI_MOSI SIO_PWM_11

+V1.8AUX PCU_SPI_CLK

+V1.8AUX R487 10K SOC_WAKE_SCI_N B18

R484 10K GPIO_S5_1 B16 GPIO_S5_0 K24

R485 10K GPIO_S5_2 C18 GPIO_S5_1 GPIO_S5_22 N24

R486 10K GPIO_S5_3 A17 GPIO_S5_2 GPIO_S5_23 M20

C17 GPIO_S5_3 GPIO_S5_24 J18

C14 C16 GPIO_S5_4 GPIO_S5_25 M18

R77 R78 R79 0.1uF/16V,X7R B14 GPIO_S5_5 GPIO_S5_26 K18

10K 10K 10K U2 R80 R81 R488 10K SOC_SMI#_V18 C15 GPIO_S5_6 GPIO_S5_27 K20

ns W25Q64DWSSIG 10K 10K GPIO_S5_7 GPIO_S5_28 M22

1.8V GPIO_S5_29

SOP8_1P27_5P3 ns M24

SPICS# 1 8 GPIO_S5_30

SPIMISO 2 CE# VDD 7 HOLD#_N C13

WP#_N 3 SO HOLD# 6 SPICLK_N A13 GPIO_S5_8

4 WP# SCK 5 SPIMOSI C19 GPIO_S5_9 AV32

VSS SI GPIO_S5_10 SIO_SPI_CS BA28

SIO_SPI_MISO AY28

N26 SIO_SPI_MOSI AY30

GPIO_RCOMP SIO_SPI_CLK

U3 +V1.8AUX R84

VLV_M_D

SST25LF040A 49.9,1%

SOIC8_1P27_3P9

SPICS# 1 8

SPIMISO 2 CE# VDD 7 HOLD#_N

WP#_N 3 SO HOLD# 6 SPICLK_N +V1.8S +V3.3S

4 WP# SCK 5 SPIMOSI

VSS SI

ns R454

1

2.2K

+V1.8S

PLTRST#_V18 2 3

PLTRST# {12,13,16,18}

B B

R501 Q75

10K BSS138

1

+V1.8AUX

+V3.3AUX

2 3

{6} SOC_SCI# IN SCI# {18}

Q74 R456

1

BSS138 2.2K

2 3

{7} PM_SLP_S4#_V18 Out PM_SLP_S4# {18}

D1

+V3.3AUX BAT54C +V3.3A_RTC

+V1.8AUX

SOT23 Q77

BSS138

2

+V1.8AUX

+V3.3AUX

3 20K R86 RTC_RST#

R459

1

1 10K

C15 ns

C16 CLRCMOS1

1uF/10V,X5R JOPEN 2 3 R457

1

1uF/10V,X5R {7} PM_PWRBTN#_V18 IN PM_PWRBTN# {18}

RESISTOR_1 2.2K

ns

R87 2 3

1K,1% Q79 {7} PM_SLP_S3#_V18 Out PM_SLP_S3# {18,25}

BSS138

3

20K R89 RTC_TEST_N Q78

1 RTCCN1

3

1 BSS138

2 W-B-2P-R

2

4

HWS2_1P25R C20

1uF/10V,X5R

4

A A

ACES

85204-02X01

YX Technology ZhengWei

Title

<Title>

Size Project Name Rev

A2 N11 A

Date: Thursday, March 06, 2014 Sheet 7 of 30

5 4 3 2 1

5 4 3 2 1

+VCC_CORE {24,26} +V3.3S {6,7,12,13,14,16,17,18,19,23,24,25,26,28,29,30}

+V1.0S {6,23,24,25,26} +V1.35S

+GFX_CORE {24,26} +V1.8AUX {6,7,21}

+V_DDR {5,10,22,23,24} +V1.0AUX {21}

+V1.8S {4,6,7,15,23,24,25,28,30} +V1.35S

+VCCSFRBD0SI0_1P35

+V1.05S {23,24} +V1.2S {23}

+V1.5S {23} +V1.35S {24}

+V3.3AUX {7,13,14,16,17,18,20,21,22,23,24,25,26} +VCCSFRICKSI0_1P35

+VCCSFRDSISI0_1P35

+V3.3A_RTC {7}

+V_DDR 1.25A

+VCCDDRXXXSI3_1P35 +V_DDR

1.0S 3A

+V1.0S +V1.0S

+V1.35S

1.35S 400mA +V1.5S +V1.8S

U1G

+VCCDIGCFISI0_1P03 +VCCDIGDI3SI0_1P03

+VCCDDRCLKSI3_1P35

P28 BD49 +VCCSFRCRTSI0_1P35

{26} VCC_CPUSENSE CORE_VCC_SENSE_P28 DRAM_VDD_S4_BD49 +VCCDIGCRTSI0_1P03 +VCCDIGDPSI0_1P03 R91 0

D BB8 BD52 +VCCDDRXXXSI3_1P35 D

{26} VCC_GFXSENSE UNCORE_VNN_SENSE DRAM_VDD_S4_BD52 R0402

N28 BD53

{26} VSS_CPUSENSE CORE_VSS_SENSE_N28 DRAM_VDD_S4_BD53 +VCCDIGXXXSI0_1P03 +VCCDIGDP2SI0_1P03 R92 0 +VCCPAD1P8SI0_1P50

BF44 C21 C22

DRAM_VDD_S4_BF44 BG51 ns R0402

+VCCDDRCLKSI3_1P35 +VCCDIGOTGSI0_1P03 +VCCDIGDRFSI0_1P03 C0805 C0805

DRAM_VDD_S4_BG51 BJ48 +V1.05S 10uF/6.3V,X5R 22uF/6.3V,X5R

DRAM_VDD_S4_BJ48 C51 +V1.2S

AD38 DRAM_VDD_S4_C51 +VCCDIGDI1SI0_1P03

DRAM_VDD_S4_AD38 D44 +VCCDIGPIOSI0_1P03

+VCCDDRXXXSI3_1P35 AF38 DRAM_VDD_S4_D44

DRAM_VDD_S4_AF38 F49

A48 DRAM_VDD_S4_F49 +VCCFHVCPU0_1SI0_1P03

DRAM_VDD_S4 F52 +VCCDIGSI1SI0_1P03 +VCCDIGDI2SI0_1P03

AK38 DRAM_VDD_S4_F52

DRAM_VDD_S4_AK38 F53 R93 0 ns

AM38 DRAM_VDD_S4_F53 +VCCDIGSLMAON_1P03

DRAM_VDD_S4_AM38 H46 +VCCDIGGENSI0_1P03 +V1.8AUX R0402

AV41 DRAM_VDD_S4_H46 +VCCDIGUSBSI0_1P03

DRAM_VDD_S4_AV41 M41 R94 0 +VCCPADSI0_1P20

AV42 DRAM_VDD_S4_M41 M42 R0402

BB46 DRAM_VDD_S4_AV42

DRAM_VDD_S4_BB46

DRAM_VDD_S4_M42 V38

1.05S 1A +VCCDIGUIOSI0_1P03 +V3.3S

+VCC_CORE DRAM_VDD_S4_V38 +VCCPADXXXSUS_1P80

Y38

DRAM_VDD_S4_Y38

+VCCDIGPSRFSI0_1P03 +VCCPADXXX1SUS_1P80

AA27

AA29 CORE_VCC_S0IX_AA27 +VCCPADCF1SI0_3P30 +V1.0AUX NO HSIC used

AA30 CORE_VCC_S0IX_AA29 +GFX_CORE +VCCDIGICKSI0_1P03

AC27 CORE_VCC_S0IX_AA30 +V3.3AUX +V1.8S

AC29 CORE_VCC_S0IX_AC27 AA24 +V3.3S +VCCPADSUS_1P20

CORE_VCC_S0IX_AC29 UNCORE_VNN_S3_AA24 +V3.3A_RTC

AC30 AC22

AD27 CORE_VCC_S0IX_AC30 UNCORE_VNN_S3_AC22 AC24 +VCCPADCF1_2SI0_1P80

AD29 CORE_VCC_S0IX_AD27 UNCORE_VNN_S3_AC24 AD22

+VCCPADCF1SUS_3P30 +V1.0AUX 350mA

CORE_VCC_S0IX_AD29 UNCORE_VNN_S3_AD22 +VCCPADCF3SI0_3P30

AD30 AD24 +VCCPADXXXRTC_3P30 +V1.0AUX

AF27 CORE_VCC_S0IX_AD30 UNCORE_VNN_S3_AD24 AF22

AF29 CORE_VCC_S0IX_AF27 UNCORE_VNN_S3_AF22 AF24

AG27 CORE_VCC_S0IX_AF29 UNCORE_VNN_S3_AF24 AG22

+VCCDIGUSB3SUS_1P03

AG29 CORE_VCC_S0IX_AG27

CORE_VCC_S0IX_AG29

UNCORE_VNN_S3_AG22

UNCORE_VNN_S3_AG24

AG24 +GFX_CORE 12A

AG30 AJ22 +VCC_CORE

P26 CORE_VCC_S0IX_AG30 UNCORE_VNN_S3_AJ22 AJ24

CORE_VCC_S0IX_P26 UNCORE_VNN_S3_AJ24 +GFX_CORE

P27 AK22 +VCC_CORE

U27 CORE_VCC_S0IX_P27

CORE_VCC_S0IX_U27

UNCORE_VNN_S3_AK22

UNCORE_VNN_S3_AK24

AK24 +VCC_CORE 14A

U29 AK25

V27 CORE_VCC_S0IX_U29 UNCORE_VNN_S3_AK25 AK27

CORE_VCC_S0IX_V27 UNCORE_VNN_S3_AK27 C26 C27 C32

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

2.2uF/6.3V,X5R

V29 AK29 C24 C31 C25

C29

C30

C33

C34

C35

C36

V30 CORE_VCC_S0IX_V29 UNCORE_VNN_S3_AK29 AK30 C0805 C0805 C0805

C28 C0603 C0805 C0805

C23

Y27 CORE_VCC_S0IX_V30 UNCORE_VNN_S3_AK30 AK32 10uF/6.3V,X5R 10uF/6.3V,X5R 10uF/6.3V,X5R

C0603 2.2uF/6.3V,X5R 22uF/6.3V,X5R 22uF/6.3V,X5R

C0603

Y29 CORE_VCC_S0IX_Y27 UNCORE_VNN_S3_AK32 AM22 10uF/6.3V,X5R

Y30 CORE_VCC_S0IX_Y29 UNCORE_VNN_S3_AM22

CORE_VCC_S0IX_Y30

C C

AF30 AA22

TP_CORE_V1P05_S4 TP2_CORE_VCC_S0IX

+VCCDIGSLMAON_1P03 +VCCDIGPIOSI0_1P03 +VCCDIGICKSI0_1P03

+VCCDIGCRTSI0_1P03

+VCCDIGDPSI0_1P03

+VCCDIGDI2SI0_1P03

VLV_M_D +VCCDIGDI3SI0_1P03 +VCCDIGDI1SI0_1P03

+VCCDDRCLKSI3_1P35

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

C37

C43

C44

1uF/10V,X5R

C42

1uF/10V,X5R

C41

1uF/10V,X5R

C38

1uF/10V,X5R

1uF/10V,X5R

C40

1uF/10V,X5R

C45

C46

C39

+VCCSFRBD0SI0_1P35

+VCCSFRICKSI0_1P35

+VCCPADCF1SI0_3P30

+VCCDIGCFISI0_1P03 +VCCDIGCFISI0_1P03 +VCCSFRBD0SI0_1P35 +VCCPAD1P8SI0_1P50 +VCCPADCF1SUS_3P30

+VCCPADSUS_1P20

+VCCDIGUSB3SUS_1P03 +VCCDIGUSB3SUS_1P03+VCCPADSI0_1P20

U1H +VCCDIGOTGSI0_1P03

+VCCDIGUSBSI0_1P03

+VCCDIGDI1SI0_1P03 +VCCPADCF1_2SI0_1P80

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

V32 AD36

C57

1uF/10V,X5R

+VCCDIGDI2SI0_1P03

0.1uF/16V,X7R

C48

C50

SVID_V1P0_S3_V32 DRAM_V1P35_S0IX_F1_AD36

1uF/10V,X5R

BJ6 AM32 +VCCPADCF1SUS_3P30

C56

C49

1uF/10V,X5R

0.01uF/25V,X7R

C47

VGA_V1P0_S3_BJ6 HDA_LPE_V1P5V1P8_S3_AM32

1uF/10V,X5R

0.01uF/25V,X7R

AD35 AM30

C58

C55

1uF/10V,X5R

0.1uF/16V,X7R

C52

C53

AF35 DRAM_V1P0_S0IX_AD35 UNCORE_V1P8_S3_AM30 AN32

C51

C54

AF36 DRAM_V1P0_S0IX_AF35 UNCORE_V1P8_S3_AN32 AM27

AA36 DRAM_V1P0_S0IX_AF36 LPC_V1P8V3P3_S3_AM27 U24

+VCCDIGDI3SI0_1P03 DRAM_V1P0_S0IX_AA36 UNCORE_V1P8_G3_U24

AJ36 N18

AK35 DRAM_V1P0_S0IX_AJ36 USB_V3P3_G3_N18 P18

AK36 DRAM_V1P0_S0IX_AK35 USB_V3P3_G3_P18 U38

+VCCDIGDP2SI0_1P03 Y35 DRAM_V1P0_S0IX_AK36 UNCORE_V1P8_S3_U38 AN24 +VCCPADSI0_1P20

Y36 DRAM_V1P0_S0IX_Y35 VGA_V3P3_S3_AN24 V25

+VCCDIGDPSI0_1P03 DRAM_V1P0_S0IX_Y36 PCU_V1P8_G3_V25

AK19 N22 +VCCPADCF3SI0_3P30

+VCCDIGDRFSI0_1P03 DDI_V1P0_S0IX_AK19 PCU_V3P3_G3_N22

AK21 AN27

AJ18 DDI_V1P0_S0IX_AK21 SD3_V1P8V3P3_S3_AN27 AD16

AM16 DDI_V1P0_S0IX_AJ18 VSS_AD16 AD18 +VCCDIGGENSI0_1P03 +VCCDDRCLKSI3_1P35 +VCCDIGGENSI0_1P03

DDI_V1P0_S0IX_AM16 VSS_AD18 +VCCPADXXX1SUS_1P80

U22 V18 +VCCDIGGENSI0_1P03

+VCCDIGICKSI0_1P03 UNCORE_V1P0_G3_U22 USB_HSIC_V1P24_G3_V18 +VCCSFRBD0SI0_1P35

+VCCDIGGENSI0_1P03 V22 AA18

B AN29 UNCORE_V1P0_G3_V22 UNCORE_V1P8_G3_AA18 P22 B

UNCORE_V1P0_S0IX_AN29 RTC_VCC_P22 C59 C60 C61

1uF/10V,X5R

0.1uF/16V,X7R

AN30 N20

C64

C65

UNCORE_V1P0_S0IX_AN30 USB_V1P8_G3_N20 C0603 C0603 C0805

1uF/10V,X5R

AF16 U25

1uF/10V,X5R

C63

AF18 UNCORE_V1P0_S3_AF16 PMU_V1P8_G3_U25 AF33 2.2uF/6.3V,X5R 2.2uF/6.3V,X5R 22uF/6.3V,X5R

C62

UNCORE_V1P0_S3_AF18 CORE_V1P05_S3_AF33 +VCCPADSUS_1P20

Y18 AG33

G1 UNCORE_V1P0_S3_Y18 CORE_V1P05_S3_AG33 AG35

AM21 UNCORE_V1P0_S3_G1 CORE_V1P05_S3_AG35 U33 +VCCDIGSLMAON_1P03

+VCCDIGOTGSI0_1P03 AN21 PCIE_V1P0_S3_AM21 CORE_V1P05_S3_U33 U35

+VCCDIGOTGSI0_1P03 PCIE_V1P0_S3_AN21 CORE_V1P05_S3_U35 V33 +VCCPADXXXRTC_3P30

AN18 CORE_V1P05_S3_V33 A3

+VCCDIGSLMAON_1P03 AN19 PCIE_SATA_V1P0_S3_AN18 VSS_A3_A3 A49

AA33 SATA_V1P0_S3_AN19 VSS_A49_A49 A5

+VCCDIGOTGSI0_1P03 CORE_V1P05_S3_AA33 VSS_A5_A5

AF21 A51 +VCCPADXXXSUS_1P80

UNCORE_V1P0_S0IX_AF21 VSS_A51_A51 +VCCPADCF1SUS_3P30

+VCCDIGUIOSI0_1P03 AG21 A52

V24 UNCORE_V1P0_S0IX_AG21 VSS_A52_A52 A6

Y22 UNCORE_V1P0_S0IX_V24 VSS_A6_A6 B2 +VCCDIGXXXSI0_1P03

+VCCDIGUSBSI0_1P03 Y24 UNCORE_V1P0_S0IX_Y22 VSS_B2_B2 B52 +VCCPADXXX1SUS_1P80 +VCCPADXXXSUS_1P80

UNCORE_V1P0_S0IX_Y24 VSS_B52_B52 +VCCDIGCFISI0_1P03 +VCCPAD1P8SI0_1P50 +VCCPADCF1_2SI0_1P80

+VCCDIGXXXSI0_1P03 M14 B53 +VCCDIGDRFSI0_1P03 +VCCDIGPSRFSI0_1P03

+VCCDIGUSB3SUS_1P03 USB_V1P0_S3_M14 VSS_B53_B53

U18 BE1

1uF/10V,X5R

U19 USB_V1P0_S3_U18 VSS_BE1_BE1 BE53

C66

USB_V1P0_S3_U19 VSS_BE53_BE53

1uF/10V,X5R

1uF/10V,X5R

AN25 BG1

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

C73

C74

GPIO_V1P0_S3_AN25 VSS_BG1_BG1

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

Y19 BG53

C70

C71

C72

C67

C68

C69

C3 USB3_V1P0_G3_Y19 VSS_BG53_BG53 BH1

+VCCFHVCPU0_1SI0_1P03 USB3_V1P0_G3_C3 VSS_BH1_BH1

C5 BH2

B6 UNCORE_V1P0_G3_C5 VSS_BH2_BH2 BH52

AC32 UNCORE_V1P0_G3_B6 VSS_BH52_BH52 BH53

+VCCSFRBD0SI0_1P35 CORE_V1P05_S3_AC32 VSS_BH53_BH53

Y32 BJ2

U36 CORE_V1P05_S3_Y32 VSS_BJ2_BJ2 BJ3

+VCCSFRCRTSI0_1P35 UNCORE_V1P35_S0IX_F4_U36 VSS_BJ3_BJ3

AA25 BJ5

AG32 UNCORE_V1P35_S0IX_F5_AA25 VSS_BJ5_BJ5 BJ49 +VCCPADCF1_2SI0_1P80

+VCCSFRDSISI0_1P35 UNCORE_V1P35_S0IX_F2_AG32 VSS_BJ49_BJ49 +VCCDIGUSB3SUS_1P03

V36 BJ51 +VCCSFRDSISI0_1P35

UNCORE_V1P35_S0IX_F3_V36 VSS_BJ51_BJ51 +VCCPADCF1SI0_3P30 +VCCSFRBD0SI0_1P35

BD1 BJ52 +VCCSFRBD0SI0_1P35

AF19 VGA_V1P35_S3_F1_BD1 VSS_BJ52_BJ52 C1

AG19 UNCORE_V1P35_S0IX_F6 VSS_C1_C1 C53

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

UNCORE_V1P35_S0IX_F1_AG19 VSS_C53_C53

1uF/10V,X5R

+VCCSFRICKSI0_1P35 AJ19 E1

C79

C80

C81

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

C76

ICLK_V1P35_S3_F1_AJ19 VSS_E1_E1

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

E53 +VCCDIGPIOSI0_1P03

C75

C77

C78

1uF/10V,X5R

C82

C83

C85

VSS_E53_E53 F1

C84

AG18 RESERVED_F1 AK18

AN16 ICLK_V1P35_S3_F2 PCIE_V1P0_S3_AK18 AM18

U16 VSSA_AN16 PCIE_V1P0_S3_AM18

USB_VSSA_U16

A A

VLV_M_D

+VCCDDRXXXSI3_1P35

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

C86

C87

C88

C89

C90

C91

C92

C93

YX Technology ZhengWei

Title

<Title>

Size Project Name Rev

A2 N11 A

Date: Thursday, March 06, 2014 Sheet 8 of 30

5 4 3 2 1

5 4 3 2 1

D D

U1M

U1L

U1J U1K

U1I

K9 U3

VSS281 VSS316 BF30 E8

AG38 AH47 AT24 AY36 L13 U30 VSS211 VSS246

A11 AC36 VSS71 VSS106 VSS141 VSS176 VSS282 VSS317 BF36 F19

VSS1 VSS36 AH4 AH48 AT27 AY4 L19 U32 VSS212 VSS247

A15 AC38 VSS72 VSS107 VSS142 VSS177 VSS283 VSS318 BF4 F2

VSS2 VSS37 AH41 AH50 AT30 AY50 L27 U40 VSS213 VSS248

A19 AD19 VSS73 VSS108 VSS143 VSS178 VSS284 VSS319 BG31 F24

VSS3 VSS38 AH45 AH51 AT35 AY9 L35 U42 VSS214 VSS249

A23 AD21 VSS74 VSS109 VSS144 VSS179 VSS285 VSS320 BG34 F27

VSS4 VSS39 AH7 AH6 AT38 BA14 M19 U43 VSS215 VSS250

A27 AD25 VSS75 VSS110 VSS145 VSS180 VSS286 VSS321 BG39 F30

VSS5 VSS40 AH9 AM44 AT4 BA19 M26 U45 VSS216 VSS251

A31 AD32 VSS76 VSS111 VSS146 VSS181 VSS287 VSS322 BG42 F35

VSS6 VSS41 AJ1 AM51 AT47 BA22 M27 U46 VSS217 VSS252

A35 AD33 VSS77 VSS112 VSS147 VSS182 VSS288 VSS323 BG45 F5

VSS7 VSS42 AJ16 AM7 AT52 BA27 M34 U48 VSS218 VSS253

A39 AD47 VSS78 VSS113 VSS148 VSS183 VSS289 VSS324 BG49 F7

VSS8 VSS43 AJ21 AN1 AU1 BA32 M35 U49 VSS219 VSS254

A43 AD7 VSS79 VSS114 VSS149 VSS184 VSS290 VSS325 BJ11 G10

VSS9 VSS44 AJ25 AN11 AU24 BA35 M38 U5 VSS220 VSS255

A47 AE1 VSS80 VSS115 VSS150 VSS185 VSS291 VSS326 BJ15 G20

VSS10 VSS45 AJ27 AN12 AU3 BA40 M47 U51 VSS221 VSS256

AA1 AE11 VSS81 VSS116 VSS151 VSS186 VSS292 VSS327 BJ19 G22

VSS11 VSS46 AJ29 AN14 AU30 BA53 M51 U53 VSS222 VSS257

AA16 AE12 VSS82 VSS117 VSS152 VSS187 VSS293 VSS328 BJ23 G26

VSS12 VSS47 AJ3 AN22 AU38 BB19 N1 U6 VSS223 VSS258

AA19 AE14 VSS83 VSS118 VSS153 VSS188 VSS294 VSS329 BJ27 G28

VSS13 VSS48 AJ30 AN3 AU51 BB27 N16 U8 VSS224 VSS259

AA21 AE3 VSS84 VSS119 VSS154 VSS189 VSS295 VSS330 BJ31 G32

VSS14 VSS49 AJ32 AN33 AV12 BB35 N38 U9 VSS225 VSS260

AA3 AE4 VSS85 VSS120 VSS155 VSS190 VSS296 VSS331 BJ35 G34

VSS15 VSS50 AJ33 AN35 AV13 BC20 N51 V12 VSS226 VSS261

AA32 AE40 VSS86 VSS121 VSS156 VSS191 VSS297 VSS332 BJ39 G42

VSS16 VSS51 AJ35 AN36 AV14 BC22 P13 V16 VSS227 VSS262

AA35 AE42 VSS87 VSS122 VSS157 VSS192 VSS298 VSS333 BJ43 H19

VSS17 VSS52 AJ38 AN38 AV18 BC26 P16 V19 VSS228 VSS263

AA38 AE43 VSS88 VSS123 VSS158 VSS193 VSS299 VSS334 BJ47 H27

VSS18 VSS53 AJ53 AN40 AV19 BC28 P19 V21 VSS229 VSS264

AA53 AE45 VSS89 VSS124 VSS159 VSS194 VSS300 VSS335 BJ7 H35

VSS19 VSS54 AK10 AN42 AV24 BC32 P20 V35 VSS230 VSS265

AB10 AE46 VSS90 VSS125 VSS160 VSS195 VSS301 VSS336 C14 J1

VSS20 VSS55 AK14 AN43 AV27 BC34 P24 V40 VSS231 VSS266

AB4 AE48 VSS91 VSS126 VSS161 VSS196 VSS302 VSS337 C31 J16

VSS21 VSS56 AK16 AN45 AV30 BC42 P32 V44 VSS232 VSS267

AB41 AE50 VSS92 VSS127 VSS162 VSS197 VSS303 VSS338 C34 J19

VSS22 VSS57 AK33 AN46 AV35 BD19 P35 V51 VSS233 VSS268

AB45 AE51 VSS93 VSS128 VSS163 VSS198 VSS304 VSS339 C39 J22

VSS23 VSS58 AK41 AN48 AV38 BD24 P38 V7 VSS234 VSS269

AB47 AE53 VSS94 VSS129 VSS164 VSS199 VSS305 VSS340 C42 J27

VSS24 VSS59 AK44 AN49 AV47 BD27 P4 Y10 VSS235 VSS270

AB48 AE6 VSS95 VSS130 VSS165 VSS200 VSS306 VSS341 C45 J32

C VSS25 VSS60 AM12 AN5 AV51 BD30 P47 Y14 VSS236 VSS271 C

AB50 AE8 VSS96 VSS131 VSS166 VSS201 VSS307 VSS342 C49 J35

VSS26 VSS61 AM19 AN51 AV7 BD35 P52 Y16 VSS237 VSS272

AB51 AE9 VSS97 VSS132 VSS167 VSS202 VSS308 VSS343 D12 J40

VSS27 VSS62 AM24 AN53 AW13 BE19 P9 Y21 VSS238 VSS273

AB6 AF10 VSS98 VSS133 VSS168 VSS203 VSS309 VSS344 D16 J53

VSS28 VSS63 AM25 AN6 AW19 BE2 T40 Y25 VSS239 VSS274

AC16 AF12 VSS99 VSS134 VSS169 VSS204 VSS310 VSS345 D24 K14

VSS29 VSS64 AM29 AN8 AW27 BE35 U1 Y33 VSS240 VSS275

AC18 AF25 VSS100 VSS135 VSS170 VSS205 VSS311 VSS346 D30 K22

VSS30 VSS65 AM33 AN9 AW3 BE8 U11 Y41 VSS241 VSS276

AC19 AF32 VSS101 VSS136 VSS171 VSS206 VSS312 VSS347 D36 K32

VSS31 VSS66 AM35 AP40 AW35 BF12 U12 Y44 VSS242 VSS277

AC21 AF47 VSS102 VSS137 VSS172 VSS207 VSS313 VSS348 D38 K36

VSS32 VSS67 AM36 AT12 AY10 BF16 U14 Y7 VSS243 VSS278

AC25 AG16 VSS103 VSS138 VSS173 VSS208 VSS314 VSS349 E19 K4

VSS33 VSS68 AM40 AT16 AY22 BF24 U21 Y9 VSS244 VSS279

AC33 AG25 VSS104 VSS139 VSS174 VSS209 VSS315 VSS350 E35 K50

VSS34 VSS69 M28 AT19 AY32 BF38 VSS245 VSS280

AC35 AG36 VSS105 VSS140 VSS175 VSS210

VSS35 VSS70

VLV_M_D

VLV_M_D

VLV_M_D VLV_M_D

VLV_M_D

B B

A A

YX Technology ZhengWei

Title

<Title>

Size Project Name Rev

A3 N11 A

Date: Thursday, March 06, 2014 Sheet 9 of 30

5 4 3 2 1

5 4 3 2 1

+V5AUX {14,17,18,21,22,24,26}

+V_DDR {5,8,22,23,24}

+V3.3S {6,7,8,12,13,14,16,17,18,19,23,24,25,26,28,29,30}

+VDDQ_DDR3L +VDDQ_DDR3L

U48 U49

J3 K2 J3 K2

{5,10} M_A_RAS# RAS# VDD_9 {5,10} M_A_RAS# RAS# VDD_9

K3 R9 K3 R9

{5,10} M_A_CAS# CAS# VDD_8 {5,10} M_A_CAS# CAS# VDD_8

L3 R1 C605 C600 C606 C601 L3 R1 C607 C602 C603 C608

{5,10} M_A_WE# WE# VDD_7 {5,10} M_A_WE# WE# VDD_7

L2 N9 L2 N9

{5,10} M_CS#0 CS# VDD_6 {5,10} M_CS#0 CS# VDD_6

N1 N1

{5,10} M_A_A[15:0] VDD_5 0.47uF/10V,X5R 0.47uF/10V,X5R {5,10} M_A_A[15:0] VDD_5 0.47uF/10V,X5R 0.47uF/10V,X5R

M_A_A0 N3 K8 M_A_A0 N3 K8

A0 VDD_4 4.7uF/10V,X5R A0 VDD_4 0.47uF/10V,X5R

M_A_A1 P7 G7 0.47uF/10V,X5R M_A_A1 P7 G7 4.7uF/10V,X5R

M_A_A2 P3 A1 VDD_3 D9 M_A_A2 P3 A1 VDD_3 D9

M_A_A3 N2 A2 VDD_2 B2 M_A_A3 N2 A2 VDD_2 B2

M_A_A4 P8 A3 VDD_1 M_A_A4 P8 A3 VDD_1

M_A_A5 P2 A4 M_A_A5 P2 A4

D A5 A5 D

M_A_A6 R8 H9 M_A_A6 R8 H9

M_A_A7 R2 A6 VDDQ_9 H2 M_A_A7 R2 A6 VDDQ_9 H2

M_A_A8 T8 A7 VDDQ_8 F1 C604 C609 M_A_A8 T8 A7 VDDQ_8 F1 C610 C611

M_A_A9 R3 A8 VDDQ_7 E9 0.47uF/10V,X5R M_A_A9 R3 A8 VDDQ_7 E9

M_A_A10 L7 A9 VDDQ_6 D2 M_A_A10 L7 A9 VDDQ_6 D2

A10/AP VDDQ_5 0.47uF/10V,X5R A10/AP VDDQ_5 0.47uF/10V,X5R

M_A_A11 R7 C9 M_A_A11 R7 C9

A11 VDDQ_4 A11 VDDQ_4 0.47uF/10V,X5R

M_A_A12 N7 C1 M_A_A12 N7 C1

M_A_A13 T3 A12/BC# VDDQ_3 A8 M_A_A13 T3 A12/BC# VDDQ_3 A8

M_A_A14 T7 A13 VDDQ_2 A1 M_A_A14 T7 A13 VDDQ_2 A1

M7 A14 VDDQ_1 M7 A14 VDDQ_1

A15 A15

M2

Close to DRAM Between DRAM M2

Close to DRAM Between DRAM

{5,10} M_A_BS0 BA0 {5,10} M_A_BS0 BA0

N8 G9 N8 G9

{5,10} M_A_BS1 BA1 VSSQ_9 {5,10} M_A_BS1 BA1 VSSQ_9

M3 G1 M3 G1

{5,10} M_A_BS2 BA2 VSSQ_8 {5,10} M_A_BS2 BA2 VSSQ_8

F9 F9

K9 VSSQ_7 E8 K9 VSSQ_7 E8

{5,10} M_CKE0 CKE VSSQ_6 {5,10} M_CKE0 CKE VSSQ_6

J7 E2 J7 E2

{5,10,11} M_CLK_DDR0 CK VSSQ_5 {5,10,11} M_CLK_DDR0 CK VSSQ_5

K7 D8 K7 D8

{5,10,11} M_CLK_DDR0# CK# VSSQ_4 {5,10,11} M_CLK_DDR0# CK# VSSQ_4

D1 D1

{5} M_A_DM[7:0] VSSQ_3 B9 VSSQ_3 B9

VSSQ_2 B1 VSSQ_2 B1

VSSQ_1 VSSQ_1

{5} M_A_DQS[7:0]

J1 J1

{5} M_A_DQS#[7:0] L1 NC_4 T9 L1 NC_4 T9

J9 NC_5 VSS_12 T1 J9 NC_5 VSS_12 T1

L9 NC_6 VSS_11 P9 L9 NC_6 VSS_11 P9

{5} M_A_DQ[63:0] NC_7 VSS_10 NC_7 VSS_10

P1 +VDDQ_DDR3L P1

T2 VSS_9 M9 T2 VSS_9 M9

{5,10} DDR3_DRAMRST# RESET# VSS_8 {5,10} DDR3_DRAMRST# RESET# VSS_8 +V_DDR

K1 M1 K1 M1

{5,10} M_ODT0 ODT VSS_7 {5,10} M_ODT0 ODT VSS_7

M0_ZQ0 L8 J8 M0_ZQ1 L8 J8

ZQ VSS_6 J2 R731 ZQ VSS_6 J2

VSS_5 G8 4.7K VSS_5 G8

M_A_DQ2 E3 VSS_4 E1 R733 M_A_DQ20 E3 VSS_4 E1

R732 M_A_DQ0 F7 DQL0 VSS_3 B3 240,1% M_A_DQ21 F7 DQL0 VSS_3 B3

F2 DQL1 VSS_2 A9 F2 DQL1 VSS_2 A9 C616 C617

240,1% M_A_DQ6 VREF_DQ0 M_A_DQ23

DQL2 VSS_1 DQL2 VSS_1 C612 C613 C614 C615 C0805 C0805

M_A_DQ3 F8 M_A_DQ17 F8

DQL3 DQL3 2.2uF/6.3V,X5R 2.2uF/6.3V,X5R 2.2uF/6.3V,X5R 2.2uF/6.3V,X5R 10uF/6.3V,X5R 10uF/6.3V,X5R

M_A_DQ1 H3 M_A_DQ18 H3

M_A_DQ4 H8 DQL4 C618 C619 R734 M_A_DQ16 H8 DQL4 ns ns

M_A_DQ7 G2 DQL5 0.1uF/16V,X7R 4.7K M_A_DQ22 G2 DQL5

M_A_DQ5 H7 DQL6 M_A_DQ19 H7 DQL6

DQL7 0.1uF/16V,X7R DQL7

M_A_DM0 E7 H1 VREF_DQ0 M_A_DM2 E7 H1 VREF_DQ0

C M_A_DQS0 F3 DML VREFDQ M8 VREF_CA0 M_A_DQS2 F3 DML VREFDQ M8 VREF_CA0

C

M_A_DQS#0 G3 DQSL VREFCA M_A_DQS#2 G3 DQSL VREFCA

DQSL# +VDDQ_DDR3L DQSL#

M_A_DQ12 D7 M_A_DQ28 D7 +V_DDR

M_A_DQ10 C3 DQU0 R735 M_A_DQ26 C3 DQU0

M_A_DQ9 C8 DQU1 4.7K M_A_DQ29 C8 DQU1

M_A_DQ11 C2 DQU2 M_A_DQ27 C2 DQU2

DQU3 DQU3 R736 10K DRAM_PWROK {5}

M_A_DQ13 A7 M_A_DQ25 A7

M_A_DQ15 A2 DQU4 VREF_CA0 M_A_DQ30 A2 DQU4

DQU5 DQU5 R737 0

M_A_DQ8 B8 M_A_DQ24 B8 V1_5_PWROK {22}

M_A_DQ14 A3 DQU6 M_A_DQ31 A3 DQU6

M_A_DM1 D3 DQU7 C620 C621 R738 M_A_DM3 D3 DQU7

DMU DMU C622

M_A_DQS1 C7 0.1uF/16V,X7R 0.1uF/16V,X7R

4.7K M_A_DQS3 C7

DQSU DQSU 1uF/10V,X5R

M_A_DQS#1 B7 M_A_DQS#3 B7

DQSU# DQSU#

EDJ4216EFBG-GNL-F EDJ4216EFBG-GNL-F

+VDDQ_DDR3L +V_DDR

Pay attention to DQS and DM order if Data Bytes need swapping.

+VDDQ_DDR3L +VDDQ_DDR3L

U50 U51

J3 K2 J3 K2

{5,10} M_A_RAS# RAS# VDD_9 {5,10} M_A_RAS# RAS# VDD_9

K3 R9 K3 R9

{5,10} M_A_CAS# CAS# VDD_8 {5,10} M_A_CAS# CAS# VDD_8

L3 R1 C623 C624 C625 C626 L3 R1 C632 C627 C628 C629

{5,10} M_A_WE# WE# VDD_7 {5,10} M_A_WE# WE# VDD_7

L2 N9 L2 N9 C633 C634 C635 C636

{5,10} M_CS#0 CS# VDD_6 {5,10} M_CS#0 CS# VDD_6

N1 N1 0.47uF/10V,X5R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R

{5,10} M_A_A[15:0] VDD_5 0.47uF/10V,X5R 0.47uF/10V,X5R {5,10} M_A_A[15:0] VDD_5 0.47uF/10V,X5R

M_A_A0 N3 K8 M_A_A0 N3 K8 4.7uF/10V,X5R

A0 VDD_4 4.7uF/10V,X5R A0 VDD_4 0.47uF/10V,X5R

M_A_A1 P7 G7 0.47uF/10V,X5R M_A_A1 P7 G7

M_A_A2 P3 A1 VDD_3 D9 M_A_A2 P3 A1 VDD_3 D9

M_A_A3 N2 A2 VDD_2 B2 M_A_A3 N2 A2 VDD_2 B2

M_A_A4 P8 A3 VDD_1 M_A_A4 P8 A3 VDD_1

M_A_A5 P2 A4 M_A_A5 P2 A4

M_A_A6 R8 A5 H9 M_A_A6 R8 A5 H9

M_A_A7 R2 A6 VDDQ_9 H2 M_A_A7 R2 A6 VDDQ_9 H2

M_A_A8 T8 A7 VDDQ_8 F1 C630 C631 M_A_A8 T8 A7 VDDQ_8 F1 C637 C638

M_A_A9 R3 A8 VDDQ_7 E9 M_A_A9 R3 A8 VDDQ_7 E9

B A9 VDDQ_6 A9 VDDQ_6 B

M_A_A10 L7 D2 0.47uF/10V,X5R M_A_A10 L7 D2 0.47uF/10V,X5R

M_A_A11R7 A10/AP VDDQ_5 C9 M_A_A11R7 A10/AP VDDQ_5 C9

A11 VDDQ_4 0.47uF/10V,X5R A11 VDDQ_4 0.47uF/10V,X5R

M_A_A12N7 C1 M_A_A12N7 C1

M_A_A13 T3 A12/BC# VDDQ_3 A8 M_A_A13 T3 A12/BC# VDDQ_3 A8

M_A_A14 T7 A13 VDDQ_2 A1 M_A_A14 T7 A13 VDDQ_2 A1

M7 A14 VDDQ_1 M7 A14 VDDQ_1

A15 A15

M2

Close to DRAM Between DRAM M2

Close to DRAM Between DRAM

{5,10} M_A_BS0 BA0 {5,10} M_A_BS0 BA0

N8 G9 N8 G9

{5,10} M_A_BS1 BA1 VSSQ_9 {5,10} M_A_BS1 BA1 VSSQ_9

M3 G1 M3 G1

{5,10} M_A_BS2 BA2 VSSQ_8 {5,10} M_A_BS2 BA2 VSSQ_8

F9 F9

K9 VSSQ_7 E8 K9 VSSQ_7 E8

{5,10} M_CKE0 CKE VSSQ_6 {5,10} M_CKE0 CKE VSSQ_6

J7 E2 J7 E2

{5,10,11} M_CLK_DDR0 K7 CK VSSQ_5 D8 {5,10,11} M_CLK_DDR0 K7 CK VSSQ_5 D8

{5,10,11} M_CLK_DDR0# CK# VSSQ_4 {5,10,11} M_CLK_DDR0# CK# VSSQ_4

D1 D1

VSSQ_3 B9 VSSQ_3 B9

VSSQ_2 B1 VSSQ_2 B1

VSSQ_1 VSSQ_1

J1 J1

L1 NC_4 T9 L1 NC_4 T9

J9 NC_5 VSS_12 T1 J9 NC_5 VSS_12 T1

L9 NC_6 VSS_11 P9 L9 NC_6 VSS_11 P9

NC_7 VSS_10 P1 +VDDQ_DDR3L NC_7 VSS_10 P1

T2 VSS_9 M9 T2 VSS_9 M9

{5,10} DDR3_DRAMRST# RESET# VSS_8 {5,10} DDR3_DRAMRST# RESET# VSS_8

K1 M1 K1 M1

{5,10} M_ODT0 ODT VSS_7 {5,10} M_ODT0 ODT VSS_7

M0_ZQ2 L8 J8 M0_ZQ3 L8 J8

ZQ VSS_6 J2 R739 ZQ VSS_6 J2

VSS_5 G8 4.7K VSS_5 G8

R740 M_A_DQ42 E3 VSS_4 E1 R741 M_A_DQ54 E3 VSS_4 E1

240,1% M_A_DQ45 F7 DQL0 VSS_3 B3 240,1% M_A_DQ49 F7 DQL0 VSS_3 B3

M_A_DQ46 F2 DQL1 VSS_2 A9 VREF_DQ1 M_A_DQ55 F2 DQL1 VSS_2 A9

M_A_DQ44 F8 DQL2 VSS_1 M_A_DQ48 F8 DQL2 VSS_1

M_A_DQ47 H3 DQL3 M_A_DQ51 H3 DQL3

DQL4 C640 R742 DQL4

M_A_DQ41 H8 C639 M_A_DQ53 H8

DQL5 4.7K DQL5

M_A_DQ43 G2 0.1uF/16V,X7R M_A_DQ50 G2

M_A_DQ40 H7 DQL6 0.1uF/16V,X7R M_A_DQ52 H7 DQL6

M_A_DM5 E7 DQL7 H1 VREF_DQ1 M_A_DM6 E7 DQL7 H1 VREF_DQ1

M_A_DQS5 F3 DML VREFDQ M8 VREF_CA1 M_A_DQS6 F3 DML VREFDQ M8 VREF_CA1

M_A_DQS#5 G3 DQSL VREFCA M_A_DQS#6 G3 DQSL VREFCA

DQSL# +VDDQ_DDR3L DQSL#

A A

M_A_DQ36 D7 M_A_DQ56 D7

M_A_DQ39 C3 DQU0 R743 M_A_DQ59 C3 DQU0

M_A_DQ33 C8 DQU1 4.7K M_A_DQ57 C8 DQU1

M_A_DQ38

M_A_DQ37

M_A_DQ35

C2

A7

A2

B8

DQU2

DQU3

DQU4

DQU5

VREF_CA1

M_A_DQ58

M_A_DQ61

M_A_DQ63

C2

A7

A2

B8

DQU2

DQU3

DQU4

DQU5

YX Technology ZhengWei

M_A_DQ32 M_A_DQ60

M_A_DQ34 A3 DQU6 M_A_DQ62 A3 DQU6

M_A_DM4 D3 DQU7 C641 C642 R744 M_A_DM7 D3 DQU7 Title

C7 DMU C7 DMU

M_A_DQS4

M_A_DQS#4 B7 DQSU

0.1uF/16V,X7R 4.7K M_A_DQS7

M_A_DQS#7 B7 DQSU <Title>

DQSU# 0.1uF/16V,X7R DQSU#

EDJ4216EFBG-GNL-F EDJ4216EFBG-GNL-F

Size Project Name Rev

B N11 A

Date: Thursday, March 06, 2014 Sheet 10 of 30

5 4 3 2 1

5 4 3 2 1

D D

R442 30.1,1% ns

{5,10} M_CLK_DDR0

C309

1.5PF/50V,NPO

R455 30.1,1% ns

{5,10} M_CLK_DDR0#

C C

C307

0.1uF/16V,X7R

ns

B B

A A

YX Technology ZhengWei

Title

<Title>

Size Project Name Rev

A4 N11 A

Date: Thursday, March 06, 2014 Sheet 11 of 30

5 4 3 2 1

5 4 3 2 1

+V3.3S {6,7,8,13,14,16,17,18,19,23,24,25,26,28,29,30}

D +V5S {6,7,8,13,14,16,17,18,19,23,24,25,26,28,29,30} D

DVDD_GL850A DVDD_GL850A

R693 R694 DVDD_GL850A

10K 10K

DVDD_GL850A

DVDD_GL850A

DVDD_GL850A

R695

OVCUR1

PGANG

PSELF

+V3.3S 100K

DVDD_GL850A PGANG

R696

48

47

46

45

44

43

42

41

40

39

38

37

DVDD5

DGND5

PAMBER1

PGREEN1

DVDD4

DGND4

PWREN1#

OVCUR1#

PGANG

DVDD3

DGND3

PSELF

R0603 PGANG

0 C559 C560 C561 C562 C563 C564

10uF/6.3V,X5R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R INPUT MODE OUTPUT MODE

C0603

AVDD 1 36 1 Gang mode 0 Normal 1 Suspend

AVDD1 PAMBER2

2 35 0 Individual mode 1 Normal 0 Suspend

AGND1 PGREEN2

R463 0 ns 3 U43 34 DVDD_GL850A

{6,12} USB_PN3 DM0 DVDD2

GL850A

R546 0 ns 4 LQFP48_P5 33

{6,12} USB_PP3 DP0 DGND2

USBDM1 5 32

DM1 PAMBER3

DVDD_GL850A USBDP1 6 31

AVDD 7

DP1

AVDD2

GL850A PGREEN3

NC

30

C R697 C

8 29

AVDD AGND2 TEST

LQFP48

R0603 USBDM2 R471 0 ns 9 28 USBRST

DM2 RESET#

0 C565 C566 C567 C568 C569 USBDP2 R548 0 ns 10 27 DVDD_GL850A

0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R DP2 DVDD1

R698 680 RREF 11 26

RREF DGND1

AVDD 12 25

AVDD3 PAMBER4

PGREEN4

AGND3

AGND4

AGND5

AVDD4

AVDD5

DM3

DM4

DP3

DP4

X1

X2

DVDD_GL850A USB1: Micro USB

USB2: Camera

13

14

15

16

17

18

19

20

21

22

23

24

USB3:

R699 C570 22pF/50V,NPO X1_GL850A USB4: BT

X1_GL850A

X2_GL850A

10K

4

ns

Y4

AVDD

AVDD

R703 0 USBRST 12MHz R700

{7,13,16,18} PLTRST#

X4S32X25 1M

R701 USBDP4

TP47 ns

51K C571

3

ns 10uF/6.3V,X5R X2_GL850A USBDM4

TP50 ns

C0603 C572 22pF/50V,NPO

ns

USBDP3

TP51 ns

USBDM3

TP59 ns

B B

R464 0 USBDM2

{6,12} USB_PN3 USBDM2 {16}

R547 0 USBDP2

{6,12} USB_PP3 USBDP2 {16}

+V5S

+V3.3S

R499 0 R0402 ns C573 0.1uF/16V,X7R

R0402 USB_TP

R498 0

FFC4 1.0

fpce4_1p0r

1

USBDM1 2 1 6

USBDP1 3 2 6 5

4 3 5

4

ns

A A

YX Technology ZhengWei

Title

<Title>

Size Project Name Rev

C N11 A

Date: Thursday, March 06, 2014 Sheet 12 of 30

5 4 3 2 1

5 4 3 2 1

+V3.3S

+V3.3AUX +V3.3S {6,7,8,12,14,16,17,18,19,23,24,25,26,28,29,30}

+V3.3AUX {7,8,14,16,17,18,20,21,22,23,24,25,26}

Y6

4 25MHz,20pF

3

Pin44-XTAL2 is External Clock Input Pin. 1 2 ns

R730 0

CLK_25M_LPC {6}

X4S32X25

D XTAL2 R127 0 ns D

CLK_25M {7}

Y7

4 3

R128 0 VDD33

+V3.3AUX

1 2

R0805 R15 25MHz,20pF

X4S50X32

C144 C145 C146 C147 C148 C149 C599 C598

0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R R129 22pF/50V,NPO 22pF/50V,NPO

C12 C14 ns ns 2.49K,1% R130 ns

R15 value should be 1K,1%

ns ns

2.49K (1%)

for all application. Using EFuse only without ASF function.

VDD33

VDD33

VDD10

VDD33

VDD10

VDD33

XTAL2

XTAL1

C17

GPO

C12 to C17

Close To U5

U8

48

47

46

45

44

43

42

41

40

39

38

37

VDD33

49

AVDD33C

AVDD33B

RSET

AVDD10B

CKXTAL2

CKXTAL1

AVDD33A

DVDD10(NC)

LED0

DVDD3B

GPO/SMBALERT

LED1/EESK

GND2

R23 For Enable Switch Regulator.

R131 R24 For Disable Switch Regulator.

0 ns

MDI0+ 1 36 REGOUT R23

MDI0- 2 MDIP0 REGOUT 35 AVDD33_REG

VDD10 3 MDIN0 VDDREG2 34 AVDD33_REG

MDI1+ 4 AVDD10 VDDREG1 33 R132 0 EEDI R133 10K

**Power Sequence Must Refer to Layout Guide.** MDI1- 5 MDIP1 ENSWREG 32 EEDI R24

VDD10 6 MDIN1 EEDI 31 EECS R134 10K

7 AVDD10(NC) LED3/EEDO 30 EECS

8 MDIP2(NC) RTL8105E EECS 29 VDD10

VDD10 9 MDIN2(NC) QFN48_P4 DVDD10B 28

10 AVDD10(NCC) LANWAKEB 27 VDD33 PCIE_WAKE# {7}

For RTL8111E-VB 11 MDIP3(NC) DVDD33A 26 R135 1K,1% +V3.3S

VDD33 12 MDIN3(NC) ISOLATEB 25

* C12 to C17 are for VDD33 pins-- 12, 27, 39, 42, 47, 48. AVDD33(NC) PERSTB

SMBDATA(NC)

R136 20K

SMBCLK(NC)

REFCLK_N

REFCLK_P

CLKREQB

DVDD10A

For RTL8105E-VC

EVDD10

C C

HSON

HSOP

GND1

* C12 to C15 are for VDD33 pins-- 27, 39, 47, 48.

HSIN

HSIP

R137 0 PLTRST# {7,12,16,18}

R0402

13

14

15

16

17

18

19

20

21

22

23

24

VDD10

EVDD10

VDD10

C150 C151 C152 C153 C154 C155 C156

0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R

C1 C4 ns ns ns C7 ns

C1 to C7 TP15

TP16

Close To U5 ns ns

For RTL8111E-VB {6} LAN_CLKREQ#

* C1 to C7 are for VDD10 pins-- 3, 6, 9, 13, 29, 41, 45. R138 0 EVDD10 PCIE_TXP1_LAN

{6} PCIE_TXP1_LAN

PCIE_TXN1_LAN

{6} PCIE_TXN1_LAN

{7} CLK_PCIE_LAN

For RTL8105E-VC C157 C158 {7} CLK_PCIE_LAN#

1uF/10V,X5R 0.1uF/16V,X7R

* C1 to C3 are for VDD10 pins-- 13, 29, 45.

C10,C11 Close To U5

{6} PCIE_RXP1_LAN C159 0.1uF/16V,X7R

{6} PCIE_RXN1_LAN C160 0.1uF/16V,X7R

* C10 ,C11 are for EVDD10 pins--21.

B B

MDI0-

LAN_TX0- {17}

MDI0+

LAN_TX0+ {17}

MDI1-

LAN_TX1- {17}

MDI1+

LAN_TX1+ {17}

A A

YX Technology ZhengWei

Title

<Title>

Size Project Name Rev

A2 N11 A

Date: Thursday, March 06, 2014 Sheet 13 of 30

5 4 3 2 1

5 4 3 2 1

+V3.3AUX {7,8,13,16,17,18,20,21,22,23,24,25,26}

+V3.3S {6,7,8,12,13,16,17,18,19,23,24,25,26,28,29,30}

+V5S {15,16,17,18,24,26,28}

+V5AUX {17,18,21,22,24,26}

+VDC {20,21,22,24,25,26}

+V1.8S {15,16,17,18,24,26,28}

LCDVDD

LCDCN1

20347-330E

R139 0 ns

LCDS30_P4

R0805

+V3.3S LCDVDD

D

Q5 500mA +V3.3AUX +V5AUX

1

1

D

2

AO3407 2

DP_HPD 3

4 3

2 3 R143 R0603 ns 4

5

0 {4} DDI1_AUXP Out 5

6

V5_CAM R145 R0603 {4} DDI1_AUXN Out 6

7

R141 0 7

8

1M C161 C162 C163 {4} DDI1_TXP0 Out 8

9

1

0.01uF/25V,X7R 0.1uF/16V,X7R 10uF/6.3V,X5R {4} DDI1_TXN0 Out 9

R335 0 10

11 10

R144 100K,1% {4} DDI1_TXP1 Out 11

CHK6 12

{4} DDI1_TXN1 Out 12

90ohm@100MHz,0.5A 13

LCDVDD rising L4S2012 14 13

ns 14

time is 470uS {6} USB_PN2

1 2 15

15

4 3 16

3

{6} USB_PP2 16

17

R146 1 Q6 +V1.8S 17

{4} DDI1_VDDEN Out V5_CAM 18

1K MMBT3904-F 18

19

R269 0 19

LCDVDD_ON R158 BKLT_PWM 20

2

R147 {5,18,25} LCDVDD_ON 20

1K R345 BKLT_ON 21

100K,1% 21

10K LED_FB1 22

LED_FB2 23 22

R152 0 ns LED_FB3 24 23

{4} DDI1_HPD IN 24

LED_FB4 25

LED_FB5 26 25 32

3

LEDVDD LED_FB6 27 26 32 31

Q62 27 31

28

29 28

C 1 DP_HPD 29 C

30

+V3.3S 2N7002K 30

2

R437

100K

R148

4.7K

ns +V5S+VDC

0 R149 ns TTL_ADJ {18}

R0402

R153 ns

0

BKLT_PWM 0 R150 +VDC

Out DDI1_BKLTCTL {4} R154 ns

R0402 LEDVDD

0

C164 R151

1000pF/50V,X7R 100K,1%

1.8V Q63

6 L7

D32

ns 4 5

2

1 10uH/2A

C418 CKS2D66 SSM34PT

STT3423P SMA

+V3.3S 4.7UF/25V X7R

C417 C419

3

C1206

4.7UF/25V X7R 4.7UF/25V X7R

GND_LEDA C1206 C1206

C319

R155 0.022uF/16V,X7R ns

4.7K C320

3

R337

B Q7 B

2N7002K 0.022uF/16V,X7R

SOT23 GND_LEDA C306 1uF/10V,X5R

1

499,1%

24

23

22

21

20

19

2

3

VCC

VIN

COMP

VFAULT

SW1

SW2

R469

R157 1 Q9

{4} DDI1_BKLT_EN Out

1K MMBT3904-F

BKLT_ON 1 18 1M

2

R159 EN PGND1

100K,1% GND_LEDA R343 0 2 17

OSC PGND2

+V3.3S GND_LEDA C324 2200pF/25V,X7R3 U38 16

FSET MP3388DR OVP

GND_LEDA C401 68nF/50V NPO 4 QFN24_P5 15 LED_FB1

PWMO LED1 R468

5 14 LED_FB2

GND LED2

High : Enable R162

BKLT_PWM 6 13 LED_FB3

33K

Low : Disable 4.7K PWMI LED3

LED8

LED7

LED6

LED5

LED4

ISET

GND_LEDA

25 R466

BKLT_ON PAD 0

10

11

12

C167

D2 1N4148WS R163

LED_FB6

{17,18} LIDSW# 1000pF/50V,X7R 100K R467

LED_FB5

LED_FB4

GND_LEDA

A LEDVDD R470 0

62K A

R0402

{5,18,25} DELAY_ALL_PWROK D3 1N4148WS

GND_LEDA

YX Technology ZhengWei

{18} EC_LBKLT_EN R164 4.7K ns Title

<Title>

D4 1N4148WS ns

Size Project Name Rev

A3 N11 A

Date: Thursday, March 06, 2014 Sheet 14 of 30

5 4 3 2 1

5 4 3 2 1

+V3.3S

+V3.3S {6,7,8,12,13,14,16,17,18,19,23,24,25,26,28,29,30}

+V5S

+V5S {14,16,17,18,24,26,28}

+V3.3AUX {7,8,13,14,16,17,18,20,21,22,23,24,25,26}

+V1.5S {8,23}

+V1.8S {4,6,7,8,23,24,25,28,30}

+V1P8S_CODEC

+V1P8S_DACREF_CODEC +V3P3S_MICVDD

+V5S

+V1P8S_CODEC U52 +V1P2A_DCVDD +V1P8S_CODEC

FB1 3 42

MICVDD DCVDD 43 +V1.8S +V1P8S_CODEC

100ohm,100MHz,3A DBVDD

+VSPKVDD_CODEC 15 +V3P3S_MICVDD +VSPKVDD_CODEC

D AVDD 23 D

10 CPVDD R745

DACREF 27 CODEC_CPVEE 0

46 CPVEE C643 C644 C645 C646 C647

2 SPKVDDR 24 CODEC_CPVPP

SPKVDDL CPVPP 2.2uF/6.3V,X5R 0.1uF/16V,X7R

I2S_2_TXD 33 17 TP_CODEC_LINEOUT_C_R TP54 ns C648 0.1uF/16V,X7R 10uF/6.3V,X5R

{4,6} I2S_2_DOUT DACDAT1 LOUTR C649

I2S_2_RXD 34 16 TP_CODEC_LINEOUT_C_L TP53 ns

{6} I2S_2_RXD ADCDAT1 LOUTL 10uF/6.3V,X5R

I2S_2_CLK 36

{6} I2S_2_CLK BCLK1 2.2uF/6.3V,X5R

I2S_2_FS 35 7 HP_MIC_IN_C

{4,6} I2S_2_FRM LRCK1 IN2+ 8 JACK_DET_N 2.2uF/6.3V,X5R

I2S_0_TXD 31 IN2-/JD2 MICVDD GND_AUD

SPKVDD

{6} I2S_0_TXD DACDAT2

I2S_0_RXD 32 5 INT_MIC1_P

{6} I2S_0_RXD I2S_0_CLK 30 ADCDAT2 IN1+/DMIC1_DAT 6 INT_MIC1_N

{6} I2S_0_CLK BCLK2 IN1-/DMIC2_DAT/JD1

I2S_0_FS 29 GND_AUD

{6} I2S_0_FS LRCK2 26 HP_OUT_R

HPO_R HP_OUT_R {17} +V1P8S_CODEC +V1P8S_CODEC

I2C_CODEC_SDA 39 28 HP_OUT_L

{6} I2C_CODEC_SDA SDA HPO_L HP_OUT_L {17} +V1P2A_DCVDD

I2C_CODEC_SCL 38

{6} I2C_CODEC_SCL SCL 1 SPKR_LP

PLT_CLK3_I2SMCLK 37 SPO_L+ 48 SPKR_LN C653

{7} PLT_CLK3_I2SMCLK MCLK SPO_L- C650 C654 C655

C651 C652

I2S_IRQ_N 40 45 SPKR_RP

{7} I2S_IRQ_N DMIC_SCL 41 GPIO1/IRQ SPO_R+ 47 SPKR_RN SPKR_RP {17} 0.1uF/16V,X7R 0.1uF/16V,X7R

ns TP55 GPIO2/DMIC_SCL SPO_R- SPKR_RN {17} 0.1uF/16V,X7R 2.2uF/6.3V,X5R 10uF/6.3V,X5R

CODEC_RESET_N 44 13 TP_MONO_DP TP56 ns 2.2uF/6.3V,X5R

{6} CODEC_RESET_N RESET MONO+ 14 TP_MONO_DN TP57 ns

CODEC_VREF1 11 MONO-

CODEC_VREF2 12 VREF1 4 MIC_BIAS DBVDD CPVDD GND_AUD

C

VREF2 MICBIAS1 DCVDD C

C656 CPP1 20 25

C657 C658 CPN1 21 CPP1 HPOFB

2.2uF/6.3V,X5R CPN1 9

C659 CPP2 19 AGND 22

4.7uF/10V,X5R CPP2 CPGND

CPN2 18 R746 0 ns +V1P8S_CODEC +V1P8S_DACREF_CODEC

4.7uF/10V,X5R 2.2uF/6.3V,X5R CPN2 49

<E-PAD> SPKGND/DGND

GND_AUD

ALC5640

GND_AUD C660 C661 C662

GND_AUD 0.1uF/16V,X7R

qfn48_p4

I2S_0_CLK 0.1uF/16V,X7R

PLT_CLK3_I2SMCLK 10uF/6.3V,X5R

+V1P8S_CODEC

I2S_2_CLK

C663 C664C665

GND_AUD

AVDD DACREF GND_AUD

22pF/50V,NPO

22pF/50V,NPO

22pF/50V,NPO

R748

C666

10K

HP_MIC_IN_C 1uF/10V,X5R HP_MIC_IN

HP_MIC_IN {17}

+V1P8S_CODEC

CODEC_RESET_N

MIC_BIAS R749

2.2K

C667

4.7uF/10V,X5R

B R747 B

10K

GND_AUD

R756 0 ns

JACK_DET_N

MIC_BIAS R750

2.2K

R757

3

Q80

100K C668

INT_MIC1_P 1uF/10V,X5R INT_MIC1_P_C

BSS138 MIC1_P {17}

1 HP_JD {17} C669

150pF/50V,NPO

C670

2

INT_MIC1_N 1uF/10V,X5R INT_MIC1_N_C

R758 MIC1_N {17}

2.2K

ns

GND_AUD R751

3

2.2K

SPK_L 1 R752 0 R0603 SPKR_LP

3

W-B-2P-R 1 2 R753 0 R0603 SPKR_LN

2

4

HWS2_1P25R

4

A C673 C674 GND_AUD {17} A

680pF/25V,X7R

680pF/25V,X7R

YX Technology ZhengWei

Title

<Title>

GND Size Project Name Rev

A3 N11 A

Date: Thursday, March 06, 2014 Sheet 15 of 30

5 4 3 2 1

5 4 3 2 1

+V3.3AUX

+V3.3AUX

+V3.3S

+V3.3S {6,7,8,12,13,14,17,18,19,23,24,25,26,28,29,30}

+V5S

+V5S {14,15,17,18,24,26,28}

R194

+V3.3AUX R581

330 R582

+V3.3AUX {7,8,13,14,17,18,20,21,22,23,24,25,26} 330

330

+V1.5S

+V1.5S {8,23}

BAT_STATE_LED

S5_LED+

D D

RED

PWR_LED1

+V3.3AUX

BLUE LED BLUE CHARGE1

CHARGE2

LED2_0805 LED RED

LED RED

LED2_0805

R0603 LED2_0805

R494 0

R0603 ns

R496 0

+V3.3S ns Q17

AO3407

R0603 2 3

R493 0

C400 C239 C219

0.01uF/25V,X7R 10uF/6.3V,X5R 0.01uF/25V,X7R

1

R285 U33

3

10K R443 U32 PWR_LED R196 1

1K Q12 1

10K BTL_LED R587 1K Q72

1 6 R495 0 1 3 MMBT3904-F

VCC ANT ANT GND1 MMBT3904-F

2

3

2 2 R197

2

{12} USBDM2 3 D- GND2

Q61 WIFI 100K

{12} USBDP2 D+ 5 C397 ns

1 4 GND2 C393

{18} HW_RATIO_OFF_BT# R445 1K 1PF 0402

C GND1 1PF 0402 I-PEX 20279-001 C

2N7002K ns

ns ipexs3

AW-NU147SM

2

WIFI_6

SATA_LED# {6}

PWR_LED {18} +V3.3S

BTL_LED {18}

CAPLOCK# {18}

NUMLOCK# {18}

CAPLOCK# LED_CAP1 LED BLUE CAP+ LED_R1 330

LED2_0805

+V3.3S NUMLOCK# R497 0 LED_NUM1 LED BLUE NUM+

LED_R2 330 R0402

LED2_0805

R479 1K ns

B B

3

SATA_LED# R478 1K ns 1 Q65 1 Q64

MMBT3904-F MMBT3904-F

ns ns

2

Note:

MB pin1----DB pin1

LPCDBG1

使使使使12pin cable 88511-12XX

FPCE12_P5R

1

+V3.3S 1

LPC_AD0 2 {19} SSD_LED#

{6,18} LPC_AD0 3 2 13

LPC_AD1

{6,18} LPC_AD1 LPC_AD2 4 3 13

{6,18} LPC_AD2 LPC_AD3 5 4

{6,18} LPC_AD3 6 5

LPC_FRAME#

{6,18} LPC_FRAME# PLTRST# 7 6

{7,12,13,18} PLTRST# 8 7

9 8

{6,18} PCICLK_KBC 9

10 14

11 1014

+V5S 11

12

{6,18} SERIRQ 12

ns

TP18

ns

TP21

ns

TP19

ns

TP20

ns

TP22

ns

TP23

ns

TP24

A A

Aces 88511-12XX Debug YX Technology ZhengWei

Pitch 0.5mm Easy on FPC Title

<Title>

Size Project Name Rev

Custom N11 A

Date: Thursday, March 06, 2014 Sheet 16 of 30

5 4 3 2 1

5 4 3 2 1

+V1.8S {4,6,7,8,15,23,24,25,28,30}

+V3.3S {6,7,8,12,13,14,16,18,19,23,24,25,26,28,29,30}

+V5S {14,15,16,18,24,26,28}

+V5AUX {14,18,21,22,24,26}

+V3.3AUX {7,8,13,14,16,18,20,21,22,23,24,25,26}

+V5AUX

USB_VDDA

R207 0

R201 0 R0805 USB_VDDA

U12 CT2 C213

C214

RT9711AGB

4 3 USB3_RXN0_1 100uF/10V,TAN C386 C387

4 5 {6} USB3_RXN0

D VIN VOUT 1 2 USB3_RXP0_1 CT3528 0.1uF/16V,X7R 0.1uF/16V,X7R D

{6} USB3_RXP0 10uF/6.3V,X5R

RT9711AGB ns 10uF/6.3V,X5R

L4S2012 ns ns

R202 1.5A CHK3

R203 3 1 90ohm@100MHz,0.5A

0 EN FLG#

10K R435 0

GND

ns USB_GND

USB_GND ns R441 0

sot23_5

2

ns

C392 0.1uF/16V,X7R 4 3 USB3_TXN0_1 USB3

{6} USB3_TXN0

C391 0.1uF/16V,X7R 1 2 USB3_TXP0_1 USB_VDDA 1

{6} USB3_TXP0 VCC1

ns

CHK4 L4S2012 2

90ohm@100MHz,0.5A 3 -DATA1 10

R436 0 +DATA1 HOLE1 11

4 HOLE2 12

R206 0 GND HOLE3 13

USB3_RXN0_1 5 HOLE4

90ohm@100MHz,0.5A SSRX-

CHK2 USB3_RXP0_1 6

L4S2012 SSRX+

ns 7

1 2 GND2

{6} USB_PN0 USB3_TXN0_1 8

4 3 SSTX-

{6} USB_PP0 USB3_TXP0_1 9

SSTX+

1 1

R341 0

D27 D9

USB_GND CUS30-276-DP

EGA10603V05A1-B EGA10603V05A1-B

usb3h52in

2 2

C ns ns +V3.3S C

USB_GND

R209

+V5S 3.3K

ns

R213 0 R0603 Vfan FAN_TACH {18}

ns

Q13

5

BCP69T1

4

3 C1 2 3

E C 2

B

R214 1 HWS3_LPF2_1P25R

1K

1

FAN

0.1uF/16V,X7R

D10

C218

1N4148WS

4

88511-22xx TP58 ns 10uF/25V,X5R Wafer3P 1.0

IO_CN1 SOD323

C217

FPCE22_P5R

R216 R217

1K 5.11K,1%

22

22 PWR_SW_VCC {25} C220 ns

21 ns

21 LAN_TX0- {13} 0.1uF/16V,X7R

20

20 LAN_TX0+ {13}

19

19 LAN_TX1- {13}

18

8

18 LAN_TX1+ {13} U53A

17

17 3

16 +

16 USB_PP1 {6} VFAN_CTL 1

15

B 15 USB_PN1 {6} 2 R218 B

14 -

14 C221 10K,1%

13

13 0.1uF/16V,X7R LM358

24 12

4

24 12 11

11 +V5AUX

10

10 9 HP_JD {15}

23 9 8

23 8 HP_OUT_L {15} R219 100K FAN_VDC

7

7 6 HP_OUT_R {15}

6 5 MIC1_P {15}

5 MIC1_N {15} R220

4

4 HP_MIC_IN {15} 100K

3

3 GND_AUD {15} ns

2

2 1 SPKR_RP {17}

1 SPKR_RN {17} VFAN_CTL

+V3.3S

LIDSW#_IO

LIDSW# {14,18}

GND_AUD

+V5S

3

+V3.3AUX R221

3.3K

ns

R223 FAN_VDC 1 2N7002K

{18} FAN_PWM Q14

1K

8

U53B C222 ns

2

5 10uF/6.3V,X5R

DC_R1 DC__C1 +

7

51K 0.1uF/16V,X7R

6

DC_U1 ns C0402 -

A180

A LM358

SOT23 A

4

1

VS+

2 LIDSW#_IO

Output

GND

3 DC_C1

1000pF/50V,X7R

YX Technology ZhengWei

C0402 Title

<Title>

Size Project Name Rev

A3 N11 A

Date: Thursday, March 06, 2014 Sheet 17 of 30

5 4 3 2 1

5 4 3 2 1

+V5S {14,15,16,17,18,24,26,28}

+V3.3S {6,7,8,12,13,14,16,17,18,23,24,25,26,28,29,30}

+V1.5S {8,23}

+V3.3AUX {7,8,13,14,16,17,18,20,21,22,23,24,25,26}

D D

+V3.3S +V3.3S_SSD

R193

0

C203

C204 C205 C206 C207 C208

10uF/6.3V,X5R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R 0.1uF/16V,X7R

+V3.3S_SSD

SATA_CN1

NGFF SLOTB

SSD75_P5

77

77

1

2 CONFIG_3(GND) 3 TP63 ns

4 3.3V_0 GND0 5

C 3.3V_1 NC0 C

6 7

8 NC1 NC2 9

R195 0 ns 10 NC3 NC4 11

{16} SSD_LED# LED#/DAS/DSS# NC5

20 21

22 NC14 CONFIG_0(GND) 23 TP64 ns

24 NC15 NC16 25

26 NC17 NC18 27

28 NC19 GND1 29

30 NC20 NC21 31

32 NC22 NC23 33

34 NC24 GND2 35

36 NC25 NC26 37

38 NC27 NC28 39

ns TP60 40 DEVSLP GND3 41 0.01uF/25V,X7R C303

NC29 +B SATA_RXP0 {6}

42 43 0.01uF/25V,X7R C302

NC30 NGFF -B SATA_RXN0 {6}

44 SLOTB 45

46 NC31 GND4 47 SATA_TXN0

NC32 -A SATA_TXN0 {6}

48 49 SATA_TXP0

50 NC33 SSD +A 51

SATA_TXP0 {6}

52 NC34 GND5 53

54 NC35 NC36 55

56 NC37 NC38 57

ns TP61 58 NC49/SCL GND6 59

ns TP62 60 NC50/SDA NC39 61

62 NC40 NC41 63

B B

64 NC42 NC43 65

66 NC44 NC45 67

68 NC46 NC47 69

70 NC48 CONFIG_1(GND) 71 TP65 ns

+V3.3S_SSD 3.3V_2 GND7

72 73

74 3.3V_3 GND8 75

3.3V_4 CONFIG_2(GND) TP66 ns

76

76

A A

YX Technology ZhengWei

Title

<Title>

Size Project Name Rev

A3 N11 A

Date: Thursday, March 06, 2014 Sheet 19 of 30

5 4 3 2 1

5 4 3 2 1

D11

SSM34PT

SMA

D12 D13

ns

DCJACK1

AD+ SSM34PT SSM34PT ns

63100203A SMA

VIN+ SMA

BAT+

D dcj5d64x125_H54 D

D14 Q18

3.5A 6

5 1 4 5

SHLD2 AD+ 2

4 1

SHLD1 0.01uF/25V,X7R 0.01uF/25V,X7R SSM34PT

SMA STT3423P

3 C246 C247

AD-2

3

AD-1 AD+

C248 C249 ns 30V/25V

6.7A/35mohm

2

ns

2200pF/25V,X7R 4700pF/25V,X7R

ns R286 0 VIN+ {27}

ns

+VDC BAT+ {27}

+VDC {14,21,22,24,25,26}

+V3.3AUX {7,8,13,14,16,17,18,21,22,23,

Q19

6

R287

4 5

30.1K,1%

2

R0402

1

ns

STT3423P

3

R288 C250 ns

100K

1000pF/50V,X7R

ns ns

C C

+V3.3AUX AD+

R289

200K

ns

R290

3

30.1K,1%

Q21 R0402

3

2N7002K

Q20

SOT23 1

2N7002K ALW_EN {21}

1 SOT23

{21} SHDN#

2

C251

ns R292 1K R293 1000pF/50V,X7R

2

R291 {18} AC_IN

C252 20K

470K

R0402

1000pF/50V,X7R

ns C253

ns

1000pF/50V,X7R R294

20K

B B

BAT+

C254 C255

C388 C389

0.1uF/25V,Y5V 0.1uF/25V,Y5V

0.1uF/25V,Y5V 0.1uF/25V,Y5V

C0402 C0402

C0402 C0402

ns ns M_BAT_TEM

8

3.3V No Battery

1

BATT+

0.5V - 2.5V Battery IN

BATT+ 2

BATCON1 < 0 .5V Battery Fail

88231-07XXX-XX 3 R295 75 EC_SMB2_DAT

SDAT EC_SMB2_DAT {18}

4 R296 75 EC_SMB2_CLK

SCLK EC_SMB2_CLK {18}

hws7_lpf2_1p25r

TEMP 5 R297

BAT_TEM {18}

BAT_IN# 75

6 C256

GND C257 C258

1000pF/50V,X7R

5.6pF/50V,NPO 5.6pF/50V,NPO

7 R298

GND ns

A 10K A

9

+V3.3AUX

YX Technology ZhengWei

Title

<Title>

Size Project Name Rev

A3 N11 A

Date: Thursday, March 06, 2014 Sheet 20 of 30

5 4 3 2 1

5 4 3 2 +V3.3AUX 1

+VDC {14,20,22,24,25,26}

R299 0 ns

R300 +V3.3AUX {7,8,13,14,16,17,18,20,22,23,24,25,26}

+V5AUX 4.7K

+V5AUX {14,17,18,22,24,26}

PM_RSMRST# {7,18}

+V1.8AUX {6,7,8}

R301

+V1.0AUX {8}

3

+V3.3AUX 47K

Q22

2N7002K

1 SOT23

GND_Aux

R302

2

3

D 47K

Q23 D

2N7002K

AUX_POK R303 0 1 SOT23

2

C259

C0603

CH1:300KHz CH2:375KHz R304 R305

2.2uF/6.3V,X5R

20K,1% 20K,1%

C260

1uF/10V,X5R

R306 30.1K,1% R307 13.3K,1%

2.0V

GND_Aux R308 200K V5A_ON V3A_ON R309 200K GND_Aux

3V_LDO

OCP

25

1

6

+VDC +VDC

1A 1A

EN1

VFB1

VREF

TON

VFB2

EN2

PAD

24 7

VO1 VO2 C264 C265

C261 C262 AUX_POK 23 8 3V_LDO C263 0.1uF/25V,Y5V 10uF/25V,X5R +V3.3AUX

C0402 C1206 PGOOD VREG3 4.7uF/10V,X5R C0805 C0402 C1206

7

0.1uF/25V,Y5V 10uF/25V,X5R C266 0.1uF/16V,X7R 22 9

+V5AUX D1 D1 VBST1 U18 VBST2 C267 0.1uF/16V,X7R D1 D1

2 21 TPS51125RGE 10 2

DH1 QFN24_P5 DH2

1G G1

S1 V5A_LX 20 11 V3A_LX S1

LL1 LL2 P33AUX1

EPI 0603H-6R8M-K01 L1

6 1 19 12 1 6 V3A_LX

C C

VREG5

P5AUX1 DL1 DL2

VCLK

L2

SKIP

GND

EN0

VIN

V5A_LX 5 5 4.7uH/5.5A CC:5A

CKS2D66 PWR_PAD

CC:5A 4.7uH/5.5A D2 D2 23.3mohm OC:8A OPEN15X50

18

17

16

15

14

13

PWR_PAD CKS2D66 4 4 EPI 0603H-4R7M-K01 C268 + + C271 ns

OC:6.8A OPEN15X50

D15 37mohm CESD66 220uF/6.3V/18mohm D16

ns + C270 Q24 S2 G2 G2 S2 Q25 220uF/6.3V,FPCAP CT7343_19 BZT52C3V6S

C269 + BZT52C5V6S

220uF/6.3V/18mohm SSG4920N SSG4920N EEFCX0J151R SOD323

CESD66

3

3

220uF/6.3V,FPCAP

CT7343_19 SOD323 SOIC8_1P27_3P9 30V/20V SOIC8_1P27_3P9

EEFCX0J151R +VDC ns

6.9A/34mohm R310 0 30V/20V 叠放在一起

6.1nC ns

ns 6.9A/34mohm

8.2A/28mohm

R311 OOA Auto SKIP 6.1nC

5.8nC 0 8.2A/28mohm

2.3A

5.8nC

5V_LDO 2.3A

C272 C273

C0805 C0805 +V3.3AUX

4.7uF/10V,X5R 4.7uF/10V,X5R

SOIC8_1P27_3P9G

APL5337KA

U19

R312 1 8

C274 VIN NC3

PD1 22.6K,1%

0.1uF/16V,X7R +V3.3AUX

1 R313 0 2 7

{18,21} ALWAYS_ON C0402 GND NC2

R0603

3 3 6

VREF VCNTL

2 U20 4 5 C276

PAD

{20} ALW_EN AME8818AEET180Z VOUT NC1

GND_Aux +V3.3AUX R314 1uF/10V,X5R

SOT23 C275

BAT54C 10K,1%

0.1uF/16V,X7R

1 C0402

9

GND +V1.8AUX

R315

B {25} PWRSWVCC_MBXP

PD2

1K

3

IN B

2

SOD323 OUT

1N4148WS +V1.0AUX

C277 C278

2.2uF/6.3V,X5R 2.2uF/6.3V,X5R

5V_LDO

C279

C0805

R316 0 ns 10uF/6.3V,X5R

{20} SHDN# V5A_ON

R317

3

20K

Q26

2N7002K C280

1 SOT23 0.01uF/25V,X7R

2

3

Q27

2N7002K

R318 0 RST# 1 SOT23

{18,21} ALWAYS_ON

V3A_ON

ns

2

R319 Q28

470K 2N7002K

ns 1 SOT23 C281

0.1uF/16V,X7R

2

5

6

SWS6D50

A 1 2TMG-533-V A

3 4 RST#

RST_SW1

V5REF must be powered up before Vcc3_3, or after

Vcc3_3 within 0.7 V. Also, V5REF must power down after

Vcc3_3, or before Vcc3_3 within 0.7 V (CRB=1.48ms)

YX Technology ZhengWei

Title

<Title>

Size Project Name H14 Rev

C N11 A

Date: Thursday, March 06, 2014 Sheet 21 of 30

5 4 3 2 +V_DDR {5,8,10,23,24}

1

+VDC {14,20,21,24,25,26}

+V5AUX {14,17,18,21,24,26}

+V3.3AUX {7,8,13,14,16,17,18,20,21,23,24,25,26}

+V1.0S {6,8,23,24,25,26}

D D

R320 0 +VDC

R0603

+V3.3AUX 2A

GND_IC

C284 C285 C286 C287

C0402 C1206 C0402 2200pF/25V,X7R

30V/20V 0.1uF/25V,Y5V 10uF/25V,X5R 0.1uF/25V,Y5V ns

R321 ns

18.9A/10mohm

5

6

7

8

10K U22

8.8nC

D

TPS51218DSC

ns QFN10_P5G C288 Q29 +V_DDR

10 0.1uF/16V,X7R 4 SI4800BDY_AO4468

G

1 10 SOIC8_1P27_3P9

{10} V1_5_PWROK PGOOD VBST

S

R322

GND_IC R323 2 9 L3 8A

3

2

1

TRIP DRVH

R324 OCP 13A 200K

1K 3 8

{18} V1_5_ON EN SW

5

6

7

8

2.2uH/8A

D

GND_IC R325 4 7 +V5AUX C0402 CKS2D66

VFB V5IN

C 10K,1%

0.7V 5 6

1uF/10V,X5R C289

4

Q30 2.2mohm

SI4800BDY_AO4468FEPI 1003H-R56M-Z01

D17 C

PAD

RF DRVL BZT52C2V0S

G

SOIC8_1P27_3P9

SOD323

S

+ + C293

C291

11

3

2

1

R326 R327

100pF/50V,NPO 30V/20V C292 CESD66

C290 9.31K,1% 100K 220uF/2V/15mohm 220uF/6.3V,FPCAP

C0402 28A/5.1mohm

0.1uF/16V,X7R 380KHz CT7343_19 ns

C0402 GND_IC 21.5nC

ns Is<40A

ns

GND_IC

EEFCD0D221ER 220uF/2V/18mohm

EEFSX0D221R 220uF/2V/9mohm

EEFCX0D221R

B B

A A

YX Technology ZhengWei

Title

<Title>

Size Project Name Rev

A3 N11 A

Date: Thursday, March 06, 2014 Sheet 22 of 30

5 4 3 2 1

+VDC {14,20,21,22,24,25,26}

+V5AUX {14,17,18,21,22,24,26}

+V1.05S {8,24}

+V3.3AUX {7,8,13,14,16,17,18,20,21,22,24,25,26}

+V3.3S {6,7,8,12,13,14,16,17,18,19,24,25,26,28,29,30}

+V_DDR +V1.8S {4,6,7,8,15,24,25,28,30}

SOIC8_1P27_3P9G +V_DDR {5,8,10,22,24}

+V1.2S {8}

APL5337KA

+V1.5S {8}

U24 +V1.0S {6,8,24,25,26}

C301

R334 1 8

C300 1uF/10V,X5R VIN NC3

D 0.1uF/16V,X7R

1K,1%

2 7 +V3.3AUX U26

D