Professional Documents

Culture Documents

Synchronous Step Down Converter: High Efficiency 3A, 24V, 500Khz

Synchronous Step Down Converter: High Efficiency 3A, 24V, 500Khz

Uploaded by

Anonymous 8bbVmLtQCopyright:

Available Formats

You might also like

- Dark Winter ImprimirDocument3 pagesDark Winter Imprimirsunayhernandez1No ratings yet

- 2A, 55V, 100Khz Step-Down ConverterDocument12 pages2A, 55V, 100Khz Step-Down Convertermichael8710No ratings yet

- U1 Xbox OneDocument14 pagesU1 Xbox OneCheckpoint Game CenterNo ratings yet

- Fast Turn-Off Intelligent Rectifier With No Need For Auxiliary Winding Description FeaturesDocument14 pagesFast Turn-Off Intelligent Rectifier With No Need For Auxiliary Winding Description FeaturesKwun Hok ChongNo ratings yet

- LM2621 Low Input Voltage, Step-Up DC-DC Converter: 1 Features 3 DescriptionDocument17 pagesLM2621 Low Input Voltage, Step-Up DC-DC Converter: 1 Features 3 DescriptionSatyashiba Sundar JenaNo ratings yet

- MP8719 6600xt SaphireDocument22 pagesMP8719 6600xt Saphiretechgamebr85No ratings yet

- Primary-Side Control, Offline LED Controller With Active PFC, NTC and PWM DimmingDocument19 pagesPrimary-Side Control, Offline LED Controller With Active PFC, NTC and PWM Dimmingzuffflor_925748656No ratings yet

- 2A, 24V Input, 600Khz 2/3-Cell Switching Li-Ion Battery ChargerDocument16 pages2A, 24V Input, 600Khz 2/3-Cell Switching Li-Ion Battery Charger123No ratings yet

- MAX77680 Datasheet and Technical InfoDocument9 pagesMAX77680 Datasheet and Technical InfojackNo ratings yet

- Offline, Primary-Side Regulator With CC/CV Control and A 700V MOSFETDocument21 pagesOffline, Primary-Side Regulator With CC/CV Control and A 700V MOSFETsluz2000No ratings yet

- MP9943Document20 pagesMP9943techgamebr85No ratings yet

- MP3389 r1.04Document16 pagesMP3389 r1.04Andres Alegria100% (1)

- Transition-Mode PFC Controller: FeaturesDocument25 pagesTransition-Mode PFC Controller: FeaturesRodrigo BonfanteNo ratings yet

- Max8732a Max8734a PDFDocument33 pagesMax8732a Max8734a PDFmirandowebsNo ratings yet

- MAQ3203YM Evaluation Board User GuideDocument23 pagesMAQ3203YM Evaluation Board User GuideJohnNo ratings yet

- TSX712Document31 pagesTSX712lugitecNo ratings yet

- SGM4812Document11 pagesSGM4812Fernando Martin GaivazziNo ratings yet

- USB On-the-Go Transceivers and Charge Pumps: General Description FeaturesDocument38 pagesUSB On-the-Go Transceivers and Charge Pumps: General Description FeaturesBilal InfotexNo ratings yet

- MP6515Document13 pagesMP6515gaatje niks aanNo ratings yet

- Max20050-Max20053 2A Synchronous-Buck Led Drivers With Integrated MosfetsDocument23 pagesMax20050-Max20053 2A Synchronous-Buck Led Drivers With Integrated MosfetsAdrian WongNo ratings yet

- Multi-Output, Low-Noise Power-Supply Controllers For Notebook ComputersDocument28 pagesMulti-Output, Low-Noise Power-Supply Controllers For Notebook ComputersAleksNo ratings yet

- Recommended For New Designs Refer T O Mp2331H: 0.5A, 24V, 1.4Mhz Step-Down Converter in A Tsot23-6Document11 pagesRecommended For New Designs Refer T O Mp2331H: 0.5A, 24V, 1.4Mhz Step-Down Converter in A Tsot23-6jeanneNo ratings yet

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDocument10 pagesNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânNo ratings yet

- General Description Features: High Performance Current Mode PWM ControllerDocument11 pagesGeneral Description Features: High Performance Current Mode PWM ControllerPhạm Tấn HảiNo ratings yet

- MAX17411 MaximIntegratedDocument72 pagesMAX17411 MaximIntegratedRoberto MouraNo ratings yet

- 100V Input, 1A High Power LED Driver: The Future of Analog IC TechnologyDocument10 pages100V Input, 1A High Power LED Driver: The Future of Analog IC TechnologyAdrian WongNo ratings yet

- A3121 2 3 Datasheet PDFDocument9 pagesA3121 2 3 Datasheet PDFAsad IqbalNo ratings yet

- MP1488Document11 pagesMP1488Jaime Andres Aranguren CardonaNo ratings yet

- NB676 DatasheetDocument19 pagesNB676 DatasheetRudy BudimanNo ratings yet

- Bd71837amwv eDocument129 pagesBd71837amwv eChip KitNo ratings yet

- Nxpusainc Mc33926pnb Datasheets 8993Document35 pagesNxpusainc Mc33926pnb Datasheets 8993Nooragha TanhaNo ratings yet

- LM3530 High Efficiency White LED Driver With Programmable Ambient Light Sensing Capability and I C-Compatible InterfaceDocument45 pagesLM3530 High Efficiency White LED Driver With Programmable Ambient Light Sensing Capability and I C-Compatible Interfacethoth2487No ratings yet

- 1.5Mhz, 30A High-Efficiency, Led Driver With Rapid Led Current PulsingDocument25 pages1.5Mhz, 30A High-Efficiency, Led Driver With Rapid Led Current PulsingDummy CekNo ratings yet

- MTC 2 eDocument8 pagesMTC 2 eravikumarrkNo ratings yet

- TinyNode Users Manual Rev11 01Document30 pagesTinyNode Users Manual Rev11 01fantomagaNo ratings yet

- 24V, High Current Synchronous Step-Down Converter: The Future of Analog IC TechnologyDocument20 pages24V, High Current Synchronous Step-Down Converter: The Future of Analog IC TechnologyRinaldyNo ratings yet

- MLX91205 DatasheetDocument14 pagesMLX91205 DatasheetRicardo ReisNo ratings yet

- Description/ordering Information: 1out 1IN 1IN+ GND V 2out 2IN 2IN+Document18 pagesDescription/ordering Information: 1out 1IN 1IN+ GND V 2out 2IN 2IN+javierrincon800No ratings yet

- Lmx31X Precision Voltage-To-Frequency Converters: 1 Features 3 DescriptionDocument23 pagesLmx31X Precision Voltage-To-Frequency Converters: 1 Features 3 DescriptionAlonso Herrera SeguraNo ratings yet

- Max16833 Max16833gDocument25 pagesMax16833 Max16833gKwun Hok ChongNo ratings yet

- LM3243 High-Current Step-Down Converter For 2G, 3G, and 4G RF Power AmplifiersDocument32 pagesLM3243 High-Current Step-Down Converter For 2G, 3G, and 4G RF Power Amplifiersgotcha75No ratings yet

- SGM706Document12 pagesSGM706Sveto SlNo ratings yet

- D D D D D D D D D: DescriptionDocument18 pagesD D D D D D D D D: DescriptionNalin Lochan GuptaNo ratings yet

- D D D D D D D D: DescriptionDocument10 pagesD D D D D D D D: DescriptionVíctor LópezNo ratings yet

- LM 318Document11 pagesLM 318Diego LeeNo ratings yet

- 5ppm, I C Real-Time Clock: General Description FeaturesDocument20 pages5ppm, I C Real-Time Clock: General Description FeaturesJosueChalenSarezNo ratings yet

- Max2680/Max2681/ Max2682 400Mhz To 2.5Ghz, Low-Noise, Sige Downconverter MixersDocument12 pagesMax2680/Max2681/ Max2682 400Mhz To 2.5Ghz, Low-Noise, Sige Downconverter MixersDusan PejicNo ratings yet

- Summary ClockDocument39 pagesSummary ClockmikcomiNo ratings yet

- Rail-To-Rail 1.8 V High-Speed Dual Comparator: FeaturesDocument20 pagesRail-To-Rail 1.8 V High-Speed Dual Comparator: FeaturesshhmmmNo ratings yet

- Low-Power Single Operational Amplifier: DescriptionDocument15 pagesLow-Power Single Operational Amplifier: Descriptionchad tan100% (1)

- Power Power: Designer DesignerDocument8 pagesPower Power: Designer DesignerNeha JainNo ratings yet

- Multisim AvanzadoDocument35 pagesMultisim AvanzadoedgarfransNo ratings yet

- SPX3819 LdoDocument14 pagesSPX3819 LdoMistaNo ratings yet

- (BISS) TransistorsDocument12 pages(BISS) TransistorsMiloud ChouguiNo ratings yet

- MAX3051Document13 pagesMAX3051Mirko GalićNo ratings yet

- Pont en HDocument17 pagesPont en Hapi-288039470No ratings yet

- MP2225GJ-Z Circuito IntegratoDocument20 pagesMP2225GJ-Z Circuito IntegratoMimmo FracchiollaNo ratings yet

- DRV 8811Document22 pagesDRV 8811nelson_loboNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- DV 410V K OperatingInstructions0418Document101 pagesDV 410V K OperatingInstructions0418Anonymous 8bbVmLtQNo ratings yet

- Zte Cabinets: Knowledge Sharing SessionsDocument41 pagesZte Cabinets: Knowledge Sharing SessionsAnonymous 8bbVmLtQNo ratings yet

- Installation and Operating Manuals: For Further Information and Up To Date Documentation Please VisitDocument1 pageInstallation and Operating Manuals: For Further Information and Up To Date Documentation Please VisitAnonymous 8bbVmLtQNo ratings yet

- Samsung Sm-t211 Service ManualDocument52 pagesSamsung Sm-t211 Service ManualAnonymous 8bbVmLtQ75% (4)

- Writing An Application LetterDocument6 pagesWriting An Application LetterNur AmaliaNo ratings yet

- Fire Detection With Image ProcessingDocument6 pagesFire Detection With Image ProcessingIJRASETPublicationsNo ratings yet

- Assignment 2 Front Sheet: Qualification BTEC Level 5 HND Diploma in Computing Unit Number and Title Submission DateDocument29 pagesAssignment 2 Front Sheet: Qualification BTEC Level 5 HND Diploma in Computing Unit Number and Title Submission DateCục MuốiNo ratings yet

- CS001 Computer Proficiency All Midterm Solved Objective and Subjective Papers in One File For Preparation of Midterm ExamDocument0 pagesCS001 Computer Proficiency All Midterm Solved Objective and Subjective Papers in One File For Preparation of Midterm ExamQazi Khubaib Alam100% (1)

- SAPDocument32 pagesSAPAnjali RanaNo ratings yet

- Confluence Interview Questions and AnswersDocument6 pagesConfluence Interview Questions and AnswerssayraNo ratings yet

- Pro-Shock Waves Pro-Shock Waves: The Most Versatile Shockwaves EverDocument2 pagesPro-Shock Waves Pro-Shock Waves: The Most Versatile Shockwaves EverPrie AjeNo ratings yet

- Influencing Ethical Culture Through A Multi-Channel Compliance ProgramDocument7 pagesInfluencing Ethical Culture Through A Multi-Channel Compliance ProgramAnn AllsoppNo ratings yet

- Learning Go LatestDocument112 pagesLearning Go LatestGaurav ChaturvediNo ratings yet

- 87-351 Lecture 11 NotesDocument10 pages87-351 Lecture 11 NotesAmritpal GillNo ratings yet

- MPI The Best Possible PractiseDocument5 pagesMPI The Best Possible Practisekam_anwNo ratings yet

- MNM3709 SummaryDocument4 pagesMNM3709 SummarynoxaNo ratings yet

- Ethernet Communication Module: Application ManualDocument11 pagesEthernet Communication Module: Application ManualSilvia MaribelNo ratings yet

- As 3822-2002 Test Methods For Bare Overhead ConductorsDocument29 pagesAs 3822-2002 Test Methods For Bare Overhead ConductorsCristian WalkerNo ratings yet

- PowerOn Fusion PDFDocument16 pagesPowerOn Fusion PDFJagan VanamaNo ratings yet

- Kakatiya University, Warangal 2020 PDFDocument2 pagesKakatiya University, Warangal 2020 PDFAkHilkumar BoragalaNo ratings yet

- Computer1 - Lesson 1 - THE WORDPAD PROGRAM - 000Document4 pagesComputer1 - Lesson 1 - THE WORDPAD PROGRAM - 000Alyessa Dawn FalladoNo ratings yet

- Brother CP1800, CP2000, CB200 Service Manual PDFDocument92 pagesBrother CP1800, CP2000, CB200 Service Manual PDFStefanNo ratings yet

- Turban 02Document88 pagesTurban 02Ayu Saida ZulfaNo ratings yet

- Working With Algebra Tiles (Project)Document8 pagesWorking With Algebra Tiles (Project)Ruben Serna CNo ratings yet

- ANSYS 9.0 - Installation ProcedureDocument26 pagesANSYS 9.0 - Installation Proceduresanthoshjoys50% (2)

- The RANDOM Statement and More Moving On With PROC MCMCDocument21 pagesThe RANDOM Statement and More Moving On With PROC MCMCarijitroyNo ratings yet

- Applications of Artificial Intelligence For Disaster ManagementDocument59 pagesApplications of Artificial Intelligence For Disaster ManagementCARLOSNo ratings yet

- Oumm3203 Professional EthicsDocument11 pagesOumm3203 Professional Ethicsdicky chongNo ratings yet

- Minimum Automotive Quality Management System Requirements For Sub Tier Suppliers 2nded Rev2Document8 pagesMinimum Automotive Quality Management System Requirements For Sub Tier Suppliers 2nded Rev2R JNo ratings yet

- CS224d - Assignment 2Document3 pagesCS224d - Assignment 2Aalok GangopadhyayNo ratings yet

- LP621024D Series: 128K X 8 Bit Cmos SramDocument16 pagesLP621024D Series: 128K X 8 Bit Cmos SramClaudiney BricksNo ratings yet

- Cosine Effect DetailsDocument3 pagesCosine Effect DetailsZohaib HassanNo ratings yet

- 27C512Document12 pages27C512technicalavrNo ratings yet

Synchronous Step Down Converter: High Efficiency 3A, 24V, 500Khz

Synchronous Step Down Converter: High Efficiency 3A, 24V, 500Khz

Uploaded by

Anonymous 8bbVmLtQOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Synchronous Step Down Converter: High Efficiency 3A, 24V, 500Khz

Synchronous Step Down Converter: High Efficiency 3A, 24V, 500Khz

Uploaded by

Anonymous 8bbVmLtQCopyright:

Available Formats

MP2325

High Efficiency 3A, 24V, 500kHz

Synchronous Step Down Converter

The Future of Analog IC Technology

DESCRIPTION FEATURES

The MP2325 is a high frequency synchronous Wide 4.5V to 24V Operating Input Range

rectified step-down switch mode converter with 90mΩ/40mΩ Low Rds(on) Internal Power

built in internal power MOSFETs. It offers a MOSFETs

very compact solution to achieve 3A continuous Low Quiescent Current

output current over a wide input supply range High Efficiency Synchronous Mode

with excellent load and line regulation. The Operation

MP2325 has synchronous mode operation for Fixed 500kHz Switching Frequency

higher efficiency over output current load range. Frequency Sync from 200kHz to 2MHz

Current mode operation provides fast transient External Clock

response and eases loop stabilization. Power Save Mode at light load

Internal Soft Start

Full protection features include OCP and

thermal shut down. Power Good Indicator

OCP Protection and Hiccup

The MP2325 requires a minimum number of Thermal Shutdown

readily available standard external components Output Adjustable from 0.8V

and is available in a space saving 8-pin Available in an 8-pin TSOT-23 package

TSOT23 package.

APPLICATIONS

Notebook Systems and I/O Power

Digital Set Top Boxes

Flat Panel Television and Monitors

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green

status, please visit MPS website under Products, Quality Assurance page.

“MPS” and “The Future of Analog IC Technology” are registered trademarks of

Monolithic Power Systems, Inc.

TYPICAL APPLICATION

MP2325 Rev. 1.01 www.MonolithicPower.com 1

10/25/2018 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

MP2325 – 24V, 3A SYNC STEP DOWN CONVERTER

ORDERING INFORMATION

Part Number* Package Top Marking

MP2325GJ TSOT23-8 See Below

* For Tape & Reel, add suffix –Z (e.g. MP2325GJ–Z);

TOP MARKING

AKE: product code of MP2325GJ

Y: year code

PACKAGE REFERENCE

TOP VIEW

PG 1 8 FB

IN 2 7 VCC

SW 3 6 EN/SYNC

GND 4 5 BST

TSOT23-8

ABSOLUTE MAXIMUM RATINGS (1) Thermal Resistance (4) θJA θJC

VIN ................................................. –0.3V to +28V TSOT23-8…………………...…….100…..55..°C/W

VSW ....... –0.3V (-5V<10ns) to +28V (30V <10ns) Notes:

VBST.......................................................... VSW+6V 1) Exceeding these ratings may damage the device.

All Other Pins .................................. -0.3V to +6V 2) The maximum allowable power dissipation is a function of the

maximum junction temperature TJ (MAX), the junction-to-

Continuous Power Dissipation (TA=+25°C) (2) ... ambient thermal resistance θJA, and the ambient temperature

................................................................... 1.25W TA. The maximum allowable continuous power dissipation at

any ambient temperature is calculated by PD (MAX) = (TJ

Junction Temperature ............................... 150°C (MAX)-TA)/θJA. Exceeding the maximum allowable power

Lead Temperature .................................... 260°C dissipation will cause excessive die temperature, and the

regulator will go into thermal shutdown. Internal thermal

Storage Temperature .................. -65°C to 150°C shutdown circuitry protects the device from permanent

damage.

Recommended Operating Conditions (3) 3) The device is not guaranteed to function outside of its

Supply Voltage VIN .............................. 4.5 to 24V operating conditions.

4) Measured on JESD51-7, 4-layer PCB.

Output Voltage VOUT .................. 0.8V to VIN*DMAX

Operating Junction Temp (TJ). .-40°C to +125°C

MP2325 Rev. 1.01 www.MonolithicPower.com 2

10/25/2018 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

MP2325 – 24V, 3A SYNC STEP DOWN CONVERTER

ELECTRICAL CHARACTERISTICS

VIN = 12V, TA = 25°C, unless otherwise noted.

Parameter Symbol Condition Min Typ Max Units

Supply Current (Shutdown) IIN VEN = 0V 5.5 μA

Supply Current (Quiescent) Iq VEN = 2V, VFB = 1V 130 180 240 μA

HS Switch On Resistance HSRDS-ON VBST-SW=5V 90 mΩ

LS Switch On Resistance LSRDS-ON VCC=5V 40 mΩ

Switch Leakage SWLKG VEN = 0V, VSW =12V 1 μA

Current Limit (5) ILIMIT Duty Cycle=40% 4.5 5.5 6.5 A

Oscillator Frequency fSW VFB=750mV 420 500 620 kHz

Fold-back Frequency fFB VFB=200mV 0.5 fSW

Maximum Duty Cycle DMAX VFB=750mV 90 95 %

Minimum On Time (5) TON_MIN 60 ns

Sync Frequency Range fSYNC 0.2 2 MHz

Feedback Voltage VFB TA=25ºC 783 791 799 mV

Feedback Current IFB VFB=820mV 10 50 nA

EN Rising Threshold VEN_RISING 1.2 1.4 1.6 V

EN Hysteresis VEN_HYS 80 150 220 mV

VEN=2V 1.5 2 2.5 μA

EN Input Current IEN

VEN=0 0 50 nA

EN Turn Off Delay ENTd-off 6 10 14 μs

Power Good Rising Threshold PGVTH-Hi 0.9 VFB

Power Good Falling Threshold PGVTH-LO 0.85 VFB

Power Good Delay PGTd 40 μs

Power Good Sink Current

VPG Sink 1mA 0.4 V

Capability

Power Good Leakage Current IPG-LEAK 1 μA

VIN Under Voltage Lockout

INUVVth 3.7 3.9 4.1 V

Threshold-Rising

VIN Under Voltage Lockout

INUVHYS 550 650 750 mV

Threshold-Hysteresis

VCC Regulator VCC 4.65 4.9 5.15 V

VCC Load Regulation ICC=5mA 0 1 3 %

Soft-Start Period TSS 0.8 1.5 2.2 ms

Thermal Shutdown(5) 150 ºC

Thermal Hysteresis(5) 20 ºC

Notes:

5) Guaranteed by design

MP2325 Rev. 1.01 www.MonolithicPower.com 3

10/25/2018 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

MP2325 – 24V, 3A SYNC STEP DOWN CONVERTER

TYPICAL CHARACTERISTICS

VIN = 12V, VOUT = 3.3V, L = 4.9μH, TA = 25°C, unless otherwise noted.

MP2325 Rev. 1.01 www.MonolithicPower.com 4

10/25/2018 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

MP2325 – 24V, 3A SYNC STEP DOWN CONVERTER

TYPICAL PERFORMANCE CHARACTERISTICS

VIN = 12V, VOUT = 3.3V, L = 4.9μH, TA = 25°C, unless otherwise noted.

MP2325 Rev. 1.01 www.MonolithicPower.com 5

10/25/2018 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

MP2325 – 24V, 3A SYNC STEP DOWN CONVERTER

TYPICAL PERFORMANCE CHARACTERISTICS (continued)

VIN = 12V, VOUT = 3.3V, L = 4.9µH, TA = 25°C, unless otherwise noted.

MP2325 Rev. 1.01 www.MonolithicPower.com 6

10/25/2018 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

MP2325 – 24V, 3A SYNC STEP DOWN CONVERTER

PIN FUNCTIONS

Package

Name Description

Pin #

Power Good Output. The output of this pin is an open drain. It’s pulled up to Vcc by

1 PG external resistor when the output voltage exceeds 90% of the normal voltage. There is a

40μs delay between FB≥90% to the PG pin goes high.

Supply Voltage. The IN pin supplies power for internal MOSFET and regulator. The

MP2325 operates from a +4.5V to +24V input rail. Requires a low-ESR, and low

2 IN

inductance capacitor (C1) to decouple the input rail. Place the input capacitor very close to

this pin and connect it with wide PCB traces and multiple vias.

Switch Output. Connect to the inductor and bootstrap capacitor. This pin is driven up to

VIN by the high-side switch during the PWM duty cycle ON time. The inductor current

3 SW drives the SW pin negative during the OFF time. The ON resistance of the low-side switch

and the internal body diode fixes the negative voltage. Connect using wide PCB traces and

multiple vias.

System Ground. This pin is the reference ground of the regulated output voltage.

4 GND For this reason care must be taken in PCB layout. Suggested to be connected to GND with

copper and vias.

Bootstrap. A capacitor and a 20Ω resistor connected between SW and BST pins are

5 BST

required to form a floating supply across the high-side switch driver.

EN=1 to enable the MP2325. External clock can be applied to EN pin for changing

6 EN/SYNC

switching frequency. For automatic start-up, connect EN pin to VIN with a 100kΩ resistor.

Bias Supply. Decouple with 0.1μF-0.22μF cap. And the capacitance should be no more

7 VCC

than 0.22μF

Feedback. An external resistor divider from the output to GND, tapped to the FB pin, sets

the output voltage. To prevent current limit run away during a short circuit fault condition

8 FB

the frequency fold-back comparator lowers the oscillator frequency when the FB voltage is

below 400mV.

MP2325 Rev. 1.01 www.MonolithicPower.com 7

10/25/2018 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

MP2325 – 24V, 3A SYNC STEP DOWN CONVERTER

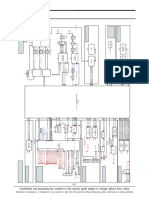

FUNCTION BLOCK DIAGRAM

IN

+

-

VCC RSEN

VCC Currrent Sense

Regulator

Amplifer

Bootstrap

Regulator BST

Oscillator HS

Driver

+

SW

- Comparator

1pF On Time Control VCC

Current Limit Logic Control

50pF

Comparator

EN/SYNC Reference 400k

LS

6.5V 1MEG

Driver

+

+

FB -

- Error Amplifier GND

PG + Ref

Figure 1: Functional Block Diagram

MP2325 Rev. 1.01 www.MonolithicPower.com 8

10/25/2018 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

MP2325 – 24V, 3A SYNC STEP DOWN CONVERTER

OPERATION

The MP2325 is a high frequency synchronous Under the light load condition, the value of

rectified step-down switch mode converter with VCOMP is low. When VCOMP is less than VAAM and

built in internal power MOSFETs. It offers a VFB is less than VREF, VCOMP ramps up until it

very compact solution to achieve 3A continuous exceeds VAAM. During this time, the internal

output current over a wide input supply range clock is blocked, thus the MP2325 skips some

with excellent load and line regulation. pulses for PFM (Pulse Frequency Modulation)

mode and achieves the light load power save.

The MP2325 operates in a fixed frequency,

peak current control mode to regulate the

output voltage. A PWM cycle is initiated by the

internal clock. The integrated high-side power

MOSFET is turned on and remains on until its

current reaches the value set by the COMP

voltage. When the power switch is off, it

remains off until the next clock cycle starts. If, in

95% of one PWM period, the current in the Figure 2: Simplified AAM Control Logic

power MOSFET does not reach the COMP set For VIN=12V, VOUT=3.3V, L=4.9μH, the inductor

current value, the power MOSFET will be peak current set internally is about 500mA at

forced to turn off. light load. The AAM voltage internally is varied

Internal Regulator with duty cycle for keeping the inductor peak

Most of the internal circuitries are powered from current constant.

the 5V internal regulator. This regulator takes

the VIN input and operates in the full VIN range.

When VIN is greater than 5.0V, the output of

the regulator is in full regulation. When VIN is

lower than 5.0V, the output decreases, a 0.1uF

ceramic capacitor for decoupling purpose is

required.

Error Amplifier

The error amplifier compares the FB pin voltage

with the internal 0.8V reference (REF) and

outputs a COMP voltage, which is used to

control the power MOSFET current. The

optimized internal compensation network

Figure 3: AAM Selection for Common Output

minimizes the external component counts and

Voltages (VIN=4.5V-24V)

simplifies the control loop design.

Enable/SYNC control

Power Save Mode for Light Load Condition EN is a digital control pin that turns the

The MP2325 has AAM (Advanced regulator on and off. Drive EN high to turn on

Asynchronous Modulation) power-save mode the regulator, drive it low to turn it off. There is

for light load. Under the heavy load condition, an internal 1MEG resistor from EN to GND thus

the VCOMP is higher than VAAM. When the clock EN can be floated to shut down the chip. Also

goes high, the high-side power MOSFET turns EN pin voltage was clamped to around 6.5V by

on and remains on until VILsense reaches the an internal zener-diode. Please use large

value set by the COMP voltage. The internal enough pull up resistor connecting between VIN

clock resets every time when VCOMP is higher and EN to limit the EN input current which

than VAAM. should be less than 100uA. Generally, around

100k resistor should be large enough for all the

applications.

MP2325 Rev. 1.01 www.MonolithicPower.com 9

10/25/2018 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

MP2325 – 24V, 3A SYNC STEP DOWN CONVERTER

The chip can be synchronized to external clock thermal issue and to protect the regulator. The

range from 200kHz up to 2MHz through this pin MP2325 exits the hiccup mode once the over

2ms right after output voltage is set, with the current condition is removed.

internal clock rising edge synchronized to the

Thermal Shutdown

external clock rising edge. EN synchronize logic

Thermal shutdown is implemented to prevent

high voltage should higher than 2V. EN

the chip from operating at exceedingly high

synchronize logic low voltage should lower than

temperatures. When the silicon die temperature

400mV. EN logic high pulse width must less

is higher than 150°C, it shuts down the whole

than 1.6µs. Otherwise the internal clock may

chip. When the temperature is lower than its

come and turn on high side MOSFET again. EN

lower threshold, typically 130°C, the chip is

logic low pulse width must less than 6µs,

enabled again.

otherwise MP2325 may EN shutdown.

Floating Driver and Bootstrap Charging

Power Good Indicator

The floating power MOSFET driver is powered

The MP2325 has an open drain pin for power

by an external bootstrap capacitor. This floating

good indicator. When FB pin is higher than 90%

driver has its own UVLO protection. This

of regulation voltage, PG pin is pulled up to

UVLO’s rising threshold is 2.2V with a

VCC by the external resistor. If FB pin voltage

hysteresis of 150mV. The bootstrap capacitor

drop down to 85% of the regulation voltage, PG

voltage is regulated internally by VIN through

pin is pulled down to ground by an internal

D1, R5, C5, L1 and C2 (Figure 4). If (VIN-VSW)

MOS FET.

is more than 5V, U1 will regulate M1 to maintain

Under-Voltage Lockout (UVLO) a 5V BST voltage across C5.

Under-voltage lockout (UVLO) is implemented

to protect the chip from operating at insufficient

supply voltage. The MP2325 UVLO comparator

monitors the output voltage of the internal

regulator, VCC. The UVLO rising threshold is

about 3.9V while its falling threshold is

consistent 3.25V.

Internal Soft-Start

The soft start is implemented to prevent the

converter output voltage from overshooting

during start up. When the chip starts, the

internal circuitry generates a soft-start voltage Figure 4: Internal Bootstrap Charging Circuit

(SS) ramping up from 0V. The soft-start period

Startup and Shutdown

lasts until the voltage on the soft-start capacitor

exceeds the reference voltage of 0.8V. At this If both VIN and EN are higher than their

point the reference voltage takes over. The soft- appropriate thresholds, the chip starts. The

start time is internally set to be around 1.5ms. reference block starts first, generating stable

reference voltage and currents, and then the

Over-Current-Protection and Hiccup

internal regulator is enabled. The regulator

The MP2325 has cycle-by-cycle over current

provides stable supply for the remaining

limit when the inductor current peak value

circuitries.

exceeds the set current limit threshold.

Meanwhile, output voltage starts to drop until Three events can shut down the chip: EN low,

FB is below the Under-Voltage (UV) threshold, VIN low and thermal shutdown. In the shutdown

typically 50% below the reference. Once a UV procedure, the signaling path is first blocked to

is triggered, the MP2325 enters hiccup mode to avoid any fault triggering. The COMP voltage

periodically restart the part. This protection and the internal supply rail are then pulled down.

mode is especially useful when the output is The floating driver is not subject to this

dead-short to ground. The average short circuit shutdown command.

current is greatly reduced to alleviate the

MP2325 Rev. 1.01 www.MonolithicPower.com 10

10/25/2018 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

MP2325 – 24V, 3A SYNC STEP DOWN CONVERTER

APPLICATION INFORMATION

COMPONENT SELECTION Choose inductor current to be approximately

30% of the maximum load current. The

Setting the Output Voltage maximum inductor peak current is:

The external resistor divider is used to set the IL

output voltage (see Typical Application on page IL(MAX ) ILOAD

2

1). The feedback resistor R1 also sets the

feedback loop bandwidth with the internal Under light load conditions below 100mA, larger

compensation capacitor (see Typical inductance is recommended for improved

Application on page 1). R2 is then given by: efficiency.

R2

R1 Selecting the Input Capacitor

VOUT

1 The input current to the step-down converter is

0.8V

discontinuous, therefore a capacitor is required

The T-type network is highly recommended, as to supply the AC current to the step-down

Figure 5 shows. converter while maintaining the DC input

Cf voltage. Use low ESR capacitors for the best

Rt R1 performance. Ceramic capacitors with X5R or

8

FB VOUT X7R dielectrics are highly recommended

R2 because of their low ESR and small

temperature coefficients. For most applications,

a 22µF capacitor is sufficient.

Figure 5: T-type Network

Since the input capacitor (C1) absorbs the input

Table 1 lists the recommended T-type resistors

switching current it requires an adequate ripple

value for common output voltages.

current rating. The RMS current in the input

Table 1—Resistor Selection for Common capacitor can be estimated by:

Output Voltages

VOUT VOUT

VOUT(V) R1(kΩ) R2(kΩ) Rt (kΩ) L (µH) Cf (µF) I C1 ILOAD 1

VIN VIN

1 20.5 76.8 100 1.8 15

The worse case condition occurs at VIN =

1.2 20.5 39.2 100 1.8 15

2VOUT, where:

1.8 40.2 31.6 56 3.3 15

ILOAD

2.5 40.2 18.7 56 3.3 15 I C1

2

3.3 40.2 12.7 33 4.9 15

5 40.2 7.5 33 4.9 15

For simplification, choose the input capacitor

whose RMS current rating greater than half of

Selecting the Inductor the maximum load current.

A 1µH to 22µH inductor with a DC current rating The input capacitor can be electrolytic, tantalum

of at least 25% percent higher than the or ceramic. When using electrolytic or tantalum

maximum load current is recommended for capacitors, a small, high quality ceramic

most applications. For highest efficiency, the capacitor, i.e. 0.1μF, should be placed as close

inductor DC resistance should be less than to the IC as possible. When using ceramic

15mΩ. For most designs, the inductance value capacitors, make sure that they have enough

can be derived from the following equation. capacitance to provide sufficient charge to

prevent excessive voltage ripple at input. The

VOUT (VIN VOUT )

L1 input voltage ripple caused by capacitance can

VIN IL fOSC

be estimated by:

Where ∆IL is the inductor ripple current. ILOAD V V

VIN OUT 1 OUT

fS C1 VIN VIN

MP2325 Rev. 1.01 www.MonolithicPower.com 11

10/25/2018 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

MP2325 – 24V, 3A SYNC STEP DOWN CONVERTER

Selecting the Output Capacitor

The output capacitor (C2) is required to

maintain the DC output voltage. Ceramic,

tantalum, or low ESR electrolytic capacitors are

recommended. Low ESR capacitors are

preferred to keep the output voltage ripple low.

The output voltage ripple can be estimated by:

VOUT V 1 Figure 6: Add Optional External

VOUT 1 OUT RESR

fS L1 VIN 8 fS C2 Bootstrap Diode to Enhance Efficiency

Where L1 is the inductor value and RESR is the The recommended external BST diode is

equivalent series resistance (ESR) value of the IN4148, and the BST cap is 0.1μF─1μF.

output capacitor. PC Board Layout (6)

In the case of ceramic capacitors, the PCB layout is very important to achieve stable

impedance at the switching frequency is operation. Please follow these guidelines and

dominated by the capacitance. The output take Figure 7 as reference.

voltage ripple is mainly caused by the 1) Keep the connection of input ground and

capacitance. For simplification, the output GND pin as short and wide as possible.

voltage ripple can be estimated by:

2) Keep the connection of input capacitor and

VOUT V IN pin as short and wide as possible.

∆VOUT 1 OUT

8 fS2 L1 C2 VIN

3) Ensure all feedback connections are short

In the case of tantalum or electrolytic capacitors, and direct. Place the feedback resistors and

the ESR dominates the impedance at the compensation components as close to the chip

switching frequency. For simplification, the as possible.

output ripple can be approximated to: 4) Route SW away from sensitive analog areas

V V such as FB.

∆VOUT OUT 1 OUT RESR

fS L1 VIN Notes:

6) The recommended layout is based on the Figure 8 Typical

The characteristics of the output capacitor also Application circuit on the next page.

affect the stability of the regulation system. The

MP2325 can be optimized for a wide range of

capacitance and ESR values.

External Bootstrap Diode

An external bootstrap diode may enhance the

efficiency of the regulator, the applicable

conditions of external BST diode are:

VOUT is 5V or 3.3V;

VOUT

Duty cycle is high: D= >65%

VIN

In these cases, an external BST diode is

recommended from the VCC pin to BST pin, as

shown in Figure 6.

MP2325 Rev. 1.01 www.MonolithicPower.com 12

10/25/2018 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

MP2325 – 24V, 3A SYNC STEP DOWN CONVERTER

Design Example

Below is a design example following the

application guidelines for the specifications:

Table 2: Design Example

VIN 19V

VOUT 5V

IO 3A

The detailed application schematics are shown

in Figures 8 through 13. The typical

performance and circuit waveforms have been

shown in the Typical Performance

Characteristics section. For more device

applications, please refer to the related

Evaluation Board Datasheets.

Figure 7: Sample Board Layout

MP2325 Rev. 1.01 www.MonolithicPower.com 13

10/25/2018 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

MP2325 – 24V, 3A SYNC STEP DOWN CONVERTER

TYPICAL APPLICATION CIRCUITS

Figure 8: Vo=5V, Io=3A

Figure 9: Vo=3.3V, Io=3A

Figure 10: Vo=2.5V, Io=3A

MP2325 Rev. 1.01 www.MonolithicPower.com 14

10/25/2018 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

MP2325 – 24V, 3A SYNC STEP DOWN CONVERTER

Figure 11: Vo=1.8V, Io=3A

Figure 12: Vo=1.2V, Io=3A

Figure 13: Vo=1V, Io=3A

MP2325 Rev. 1.01 www.MonolithicPower.com 15

10/25/2018 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

MP2325 – 24V, 3A SYNC STEP DOWN CONVERTER

PACKAGE INFORMATION

TSOT23-8

NOTICE: The information in this document is subject to change without notice. Users should warrant and guarantee that third

party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not

assume any legal responsibility for any said applications.

MP2325 Rev. 1.01 www.MonolithicPower.com 16

10/25/2018 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

You might also like

- Dark Winter ImprimirDocument3 pagesDark Winter Imprimirsunayhernandez1No ratings yet

- 2A, 55V, 100Khz Step-Down ConverterDocument12 pages2A, 55V, 100Khz Step-Down Convertermichael8710No ratings yet

- U1 Xbox OneDocument14 pagesU1 Xbox OneCheckpoint Game CenterNo ratings yet

- Fast Turn-Off Intelligent Rectifier With No Need For Auxiliary Winding Description FeaturesDocument14 pagesFast Turn-Off Intelligent Rectifier With No Need For Auxiliary Winding Description FeaturesKwun Hok ChongNo ratings yet

- LM2621 Low Input Voltage, Step-Up DC-DC Converter: 1 Features 3 DescriptionDocument17 pagesLM2621 Low Input Voltage, Step-Up DC-DC Converter: 1 Features 3 DescriptionSatyashiba Sundar JenaNo ratings yet

- MP8719 6600xt SaphireDocument22 pagesMP8719 6600xt Saphiretechgamebr85No ratings yet

- Primary-Side Control, Offline LED Controller With Active PFC, NTC and PWM DimmingDocument19 pagesPrimary-Side Control, Offline LED Controller With Active PFC, NTC and PWM Dimmingzuffflor_925748656No ratings yet

- 2A, 24V Input, 600Khz 2/3-Cell Switching Li-Ion Battery ChargerDocument16 pages2A, 24V Input, 600Khz 2/3-Cell Switching Li-Ion Battery Charger123No ratings yet

- MAX77680 Datasheet and Technical InfoDocument9 pagesMAX77680 Datasheet and Technical InfojackNo ratings yet

- Offline, Primary-Side Regulator With CC/CV Control and A 700V MOSFETDocument21 pagesOffline, Primary-Side Regulator With CC/CV Control and A 700V MOSFETsluz2000No ratings yet

- MP9943Document20 pagesMP9943techgamebr85No ratings yet

- MP3389 r1.04Document16 pagesMP3389 r1.04Andres Alegria100% (1)

- Transition-Mode PFC Controller: FeaturesDocument25 pagesTransition-Mode PFC Controller: FeaturesRodrigo BonfanteNo ratings yet

- Max8732a Max8734a PDFDocument33 pagesMax8732a Max8734a PDFmirandowebsNo ratings yet

- MAQ3203YM Evaluation Board User GuideDocument23 pagesMAQ3203YM Evaluation Board User GuideJohnNo ratings yet

- TSX712Document31 pagesTSX712lugitecNo ratings yet

- SGM4812Document11 pagesSGM4812Fernando Martin GaivazziNo ratings yet

- USB On-the-Go Transceivers and Charge Pumps: General Description FeaturesDocument38 pagesUSB On-the-Go Transceivers and Charge Pumps: General Description FeaturesBilal InfotexNo ratings yet

- MP6515Document13 pagesMP6515gaatje niks aanNo ratings yet

- Max20050-Max20053 2A Synchronous-Buck Led Drivers With Integrated MosfetsDocument23 pagesMax20050-Max20053 2A Synchronous-Buck Led Drivers With Integrated MosfetsAdrian WongNo ratings yet

- Multi-Output, Low-Noise Power-Supply Controllers For Notebook ComputersDocument28 pagesMulti-Output, Low-Noise Power-Supply Controllers For Notebook ComputersAleksNo ratings yet

- Recommended For New Designs Refer T O Mp2331H: 0.5A, 24V, 1.4Mhz Step-Down Converter in A Tsot23-6Document11 pagesRecommended For New Designs Refer T O Mp2331H: 0.5A, 24V, 1.4Mhz Step-Down Converter in A Tsot23-6jeanneNo ratings yet

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDocument10 pagesNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânNo ratings yet

- General Description Features: High Performance Current Mode PWM ControllerDocument11 pagesGeneral Description Features: High Performance Current Mode PWM ControllerPhạm Tấn HảiNo ratings yet

- MAX17411 MaximIntegratedDocument72 pagesMAX17411 MaximIntegratedRoberto MouraNo ratings yet

- 100V Input, 1A High Power LED Driver: The Future of Analog IC TechnologyDocument10 pages100V Input, 1A High Power LED Driver: The Future of Analog IC TechnologyAdrian WongNo ratings yet

- A3121 2 3 Datasheet PDFDocument9 pagesA3121 2 3 Datasheet PDFAsad IqbalNo ratings yet

- MP1488Document11 pagesMP1488Jaime Andres Aranguren CardonaNo ratings yet

- NB676 DatasheetDocument19 pagesNB676 DatasheetRudy BudimanNo ratings yet

- Bd71837amwv eDocument129 pagesBd71837amwv eChip KitNo ratings yet

- Nxpusainc Mc33926pnb Datasheets 8993Document35 pagesNxpusainc Mc33926pnb Datasheets 8993Nooragha TanhaNo ratings yet

- LM3530 High Efficiency White LED Driver With Programmable Ambient Light Sensing Capability and I C-Compatible InterfaceDocument45 pagesLM3530 High Efficiency White LED Driver With Programmable Ambient Light Sensing Capability and I C-Compatible Interfacethoth2487No ratings yet

- 1.5Mhz, 30A High-Efficiency, Led Driver With Rapid Led Current PulsingDocument25 pages1.5Mhz, 30A High-Efficiency, Led Driver With Rapid Led Current PulsingDummy CekNo ratings yet

- MTC 2 eDocument8 pagesMTC 2 eravikumarrkNo ratings yet

- TinyNode Users Manual Rev11 01Document30 pagesTinyNode Users Manual Rev11 01fantomagaNo ratings yet

- 24V, High Current Synchronous Step-Down Converter: The Future of Analog IC TechnologyDocument20 pages24V, High Current Synchronous Step-Down Converter: The Future of Analog IC TechnologyRinaldyNo ratings yet

- MLX91205 DatasheetDocument14 pagesMLX91205 DatasheetRicardo ReisNo ratings yet

- Description/ordering Information: 1out 1IN 1IN+ GND V 2out 2IN 2IN+Document18 pagesDescription/ordering Information: 1out 1IN 1IN+ GND V 2out 2IN 2IN+javierrincon800No ratings yet

- Lmx31X Precision Voltage-To-Frequency Converters: 1 Features 3 DescriptionDocument23 pagesLmx31X Precision Voltage-To-Frequency Converters: 1 Features 3 DescriptionAlonso Herrera SeguraNo ratings yet

- Max16833 Max16833gDocument25 pagesMax16833 Max16833gKwun Hok ChongNo ratings yet

- LM3243 High-Current Step-Down Converter For 2G, 3G, and 4G RF Power AmplifiersDocument32 pagesLM3243 High-Current Step-Down Converter For 2G, 3G, and 4G RF Power Amplifiersgotcha75No ratings yet

- SGM706Document12 pagesSGM706Sveto SlNo ratings yet

- D D D D D D D D D: DescriptionDocument18 pagesD D D D D D D D D: DescriptionNalin Lochan GuptaNo ratings yet

- D D D D D D D D: DescriptionDocument10 pagesD D D D D D D D: DescriptionVíctor LópezNo ratings yet

- LM 318Document11 pagesLM 318Diego LeeNo ratings yet

- 5ppm, I C Real-Time Clock: General Description FeaturesDocument20 pages5ppm, I C Real-Time Clock: General Description FeaturesJosueChalenSarezNo ratings yet

- Max2680/Max2681/ Max2682 400Mhz To 2.5Ghz, Low-Noise, Sige Downconverter MixersDocument12 pagesMax2680/Max2681/ Max2682 400Mhz To 2.5Ghz, Low-Noise, Sige Downconverter MixersDusan PejicNo ratings yet

- Summary ClockDocument39 pagesSummary ClockmikcomiNo ratings yet

- Rail-To-Rail 1.8 V High-Speed Dual Comparator: FeaturesDocument20 pagesRail-To-Rail 1.8 V High-Speed Dual Comparator: FeaturesshhmmmNo ratings yet

- Low-Power Single Operational Amplifier: DescriptionDocument15 pagesLow-Power Single Operational Amplifier: Descriptionchad tan100% (1)

- Power Power: Designer DesignerDocument8 pagesPower Power: Designer DesignerNeha JainNo ratings yet

- Multisim AvanzadoDocument35 pagesMultisim AvanzadoedgarfransNo ratings yet

- SPX3819 LdoDocument14 pagesSPX3819 LdoMistaNo ratings yet

- (BISS) TransistorsDocument12 pages(BISS) TransistorsMiloud ChouguiNo ratings yet

- MAX3051Document13 pagesMAX3051Mirko GalićNo ratings yet

- Pont en HDocument17 pagesPont en Hapi-288039470No ratings yet

- MP2225GJ-Z Circuito IntegratoDocument20 pagesMP2225GJ-Z Circuito IntegratoMimmo FracchiollaNo ratings yet

- DRV 8811Document22 pagesDRV 8811nelson_loboNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- DV 410V K OperatingInstructions0418Document101 pagesDV 410V K OperatingInstructions0418Anonymous 8bbVmLtQNo ratings yet

- Zte Cabinets: Knowledge Sharing SessionsDocument41 pagesZte Cabinets: Knowledge Sharing SessionsAnonymous 8bbVmLtQNo ratings yet

- Installation and Operating Manuals: For Further Information and Up To Date Documentation Please VisitDocument1 pageInstallation and Operating Manuals: For Further Information and Up To Date Documentation Please VisitAnonymous 8bbVmLtQNo ratings yet

- Samsung Sm-t211 Service ManualDocument52 pagesSamsung Sm-t211 Service ManualAnonymous 8bbVmLtQ75% (4)

- Writing An Application LetterDocument6 pagesWriting An Application LetterNur AmaliaNo ratings yet

- Fire Detection With Image ProcessingDocument6 pagesFire Detection With Image ProcessingIJRASETPublicationsNo ratings yet

- Assignment 2 Front Sheet: Qualification BTEC Level 5 HND Diploma in Computing Unit Number and Title Submission DateDocument29 pagesAssignment 2 Front Sheet: Qualification BTEC Level 5 HND Diploma in Computing Unit Number and Title Submission DateCục MuốiNo ratings yet

- CS001 Computer Proficiency All Midterm Solved Objective and Subjective Papers in One File For Preparation of Midterm ExamDocument0 pagesCS001 Computer Proficiency All Midterm Solved Objective and Subjective Papers in One File For Preparation of Midterm ExamQazi Khubaib Alam100% (1)

- SAPDocument32 pagesSAPAnjali RanaNo ratings yet

- Confluence Interview Questions and AnswersDocument6 pagesConfluence Interview Questions and AnswerssayraNo ratings yet

- Pro-Shock Waves Pro-Shock Waves: The Most Versatile Shockwaves EverDocument2 pagesPro-Shock Waves Pro-Shock Waves: The Most Versatile Shockwaves EverPrie AjeNo ratings yet

- Influencing Ethical Culture Through A Multi-Channel Compliance ProgramDocument7 pagesInfluencing Ethical Culture Through A Multi-Channel Compliance ProgramAnn AllsoppNo ratings yet

- Learning Go LatestDocument112 pagesLearning Go LatestGaurav ChaturvediNo ratings yet

- 87-351 Lecture 11 NotesDocument10 pages87-351 Lecture 11 NotesAmritpal GillNo ratings yet

- MPI The Best Possible PractiseDocument5 pagesMPI The Best Possible Practisekam_anwNo ratings yet

- MNM3709 SummaryDocument4 pagesMNM3709 SummarynoxaNo ratings yet

- Ethernet Communication Module: Application ManualDocument11 pagesEthernet Communication Module: Application ManualSilvia MaribelNo ratings yet

- As 3822-2002 Test Methods For Bare Overhead ConductorsDocument29 pagesAs 3822-2002 Test Methods For Bare Overhead ConductorsCristian WalkerNo ratings yet

- PowerOn Fusion PDFDocument16 pagesPowerOn Fusion PDFJagan VanamaNo ratings yet

- Kakatiya University, Warangal 2020 PDFDocument2 pagesKakatiya University, Warangal 2020 PDFAkHilkumar BoragalaNo ratings yet

- Computer1 - Lesson 1 - THE WORDPAD PROGRAM - 000Document4 pagesComputer1 - Lesson 1 - THE WORDPAD PROGRAM - 000Alyessa Dawn FalladoNo ratings yet

- Brother CP1800, CP2000, CB200 Service Manual PDFDocument92 pagesBrother CP1800, CP2000, CB200 Service Manual PDFStefanNo ratings yet

- Turban 02Document88 pagesTurban 02Ayu Saida ZulfaNo ratings yet

- Working With Algebra Tiles (Project)Document8 pagesWorking With Algebra Tiles (Project)Ruben Serna CNo ratings yet

- ANSYS 9.0 - Installation ProcedureDocument26 pagesANSYS 9.0 - Installation Proceduresanthoshjoys50% (2)

- The RANDOM Statement and More Moving On With PROC MCMCDocument21 pagesThe RANDOM Statement and More Moving On With PROC MCMCarijitroyNo ratings yet

- Applications of Artificial Intelligence For Disaster ManagementDocument59 pagesApplications of Artificial Intelligence For Disaster ManagementCARLOSNo ratings yet

- Oumm3203 Professional EthicsDocument11 pagesOumm3203 Professional Ethicsdicky chongNo ratings yet

- Minimum Automotive Quality Management System Requirements For Sub Tier Suppliers 2nded Rev2Document8 pagesMinimum Automotive Quality Management System Requirements For Sub Tier Suppliers 2nded Rev2R JNo ratings yet

- CS224d - Assignment 2Document3 pagesCS224d - Assignment 2Aalok GangopadhyayNo ratings yet

- LP621024D Series: 128K X 8 Bit Cmos SramDocument16 pagesLP621024D Series: 128K X 8 Bit Cmos SramClaudiney BricksNo ratings yet

- Cosine Effect DetailsDocument3 pagesCosine Effect DetailsZohaib HassanNo ratings yet

- 27C512Document12 pages27C512technicalavrNo ratings yet