Professional Documents

Culture Documents

Micro Power 3 V Linear Hall Effect Sensor Ics Withtri-State Output and User-Selectable Sleep Mode

Micro Power 3 V Linear Hall Effect Sensor Ics Withtri-State Output and User-Selectable Sleep Mode

Uploaded by

DomRuanOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Micro Power 3 V Linear Hall Effect Sensor Ics Withtri-State Output and User-Selectable Sleep Mode

Micro Power 3 V Linear Hall Effect Sensor Ics Withtri-State Output and User-Selectable Sleep Mode

Uploaded by

DomRuanCopyright:

Available Formats

A1391, A1392, A1393, and A1395

Micro Power 3 V Linear Hall Effect Sensor ICs

withTri-State Output and User-Selectable Sleep Mode

Features and Benefits Description

▪ High-impedance output during sleep mode The A139x family of linear Hall effect sensor integrated circuits

▪ Compatible with 2.5 to 3.5 V power supplies (ICs) provide a voltage output that is directly proportional to

▪ 10 mW power consumption in the active mode an applied magnetic field. Before amplification, the sensitivity

▪ Miniature MLP/DFN package of typical Hall effect ICs (measured in mV/G) is directly

▪ Ratiometric output scales with the ratiometric supply proportional to the current flowing through the Hall effect

reference voltage (VREF pin) transducer element inside the ICs. In many applications, it

▪ Temperature-stable quiescent output voltage and is difficult to achieve sufficient sensitivity levels with a Hall

sensitivity effect sensor IC without consuming more than 3 mA of current.

▪ Wide ambient temperature range: –20°C to 85°C The A139x minimize current consumption to less than 25 µA

▪ ESD protection greater than 3 kV through the addition of a user-selectable sleep mode. This makes

▪ Solid-state reliability these devices perfect for battery-operated applications such as:

▪ Preset sensitivity and offset at final test cellular phones, digital cameras, and portable tools. End users

can control the current consumption of the A139x by applying a

logic level signal to the S̄L̄¯Ē¯Ē¯P̄¯ pin. The outputs of the devices

are not valid (high-impedance mode) during sleep mode. The

Package: 6 pin MLP/DFN (suffix EH) high-impedance output feature allows the connection of multiple

A139x Hall effect devices to a single A-to-D converter input.

The quiescent output voltage of these devices is 50 % nominal of

the ratiometric supply reference voltage applied to the VREF pin

of the device. The output voltage of the device is not ratiometric

with respect to the SUPPLY pin.

Approximate scale Continued on the next page…

Functional Block Diagram

VCC VREF

To all subcircuits

RRatio / 2

Hall Element

Regulator

RRatio / 2

Dynamic Offset

Cancellation

OUT

Filter

Amp Out

Gain Offset

Programming Logic

SLEEP

Circuit Reference Current

GND

1391-DS, Rev. 8 February 13, 2019

MCO-0000591

A1391, A1392, Micro Power 3 V Linear Hall Effect Sensor ICs

A1393, and A1395 with Tri-State Output and User Selectable Sleep Mode

Description (continued)

Despite the low power consumption of the circuitry in the A139x, offset cancellation circuits. End of line, post-packaging, factory

the features required to produce a highly-accurate linear Hall effect programming allows precise control of device sensitivity and

IC have not been compromised. Each BiCMOS monolithic circuit offset.

integrates a Hall element, improved temperature-compensating These devices are available in a small 2.0 × 3.0 mm, 0.75 mm nominal

circuitry to reduce the intrinsic sensitivity drift of the Hall element, height microleaded package (MLP/DFN). It is Pb (lead) free, with

a small-signal high-gain amplifier, and proprietary dynamic 100% matte tin leadframe plating.

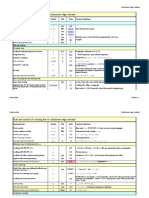

Selection Guide

Sensitivity

Part Number Package Packing1

(mV / G, Typ.)

A1391SEHLT-T2 1.25 DFN/MLP 2×3 mm; 0.75 mm nominal height 7-in. reel, 3000 pieces/reel

A1392SEHLT-T2 2.50 DFN/MLP 2×3 mm; 0.75 mm nominal height 7-in. reel, 3000 pieces/reel

A1393SEHLT-T2 5 DFN/MLP 2×3 mm; 0.75 mm nominal height 7-in. reel, 3000 pieces/reel

A1395SEHLT-T2 10 DFN/MLP 2×3 mm; 0.75 mm nominal height 7-in. reel, 3000 pieces/reel

1Contact Allegro™ for additional packing options.

2Allegro products sold in DFN package types are not intended for automotive applications.

Absolute Maximum Ratings*

Characteristic Symbol Notes Rating Unit

Supply Voltage VCC 8 V

Reverse-Supply Voltage VRCC –0.1 V

Ratiometric Supply Reference Voltage VREF 7 V

Reverse-Ratiometric Supply Reference Voltage VRREF –0.1 V

Logic Supply Voltage VS̄¯

L̄¯ Ē¯ Ē¯ P̄¯ (VCC > 2.5 V) 32 V

Reverse-Logic Supply Voltage VRS̄¯

L̄¯ Ē¯ Ē¯ P̄¯ –0.1 V

Output Voltage VOUT VCC + 0.1 V

Reverse-Output Voltage VROUT –0.1 V

Operating Ambient Temperature TA Range S –20 to 85 ºC

Junction Temperature TJ(MAX) 165 ºC

StorageTemperature Tstg –65 to 170 ºC

*All ratings with reference to ground

Pin-out Diagram Terminal List Table

Pin Name Function

VCC 1 6 VREF

OUT 2 5 SLEEP 1 VCC Supply

GND 3 4 GND 2 OUT Output

3 GND Ground

4 GND Ground

5 ¯ Ē¯ Ē¯ P̄¯

S̄¯ L̄ Toggle sleep mode

6 VREF Supply for ratiometric reference

Allegro MicroSystems, LLC 2

955 Perimeter Road

Manchester, NH 03103-3353 U.S.A.

www.allegromicro.com

A1391, A1392, Micro Power 3 V Linear Hall Effect Sensor ICs

A1393, and A1395 with Tri-State Output and User Selectable Sleep Mode

Device Characteristics Tables

ELECTRICAL CHARACTERISTICS valid through full operating ambient temperature range, unless otherwise noted

Characteristic Symbol Test Conditions Min. Typ.1 Max. Units

Supply Voltage VCC 2.5 – 3.5 V

Nominal Supply Voltage VCCN – 3.0 – V

Supply Zener Clamp Voltage VCCZ ICC = 7 mA, TA = 25°C 6 8.3 – V

Ratiometric Reference Voltage2 VREF 2.5 – VCC V

Ratiometric Reference Zener Clamp Voltage VREFZ IVREF = 3 mA, TA = 25°C 6 8.3 – V

¯ L̄¯ Ē¯ Ē¯ P̄¯ Input Voltage

S̄ –0.1 – VCC + 0.5 V

VINH For active mode – 0.45 × VCC – V

S̄¯ L̄¯ Ē¯ Ē¯ P̄¯ Input Threshold

VINL For sleep mode – 0.20 × VCC – V

VSLEEP > VINH , VCC = VCCN,

250 – – kΩ

TA = 25°C

Ratiometric Reference Input Resistance RREF

VSLEEP < VINL, VCC = VCCN,

– 5 – MΩ

TA = 25°C

Chopper Stabilization Chopping Frequency fC VCC = VCCN, TA = 25°C – 200 – kHz

S̄¯ L̄¯ Ē¯ Ē¯ P̄¯ Input Current ISLEEP VSLEEP = 3 V, VCC = VCCN – 1 – μA

VSLEEP < VINL, VCC = VCCN,

– 0.025 – mA

TA = 25°C

Supply Current3 ICC

VSLEEP > VINH , VCC = VCCN,

– 3.2 – mA

TA = 25°C

Quiescent Output Power Supply Rejection4 PSRVOQ fAC < 1 kHz – –60 – dB

1Typical data are for initial design estimations only, and assume optimum manufacturing and application conditions, such as T = 25°C. Performance

A

may vary for individual units, within the specified maximum and minimum limits.

2 Voltage applied to the VREF pin. Note that the V voltage must be less than or equal to V . Degradation in device accuracy will occur with applied

REF cc

voltages of less than 2.5 V.

3 If the VREF pin is tied to the VCC pin, the supply current would be I

CC + VREF / RREF

4f

AC is any AC component frequency that exists on the supply line.

Allegro MicroSystems, LLC 3

955 Perimeter Road

Manchester, NH 03103-3353 U.S.A.

www.allegromicro.com

A1391, A1392, Micro Power 3 V Linear Hall Effect Sensor ICs

A1393, and A1395 with Tri-State Output and User Selectable Sleep Mode

OUTPUT CHARACTERISTICS valid through full operating ambient temperature range, unless otherwise noted

Characteristic Symbol Test Conditions Min. Typ.1 Max. Units

Linear Output Voltage VOUTH VCC = VCCN, VREF ≤ VCC – VREF – 0.1 – V

Range VOUTL VCC = VCCN, VREF ≤ VCC – 0.1 – V

Maximum Voltage Applied

VOUTMAX VSLEEP < VINL – – VCC + 0.1 V

to Output

A1391 TA = 25°C, VCC = VREF = VCCN – 1.25 – mV/G

A1392 TA = 25°C, VCC = VREF = VCCN – 2.50 – mV/G

Sensitivity2 Sens

A1393 TA = 25°C, VCC = VREF = VCCN – 5 – mV/G

A1395 TA = 25°C, VCC = VREF = VCCN – 10 – mV/G

Quiescent Output VOUTQ TA = 25°C, B = 0 G – 0.500 × VREF – V

fout = 1 kHz, VSLEEP > VINH , active mode – 20 – Ω

Output Resistance3 ROUT

fout = 1 kHz, VSLEEP < VINL, sleep mode – 4M – Ω

Output Load Resistance RL Output to ground 15 – – kΩ

Output Load Capacitance CL Output to ground – – 10 nF

–3 dB point, VOUT = 1 Vpp sinusoidal,

Output Bandwidth BW – 10 – kHz

VCC = VCCN

Cbypass = 0.1 µF,

– 6 12 mVpp

1391 BWexternalLPF = 2 kHz

Cbypass = 0.1 µF, no load – – 20 mVpp

1392 Cbypass = 0.1 µF, no load – – 40 mVpp

Noise4,5 Vn

Cbypass = 0.1 µF,

– 12 24 mVpp

1393 BWexternalLPF = 2 kHz

Cbypass = 0.1 µF, no load – – 40 mVpp

1395 Cbypass = 0.1 µF, no load – – 80 mVpp

1Typical data are for initial design estimations only, and assume optimum manufacturing and application conditions, such as TA = 25°C. Performance

may vary for individual units, within the specified maximum and minimum limits.

2For V

REF values other than VREF = VCCN , the sensitivity can be derived from the following equation: K × VREF , where K =0.416 for the A1391, K= 0.823

for the A1392, K = 1.664 for the A1393, and K = 3.328 for the A1395.

3f

OUT is the output signal frequency

4Noise specification includes digital and analog noise.

5Values for BW

externalLPF do not include any noise resulting from noise on the externally-supplied VREF voltage.

Allegro MicroSystems, LLC 4

955 Perimeter Road

Manchester, NH 03103-3353 U.S.A.

www.allegromicro.com

A1391, A1392, Micro Power 3 V Linear Hall Effect Sensor ICs

A1393, and A1395 with Tri-State Output and User Selectable Sleep Mode

OUTPUT TIMING CHARACTERISTICS1 TA = 25°C

Characteristic Symbol Test Conditions Min. Typ.2 Max. Units

Power-On Time3 tPON – 40 60 µs

Power-Off Time4 tPOFF – 1 – µs

1See figure 1 for explicit timing delays.

2Typical data are for initial design estimations only, and assume optimum manufacturing and application conditions, such as TA = 25°C. Performance

may vary for individual units, within the specified maximum and minimum limits.

3Power-On Time is the elapsed time after the voltage on the S̄ ¯ L̄¯ Ē¯ Ē¯ P̄¯ pin exceeds the active mode threshold voltage,VINH, until the time the device output

reaches 90% of its value.

4Power-Off Time is the duration of time between when the signal on the ¯ ¯ L̄¯ Ē¯ Ē¯ P̄¯ pin switches from HIGH to LOW and when ICC drops to under 100 μA.

S̄

During this time period, the output goes into the HIGH impedance state.

MAGNETIC CHARACTERISTICS TA = 25°C

Characteristic Symbol Test Conditions Min. Typ.* Max. Units

Ratiometry ΔVOUTQ(ΔV) – 100 – %

Ratiometry ΔSens(ΔV) – 100 – %

Positive Linearity Lin+ – 100 – %

Negative Linearity Lin– – 100 – %

Symmetry Sym – 100 – %

*Typical data are for initial design estimations only, and assume optimum manufacturing and application conditions, such as TA = 25°C. Performance

may vary for individual units, within the specified maximum and minimum limits.

Allegro MicroSystems, LLC 5

955 Perimeter Road

Manchester, NH 03103-3353 U.S.A.

www.allegromicro.com

A1391, A1392, Micro Power 3 V Linear Hall Effect Sensor ICs

A1393, and A1395 with Tri-State Output and User Selectable Sleep Mode

Electrical Characteristic Data

Supply Current versus Ambient Temperature

A139x, VCC = VREF = 3 V

3.5

3.0

2.5

ICC (mA)

2.0 Active Mode

Sleep Mode

1.5

1.0

0.5

0

-20 -5 10 25 40 55 70 85

TA (°C)

Ratiometric Reference Input Current SLEEP Input Current

versus Ambient Temperature versus Ambient Temperature

A139x, VCC = VREF= VSLEEP = 3 V A139x, VCC = VREF= VSLEEP = 3 V

19 2.0

17 1.8

15 1.6

13 1.4

ISLEEP (µA)

1.2

IREF (µA)

11

1.0

9

0.8

7 0.6

5 0.4

3 0.2

1 0

-20 -5 10 25 40 55 70 85 -20 -5 10 25 40 55 70 85

TA (°C) TA (°C)

Allegro MicroSystems, LLC 6

955 Perimeter Road

Manchester, NH 03103-3353 U.S.A.

www.allegromicro.com

A1391, A1392, Micro Power 3 V Linear Hall Effect Sensor ICs

A1393, and A1395 with Tri-State Output and User Selectable Sleep Mode

Magnetic Characteristic Data

Average Ratiometry, VOUTQ , versus Ambient Temperture

(A139x)

101.0

100.8 2.5 to 3 V

Average Ratiometry, Voq (%)

100.6 3.5 to 3 V

100.4

100.2

100.0

99.8

99.6

99.4

99.2

99.0

-20 -5 10 25 40 55 70 85

TA (°C)

Average Ratiometry, Sens, versus Ambient Temperture Average Ratiometry, Sens, versus Ambient Temperture

(A1391) (A1392)

102.0 102.0

101.5 101.5

Average Ratiometry, Sens (%)

Average Ratiometry, Sens (%)

101.0 101.0

2.5 to 3 V

100.5 3.5 to 3 V 100.5

100.0 100.0 2.5 to 3 V

3.5 to 3 V

99.5 99.5

99.0 99.0

98.5 98.5

98.0 98.0

97.5 97.5

-20 -5 10 25 40 55 70 85 -20 -5 10 25 40 55 70 85

TA (°C) TA (°C)

Average Symmetry, Vcc=Vref=Vsleep=3V Average Linearity

(A139x) (A139x)

102.0

102.0

101.5

101.5

101.0

Average Linearity (%)

101.0

Average Symetry (%)

100.5

100.5

100.0

100.0 99.5

99.5 99.0

Linearity - , Vcc=3.5V

99.0 98.5 Linearity +, Vcc=3.5V

98.5 98.0 Linearity +, Vcc=2.5V

Linearity -, Vcc = 2.5V

98.0 97.5

97.0

97.5

-20 -5 10 25 40 55 70 85

-20 -5 10 25 40 55 70 85

TA (°C) TA (°C)

Allegro MicroSystems, LLC 7

955 Perimeter Road

Manchester, NH 03103-3353 U.S.A.

www.allegromicro.com

A1391, A1392, Micro Power 3 V Linear Hall Effect Sensor ICs

A1393, and A1395 with Tri-State Output and User Selectable Sleep Mode

THERMAL CHARACTERISTICS may require derating at maximum conditions, see application information

Characteristic Symbol Test Conditions Min. Units

1-layer PCB with copper limited to solder pads 221 ºC/W

2-layer PCB with 0.6 in.2 of copper area each side, connected by

Package Thermal Resistance RθJA 70 ºC/W

thermal vias

4-layer PCB based on JEDEC standard 50 ºC/W

Power Dissipation versus Ambient Temperature

4500

4000

3500

4-layer PCB

Power Dissipation, PD (m W)

3000 (RθJA = 50 ºC/W)

2-layer PCB

2500

(RθJA = 70 ºC/W)

2000

1-layer PCB

(RθJA = 221 ºC/W)

1500

1000

500

0

20 40 60 80 100 120 140 160 180

Temperature (°C)

Allegro MicroSystems, LLC 8

955 Perimeter Road

Manchester, NH 03103-3353 U.S.A.

www.allegromicro.com

A1391, A1392, Micro Power 3 V Linear Hall Effect Sensor ICs

A1393, and A1395 with Tri-State Output and User Selectable Sleep Mode

Characteristics Definitions

Ratiometric. The A139x devices feature ratiometric output. Linearity and Symmetry. The on-chip output stage is

The quiescent voltage output and sensitivity are proportional to designed to provide a linear output with maximum supply voltage

the ratiometric supply reference voltage. of VCCN. Although application of very high magnetic fields will

The percent ratiometric change in the quiescent voltage output is not damage these devices, it will force the output into a non-lin-

defined as: ear region. Linearity in percent is measured and defined as

VOUT(+B) – VOUTQ

∆VOUTQ(VREF)÷ ∆VOUTQ(3V) (3)

∆VOUTQ(∆V) = × 100 % (1) Lin+ =

2(VOUT(+B / 2) – VOUTQ )

× 100 %

VREF ÷ 3 V

and the percent ratiometric change in sensitivity is defined as: VOUT(–B) – VOUTQ

∆Sens(VREF)÷ ∆Sens(3V)

Lin– = × 100 % (4)

∆Sens(∆V) =

VREF ÷ 3 V

× 100% (2) 2(VOUT(–B / 2) – VOUTQ )

and output symmetry as

VOUT(+B) – VOUTQ

Sym = × 100 % (5)

VOUTQ – VOUT(–B)

Allegro MicroSystems, LLC 9

955 Perimeter Road

Manchester, NH 03103-3353 U.S.A.

www.allegromicro.com

A1391, A1392, Micro Power 3 V Linear Hall Effect Sensor ICs

A1393, and A1395 with Tri-State Output and User Selectable Sleep Mode

Device Low-Power Functionality

A139x are low-power Hall effect sensor ICs that are perfect for valid. The device output transitions into the high impedance state

power sensitive customer applications. The current consumption approximately tPOFF seconds after a logic low signal is applied to

of these devices is typically 3.2 mA, while the device is in the the S̄L̄¯Ē

¯Ē¯P̄¯ pin (see figure 1).

active mode, and less than 25 µA when the device is in the sleep

mode. Toggling the logic level signal connected to the S̄L̄¯Ē¯Ē

¯P̄¯ pin If possible, it is recommended to power-up the device in the

drives the device into either the active mode or the sleep mode. sleep mode. However, if the application requires that the device

A logic low sleep signal drives the device into the sleep mode, be powered on in the active mode, then a 10 kΩ resistor in series

while a logic high sleep signal drives the device into the active ¯Ē¯Ē¯P̄¯ pin is recommended. This resistor will limit the

with the S̄L̄

mode. current that flows into the S̄L̄¯Ē

¯Ē¯P̄¯ pin if certain semiconductor

In the case in which the VREF pin is powered before the VCC junctions become forward biased before the ramp up of the volt-

pin, the device will not operate within the specified limits until age on the VCC pin. Note that this current limiting resistor is not

the supply voltage is equal to the reference voltage. When the required if the user connects the S̄L̄¯Ē¯Ē¯P̄¯ pin directly to the VCC

device is switched from the sleep mode to the active mode, a time pin. The same precautions are advised if the device supply is

defined by tPON must elapse before the output of the device is powered-off while power is still applied to the S̄L̄¯Ē¯Ē ¯P̄¯ pin.

VCC

VSLEEP

ICC

+B

B field 0

–B

HIGH HIGH HIGH

VOUT

IMPEDANCE IMPEDANCE IMPEDANCE

tPON tPON

tPOFF tPOFF

Figure 1. A139x Timing Diagram

Allegro MicroSystems, LLC 10

955 Perimeter Road

Manchester, NH 03103-3353 U.S.A.

www.allegromicro.com

A1391, A1392, Micro Power 3 V Linear Hall Effect Sensor ICs

A1393, and A1395 with Tri-State Output and User Selectable Sleep Mode

Device Supply Ratiometry Application Circuit

Figures 2 and 3 present applications where the VCC pin is con- In both figures, the device output is connected to the input of an

nected together with the VREF pin of the A139x. Both of these A-to-D converter. In this configuration, the converter reference

pins are connected to the battery, Vbat2. In this case, the device voltage is Vbat1.

output will be ratiometric with respect to the battery voltage.

It is strongly recommended that an external bypass capacitor be

The only difference between these two applications is that the

connected, in close proximity to the A139x device, between the

S̄L̄¯Ē¯Ē¯P̄¯ pin in figure 2 is connected to the Vbat2 potential, so the

device is always in the active mode. In figure 3, the S̄L̄¯Ē¯Ē¯P̄¯ pin is VCC and GND pins of the device to reduce both external noise

toggled by the microprocessor; therefore, the device is selectively and noise generated by the chopper-stabilization circuits inside of

and periodically toggled between active mode and sleep mode. the A139x.

Vbat1 Cbypass Vbat2

Supply pin

VCC VREF

Micro- A139x

I/O

processor

OUT SLEEP

I/O

GND GND

Figure 2. Application circuit showing sleep mode disabled and output ratiometirc to the

A139x supply.

Vbat1 Cbypass Vbat2

Supply pin

VCC VREF

Micro-

I/O

A139x

processor

OUT SLEEP

I/O

GND GND

Figure 3. Application circuit showing microprocessor-controlled sleep mode and output ratiome-

tirc to the A139x supply.

Allegro MicroSystems, LLC 11

955 Perimeter Road

Manchester, NH 03103-3353 U.S.A.

www.allegromicro.com

A1391, A1392, Micro Power 3 V Linear Hall Effect Sensor ICs

A1393, and A1395 with Tri-State Output and User Selectable Sleep Mode

Application Circuit with User-Configurable Ratiometry

In figures 4 and 5, the microprocessor supply voltage determines between the active and sleep modes.

the ratiometric performance of the A139x output signal. As in the

The capacitor Cfilter is optional, and can be used to prevent pos-

circuits shown in figures 2 and 3, the device is powered by the

sible noise transients from the microprocessor supply reaching

Vbat2 supply, but in this case, ratiometry is determined by the

microprocessor supply, Vbat1. the device reference pin, VREF.

The S̄L̄¯Ē¯Ē¯P̄¯ pin is triggered by the output logic signal from the It is strongly recommended that an external bypass capacitor be

microprocessor in figure 5, while in figure 4, the S̄L̄¯Ē ¯Ē¯P̄¯ pin is connected, in close proximity to the A139x device, between the

connected to the device power supply pin. Therefore, the device VCC and GND pins of the device to reduce both external noise

as configured in figure 4 is constantly in active mode, while and noise generated by the chopper-stabilization circuits inside of

the device as confiugred in figure 5 can be periodically toggled the A139x.

Cfilter Vbat 1 Cbypass Vbat2

Supply pin

VCC VREF

Micro- I/O A139x

processor

OUT SLEEP

I/O

GND GND

Figure 4. Application circuit showing ratiometry of VREF . Sleep mode is disabled and the VREF

pin is tied to the microprocessor supply.

Cfilter Vbat1 Cbypass Vbat2

Supply pin

VCC VREF

Micro- I/O A139x

processor

OUT SLEEP

I/O

GND GND

Figure 5. Application circuit showing device reference pin, VREF, tied to microprocessor supply. The device

sleep mode also is controlled by the microprocessor.

Allegro MicroSystems, LLC 12

955 Perimeter Road

Manchester, NH 03103-3353 U.S.A.

www.allegromicro.com

A1391, A1392, Micro Power 3 V Linear Hall Effect Sensor ICs

A1393, and A1395 with Tri-State Output and User Selectable Sleep Mode

Summary of Single-Device Application Circuits

Device Pin Connections

Application Circuit VREF pin (Ratiometric Device Output

Reference Supply)

S̄¯

L̄¯

Ē¯

Ē¯

P̄¯ pin

Vbat1 Cbypass Vbat2

Supply pin

VCC VREF

Micro-

I/O A139x Connected to Connected to Ratiometric to device

processor

OUT SLEEP A139x device supply, A139x device supply, supply (VCC), and

VCC VCC always valid

I/O

GND GND

Vbat1 Cbypass Vbat2

Supply pin

VCC VREF

Ratiometric to device

Micro- A139x Connected to

processor

I/O Controlled by supply (VCC), and

A139x device supply,

OUT SLEEP microprocessor controlled by the

VCC

I/O microprocessor

GND GND

Cfilter Vbat 1 Cbypass Vbat2

Supply pin

VCC VREF

Micro- I/O Connected to Ratiometric to micro-

A139x Connected to

processor A139x device supply, processor supply, and

OUT SLEEP microprocessor supply

I/O VCC always valid

GND GND

Cfilter Vbat1 Cbypass Vbat2

Supply pin

VCC VREF Ratiometric to micro-

Micro- I/O A139x Connected to Controlled by processor supply,

processor

OUT SLEEP microprocessor supply microprocessor and controlled by the

I/O microprocessor

GND GND

Allegro MicroSystems, LLC 13

955 Perimeter Road

Manchester, NH 03103-3353 U.S.A.

www.allegromicro.com

A1391, A1392, Micro Power 3 V Linear Hall Effect Sensor ICs

A1393, and A1395 with Tri-State Output and User Selectable Sleep Mode

Application Circuit with Multiple Hall Devices and a Single A-to-D Converter

Multiple A139x devices can be connected to a single micro- ¯Ē

according to microprocessor input to the S̄L̄ ¯Ē

¯P̄¯ pins.

processor or A-to-D converter input. In this case, a single

When multiple device outputs are connected to the same

device is periodically triggered and put into active mode by microprocessor input, pulse timing from the microproces-

the microprocessor. While one A139x device is in active sor (for example, lines A1 through A4 in figure 6) must be

mode, all of the other A139x devices must remain in sleep configured to prevent more than one device from being in the

mode. While these devices are in sleep mode, their outputs awake mode at any given time of the application. A device

are in a high-impedance state. In this circuit configuration, output structure can be damaged when its output voltage is

the microprocessor reads the output of one device at a time, forced above the device supply voltage by more than 0.1 V.

Cbypass Vbat2

VCC VREF

A139x

OUT SLEEP

GND GND

Cbypass Vbat2

VCC VREF

A1391x

OUT SLEEP

Supply pin

Cfilter Vbat1 GND GND

Microprocessor

I/O

A1

Cbypass Vbat2

A2

A1 A3

VCC VREF

A139x

A4

A2 OUT SLEEP

GND GND

A3

A4

Cbypass Vbat2

VCC VREF

A139x

OUT SLEEP

GND GND

Figure 6. Application circuit showing multiple A139x devices, controlled by a single microprocessor.

Allegro MicroSystems, LLC 14

955 Perimeter Road

Manchester, NH 03103-3353 U.S.A.

www.allegromicro.com

A1391, A1392, Micro Power 3 V Linear Hall Effect Sensor ICs

A1393, and A1395 with Tri-State Output and User Selectable Sleep Mode

Package EH, 6-pin MLP/DFN

2.00 ±0.15 0.50

0.30

1.00 E F 6

6

1.00

1.50 E

3.00 ±0.15 3.70 1.25

A E

1 2

1

0.95

7X D C

SEATING

0.08 C PLANE C PCB Layout Reference View

0.25 ±0.05 0.75 ±0.05

0.5 BSC

1 2 YWW

LLL

0.55 ±0.10

NN

1.224 ±0.050

B 1

G Standard Branding Reference View

Y = Last two digits of year of manufacture

W = Week of manufacture

6

L = Lot number

N = Last two digits of device part number

+0.100

1.042 –0.150

For Reference Only, not for tooling use (reference DWG-2861;

reference JEDEC MO-229WCED, Type 1)

Dimensions in millimeters

Exact case and lead configuration at supplier discretion within limits shown

A Terminal #1 mark area D Coplanarity includes exposed thermal pad and terminals

B Exposed thermal pad (reference only, terminal #1

E Hall Element (not to scale); U.S. customary dimensions controlling

identifier appearance at supplier discretion)

C Reference land pattern layout; F Active Area Depth, 0.32 mm NOM

All pads a minimum of 0.20 mm from all adjacent pads; adjust as

necessary to meet application process requirements and PCB layout G Branding scale and appearance at supplier discretion

tolerances; when mounting on a multilayer PCB, thermal vias at the

exposed thermal pad land can improve thermal dissipation (reference

EIA/JEDEC Standard JESD51-5)

Allegro MicroSystems, LLC 15

955 Perimeter Road

Manchester, NH 03103-3353 U.S.A.

www.allegromicro.com

A1391, A1392, Micro Power 3 V Linear Hall Effect Sensor ICs

A1393, and A1395 with Tri-State Output and User Selectable Sleep Mode

Revision History

Revision Revision Date Description of Revision

Rev. 7 October 26, 2011 Update Selection Guide

Rev. 8 February 13, 2019 Minor editorial updates

Copyright ©2019, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to

permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that

the information being relied upon is current.

Allegro’s products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of

Allegro’s product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its

use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com

Allegro MicroSystems, LLC 16

955 Perimeter Road

Manchester, NH 03103-3353 U.S.A.

www.allegromicro.com

You might also like

- Traction Protection RelaysDocument8 pagesTraction Protection Relayskylegaze100% (2)

- Ipc 9592 Final Draft 0407 Normas LayoutDocument92 pagesIpc 9592 Final Draft 0407 Normas LayoutDomRuanNo ratings yet

- Generator NGTR Sizing Calculation PDFDocument1 pageGenerator NGTR Sizing Calculation PDFmv_mallik100% (1)

- Footwear Lab Test Protocol: Full ShoeDocument3 pagesFootwear Lab Test Protocol: Full ShoeFebi Pratama100% (1)

- A1381 AllegroMicroSystemsDocument18 pagesA1381 AllegroMicroSystemsDenis OliveiraNo ratings yet

- A1369 DatasheetDocument22 pagesA1369 Datasheetconaco.tecnologiaNo ratings yet

- A1308 9 DatasheetDocument12 pagesA1308 9 DatasheetRobson Da SilvaNo ratings yet

- A1318 A1319 DatasheetDocument13 pagesA1318 A1319 DatasheetTamás SzabóNo ratings yet

- A1308 and A1309 DatasheetDocument12 pagesA1308 and A1309 DatasheetjeremyNo ratings yet

- Low-Noise Programmable Linear Hall Effect Sensors With Adjustable Bandwidth (50 KHZ Maximum) and Analog OutputDocument25 pagesLow-Noise Programmable Linear Hall Effect Sensors With Adjustable Bandwidth (50 KHZ Maximum) and Analog Outputperon_666No ratings yet

- A1126 DatasheetDocument15 pagesA1126 DatasheetkatofNo ratings yet

- Discontinued Product: A1301 and A1302Document10 pagesDiscontinued Product: A1301 and A1302Nebojša MićićNo ratings yet

- High Accuracy Analog Speed Sensor IC With Integrated Filter Capacitor and Dual Zero-Crossing Output SignalDocument13 pagesHigh Accuracy Analog Speed Sensor IC With Integrated Filter Capacitor and Dual Zero-Crossing Output SignalДрагиша Небитни ТрифуновићNo ratings yet

- A1324 5 6 DatasheetDocument12 pagesA1324 5 6 DatasheetJuan Pablo Merck SifontesNo ratings yet

- A1363LU DatasheetDocument29 pagesA1363LU DatasheetJacopo PacioniNo ratings yet

- A1301 2 Datasheet PDFDocument10 pagesA1301 2 Datasheet PDFJarfoNo ratings yet

- A1324 5 6 DatasheetDocument12 pagesA1324 5 6 DatasheetKrisztian BoneraNo ratings yet

- An 6041.PdfcnDocument6 pagesAn 6041.PdfcncsclzNo ratings yet

- Trasducor Efecto Hall Datasheet.A1120Document9 pagesTrasducor Efecto Hall Datasheet.A1120jorge molinaNo ratings yet

- Low-Noise Linear Hall-Effect Sensor Ics With Analog Output: A1324, A1325, and A1326Document13 pagesLow-Noise Linear Hall-Effect Sensor Ics With Analog Output: A1324, A1325, and A1326Erick GarciaNo ratings yet

- Low-Noise Linear Hall-Effect Sensor Ics With Analog Output: A1324, A1325, and A1326Document13 pagesLow-Noise Linear Hall-Effect Sensor Ics With Analog Output: A1324, A1325, and A1326Leonard GržetićNo ratings yet

- A1301 2 Datasheet PDFDocument10 pagesA1301 2 Datasheet PDFzeze1982No ratings yet

- Data SheetDocument13 pagesData SheetJoão SantosNo ratings yet

- Datasheet Photo SwicthDocument3 pagesDatasheet Photo Swicthdwi aryantoNo ratings yet

- A1302 - Sensor de Efeito Hall Linear PDFDocument10 pagesA1302 - Sensor de Efeito Hall Linear PDFRicardoNo ratings yet

- D UCT: Not Recommended For New DesignsDocument6 pagesD UCT: Not Recommended For New DesignsAdvance CNC TechnologiesNo ratings yet

- Ad 22151Document8 pagesAd 22151hector Miranda BernalNo ratings yet

- A1421 2 3 DatasheetDocument16 pagesA1421 2 3 Datasheetdmitry esaulkovNo ratings yet

- Automatic Switch-Onto-Fault Function For Distance ProtectionDocument6 pagesAutomatic Switch-Onto-Fault Function For Distance ProtectionRhun Riang ChuahNo ratings yet

- GR612Document4 pagesGR612BhootNo ratings yet

- 4601 FeDocument30 pages4601 Fekrushnasis pradhanNo ratings yet

- Asa2310 High-Speed TMR Analog Front-End 1piDocument2 pagesAsa2310 High-Speed TMR Analog Front-End 1piMohammed Abdul HamidNo ratings yet

- RSLM Series Datasheet-1-1 PDFDocument3 pagesRSLM Series Datasheet-1-1 PDFGhayur ShahNo ratings yet

- ACS724LMC, ACS725LMC: High Accuracy Hall-Effect-Based Current Sensor with 265 µΩ Integrated ConductorDocument17 pagesACS724LMC, ACS725LMC: High Accuracy Hall-Effect-Based Current Sensor with 265 µΩ Integrated ConductorRicardo UrioNo ratings yet

- LTC 3124Document28 pagesLTC 3124m3rishorNo ratings yet

- Numerical Over Current Relay Ocr With Earth Fault Relay EfrDocument5 pagesNumerical Over Current Relay Ocr With Earth Fault Relay EfrMohsin NaushadNo ratings yet

- Digital Frequency: Under and Overfrequency Protection in AC SystemsDocument3 pagesDigital Frequency: Under and Overfrequency Protection in AC Systemsgeoff collinsNo ratings yet

- A112x DatasheetDocument18 pagesA112x DatasheetKukinjosNo ratings yet

- IMD Product Manual (Obsolete - For Reference Only)Document4 pagesIMD Product Manual (Obsolete - For Reference Only)Jonathan LujanNo ratings yet

- A1301,02Document10 pagesA1301,02jorje5No ratings yet

- Features Descriptio: LTC1438/LTC1439 Dual High Efficiency, Low Noise, Synchronous Step-Down Switching RegulatorsDocument32 pagesFeatures Descriptio: LTC1438/LTC1439 Dual High Efficiency, Low Noise, Synchronous Step-Down Switching RegulatorsWalberSNo ratings yet

- LM3481MM NOPB National SemiconductorDocument22 pagesLM3481MM NOPB National Semiconductorvs674584No ratings yet

- MDX DC 1kW & 1.5kW SereisDocument6 pagesMDX DC 1kW & 1.5kW SereisBaehyoungryeolNo ratings yet

- LM2641 Dual Adjustable Step-Down Switching Power Supply ControllerDocument29 pagesLM2641 Dual Adjustable Step-Down Switching Power Supply ControllerMohamedKecibaNo ratings yet

- Chopper-Stabilized, Two Wire Hall-Effect Latch: Description Features and BenefitsDocument12 pagesChopper-Stabilized, Two Wire Hall-Effect Latch: Description Features and BenefitsMcOrtiz OrtizNo ratings yet

- Analog Devices Datasheet CN0511Document9 pagesAnalog Devices Datasheet CN0511Ravindra MogheNo ratings yet

- Operating Manual: Vertex Standard LMR, IncDocument32 pagesOperating Manual: Vertex Standard LMR, IncIndra GunawanNo ratings yet

- Isolated Current Output 5B39: FeaturesDocument8 pagesIsolated Current Output 5B39: Featuresjuan olarteNo ratings yet

- Max15058 PDFDocument22 pagesMax15058 PDFjhnkerenNo ratings yet

- Redlion IMPDocument4 pagesRedlion IMPE. MurilloNo ratings yet

- Plasma Manual: ServiceDocument36 pagesPlasma Manual: ServicegondifNo ratings yet

- A115x DatasheetDocument14 pagesA115x DatasheetkhoaNo ratings yet

- Discontinued Product: Chopper-Stabilized Omnipolar Hall-Effect SwitchesDocument13 pagesDiscontinued Product: Chopper-Stabilized Omnipolar Hall-Effect SwitchesCristian BandilaNo ratings yet

- Datasheet MLX92251 PDFDocument13 pagesDatasheet MLX92251 PDFedroalNo ratings yet

- Datasheet - HK Pcf7991at 450658Document1 pageDatasheet - HK Pcf7991at 450658Adrian FernandezNo ratings yet

- Ratiometric Linear Hall Effect Sensor For High-Temperature OperationDocument9 pagesRatiometric Linear Hall Effect Sensor For High-Temperature OperationVishnu K NairNo ratings yet

- General Specifications: Axfa11G Magnetic Flowmeter Remote ConverterDocument10 pagesGeneral Specifications: Axfa11G Magnetic Flowmeter Remote ConverterEmerson Müller Juarez AvilaNo ratings yet

- Sx440 Automatic Voltage Regulator (Avr) : Specification, Installation and AdjustmentsDocument4 pagesSx440 Automatic Voltage Regulator (Avr) : Specification, Installation and AdjustmentsJose PirulliNo ratings yet

- Remsdaq Callisto NXL Lite System BrochureDocument2 pagesRemsdaq Callisto NXL Lite System BrochureFarid AhmadNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Instrumentation and Test Gear Circuits ManualFrom EverandInstrumentation and Test Gear Circuits ManualRating: 5 out of 5 stars5/5 (1)

- Escholarship UC Item 2dx9773tDocument120 pagesEscholarship UC Item 2dx9773tDomRuanNo ratings yet

- BD LBC1020Document7 pagesBD LBC1020DomRuanNo ratings yet

- A Comparative Study of QRDM Detection and Sphere Decoding For MiDocument5 pagesA Comparative Study of QRDM Detection and Sphere Decoding For MiDomRuanNo ratings yet

- On The Use of Generalized DFT-s-OFDM To Reduce Inter-Numerology Interference in 5G-NR NetworksDocument5 pagesOn The Use of Generalized DFT-s-OFDM To Reduce Inter-Numerology Interference in 5G-NR NetworksDomRuanNo ratings yet

- PTS OfdmDocument4 pagesPTS OfdmDomRuanNo ratings yet

- PAPR Reduction in GFDM SystemsDocument41 pagesPAPR Reduction in GFDM SystemsDomRuanNo ratings yet

- Signal Processing: Markus Myllyl A, Markku Juntti, Joseph R. CavallaroDocument14 pagesSignal Processing: Markus Myllyl A, Markku Juntti, Joseph R. CavallaroDomRuanNo ratings yet

- New Transceiver Scheme For OFDM-Based Broadband Power Line CommunicationsDocument12 pagesNew Transceiver Scheme For OFDM-Based Broadband Power Line CommunicationsDomRuanNo ratings yet

- EMSpringerDocument12 pagesEMSpringerDomRuanNo ratings yet

- User Guide 使用说明 ユーザーガイド 사용자 가이드Document26 pagesUser Guide 使用说明 ユーザーガイド 사용자 가이드DomRuanNo ratings yet

- A List Sphere Detector Based On Dijkstra'S Algorithm For Mimo-Ofdm SystemsDocument5 pagesA List Sphere Detector Based On Dijkstra'S Algorithm For Mimo-Ofdm SystemsDomRuanNo ratings yet

- Parallel Searching-Based Sphere Detector For MIMODocument14 pagesParallel Searching-Based Sphere Detector For MIMODomRuanNo ratings yet

- Parallel Searching-Based Sphere Detector For MIMO Downlink OFDM SystemsDocument13 pagesParallel Searching-Based Sphere Detector For MIMO Downlink OFDM SystemsDomRuanNo ratings yet

- Steiner Sensors 2010Document4 pagesSteiner Sensors 2010DomRuanNo ratings yet

- Rado Savlje Vic 2009Document13 pagesRado Savlje Vic 2009DomRuanNo ratings yet

- Fixed Effort Sphere Decoder For MIMO OFDM Systems: Nora Tax and Berthold LanklDocument6 pagesFixed Effort Sphere Decoder For MIMO OFDM Systems: Nora Tax and Berthold LanklDomRuanNo ratings yet

- No Guera 2011Document11 pagesNo Guera 2011DomRuanNo ratings yet

- Comparison of Two Novel List Sphere Detector Algorithms For Mimo-Ofdm SystemsDocument5 pagesComparison of Two Novel List Sphere Detector Algorithms For Mimo-Ofdm SystemsDomRuanNo ratings yet

- Reduced Complexity Soft-Output MIMO Sphere Detectors-Part II: Architectural OptimizationsDocument15 pagesReduced Complexity Soft-Output MIMO Sphere Detectors-Part II: Architectural OptimizationsDomRuanNo ratings yet

- Signal Processing: Janne Janhunen, Olli Silve N, Markku JunttiDocument11 pagesSignal Processing: Janne Janhunen, Olli Silve N, Markku JunttiDomRuanNo ratings yet

- User'S Guide: Tms320Dm36X Digital Media System-On-Chip (Dmsoc) Ethernet Media Access Controller (Emac)Document134 pagesUser'S Guide: Tms320Dm36X Digital Media System-On-Chip (Dmsoc) Ethernet Media Access Controller (Emac)DomRuanNo ratings yet

- Adaptive Radius Sphere Detection in MIMO OFDM Systems: March 2015Document4 pagesAdaptive Radius Sphere Detection in MIMO OFDM Systems: March 2015DomRuanNo ratings yet

- Sensors 20 05586 v2Document41 pagesSensors 20 05586 v2DomRuanNo ratings yet

- A Configurable Medium Access Control Protocol For IEEE 802.15.4 NetworksDocument8 pagesA Configurable Medium Access Control Protocol For IEEE 802.15.4 NetworksDomRuanNo ratings yet

- Steiner Sensors 2010Document4 pagesSteiner Sensors 2010DomRuanNo ratings yet

- Aprendendo Python PDFDocument576 pagesAprendendo Python PDFDomRuanNo ratings yet

- STM32G031x4/x6/x8: Arm Cortex - M0+ 32-Bit MCU, Up To 64 KB Flash, 8 KB RAM, 2x USART, Timers, ADC, Comm. I/Fs, 1.7-3.6VDocument117 pagesSTM32G031x4/x6/x8: Arm Cortex - M0+ 32-Bit MCU, Up To 64 KB Flash, 8 KB RAM, 2x USART, Timers, ADC, Comm. I/Fs, 1.7-3.6VDomRuanNo ratings yet

- Polymer Plain BearingsDocument269 pagesPolymer Plain BearingsMartí BertranNo ratings yet

- P2019 Bba-403Document2 pagesP2019 Bba-403cantabpublisher98No ratings yet

- Scientists Who Believe The Bible-1Document26 pagesScientists Who Believe The Bible-1Carla MeloNo ratings yet

- 4.12 ETH CableDocument4 pages4.12 ETH CableadinugrohoNo ratings yet

- Use of IS EN 1991-1-7 For The Design of The Accidental ActionsDocument23 pagesUse of IS EN 1991-1-7 For The Design of The Accidental Actionsdalton wongNo ratings yet

- H07RN Cables Top CablesDocument6 pagesH07RN Cables Top CablesElsan BalucanNo ratings yet

- Module 2 Class 9 Atoms and MoleculesDocument3 pagesModule 2 Class 9 Atoms and Moleculesmyshachaudhuri75No ratings yet

- Analog and Mixed-Signal Modeling Using VHDL-AMSDocument199 pagesAnalog and Mixed-Signal Modeling Using VHDL-AMSmarcos78arNo ratings yet

- Cambridge IGCSE: Combined Science 0653/63Document16 pagesCambridge IGCSE: Combined Science 0653/63septina restuNo ratings yet

- Specification - Particle BoardDocument2 pagesSpecification - Particle BoardAlcoholic MeNo ratings yet

- SMC-3, SMC Flex, and SMC-50 Smart Motor Controller SpecificationsDocument168 pagesSMC-3, SMC Flex, and SMC-50 Smart Motor Controller Specificationsoscard1ofNo ratings yet

- C766 Crack Calculator For WallsDocument23 pagesC766 Crack Calculator For WallsMajdoline SadeddineNo ratings yet

- Oua3-Srme-lt-0001 Rev 3 Mechanical Equipment ListDocument5 pagesOua3-Srme-lt-0001 Rev 3 Mechanical Equipment ListmessaoudiNo ratings yet

- 1HID1-3-4048-E022 GIS Buiding Foundation Calculation NotesDocument53 pages1HID1-3-4048-E022 GIS Buiding Foundation Calculation Notesanisya lestariNo ratings yet

- Iso/ts 6336-20:2017 (E)Document5 pagesIso/ts 6336-20:2017 (E)Anirban DasNo ratings yet

- LAS SHS PhySci MELC 7 Q2 Week-3Document10 pagesLAS SHS PhySci MELC 7 Q2 Week-3Nini VillezaNo ratings yet

- 3-Komponen Dasar ElektronikaDocument42 pages3-Komponen Dasar ElektronikaNovia Diajeng ArumsariNo ratings yet

- Combustion Chemstry1Document6 pagesCombustion Chemstry1Dr Mohammad AlzoubyNo ratings yet

- Metrology-and-Measurement-Laboratory-Manual ReferenceDocument32 pagesMetrology-and-Measurement-Laboratory-Manual Referencechandrarao chNo ratings yet

- T3 Revision Internal ResistanceDocument22 pagesT3 Revision Internal Resistancejordan2gardnerNo ratings yet

- Declaration of Conformity: Elcometer LimitedDocument1 pageDeclaration of Conformity: Elcometer Limitedhadyan rafdiNo ratings yet

- Is There A Relationship Between Landing, Cutting, and Pivoting Tasks in Terms of The Characteristics of Dynamic Valgus?Document8 pagesIs There A Relationship Between Landing, Cutting, and Pivoting Tasks in Terms of The Characteristics of Dynamic Valgus?Sebastian BejaranoNo ratings yet

- Sinano Ja enDocument53 pagesSinano Ja enTrung kien NguyenNo ratings yet

- EE All TutorialsDocument39 pagesEE All Tutorialsjoahua mickkinNo ratings yet

- Huygens' Principle: Traite de La LumiereDocument10 pagesHuygens' Principle: Traite de La LumiereNathalie LaurinNo ratings yet

- Subarc 5Document60 pagesSubarc 5Geoffroy CECCONENo ratings yet

- Nuclear Over Hauser Enhancement (NOE)Document18 pagesNuclear Over Hauser Enhancement (NOE)Fatima AhmedNo ratings yet

- Raman Nath Diffraction ManualDocument8 pagesRaman Nath Diffraction ManualPratik PatnaikNo ratings yet