Professional Documents

Culture Documents

R2 3 Quartus2 Introduction

R2 3 Quartus2 Introduction

Uploaded by

Masood Ur RehmanCopyright:

Available Formats

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5834)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (823)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (405)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Self Reference CriterionDocument2 pagesSelf Reference CriterionJaemarie CamachoNo ratings yet

- Wire Wrap IDs and LabelsDocument1 pageWire Wrap IDs and LabelsKarthik V KalyaniNo ratings yet

- Training TC Theory SaafgDocument6 pagesTraining TC Theory SaafgMuhammad Ikhsan HermasNo ratings yet

- DenverToBlrAndReturn Travel InfoDocument2 pagesDenverToBlrAndReturn Travel InfoKarthik V KalyaniNo ratings yet

- 150 Word StudiesDocument304 pages150 Word StudiesKarthik V KalyaniNo ratings yet

- Functional Analysis Module V1.0Document21 pagesFunctional Analysis Module V1.0Karthik V KalyaniNo ratings yet

- Exercise 2 RequirementsDocument4 pagesExercise 2 RequirementsKarthik V KalyaniNo ratings yet

- Elec 533Document2 pagesElec 533Karthik V KalyaniNo ratings yet

- Direct File Topic DownloadDocument4 pagesDirect File Topic DownloadKarthik V KalyaniNo ratings yet

- 1 What Is A Digital Audio Effect?: Daniel ArfibDocument4 pages1 What Is A Digital Audio Effect?: Daniel ArfibKarthik V KalyaniNo ratings yet

- Time-Frequency Joint Sparse Channel Estimation For MIMO-OFDM SystemsDocument4 pagesTime-Frequency Joint Sparse Channel Estimation For MIMO-OFDM SystemsKarthik V KalyaniNo ratings yet

- Verilog Design) and Dump Code Using Programmer. Test by Sliding SwitchesDocument4 pagesVerilog Design) and Dump Code Using Programmer. Test by Sliding SwitchesKarthik V KalyaniNo ratings yet

- Independent Study Agreement: College of Engineering and Applied ScienceDocument2 pagesIndependent Study Agreement: College of Engineering and Applied ScienceKarthik V KalyaniNo ratings yet

- Project2 PsocDocument10 pagesProject2 PsocKarthik V KalyaniNo ratings yet

- Compilation of Assignments: Structural Theory IDocument2 pagesCompilation of Assignments: Structural Theory ITejay TolibasNo ratings yet

- Ready To Use 101 Powerful Excel VBA Code Just Copy - Paste - Run (For Functional Users) (Anil Nahar) (Z-Library)Document152 pagesReady To Use 101 Powerful Excel VBA Code Just Copy - Paste - Run (For Functional Users) (Anil Nahar) (Z-Library)rahulNo ratings yet

- Intelligent Urbanism: Convivial Living in Smart Cities: Stephanie Santoso Andreas KuehnDocument5 pagesIntelligent Urbanism: Convivial Living in Smart Cities: Stephanie Santoso Andreas KuehnAdrian VodițăNo ratings yet

- 4 Process - Analysis - Practice - Problem - SolutionsDocument7 pages4 Process - Analysis - Practice - Problem - SolutionsHEMANT KUMARNo ratings yet

- Businessstudy Xii DDocument2 pagesBusinessstudy Xii Dvarun ChoudharyNo ratings yet

- 2019 (Gatsov-Nedelcheva) Pietrele 2 Lithic-Industry (Small)Document177 pages2019 (Gatsov-Nedelcheva) Pietrele 2 Lithic-Industry (Small)Clive BonsallNo ratings yet

- Welder's Qualification Test CertificateDocument1 pageWelder's Qualification Test CertificatekannanNo ratings yet

- Corrosión Manual NalcoDocument126 pagesCorrosión Manual NalcotinovelazquezNo ratings yet

- St. Andrew Academy Bacarra, Ilocos Norte First Grading-Grade 7 MathematicsDocument10 pagesSt. Andrew Academy Bacarra, Ilocos Norte First Grading-Grade 7 MathematicsJACOBAGONOYNo ratings yet

- Research/Capstone Project RubricDocument4 pagesResearch/Capstone Project RubricMark Alvin Jay CarpioNo ratings yet

- Foundation Design ProjectDocument31 pagesFoundation Design ProjectChoco Late100% (1)

- On Thi Cao Hoc Mon Linguistics PDFDocument210 pagesOn Thi Cao Hoc Mon Linguistics PDFThinh PhanNo ratings yet

- Projectile Motion EtoosDocument24 pagesProjectile Motion EtoosT sidharth100% (1)

- Classical and Operant ConditioningDocument14 pagesClassical and Operant ConditioningrajnaNo ratings yet

- Chapter 5 - Welding Joint Design and Welding SymbolsDocument43 pagesChapter 5 - Welding Joint Design and Welding Symbolsyves suarezNo ratings yet

- F520Document2 pagesF520Marcos AldrovandiNo ratings yet

- IADC Daily Drilling Report RevADocument4 pagesIADC Daily Drilling Report RevAdullahnurkalimNo ratings yet

- Z370 AORUS Gaming 3: User's ManualDocument48 pagesZ370 AORUS Gaming 3: User's ManualAtrocitus RedNo ratings yet

- Basic COMPETENCIES Module of InstructionDocument18 pagesBasic COMPETENCIES Module of InstructionMarveen TingkahanNo ratings yet

- Angell Mobile X-Ray Machine DP326 USER MANUALDocument149 pagesAngell Mobile X-Ray Machine DP326 USER MANUALBiomedical STRH100% (2)

- Man and SupermanDocument4 pagesMan and SupermanSrestha Kar100% (1)

- Edison Robot BarcodesDocument4 pagesEdison Robot BarcodesethanNo ratings yet

- SECOND Periodic Test in AP 4 With TOS SY 2022 2023Document6 pagesSECOND Periodic Test in AP 4 With TOS SY 2022 2023MICHAEL VERINANo ratings yet

- Lumix Dmcgm5kpDocument62 pagesLumix Dmcgm5kpArif SriwidodoNo ratings yet

- ICN AVoiceToLead Guidancepack-9Document60 pagesICN AVoiceToLead Guidancepack-9Muh. AkbarNo ratings yet

- UntitledDocument27 pagesUntitledFlavio MagelaNo ratings yet

- GalvinDocument9 pagesGalvinІгор ШNo ratings yet

- Sol8 PDFDocument11 pagesSol8 PDFMichael ARKNo ratings yet

- TrackersDocument14 pagesTrackersSabahudinBuroNo ratings yet

R2 3 Quartus2 Introduction

R2 3 Quartus2 Introduction

Uploaded by

Masood Ur RehmanCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

R2 3 Quartus2 Introduction

R2 3 Quartus2 Introduction

Uploaded by

Masood Ur RehmanCopyright:

Available Formats

Introduction to Quartus II Software

Introduction to Quartus II Software

The Altera® Quartus® II design software is a multiplatform design environment that easily adapts to your specific

needs in all phases of FPGA and CPLD design. Quartus II software delivers the highest productivity and

performance for Altera FPGAs, CPLDs, and HardCopy® ASICs.

Quartus II software delivers superior synthesis and placement and routing, resulting in compilation time

advantages. Compilation time reduction features include:

• Multiprocessor support

• Rapid Recompile

• Incremental compilation

Incremental Compilation and Rapid Recompile

Quartus II Analysis and Synthesis, together with the Quartus II Fitter, incrementally compiles only the parts of your

design that change between compilations. By compiling only changed partitions, incremental compilation reduces

compilation time by up to 70 percent.

For small engineering change orders (ECOs), the Rapid Recompile feature maximizes your productivity by reducing

your compilation time by 65 percent on average, and improves design timing preservation.

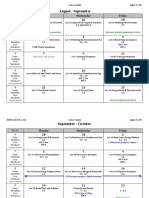

Compilation Time Comparison

Quartus II Relative Compilation Time by Release

(Relative Time Based on Fixed Designs and Fixed CPU)

Simulation

100%

You can perform the

75% functional and timing

simulation of your design

Relative Compile Time (Log Scale)

with the ModelSim®-Altera

50% Edition software, or any

EDA simulators supported

by Quartus II software. The

Quartus II NativeLink

feature allows you to run

25%

your third-party simulator

and other EDA tools from

within Quartus II software.

10%

4.0 5.0 6.0 7.0 8.0 9.0 10.0 11.0

Quartus II Software Version

The Qsys system integration tool saves significant time and effort in the

FPGA design process by automatically generating interconnect logic to

connect IP functions and subsystems. Qsys is the next-generation SOPC

Builder tool powered by a new FPGA-optimized Network-on-a-Chip

(NoC) technology delivering high-performance, scalable systems, and

improved design reuse opportunities.

4.0 5.0 6.0 7.0 8.0 9.0 10.0 11.0.

2 Quartus II Design Software • 2011 • www.altera.com

For v11.0, use v10.1 data point.

Design Entry

Your design can begin as HDL or a schematic. The MegaWizard™ Plug-In Manager helps you create or modify design

files that contain custom megafunction variations, which you can then instantiate in a design file.

Timing and Power Analysis TimeQuest Timing Analyzer

The Quartus II TimeQuest timing analyzer

allows you to analyze the timing characteristics

of your design. Altera is the only FPGA vendor

with comprehensive Synopsys Design Con-

straints (SDC) support in its second-generation,

easy-to-use timing analyzer. The TimeQuest

analyzer offers a complete GUI and scripting

environment to create timing constraints and

reports. It also includes a timing analysis wizard

that makes it easy to create initial constraints.

The Quartus II PowerPlay power analysis and optimization tools

PowerPlay Power Analyzer Flow allow you to estimate power consumption throughout the design

cycle. They use power optimization technology, which provides on

Speed

Design average a 10-percent reduction in power consumption. The Altera

Constraints Area

Entry PowerPlay Early Power Estimator estimates power consumption

Power

and produces a Microsoft Excel-based spreadsheet with estimate

information. The PowerPlay power analyzer performs post-fitting

Synthesis power analysis and reports power characteristics by device resource

and design entity.

Placement and

Routing PowerPlay

Power Analyzer

Optimize Power

Power-Optimized Design

Verification

Quartus II software offers several tools to help you analyze the results of compilation and fitting. Verification with the

SignalTap™ II logic analyzer and the System Console allows you to probe your design as it functions on the device

and in the system.

Links to Online Resources

Video: Basic Compilation Flow

Documentation: Design Planning with the Quartus II Software

Quartus II Design Software • 2011 • www.altera.com 3

Design Entry

Qsys

The Qsys system integration tool saves significant time and effort in the FPGA design process by automatically generat-

ing interconnect logic to connect custom HDL design blocks, commonly referred to as design modules; intellectual

property (IP) cores; and components. Qsys is powered by a new FPGA-optimized NoC–based technology delivering

higher performance. Qsys also raises the level of abstraction and increases productivity by enabling design reuse and

scalable systems.

Qsys Interconnect Fabric Example

Control A Control B

32 Bit 32 Bit

Memory A

Address

Data

Address

Data

Interrupt

Controller

Arbiter

Width Match Width Match Width Match Width Match Width Match

Processing 1 Processing 2 Processing 3 Processing 4 Processing 5

... Processing X

8 Bit 8 Bit 16 Bit 64 Bit 64 Bit

Address

Arbiter

Data

Memory B Memory C

Clock 1 Clock 2 Qsys Auto-Generated Interconnect

Quartus II Block Editor

The Quartus II Block Editor allows you to enter and edit graphic design information in the form of schematics and block

diagrams. The Block Editor reads and edits Block Design Files (.bdf) that contain blocks and symbols representing logic.

MegaWizard Plug-In Manager

The MegaWizard Plug-In Manager helps you create or modify design files that contain custom megafunction variations,

which you can then instantiate in a design file. The MegaWizard Plug-In Manager allows you to set values for param-

eters and optional ports.

4 Quartus II Design Software • 2011 • www.altera.com

Design Partitions

You can assign design entities to design partitions—logical design blocks that are preserved or recompiled during

incremental compilation. Incremental compilation saves you time and effort by recompiling only those design partitions

you are optimizing. Quartus II software preserves previous compilation results for partitions that already meet your

design requirements. The Design Partition Planner allows you to view a graphical representation of your design

hierarchy and assists you in creating effective design partitions.

Links to Online Resources

Video: Design Entry

Webcast: Why You Should Evaluate Qsys System Integration Tool

Quartus II Online Help: About Design Entry

Web: Design Entry and Planning Resource Center

Documentation: Creating a System with Qsys

Incremental Design Planning and Methodology

Quartus II software is tailored to several different design methodologies, including incremental compilation design

flows and block-based design flows. In a team-based incremental compilation flow, the design is divided into partitions.

Each team member can functionally verify a partition independently, and then simply provide the source code for the

partition to a project lead for integration. Using placeholders, the project lead can compile the larger design even if the

source code is not yet complete for a partition.

Compiling all design partitions in a single Quartus II project ensures that the design is compiled with a consistent set of

assignments.

Incremental design encompasses the following:

• Synthesis

• Design partitioning

• Full compilation

• Simulation, verification, and analysis, followed by changes to the design

• Recompilation of only changed elements of the design hierarchy

Links to Online Resources

Video: Incremental Compilation

Video: Rapid Recompile

Web: Incremental Compilation Resource Center

Online Help: About Incremental Compilation

Documentation: Best Practices for Incremental Compilation Partitions and

Floorplan Assignments

Documentation: Quartus II Handbook: Incremental Compilation for

Hierarchical and Team-Based Design

Quartus II Design Software • 2011 • www.altera.com 5

Quartus Integrated Synthesis and the Fitter

Quartus II software includes a comprehensive integrated synthesis solution and advanced integration with leading

third-party synthesis software vendors. Quartus II integrated synthesis fully supports the Verilog HDL and VHDL

languages, and includes algorithms to minimize gate count, remove redundant logic, and use device architecture

efficiently. Quartus II integrated synthesis includes advanced synthesis options and compiler directives to guide the

synthesis process to achieve optimal results.

The Quartus II Fitter places and routes your design for the target device. Using the database created by Quartus II

integrated synthesis, the Fitter matches the logic and timing requirements of the project with the available resources of

the target device. It assigns each logic function to the best logic cell location for routing and timing, and selects appro-

priate interconnection paths and pin assignments.

Netlist Viewers and the Chip Planner

The Quartus II RTL Viewer, State Machine Viewer, and Technology Map Viewer provide powerful ways to view your

initial and fully mapped synthesis results during the debugging, optimization, and constraint entry processes. The Chip

Planner supports ECOs by allowing quick and efficient changes to your logic late in the design cycle. It provides a visual

display of your post placement-and-routing design mapped to device architecture, and allows you to create, move, and

delete specific routing and resource usage.

Links to Online Resources Compare Full and Incremental Compilation

Web: Synthesis and Netlist Incremental Compilation

Full Compilation

Viewers Resource Center Top-Down Approach

Online Help: About the Netlist Create Design Partitions (A, B, C)

Viewers

Quartus II Project

Quartus II Project

Online Help: About the Chip Step 1 Step 1

(No Partitions) AA B

B C

C

Planner

Modify Design (In Red) Modify Design in Partition A

Re-Compile Whole Project Re-Compile Only Partition A

Quartus II Project

Quartus II Project

Step 2 (No Partitions) Step 2

AA B

B C

C

6 Quartus II Design Software • 2011 • www.altera.com

Making Assignments

Assignments allow you to specify various options and settings for the logic in your design. When you make resource

assignments in your design, Quartus II software attempts to match those resource assignments with the resources on the

device, meet any other constraints you have set, and then optimize the remaining logic in the design. The Assignment

Editor and Pin Planner are interfaces for creating and editing pin, node, and entity-level assignments in Quartus II

software. The Pin Planner allows you to make assignments to individual pins and also groups of pins. It includes a

package view of the device with different colors and symbols that represent the different types of pins and additional

symbols that represent I/O banks. The symbols used in the Pin Planner are very similar to the symbols used in device

family data sheets.

Assignment Entry Flow

Links to Online Resources

Online Help: About Assignments Quartus II

Settings Dialog Box Quartus II

Online Help: About the Pin Design Files

Planner Quartus II

Documentation: Constraining Assignment Editor

Quartus II To Quartus II

Designs Project File (.qpf) Analysis &

Quartus II

Synthesis

Documentation: I/O Management Pin Planner

Quartus II

Quartus II Settings File (.qsf)

Design Partitions

Window

Verilog Quartus

Quartus II Mapping Files (.vqm)

Chip Planner

From Block-Based Design

TimeQuest

Timing Analyzer

Synopsys Design

Constraints File (.sdc)

Simulation

You can perform functional and Altera provides functional simulation libraries for designs that contain

timing simulation of your design with Altera-specific components, and atom-based timing simulation libraries for

the ModelSim-Altera Edition software designs compiled in Quartus II software.

or any EDA simulators supported by

Quartus II software also allows you to use the EDA tools you are familiar with

Quartus II software. Quartus II

for other stages of the design flow, including synthesis, timing analysis, and

software provides the following

formal verification.

features for performing simulation:

• NativeLink integration with

simulation tools Links to Online Resources

• Generation of output netlist files

Video: ModelSim Simulation

• Functional and timing simulation

Web: EDA Partners

libraries

Online Help: About Using the ModelSim Software with the Quartus II

• Generation of testbench templates

Software

and memory initialization

Documentation: Simulating Altera Designs

• Generation of input for power analysis

Quartus II Design Software • 2011 • www.altera.com 7

The TimeQuest Timing Analyzer

Links to Online Resources

The TimeQuest timing analyzer is a powerful ASIC-style timing analysis tool

that uses industry-standard constraint, analysis, and reporting methodologies. Video: TimeQuest Timing

You can use SDC commands and formatting to direct the analysis, and also to Analysis

instruct the Quartus II Fitter to optimize the placement of logic in the device Web: TimeQuest Timing

in order to meet timing constraints. Analyzer Resource Center

The TimeQuest analyzer analyzes the timing paths in the design, calculates Online Help: About TimeQuest

the propagation delay along each path, checks for timing constraint violations, Timing Analysis

and reports results. If the TimeQuest analyzer reports timing violations, you

can customize the reports to view precise timing information about specific Documentation: The Quartus II

paths. You can then determine whether the design requires additional timing TimeQuest Timing Analyzer

constraints or exceptions, logic changes, or placement-and-routing con- Documentation: Best Practices

straints. for the Quartus II TimeQuest

Timing Analyzer

The PowerPlay Power Analyzer

The Quartus II PowerPlay power analysis tools allow you to estimate static and dynamic power consumption throughout

the design cycle. The PowerPlay power analyzer produces a power report that highlights–by block type and entity–the

power consumed, allowing you to plan for thermal conditions and power supply requirements.

The PowerPlay power analyzer

accepts information from a variety

Power Analysis Flow

of data sources, and analyzes it

with several factors affecting

From Quartus II Analysis & Synthesis and Quartus II Fitter

power consumption. The result is a

Quartus II PowerPlay

high-quality power estimate. It Power Analyzer

reports total calculated dynamic quartus_pow

and static thermal power con- From Quartus II

Simulator or Quartus II Settings Signal Activity

sumption, current consumed from File (.saf)

Other EDA File (.qsf)

voltage sources, a summary of the Signal Activity File

Simulation Tool

signal activities used for analysis, (.saf) or Value Change Dump File (.vcd)

and a confidence metric detailing User-Defined PowerPlay Early

the various inputs on which it Settings Power Estimator Report

bases the power analysis. From Quartus II Spreadsheet Files

Compiler (.rpt, .htm)

Power Estimation File (<revision name>_early_pwr.csv)

Links to Online Resources

Video: PowerPlay Power Analyzer - Power Analysis

Web: PowerPlay Power Analyzer Support Resources

Online Help: About the PowerPlay Power Analyzer

Online Help: Performing an Early Power Estimate Using the PowerPlay Early Power Estimator

Documentation: PowerPlay Power Analysis

8 Quartus II Design Software • 2011 • www.altera.com

Verification

Quartus II software provides several verification tools that allow you to analyze your design operating in-system and at

system speeds:

• The SignalTap II logic analyzer allows you to route signals through the JTAG interface to Quartus II software based on

user-defined trigger conditions.

• The SignalProbe feature allows you to use otherwise unused device routing resources to route selected signals to an

external logic analyzer or oscilloscope.

• The In-System Memory Content and In-System Sources and Probes Editors allow you to view and modify data in a

design at run time.

• The external logic analyzer interface and virtual JTAG interface allow you fully customized interaction with your

design.

• The Simultaneous Switching Noise (SSN) Analyzer supports I/O planning by estimating the voltage noise caused by

the simultaneous switching of output pins.

System Console

System Console provides you with Tcl scripts and a GUI to perform low-level hardware debugging of your design, to

identify a Qsys module by its path, and to open and close a debugging connection to a module. You can use the

Transceiver Toolkit component of the System Console to set up channel links in your transceiver-based designs, and

then automatically run EyeQ and Auto Sweep testing for a graphical view of your test.

Links to Online Resources

Video: Transceiver Toolkit

Web: On-Chip Debugging Design Examples

Documentation: System Debugging Tools Overview

Quartus II Design Software • 2011 • www.altera.com 9

For More Information

Online Help Altera Software Installation and Licensing

manual

http://quartushelp.altera.com

http://www.altera.com/literature/manual/

Quartus II software includes a browser-based Help

quartus_install.pdf

system that provides comprehensive documentation

for Quartus II software. The Help system is also The Altera Software Installation and Licensing

available separately from the Quartus II software. manual provides detailed information about

software requirements, installation, and licensing

for Windows and Linux workstations.

Knowledge Database

http://www.altera.com/support/kdb/kdb-index.jsp Other Altera Literature

The Altera Knowledge Database provides support

http://www.altera.com/literature/lit-qts.jsp

solutions, frequently asked questions, and known

issues. The literature that is available from the Altera

website is the most current information about

Altera products and features; it is updated

frequently, even after a product has been released.

The Quartus II Interactive Tutorial

Altera continues to add literature on the latest

product features and also any additional informa-

http://www.altera.com/education/training/courses/ tion as requested by customers.

ODSW1050

Web: Ordering Information http://www.altera.

Quartus II software includes the Flash-based com/buy/software/buy-software.html

Quartus II Interactive Tutorial. The modules of this

tutorial teach you how to use the basic features of Training: Using the Quartus II Software: An

Quartus II design software, including design entry, Introduction http://www.altera.com/education/

compilation, timing analysis, programming, training/courses/ODSW1100

incremental compilation, debugging, and the Qsys

system integration tool.

Quartus II Handbook

http://www.altera.com/literature/hb/qts/

quartusii_handbook.pdf

The Quartus II Handbook provides comprehensive

information about the programmable logic design

cycle from design to verification.

10 Quartus II Design Software • 2011 • www.altera.com

Altera Corporation Altera European Headquarters Altera Japan Ltd. Altera International Ltd.

101 Innovation Drive Holmers Farm Way Shinjuku i-Land Tower 32F Unit 11-18, 9/F

San Jose, CA 95134 High Wycombe 6-5-1, Nishi-Shinjuku Millennium City 1, Tower 1

USA Buckinghamshire Shinjuku-ku, Tokyo 163-1332 388 Kwun Tong Road

www.altera.com HP12 4XF Japan Kwun Tong

United Kingdom Telephone: (81) 3 3340 9480 Kowloon, Hong Kong

Telephone: (44) 1494 602000 www.altera.co.jp Telephone: (852) 2945 7000

Copyright © 2011 Altera Corporation. All rights reserved. Altera, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks

are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera

products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights. PDF, April 2011 GB-1003-1.0

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5834)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (823)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (405)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Self Reference CriterionDocument2 pagesSelf Reference CriterionJaemarie CamachoNo ratings yet

- Wire Wrap IDs and LabelsDocument1 pageWire Wrap IDs and LabelsKarthik V KalyaniNo ratings yet

- Training TC Theory SaafgDocument6 pagesTraining TC Theory SaafgMuhammad Ikhsan HermasNo ratings yet

- DenverToBlrAndReturn Travel InfoDocument2 pagesDenverToBlrAndReturn Travel InfoKarthik V KalyaniNo ratings yet

- 150 Word StudiesDocument304 pages150 Word StudiesKarthik V KalyaniNo ratings yet

- Functional Analysis Module V1.0Document21 pagesFunctional Analysis Module V1.0Karthik V KalyaniNo ratings yet

- Exercise 2 RequirementsDocument4 pagesExercise 2 RequirementsKarthik V KalyaniNo ratings yet

- Elec 533Document2 pagesElec 533Karthik V KalyaniNo ratings yet

- Direct File Topic DownloadDocument4 pagesDirect File Topic DownloadKarthik V KalyaniNo ratings yet

- 1 What Is A Digital Audio Effect?: Daniel ArfibDocument4 pages1 What Is A Digital Audio Effect?: Daniel ArfibKarthik V KalyaniNo ratings yet

- Time-Frequency Joint Sparse Channel Estimation For MIMO-OFDM SystemsDocument4 pagesTime-Frequency Joint Sparse Channel Estimation For MIMO-OFDM SystemsKarthik V KalyaniNo ratings yet

- Verilog Design) and Dump Code Using Programmer. Test by Sliding SwitchesDocument4 pagesVerilog Design) and Dump Code Using Programmer. Test by Sliding SwitchesKarthik V KalyaniNo ratings yet

- Independent Study Agreement: College of Engineering and Applied ScienceDocument2 pagesIndependent Study Agreement: College of Engineering and Applied ScienceKarthik V KalyaniNo ratings yet

- Project2 PsocDocument10 pagesProject2 PsocKarthik V KalyaniNo ratings yet

- Compilation of Assignments: Structural Theory IDocument2 pagesCompilation of Assignments: Structural Theory ITejay TolibasNo ratings yet

- Ready To Use 101 Powerful Excel VBA Code Just Copy - Paste - Run (For Functional Users) (Anil Nahar) (Z-Library)Document152 pagesReady To Use 101 Powerful Excel VBA Code Just Copy - Paste - Run (For Functional Users) (Anil Nahar) (Z-Library)rahulNo ratings yet

- Intelligent Urbanism: Convivial Living in Smart Cities: Stephanie Santoso Andreas KuehnDocument5 pagesIntelligent Urbanism: Convivial Living in Smart Cities: Stephanie Santoso Andreas KuehnAdrian VodițăNo ratings yet

- 4 Process - Analysis - Practice - Problem - SolutionsDocument7 pages4 Process - Analysis - Practice - Problem - SolutionsHEMANT KUMARNo ratings yet

- Businessstudy Xii DDocument2 pagesBusinessstudy Xii Dvarun ChoudharyNo ratings yet

- 2019 (Gatsov-Nedelcheva) Pietrele 2 Lithic-Industry (Small)Document177 pages2019 (Gatsov-Nedelcheva) Pietrele 2 Lithic-Industry (Small)Clive BonsallNo ratings yet

- Welder's Qualification Test CertificateDocument1 pageWelder's Qualification Test CertificatekannanNo ratings yet

- Corrosión Manual NalcoDocument126 pagesCorrosión Manual NalcotinovelazquezNo ratings yet

- St. Andrew Academy Bacarra, Ilocos Norte First Grading-Grade 7 MathematicsDocument10 pagesSt. Andrew Academy Bacarra, Ilocos Norte First Grading-Grade 7 MathematicsJACOBAGONOYNo ratings yet

- Research/Capstone Project RubricDocument4 pagesResearch/Capstone Project RubricMark Alvin Jay CarpioNo ratings yet

- Foundation Design ProjectDocument31 pagesFoundation Design ProjectChoco Late100% (1)

- On Thi Cao Hoc Mon Linguistics PDFDocument210 pagesOn Thi Cao Hoc Mon Linguistics PDFThinh PhanNo ratings yet

- Projectile Motion EtoosDocument24 pagesProjectile Motion EtoosT sidharth100% (1)

- Classical and Operant ConditioningDocument14 pagesClassical and Operant ConditioningrajnaNo ratings yet

- Chapter 5 - Welding Joint Design and Welding SymbolsDocument43 pagesChapter 5 - Welding Joint Design and Welding Symbolsyves suarezNo ratings yet

- F520Document2 pagesF520Marcos AldrovandiNo ratings yet

- IADC Daily Drilling Report RevADocument4 pagesIADC Daily Drilling Report RevAdullahnurkalimNo ratings yet

- Z370 AORUS Gaming 3: User's ManualDocument48 pagesZ370 AORUS Gaming 3: User's ManualAtrocitus RedNo ratings yet

- Basic COMPETENCIES Module of InstructionDocument18 pagesBasic COMPETENCIES Module of InstructionMarveen TingkahanNo ratings yet

- Angell Mobile X-Ray Machine DP326 USER MANUALDocument149 pagesAngell Mobile X-Ray Machine DP326 USER MANUALBiomedical STRH100% (2)

- Man and SupermanDocument4 pagesMan and SupermanSrestha Kar100% (1)

- Edison Robot BarcodesDocument4 pagesEdison Robot BarcodesethanNo ratings yet

- SECOND Periodic Test in AP 4 With TOS SY 2022 2023Document6 pagesSECOND Periodic Test in AP 4 With TOS SY 2022 2023MICHAEL VERINANo ratings yet

- Lumix Dmcgm5kpDocument62 pagesLumix Dmcgm5kpArif SriwidodoNo ratings yet

- ICN AVoiceToLead Guidancepack-9Document60 pagesICN AVoiceToLead Guidancepack-9Muh. AkbarNo ratings yet

- UntitledDocument27 pagesUntitledFlavio MagelaNo ratings yet

- GalvinDocument9 pagesGalvinІгор ШNo ratings yet

- Sol8 PDFDocument11 pagesSol8 PDFMichael ARKNo ratings yet

- TrackersDocument14 pagesTrackersSabahudinBuroNo ratings yet