Professional Documents

Culture Documents

Charge Pump DC-to-DC Converter: Features Package Type

Charge Pump DC-to-DC Converter: Features Package Type

Uploaded by

Alex KarimOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Charge Pump DC-to-DC Converter: Features Package Type

Charge Pump DC-to-DC Converter: Features Package Type

Uploaded by

Alex KarimCopyright:

Available Formats

TC7662A

Charge Pump DC-to-DC Converter

Features Package Type

• Wide Operating Range 8-Pin PDIP

- 3V to 18V 8-Pin CERDIP

• Increased Output Current (40mA)

NC 1 8 VDD

• Pin Compatible with ICL7662/SI7661/TC7660/

LTC1044 C+ 2 7 OSC

• No External Diodes Required TC7662A

GND 3 6 NC

• Low Output Impedance @ IL = 20mA

- 40 Typ. C– 4 5 VOUT

• No Low-Voltage Terminal Required

• CMOS Construction General Description

• Available in 8-Pin PDIP and 8-Pin CERDIP

Packages The TC7662A is a pin-compatible upgrade to the

industry standard TC7660 charge pump voltage

Applications converter. It converts a +3V to +18V input to a

corresponding -3V to -18V output using only two low-

• Laptop Computers cost capacitors, eliminating inductors and their

• Disk Drives associated cost, size and EMI. In addition to a wider

• Process Instrumentation power supply input range (3V to 18V versus 1.5V to

• P-based Controllers 10V for the TC7660), the TC7662A can source output

currents as high as 40mA. The on-board oscillator

Device Selection Table operates at a nominal frequency of 12kHz. Operation

below 12kHz (for lower supply current applications) is

Operating also possible by connecting an external capacitor from

Part OSC to ground.

Package Temp.

Number

Range The TC7662A directly is recommended for designs

TC7662ACPA 8-Pin PDIP 0°C to +70°C requiring greater output current and/or lower input/

output voltage drop. It is available in 8-pin PDIP and

TC7662AEPA 8-Pin PDIP -40°C to +85°C CERDIP packages in commercial and extended

TC7662AIJA 8-Pin CERDIP -25°C to +85°C temperature ranges.

TC7662AMJA 8-Pin CERDIP -55°C to +125°C

2001-2012 Microchip Technology Inc. DS21468B-page 1

TC7662A

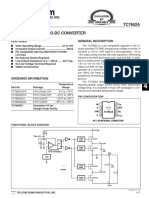

Functional Block Diagram

8 VDD

I

TC7662A

7

OSC

Level P SW1

Shift

Q

2 +

+ F/F CAP

C

– Q

Level N SW4 +

Shift CP

Comparator

with Hysteresis EXT

GND

VREF 3

+

OUT CR

Level N SW2

Shift EXT

4 –

CAP RL

Level N SW3

Shift

5

VOUT

DS21468B-page 2 2001-2012 Microchip Technology Inc.

TC7662A

1.0 ELECTRICAL Stresses above those listed under "Absolute Maximum

Ratings" may cause permanent damage to the device. These

CHARACTERISTICS are stress ratings only and functional operation of the device

at these or any other conditions above those indicated in the

Absolute Maximum Ratings*

operation sections of the specifications is not implied.

Supply Voltage VDD to GND................................. +18V Exposure to Absolute Maximum Rating conditions for

extended periods may affect device reliability.

Input Voltage (Any Pin) .........(VDD + 0.3) to (VSS – 0.3)

Current into Any Pin ............................................ 10mA

Output Short Circuit ........... Continuous (at 5.5V Input)

ESD Protection ................................................ ±2000V

Package Power Dissipation (TA 70°C)

8-Pin CERDIP .......................................... 800mW

8-Pin PDIP ............................................... 730mW

Package Thermal Resistance

CPA, EPA JA ......................................... 140°C/W

IJA, MJA JA ............................................ 90°C/W

Operating Temperature Range

C Suffix............................................ 0°C to +70°C

I Suffix .......................................... -25°C to +85°C

E Suffix......................................... -40°C to +85°C

M Suffix ...................................... -55°C to +125°C

Storage Temperature Range.............. -65°C to +150°C

TC7662A ELECTRICAL SPECIFICATIONS

Electrical Characteristics: VDD = 15V, TA = +25°C, Test circuit (Figure 3-1) unless otherwise noted.

Symbol Parameter Min Typ Max Units Test Conditions

VDD Supply Voltage 3 — 18 V

IS Supply Current — — — A RL =

— 510 700 VDD = +15V

— 560 — 0C TA +70C

— 650 — -55°C TA +125°C

— 190 — VDD = +5V

— 210 — 0C TA +70C

— 210 — -55°C TA +125°C

RO Output Source Resistance — 40 50 IL = 20mA, VDD = +15V

— 50 60 IL = 40mA, VDD = +15V

— 100 125 IL = 3mA, VDD = +5V

FOSC Oscillator Frequency — 12 — kHz

PEFF Power Efficiency 93 97 — % VDD = +15V

— — — RL = 2k

VEFF Voltage Efficiency 99 99.9 — % VDD = +15V

— — — RL =

96 — — Over operating temperature range.

2001-2012 Microchip Technology Inc. DS21468B-page 3

TC7662A

2.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1.

TABLE 2-1: PIN FUNCTION TABLE

Pin No.

(8-Pin PDIP, Symbol Description

CERDIP)

1 NC No connection.

2 C+ Charge pump capacitor positive terminal.

3 GND Ground terminal.

4 C- Charge pump capacitor negative terminal.

5 VOUT Output voltage.

6 NC No connection.

7 OSC Oscillator control input. Bypass with an external capacitor to slow the oscillator.

8 VDD Power supply positive voltage input.

DS21468B-page 4 2001-2012 Microchip Technology Inc.

TC7662A

3.0 DETAILED DESCRIPTION 3.1 Theoretical Power Efficiency

Considerations

The TC7662A is a capacitive charge pump (sometimes

called a switched-capacitor circuit), where four In theory, a voltage converter can approach 100%

MOSFET switches control the charge and discharge of efficiency if certain conditions are met:

a capacitor.

1. The drive circuitry consumes minimal power.

The functional block diagram shows how the switching 2. The output switches have extremely low ON

action works. SW1 and SW2 are turned on simulta- resistance and virtually no offset.

neously, charging CP to the supply voltage, VDD. This

3. The impedances of the pump and reservoir

assumes that the ON resistance of the MOSFETs in

capacitors are negligible at the pump frequency.

series with the capacitor produce a charging time

(3 time constants) less than the ON time provided by The TC7662A approaches these conditions for

the oscillator frequency, as shown: negative voltage conversion if large values of CP and

CR are used.

3 (RDS(ON) CP) <CP/(0.5 fOSC).

Note: Energy is lost only in the transfer of charge

In the next cycle, SW1 and SW2 are turned OFF and, between capacitors if a change in voltage

after a very short interval with all switches OFF occurs.

(preventing large currents from occurring due to cross The energy lost is defined by:

conduction), SW3 and SW4 are turned ON. The charge

in CP is then transferred to CR, but with the polarity E = 1/2 CP (V12 – V22)

inverted. In this way, a negative voltage is derived.

V1 and V2 are the voltages on CP during the pump and

An oscillator supplies pulses to a flip-flop that is fed to transfer cycles. If the impedances of CP and CR are

a set of level shifters. These level shifters then drive relatively high at the pump frequency (refer to Figure 3-

each set of switches at one-half the oscillator 1), compared to the value of RL, there will be a

frequency. substantial difference in voltages V1 and V2. Therefore,

The oscillator has a pin that controls the frequency it is desirable not only to make CR as large as possible

of oscillation. Pin 7 can have a capacitor added that to eliminate output voltage ripple, but also to employ a

is connected to ground. This will lower the frequency correspondingly large value for CP in order to achieve

of the oscillator by adding capacitance to the maximum efficiency of operation.

internal timing capacitor of the TC7662A. (See Typical

Characteristics – Oscillator Frequency vs. COSC.) 3.2 Dos and Don'ts

• Do not exceed maximum supply voltages.

FIGURE 3-1: TC7662A TEST CIRCUIT • Do not short circuit the output to V+ supply for

IS voltages above 5.5V for extended periods;

1 8 VDD however, transient conditions including start-up

NC

IL (+5V)

2 7 are okay.

+ 10μF TC7662A 6 COSC • When using polarized capacitors in the inverting

CP 3 RL

NC

mode, the + terminal of CP must be connected to

4 5 VOUT

pin 2 of the TC7662A and the + terminal of CR

(-5V)

must be connected to GND (pin 3).

CR 10μF

+ • If the voltage supply driving the TC7662A has a

large source impedance (25-30 ohms), then a

2.2F capacitor from pin 8 to ground may be

required to limit the rate of rise of the input voltage

to less than 2V/sec.

2001-2012 Microchip Technology Inc. DS21468B-page 5

TC7662A

4.0 TYPICAL APPLICATIONS Combining the four RSWX terms as RSW, we see that:

1

4.1 Simple Negative Voltage RO 2 x RSW + + 4 x ESRCP + ESRCR

fPUMP x CP

Converter

RSW, the total switch resistance, is a function of supply

The majority of applications will undoubtedly utilize the

voltage and temperature (See Section 5.0, Typical

TC7662A for generation of negative supply voltages.

Characteristics “Output Source Resistance” graphs),

Figure 4-1 shows typical connections to provide a

typically 23 at +25°C and 5V. Careful selection of CP

negative supply where a positive supply of +3V to +18V

and CR will reduce the remaining terms, minimizing the

is available.

output impedance. High value capacitors will

reduce the 1/(fPUMP x CP) component, and low ESR

FIGURE 4-1: SIMPLE NEGATIVE capacitors will lower the ESR term. Increasing the

CONVERTER AND ITS oscillator frequency will reduce the 1/(fPUMP x CP) term,

OUTPUT EQUIVALENT but may have the side effect of a net increase in output

VDD impedance when CP > 10F and there is not enough

time to fully charge the capacitors every cycle. In a typ-

1 8 ical application when fOSC = 12kHz and C = CP = CR =

+

2 7 10F:

10μF TC7662A

3 6 1

RO RO 2 x 23 + + 4 x ESRCP + ESRCR

4 5 VOUT (5 x 123 x 10 x 10-6)

VOUT = -V+ –

10μF

–

V

VDD

V DD

DD RO (46 + 20 + 5 x ESRC)

+

+

Since the ESRs of the capacitors are reflected in the

A B output impedance multiplied by a factor of 5, a high

value could potentially swamp out a low 1/(fPUMP x CP)

The output characteristics of the circuit in Figure 4-1 term, rendering an increase in switching frequency

are those of a nearly ideal voltage source in series with or filter capacitance ineffective. Typical electrolytic

a resistance as shown in Figure 4-1b. The voltage capacitors may have ESRs as high as 10.

source has a value of -(VDD). The output impedance

(RO) is a function of the ON resistance of the internal

MOS switches (shown in the Functional Block

Diagram), the switching frequency, the value of CP and

CR, and the ESR (equivalent series resistance) of CP

and CR. A good first order approximation for RO is:

RO 2(RSW1 + RSW2 + ESRCP) + 2(RSW3 + RSW4 +

1

ESRCP) + + ESRCR

fPUMP x CP

f

(fPUMP = OSC, RSWX = MOSFET switch resistance)

2

DS21468B-page 6 2001-2012 Microchip Technology Inc.

TC7662A

4.2 Output Ripple 4.3 Paralleling Devices

ESR also affects the ripple voltage seen at the output. Any number of TC7662A voltage converters may be

The total ripple is determined by 2 voltages, A and B, paralleled to reduce output resistance (Figure 4-3).

as shown in Figure 4-2. Segment A is the voltage drop The reservoir capacitor, CR, serves all devices, while

across the ESR of CR at the instant it goes from being each device requires its own pump capacitor, CP. The

charged by CP (current flowing into CR) to being dis- resultant output resistance would be approximately:

charged through the load (current flowing out of CR).

The magnitude of this current change is 2 x IOUT, hence ROUT (of TC7662A)

ROUT =

the total drop is 2 x IOUT x ESRCR volts. Segment B is n (number of devices)

the voltage change across CR during time t2, the half of

the cycle when CR supplies current to the load. The 4.4 Cascading Devices

drop at B is IOUT x t2/CR volts. The peak-to-peak ripple

voltage is the sum of these voltage drops: The TC7662A may be cascaded as shown (Figure 4-4)

to produce larger negative multiplication of the initial

1

(

VRIPPLE 2 x f

PUMP x CR

+ 2 x ESRCR x IOUT ) supply voltage. However, due to the finite efficiency of

each device, the practical limit is 10 devices for light

loads. The output voltage is defined by:

FIGURE 4-2: OUTPUT RIPPLE

VOUT = – n (VIN)

t2 t1

where n is an integer representing the number of

devices cascaded. The resulting output resistance

would be approximately the weighted sum of the

0 B individual TC7662A ROUT values.

A

-(VDD)

FIGURE 4-3: PARALLELING DEVICES LOWERS OUTPUT IMPEDANCE

VDD

1 8

2 7 1 8

TC7662A

C1 3 6 RL

2 7

TC7662A

4 "1" 5 C1 3 6

4 "n" 5

C2

+

FIGURE 4-4: INCREASED OUTPUT VOLTAGE BY CASCADING DEVICES

VDD

1 8

2 7 1 8

+ TC7662A

10μF 3 6 2 7

+

TC7662A

4 "1" 5 10μF 3 6

4 "n" 5 VOUT*

10μF

+

10μF

*VOUT = -nVDD

2001-2012 Microchip Technology Inc. DS21468B-page 7

TC7662A

4.5 Changing the TC7662A Oscillator 4.7 Combined Negative Voltage

Frequency Conversion and Positive Supply

Multiplication

It is possible to increase the conversion efficiency of

the TC7662A at low load levels by lowering the Figure 4-7 combines the functions shown in Figure 4-1

oscillator frequency. This reduces the switching losses, and Figure 4-6 to provide negative voltage conversion

and is shown in Figure 4-5. However, lowering the and positive voltage doubling simultaneously. This

oscillator frequency will cause an undesirable increase approach would be, for example, suitable for generat-

in the impedance of the pump (CP) and reservoir (CR) ing +9V and -5V from an existing +5V supply. In this

capacitors; this is overcome by increasing the values of instance, capacitors C1 and C3 perform the pump and

CP and CR by the same factor that the frequency has reservoir functions, respectively, for the generation of

been reduced. For example, the addition of a 100pF the negative voltage, while capacitors C2 and C4 are

pump and reservoir, respectively, for the doubled

capacitor between pin 7 (OSC) and VDD will lower the

positive voltage. There is a penalty in this configuration

oscillator frequency to 2kHz from its nominal frequency

which combines both functions, however, in that the

of 12kHz (multiple of 6), and thereby necessitate a

source impedances of the generated supplies will be

corresponding increase in the value of CP and CR (from

somewhat higher due to the finite impedance of the

10F to 68F).

common charge pump driver at pin 2 of the device.

FIGURE 4-5: LOWERING OSCILLATOR FIGURE 4-7: COMBINED NEGATIVE

FREQUENCY CONVERTER AND

VDD POSITIVE DOUBLER

VDD

VOUT =

1 8

-(VDD – VF)

2 7 1 8

+ TC7662A 6 COSC 2 7 C3

10μF 3 +

TC7662A D1

3 6

4 5 VOUT

VOUT =

4 5

10μF + (2 VDD) – (2 VF)

C1 D2

+

+

C2 +

C4

4.6 Positive Voltage Doubling

The TC7662A may be employed to achieve positive

voltage doubling using the circuit shown in Figure 4-6. 4.8 Voltage Splitting

In this application, the pump inverter switches of the The same bidirectional characteristics can be used to

TC7662A are used to charge CP to a voltage level of split a higher supply in half, as shown in Figure 4-8.

VDD – VF (where VDD is the supply voltage and VF is The combined load will be evenly shared between the

the forward voltage on CP plus the supply voltage (VDD) two sides. Because the switches share the load in

applied through diode D2 to capacitor CR). The voltage parallel, the output impedance is much lower than in

thus created on CR becomes (2 VDD) – (2 VF), or twice the standard circuits, and higher currents can be drawn

the supply voltage minus the combined forward voltage from the device. By using this circuit, and then the

drops of diodes D1 and D2. circuit of Figure 4-4, +15V can be converted (via +7.5V

The source impedance of the output (VOUT) will depend and -7.5V) to a nominal -15V, though with rather high

on the output current, but for VDD = 5V and an output series resistance (~250).

current of 10 mA, it will be approximately 60.

FIGURE 4-8: SPLITTING A SUPPLY IN

HALF

FIGURE 4-6: POSITIVE VOLTAGE

MULTIPLIER VDD

+

VDD RL1 50μF

– 1 8

1 8 2 7

VOUT =

+ TC7662A

VDD – V – 50 3 6

2 7 D1 VOUT = 2 μF –

TC7662A D2 (2 VDD) – (2 VF) RL2

4 5

3 6

4 5 + +

+

CP CR 50μF

–

V–

DS21468B-page 8 2001-2012 Microchip Technology Inc.

TC7662A

5.0 TYPICAL CHARACTERISTICS

Note: The graphs and tables provided following this note are a statistical summary based on a limited number of

samples and are provided for informational purposes only. The performance characteristics listed herein are

not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified

operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

Circuit of Figure 3-1, CP = CR = 10F, CESRCP CESRCR 1, TA = 25°C unless otherwise noted.

Supply Current vs. Temperature Oscillator Frequency vs. COSC

700

TA = +25°C

600 10k

SUPPLY CURRENT (μA)

FREQUENCY (Hz)

500

400 VDD = 15V 1k

300

200 100

VDD = 5V

100

0 10

-60 -40 -20 0 20 40 60 80 100 120 140 1 10 100 1000 10,000

TEMPERATURE (°C) CAPACITANCE (pF)

Frequency vs. Temperature Output Resistance vs. Temperature

20 160

18 140

OUTPUT RESISTANCE ( Ω)

FREQUENCY (kHz)

16 120

VDD = 5V, IL = 3mA

14 100

12 80

10 60

VDD = 15V, IL = 20mA

8 40

6 20

-60 -40 -20 0 20 40 60 80 100 120 140 -60 -40 -20 0 20 40 60 80 100 120 140

TEMPERATURE (°C) TEMPERATURE (°C)

Power Conversion Efficiency vs. ILOAD Output Resistance vs. Input Voltage

110 165 110

POWER CONVERSION EFFICIENCY (%)

100 150 100 TA = +25°C

OUTPUT RESISTANCE (Ω)

90 135 90

SUPPLY CURRENT (mA)

80 Efficiency 120 80

70 105 70

60 90 60

50 75 50 IL = 20mA

Supply

40 Current 60 40

30 45 30

20 30

20

10 TA = +25°C 15

10

0

0 8 16 24 32 40 48 56 64 72 80

0 2 4 6 8 10 12 14 16 18 20

LOAD CURRENT (mA)

INPUT VOLTAGE (V)

2001-2012 Microchip Technology Inc. DS21468B-page 9

TC7662A

6.0 PACKAGING INFORMATION

6.1 Package Marking Information

Package marking data not available at this time.

6.2 Package Dimensions

Note: For the most current package drawings, please see the Microchip Packaging Specification located

at http://www.microchip.com/packaging

8-Pin Plastic DIP

PIN 1

.260 (6.60)

.240 (6.10)

.045 (1.14) .070 (1.78)

.030 (0.76) .040 (1.02) .310 (7.87)

.400 (10.16) .290 (7.37)

.348 (8.84)

.200 (5.08)

.140 (3.56) .040 (1.02)

.020 (0.51) .015 (0.38) 3° MIN.

.150 (3.81) .008 (0.20)

.115 (2.92)

.400 (10.16)

.310 (7.87)

.110 (2.79) .022 (0.56)

.090 (2.29) .015 (0.38)

Dimensions: inches (mm)

DS21468B-page 10 2001-2012 Microchip Technology Inc.

TC7662A

Note: For the most current package drawings, please see the Microchip Packaging Specification located

at http://www.microchip.com/packaging

8-Pin CDIP (Narrow)

.110 (2.79)

.090 (2.29)

PIN 1

.300 (7.62)

.230 (5.84)

.055 (1.40) MAX. .020 (0.51) MIN.

.400 (10.16) .320 (8.13)

.370 (9.40) .290 (7.37)

.040 (1.02)

.200 (5.08) .020 (0.51)

.160 (4.06)

.015 (0.38) 3° MIN.

.200 (5.08) .150 (3.81)

MIN. .008 (0.20)

.125 (3.18)

.400 (10.16)

.320 (8.13)

.065 (1.65) .020 (0.51)

.045 (1.14) .016 (0.41)

Dimensions: inches (mm)

2001-2012 Microchip Technology Inc. DS21468B-page 11

TC7662A

7.0 REVISION HISTORY

Revision B (December 2012)

Added a note to each package outline drawing.

DS21468B-page 12 2001-2012 Microchip Technology Inc.

TC7662A

Sales and Support

Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recom-

mended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

1. Your local Microchip sales office

2. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

2001-2012 Microchip Technology Inc. DS21468B-page13

TC7662A

NOTES:

DS21468B-page14 2001-2012 Microchip Technology Inc.

Note the following details of the code protection feature on Microchip devices:

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device Trademarks

applications and the like is provided only for your convenience The Microchip name and logo, the Microchip logo, dsPIC,

and may be superseded by updates. It is your responsibility to

FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro,

ensure that your application meets with your specifications.

PICSTART, PIC32 logo, rfPIC, SST, SST Logo, SuperFlash

MICROCHIP MAKES NO REPRESENTATIONS OR and UNI/O are registered trademarks of Microchip Technology

WARRANTIES OF ANY KIND WHETHER EXPRESS OR

Incorporated in the U.S.A. and other countries.

IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION, FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor,

INCLUDING BUT NOT LIMITED TO ITS CONDITION, MTP, SEEVAL and The Embedded Control Solutions

QUALITY, PERFORMANCE, MERCHANTABILITY OR Company are registered trademarks of Microchip Technology

FITNESS FOR PURPOSE. Microchip disclaims all liability Incorporated in the U.S.A.

arising from this information and its use. Use of Microchip Silicon Storage Technology is a registered trademark of

devices in life support and/or safety applications is entirely at Microchip Technology Inc. in other countries.

the buyer’s risk, and the buyer agrees to defend, indemnify and

Analog-for-the-Digital Age, Application Maestro, BodyCom,

hold harmless Microchip from any and all damages, claims,

chipKIT, chipKIT logo, CodeGuard, dsPICDEM,

suits, or expenses resulting from such use. No licenses are

dsPICDEM.net, dsPICworks, dsSPEAK, ECAN,

conveyed, implicitly or otherwise, under any Microchip

ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial

intellectual property rights.

Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB

Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code

Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit,

PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O,

Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA

and Z-Scale are trademarks of Microchip Technology

Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip

Technology Germany II GmbH & Co. & KG, a subsidiary of

Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their

respective companies.

© 2001-2012, Microchip Technology Incorporated, Printed in

the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620768426

QUALITY MANAGEMENT SYSTEM Microchip received ISO/TS-16949:2009 certification for its worldwide

headquarters, design and wafer fabrication facilities in Chandler and

CERTIFIED BY DNV Tempe, Arizona; Gresham, Oregon and design centers in California

and India. The Company’s quality system processes and procedures

== ISO/TS 16949 ==

are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchip’s quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

2001-2012 Microchip Technology Inc. DS21468B-page 15

Worldwide Sales and Service

AMERICAS ASIA/PACIFIC ASIA/PACIFIC EUROPE

Corporate Office Asia Pacific Office India - Bangalore Austria - Wels

2355 West Chandler Blvd. Suites 3707-14, 37th Floor Tel: 91-80-3090-4444 Tel: 43-7242-2244-39

Chandler, AZ 85224-6199 Tower 6, The Gateway Fax: 91-80-3090-4123 Fax: 43-7242-2244-393

Tel: 480-792-7200 Harbour City, Kowloon Denmark - Copenhagen

India - New Delhi

Fax: 480-792-7277 Hong Kong Tel: 45-4450-2828

Tel: 91-11-4160-8631

Technical Support: Tel: 852-2401-1200 Fax: 45-4485-2829

Fax: 91-11-4160-8632

http://www.microchip.com/ Fax: 852-2401-3431

India - Pune France - Paris

support

Australia - Sydney Tel: 91-20-2566-1512 Tel: 33-1-69-53-63-20

Web Address:

Tel: 61-2-9868-6733 Fax: 91-20-2566-1513 Fax: 33-1-69-30-90-79

www.microchip.com

Fax: 61-2-9868-6755 Germany - Munich

Atlanta Japan - Osaka

China - Beijing Tel: 49-89-627-144-0

Duluth, GA Tel: 81-6-6152-7160

Tel: 86-10-8569-7000 Fax: 49-89-627-144-44

Tel: 678-957-9614 Fax: 81-6-6152-9310

Fax: 86-10-8528-2104 Italy - Milan

Fax: 678-957-1455 Japan - Tokyo

China - Chengdu Tel: 39-0331-742611

Boston Tel: 81-3-6880- 3770

Tel: 86-28-8665-5511 Fax: 39-0331-466781

Westborough, MA Fax: 81-3-6880-3771

Fax: 86-28-8665-7889 Netherlands - Drunen

Tel: 774-760-0087 Korea - Daegu

Fax: 774-760-0088 China - Chongqing Tel: 82-53-744-4301 Tel: 31-416-690399

Tel: 86-23-8980-9588 Fax: 82-53-744-4302 Fax: 31-416-690340

Chicago

Itasca, IL Fax: 86-23-8980-9500 Spain - Madrid

Korea - Seoul

Tel: 630-285-0071 China - Hangzhou Tel: 34-91-708-08-90

Tel: 82-2-554-7200

Fax: 630-285-0075 Tel: 86-571-2819-3187 Fax: 82-2-558-5932 or Fax: 34-91-708-08-91

Cleveland Fax: 86-571-2819-3189 82-2-558-5934 UK - Wokingham

Independence, OH China - Hong Kong SAR Tel: 44-118-921-5869

Malaysia - Kuala Lumpur

Tel: 216-447-0464 Tel: 852-2943-5100 Fax: 44-118-921-5820

Tel: 60-3-6201-9857

Fax: 216-447-0643 Fax: 852-2401-3431 Fax: 60-3-6201-9859

Dallas China - Nanjing Malaysia - Penang

Addison, TX Tel: 86-25-8473-2460 Tel: 60-4-227-8870

Tel: 972-818-7423 Fax: 86-25-8473-2470 Fax: 60-4-227-4068

Fax: 972-818-2924

China - Qingdao Philippines - Manila

Detroit Tel: 86-532-8502-7355 Tel: 63-2-634-9065

Farmington Hills, MI

Fax: 86-532-8502-7205 Fax: 63-2-634-9069

Tel: 248-538-2250

Fax: 248-538-2260 China - Shanghai Singapore

Tel: 86-21-5407-5533 Tel: 65-6334-8870

Indianapolis Fax: 86-21-5407-5066 Fax: 65-6334-8850

Noblesville, IN

Tel: 317-773-8323 China - Shenyang Taiwan - Hsin Chu

Fax: 317-773-5453 Tel: 86-24-2334-2829 Tel: 886-3-5778-366

Fax: 86-24-2334-2393 Fax: 886-3-5770-955

Los Angeles

Mission Viejo, CA China - Shenzhen Taiwan - Kaohsiung

Tel: 949-462-9523 Tel: 86-755-8864-2200 Tel: 886-7-213-7828

Fax: 949-462-9608 Fax: 86-755-8203-1760 Fax: 886-7-330-9305

Santa Clara China - Wuhan Taiwan - Taipei

Santa Clara, CA Tel: 86-27-5980-5300 Tel: 886-2-2508-8600

Tel: 408-961-6444 Fax: 86-27-5980-5118 Fax: 886-2-2508-0102

Fax: 408-961-6445 China - Xian Thailand - Bangkok

Toronto Tel: 86-29-8833-7252 Tel: 66-2-694-1351

Mississauga, Ontario, Fax: 86-29-8833-7256 Fax: 66-2-694-1350

Canada China - Xiamen

Tel: 905-673-0699 Tel: 86-592-2388138

Fax: 905-673-6509 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040

11/29/12

Fax: 86-756-3210049

DS21468B-page 16 2001-2012 Microchip Technology Inc.

Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Microchip:

TC7662ACPA TC7662AMJA TC7662AIJA TC7662AEPA

You might also like

- Audio Unlimited Wireless Speakers ManualDocument6 pagesAudio Unlimited Wireless Speakers ManualMinh Long ĐỗNo ratings yet

- BPW Flyer L Achsen 15691301eDocument2 pagesBPW Flyer L Achsen 15691301eAlex KarimNo ratings yet

- In Circuit Testing ConceptDocument39 pagesIn Circuit Testing Conceptsawtoh100% (2)

- TC7662A Charge Pump Dc-To-Dc Converter: General Description FeaturesDocument8 pagesTC7662A Charge Pump Dc-To-Dc Converter: General Description FeaturesAlex KarimNo ratings yet

- TC7662A Charge Pump Dc-To-Dc Converter: General Description FeaturesDocument5 pagesTC7662A Charge Pump Dc-To-Dc Converter: General Description FeaturesHAITHAMNo ratings yet

- Charge Pump Dc-To-Dc Voltage ConverterDocument11 pagesCharge Pump Dc-To-Dc Voltage ConverterRicardo KraftmanNo ratings yet

- High Current Charge Pump DC-to-DC Converter: Features: General DescriptionDocument12 pagesHigh Current Charge Pump DC-to-DC Converter: Features: General DescriptionBaglaNo ratings yet

- TC4420M/TC4429M: 6A High-Speed MOSFET DriversDocument18 pagesTC4420M/TC4429M: 6A High-Speed MOSFET Driversdaniela espinosaNo ratings yet

- Charge Pump DC-to-DC Voltage Converter: Features Package TypesDocument20 pagesCharge Pump DC-to-DC Voltage Converter: Features Package TypesTomás CuetoNo ratings yet

- MT7830A MaxicTechnologyDocument8 pagesMT7830A MaxicTechnologyKamran AzamNo ratings yet

- Noninverting Circuit For High-To-Low Voltage Level Translation Very ImportantDocument7 pagesNoninverting Circuit For High-To-Low Voltage Level Translation Very Importantsung quekNo ratings yet

- Datasheet - HK tc429 1085381Document7 pagesDatasheet - HK tc429 1085381Vladimir KrivenokNo ratings yet

- TC426/TC427/TC428: 1.5A Dual High-Speed Power MOSFET DriversDocument18 pagesTC426/TC427/TC428: 1.5A Dual High-Speed Power MOSFET DriversShashikant PatilNo ratings yet

- MT7814BD MaxicTechnologyDocument7 pagesMT7814BD MaxicTechnologyAdriano HenriqueNo ratings yet

- 3-Phase Brushless Fan Motor DriverDocument30 pages3-Phase Brushless Fan Motor DriverAravind Prasad Sounder RajNo ratings yet

- Features Description: Micropower Inverting DC/DC ConverterDocument6 pagesFeatures Description: Micropower Inverting DC/DC ConverterJosé FariaNo ratings yet

- TC 4420Document8 pagesTC 4420МИШАNo ratings yet

- Control IC For Single-Ended and Push-Pull Switched-Mode Power Supplies (SMPS) TDA 4700 TDA 4718Document21 pagesControl IC For Single-Ended and Push-Pull Switched-Mode Power Supplies (SMPS) TDA 4700 TDA 4718Wellison RodriguesNo ratings yet

- LM2903 LM393 LM393A LM293A - FairchildDocument9 pagesLM2903 LM393 LM393A LM293A - FairchildElectronicos CaldasNo ratings yet

- TC4421 TC4422 9A High-Speed Mosfet Drivers: Features General DescriptionDocument9 pagesTC4421 TC4422 9A High-Speed Mosfet Drivers: Features General DescriptionAli JanjuaNo ratings yet

- 3-Phase Brushless Fan Motor DriverDocument30 pages3-Phase Brushless Fan Motor DriverAravind Prasad Sounder RajNo ratings yet

- 3-Phase Brushless Fan Motor DriverDocument30 pages3-Phase Brushless Fan Motor DriverAravind Prasad Sounder RajNo ratings yet

- Ucc28c40, Ucc28c41, Ucc28c42, Ucc28c43, Ucc28c44, Ucc28c45 Ucc38c40, Ucc38c41, Ucc38c42, Ucc38c43, Ucc38c44, Ucc38c45Document32 pagesUcc28c40, Ucc28c41, Ucc28c42, Ucc28c43, Ucc28c44, Ucc28c45 Ucc38c40, Ucc38c41, Ucc38c42, Ucc38c43, Ucc38c44, Ucc38c45curz0% (1)

- MAX1044/ICL7660 Switched-Capacitor Voltage Converters: General Description FeaturesDocument15 pagesMAX1044/ICL7660 Switched-Capacitor Voltage Converters: General Description FeaturesJuan CarlosNo ratings yet

- High-Frequency Waveform Generator: - General Description - FeaturesDocument16 pagesHigh-Frequency Waveform Generator: - General Description - FeaturesahmedNo ratings yet

- Hysteretic Boost-Buck (Ćuk) LED Driver IC: Features General DescriptionDocument16 pagesHysteretic Boost-Buck (Ćuk) LED Driver IC: Features General DescriptionJohnNo ratings yet

- TC4420 TC4429 6A High-Speed Mosfet Drivers: Features General DescriptionDocument2 pagesTC4420 TC4429 6A High-Speed Mosfet Drivers: Features General DescriptionKSNo ratings yet

- 6A High-Speed Power MOSFET Drivers: Features General DescriptionDocument22 pages6A High-Speed Power MOSFET Drivers: Features General DescriptionJossy H AtocheNo ratings yet

- TCM809/TCM810: 3-Pin Microcontroller Reset MonitorsDocument16 pagesTCM809/TCM810: 3-Pin Microcontroller Reset Monitorsscribd_alphaNo ratings yet

- Description Features: LTC485 Low Power RS485 Interface TransceiverDocument14 pagesDescription Features: LTC485 Low Power RS485 Interface Transceivergreemax100% (1)

- RT4 433Document2 pagesRT4 433Junior ShoboyNo ratings yet

- MC14538B Dual Precision Retriggerable/Resettable Monostable MultivibratorDocument13 pagesMC14538B Dual Precision Retriggerable/Resettable Monostable MultivibratorAnonymous JoB5ZxgNo ratings yet

- STPS2045CTCFCGCFPCRDocument8 pagesSTPS2045CTCFCGCFPCROmaraye JoshuaNo ratings yet

- Control IC For Single-Ended and Push-Pull Switched-Mode Power Supplies (SMPS) TDA 4718 ADocument17 pagesControl IC For Single-Ended and Push-Pull Switched-Mode Power Supplies (SMPS) TDA 4718 ASledge HammerNo ratings yet

- Precision 2.5V FGA™ Voltage Reference: X60008B-25 X60008C-25 X60008D-25Document10 pagesPrecision 2.5V FGA™ Voltage Reference: X60008B-25 X60008C-25 X60008D-25Alejandro HerediaNo ratings yet

- 921 MHZ - 960 MHZ Sifet RF Integrated Power Amplifier: Mhvic910Hr2Document11 pages921 MHZ - 960 MHZ Sifet RF Integrated Power Amplifier: Mhvic910Hr2Claudinei FigueiraNo ratings yet

- Probador de Flyback de Isaac HernandezDocument8 pagesProbador de Flyback de Isaac HernandezANTONIO PEREZNo ratings yet

- Driver Mosfet TC428Document16 pagesDriver Mosfet TC428jaimeNo ratings yet

- Description Features: High Efficiency High Precision Buck Constant Current DriverDocument9 pagesDescription Features: High Efficiency High Precision Buck Constant Current DriverThiagoAlmeidaNo ratings yet

- sc4525c 1278277Document23 pagessc4525c 1278277Paulo OliveiraNo ratings yet

- TC4452 PDFDocument23 pagesTC4452 PDFCHARIS ZEVGARASNo ratings yet

- Dual Power MOSFET Driver Features: File Number Data Sheet April 1999Document8 pagesDual Power MOSFET Driver Features: File Number Data Sheet April 1999tommyhghNo ratings yet

- TC4426A/TC4427A/TC4428A: 1.5A Dual High-Speed Power MOSFET DriversDocument26 pagesTC4426A/TC4427A/TC4428A: 1.5A Dual High-Speed Power MOSFET DriversFarhanNo ratings yet

- Datasheet - Transceiver CAN - Sgls398aDocument35 pagesDatasheet - Transceiver CAN - Sgls398aAntonio Carlos ACSJRNo ratings yet

- Sgls 398 ADocument31 pagesSgls 398 Aa.escalant.tNo ratings yet

- 10-Bit Digital-to-Analog Converter With Two-Wire Interface: Features General DescriptionDocument24 pages10-Bit Digital-to-Analog Converter With Two-Wire Interface: Features General DescriptionSergio MuriloNo ratings yet

- Instruction Manual Codes 273S.A/3-/4 - /5: Technical CharacteristicsDocument4 pagesInstruction Manual Codes 273S.A/3-/4 - /5: Technical Characteristicsamskroud brahimNo ratings yet

- TC1265 Fixed-Output CMOS LDO With ShutdownDocument16 pagesTC1265 Fixed-Output CMOS LDO With ShutdownJose PerezNo ratings yet

- Tda 2320Document5 pagesTda 2320api-3747180No ratings yet

- Features Applications: TL7660 Cmos Voltage ConverterDocument23 pagesFeatures Applications: TL7660 Cmos Voltage ConverterGalih RaharnataNo ratings yet

- 741 IcDocument24 pages741 IcHaneef AhmadNo ratings yet

- S1F76610 Series CMOS DC/DC Converter (Voltage Doubler / Tripler) & Voltage RegulatorDocument14 pagesS1F76610 Series CMOS DC/DC Converter (Voltage Doubler / Tripler) & Voltage RegulatorAndyNo ratings yet

- V02 0409en - DS - HCPL 7860 - 2015 03 061 908727Document18 pagesV02 0409en - DS - HCPL 7860 - 2015 03 061 908727Shirley CastañedaNo ratings yet

- Cargador Enercell cr623xDocument11 pagesCargador Enercell cr623xcuco777No ratings yet

- TC4451/TC4452: 12A High-Speed MOSFET DriversDocument24 pagesTC4451/TC4452: 12A High-Speed MOSFET DriversVolodiyaNo ratings yet

- TC4538BP Datasheet en 20140301Document9 pagesTC4538BP Datasheet en 20140301Strati YovchevNo ratings yet

- Ultra Low Output Voltage Linear N-FET Controller: Global Mixed-Mode Technology IncDocument1 pageUltra Low Output Voltage Linear N-FET Controller: Global Mixed-Mode Technology IncDaniel Norberto DemariaNo ratings yet

- Max712 Max713Document17 pagesMax712 Max713123No ratings yet

- 74ABT377A: Octal D-Type Flip-Flop With EnableDocument12 pages74ABT377A: Octal D-Type Flip-Flop With EnableStuxnetNo ratings yet

- Kuman 3.5 Inch Touch Screen DatasheetDocument15 pagesKuman 3.5 Inch Touch Screen DatasheetMarcGarciaNo ratings yet

- AL8862QDocument17 pagesAL8862QIvo MatosNo ratings yet

- Spec-C7H 6X6 CARGO CHASSIS-TAZ5466TYTDocument1 pageSpec-C7H 6X6 CARGO CHASSIS-TAZ5466TYTAlex KarimNo ratings yet

- TC7662A Charge Pump Dc-To-Dc Converter: General Description FeaturesDocument8 pagesTC7662A Charge Pump Dc-To-Dc Converter: General Description FeaturesAlex KarimNo ratings yet

- DLZ 19 Data SheetDocument1 pageDLZ 19 Data SheetAlex KarimNo ratings yet

- Improved, 16-Channel/Dual 8-Channel, CMOS Analog MultiplexersDocument13 pagesImproved, 16-Channel/Dual 8-Channel, CMOS Analog MultiplexersAlex KarimNo ratings yet

- Scrap HandlerDocument2 pagesScrap HandlerAlex KarimNo ratings yet

- T R I 6 0 - 3 0 Turbojet Engine: Main FeaturesDocument1 pageT R I 6 0 - 3 0 Turbojet Engine: Main FeaturesAlex KarimNo ratings yet

- Fdn358P: Single P-Channel, Logic Level, Powertrench MosfetDocument5 pagesFdn358P: Single P-Channel, Logic Level, Powertrench MosfetAlex KarimNo ratings yet

- Requires Acrobat 62Document3 pagesRequires Acrobat 62Alex KarimNo ratings yet

- Exploring Optical and Magnetic Sensors: Figure 1b Shows A ReflecDocument3 pagesExploring Optical and Magnetic Sensors: Figure 1b Shows A ReflecAlex KarimNo ratings yet

- Frequency Response of A Thin Cobalt Film Magnetooptic SensorDocument5 pagesFrequency Response of A Thin Cobalt Film Magnetooptic SensorAlex KarimNo ratings yet

- Application Note 226: Step-Up DC-DC Converter Calibration and Adjustment Using A Digital PotentiometerDocument8 pagesApplication Note 226: Step-Up DC-DC Converter Calibration and Adjustment Using A Digital PotentiometerAlex KarimNo ratings yet

- Parker Comoso 7373T SeriesDocument1 pageParker Comoso 7373T SeriesAlex KarimNo ratings yet

- CAT3200DB1 Demonstration Board For The CAT3200 DC - DC ConverterDocument4 pagesCAT3200DB1 Demonstration Board For The CAT3200 DC - DC ConverterAlex KarimNo ratings yet

- 8common - Noise DC-DC ConverterDocument4 pages8common - Noise DC-DC ConverterAlex KarimNo ratings yet

- How To Generate Auxiliary Supplies From A Positive Buck DC-DC ConverterDocument15 pagesHow To Generate Auxiliary Supplies From A Positive Buck DC-DC ConverterAlex KarimNo ratings yet

- Vickers: Proportional Pressure Control Valve With Integrated ElectronicsDocument8 pagesVickers: Proportional Pressure Control Valve With Integrated ElectronicsAlex KarimNo ratings yet

- OPTIMUS Eng'g Workshop: AgendaDocument13 pagesOPTIMUS Eng'g Workshop: AgendaHatem MOKHTARINo ratings yet

- What Is An Operating SystemDocument11 pagesWhat Is An Operating SystemObby-GiftMwambaKachecheNo ratings yet

- OptiX WDM Product System Commissioning-V1.0Document41 pagesOptiX WDM Product System Commissioning-V1.0Elfatih HashimNo ratings yet

- UC2502Document5 pagesUC2502Angelo ZuñigaNo ratings yet

- MICROSENS WhitePaper Smart Office en WebDocument8 pagesMICROSENS WhitePaper Smart Office en Webvictor mauricio colonia rangelNo ratings yet

- Cisco Tech Update 6-Asr1k-RoadmapDocument29 pagesCisco Tech Update 6-Asr1k-Roadmapnguyenbaviet89No ratings yet

- How To Change Frequency On PWM Pins of Arduino UNODocument1 pageHow To Change Frequency On PWM Pins of Arduino UNOCPtaller MTTONo ratings yet

- Think About Poorman's TRX (Filter Edition)Document13 pagesThink About Poorman's TRX (Filter Edition)Ashok Shankar DasNo ratings yet

- Network Design Template FinalDocument16 pagesNetwork Design Template FinaladdisuNo ratings yet

- Eds 3400Document2 pagesEds 3400Marlon CalixNo ratings yet

- Iris 4015Document6 pagesIris 4015vetchboyNo ratings yet

- Gm7mainunit SheetDocument2 pagesGm7mainunit Sheetmark luigi SarmientoNo ratings yet

- Augmented Spark Gap Igniter For Propellants: Descr Mouser Part NumberDocument3 pagesAugmented Spark Gap Igniter For Propellants: Descr Mouser Part NumberFrançois LeroyNo ratings yet

- Man pr5220 Inst en 949905052201-Rel450Document234 pagesMan pr5220 Inst en 949905052201-Rel450helroxoNo ratings yet

- Wave Mate Z80 Super Bullet Manual Feb84Document25 pagesWave Mate Z80 Super Bullet Manual Feb84juanNo ratings yet

- Price ListDocument98 pagesPrice ListVeaceslav Gheorghe VrabieNo ratings yet

- Lab 11Document6 pagesLab 11Rizwan Ahmad Muhammad AslamNo ratings yet

- Canon I550, I850, I950 Service ManualDocument46 pagesCanon I550, I850, I950 Service ManualSelagea IoanNo ratings yet

- MQAM Product Sheet - 714341Document2 pagesMQAM Product Sheet - 714341Andrei StefanNo ratings yet

- FTC470XETDocument2 pagesFTC470XETDecebal ScorilloNo ratings yet

- Design and Performance Analysis of Three-Phase Solar PVDocument12 pagesDesign and Performance Analysis of Three-Phase Solar PVThejeshwi Reddy0% (1)

- Perating Anual: VX-3200 O MDocument16 pagesPerating Anual: VX-3200 O MLisnik W. F. BerrielNo ratings yet

- CSE 318 ReportDocument23 pagesCSE 318 Reportrubayat mahmudNo ratings yet

- Plagiarism ReportDocument104 pagesPlagiarism ReportMahtab ANo ratings yet

- Magnetic Tape RecorderDocument3 pagesMagnetic Tape RecorderNoman M HasanNo ratings yet

- EE891 Stochastic Systems: Welcome and IntroductionDocument16 pagesEE891 Stochastic Systems: Welcome and IntroductionMohammad SadiqNo ratings yet

- MM 6800 DatasheetDocument2 pagesMM 6800 Datasheetgroovey9040No ratings yet

- Physics Project Sample Copy Std. 12Document21 pagesPhysics Project Sample Copy Std. 12cytrfNo ratings yet