Professional Documents

Culture Documents

Analog Electronic Circuits (ECE - 2101) RCS

Analog Electronic Circuits (ECE - 2101) RCS

Uploaded by

deevCopyright:

Available Formats

You might also like

- Cat 3508-B Electr - DiagramDocument2 pagesCat 3508-B Electr - DiagramCésar Pérez88% (8)

- Transformer Manual PDFDocument31 pagesTransformer Manual PDFpitamberverma56% (16)

- Analog Electronics Circuit (ECE - 2101) (Make Up) RCSDocument2 pagesAnalog Electronics Circuit (ECE - 2101) (Make Up) RCSdeevNo ratings yet

- NPTEL - Assignment - 11 - Travelling WaveDocument6 pagesNPTEL - Assignment - 11 - Travelling WaveAKSH0211No ratings yet

- Analog Electronic Circuits (ECE 201)Document3 pagesAnalog Electronic Circuits (ECE 201)Ankith Jai KrishnaNo ratings yet

- Basic Electronics (ECE 101) PDFDocument2 pagesBasic Electronics (ECE 101) PDFRahul PinnamaneniNo ratings yet

- Power Systems QuestionsDocument45 pagesPower Systems Questionssamg27No ratings yet

- Manipal Institute of Technology: Reg. NoDocument2 pagesManipal Institute of Technology: Reg. Nodreamivory29No ratings yet

- 01 Ee001 3 2 Ae Fe QPDocument5 pages01 Ee001 3 2 Ae Fe QPMohamed AltijaniNo ratings yet

- Answer Any Two Full Questions, Each Carries 15 Marks.: Reg No.: - NameDocument2 pagesAnswer Any Two Full Questions, Each Carries 15 Marks.: Reg No.: - Namesheena mNo ratings yet

- Scenario:: Internal Verification Form D1Document10 pagesScenario:: Internal Verification Form D1tanmoyr2001No ratings yet

- Question Paper: A Answer All The QuestionsDocument3 pagesQuestion Paper: A Answer All The QuestionsHarshita GauravNo ratings yet

- Analog Electronics (0500625) SET 1Document8 pagesAnalog Electronics (0500625) SET 1Avinash PandeyNo ratings yet

- 1534254762537-GDCE 2018 EngDocument200 pages1534254762537-GDCE 2018 EngNaveen KumarNo ratings yet

- Network Analysis (ECE 2103)Document3 pagesNetwork Analysis (ECE 2103)Shoumik DeyNo ratings yet

- Basic Electronics (ECE 1051)Document2 pagesBasic Electronics (ECE 1051)aryansorout1612No ratings yet

- WWW - Manaresults.Co - In: (Common To Ece, Eie, Etm)Document2 pagesWWW - Manaresults.Co - In: (Common To Ece, Eie, Etm)Dr Prateek AsthanaNo ratings yet

- Conventional Paper-II-2011 Part-1ADocument6 pagesConventional Paper-II-2011 Part-1ASoumyabrataPatraNo ratings yet

- PHY308 April 2019Document2 pagesPHY308 April 2019solomonfisaacNo ratings yet

- Network Analysis (ECE - 2103)Document3 pagesNetwork Analysis (ECE - 2103)Preeti SharmaNo ratings yet

- Ece 1071 - Ece-1071 - Basic ElectronicsDocument2 pagesEce 1071 - Ece-1071 - Basic ElectronicsChalla SaiNo ratings yet

- Ee141 HW2 3 PDFDocument5 pagesEe141 HW2 3 PDFVidhya DsNo ratings yet

- Elec1041y 1 2007 2 PDFDocument7 pagesElec1041y 1 2007 2 PDFchetsNo ratings yet

- Power System Mcqs PDFDocument5 pagesPower System Mcqs PDFHarith NawfelNo ratings yet

- Analog Circuits: Time Allotted: 3 Hrs Full Marks: 70Document4 pagesAnalog Circuits: Time Allotted: 3 Hrs Full Marks: 70Vikash KumarNo ratings yet

- Khwaja Yunus Ali University: Department of Electrical and Electronic Engineering Online Final Examination: Spring-2021Document3 pagesKhwaja Yunus Ali University: Department of Electrical and Electronic Engineering Online Final Examination: Spring-2021Abdullah SaikatNo ratings yet

- Test-1 (Mains) - Electrical EnggDocument5 pagesTest-1 (Mains) - Electrical EnggRitsheNo ratings yet

- Electronics Circuit AnalysisDocument8 pagesElectronics Circuit AnalysisrpramkmrNo ratings yet

- KTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedDocument16 pagesKTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedsunNo ratings yet

- Power System Protection DR - Prf.Mohammed Tawfeeq Tutorial Sheet No.3Document8 pagesPower System Protection DR - Prf.Mohammed Tawfeeq Tutorial Sheet No.3Irwan100% (1)

- IES - Electronics Engineering - Analog Electronic CircuitsDocument71 pagesIES - Electronics Engineering - Analog Electronic CircuitsVishwanath MalakarNo ratings yet

- I C Systems (ECE-2202) RCS (Makeup)Document2 pagesI C Systems (ECE-2202) RCS (Makeup)1x1pNo ratings yet

- WWW - Manaresults.Co - In: (Electrical and Electronics Engineering)Document3 pagesWWW - Manaresults.Co - In: (Electrical and Electronics Engineering)Anonymous MYbA037ikNo ratings yet

- Measurements and Instrumentation (ELE 3202)Document4 pagesMeasurements and Instrumentation (ELE 3202)JithinNo ratings yet

- Edc 3Document10 pagesEdc 329viswa12No ratings yet

- EE210A Assignment 4 IIT KanpurDocument2 pagesEE210A Assignment 4 IIT KanpurPriyanka Tiwari100% (1)

- Network Analysis (ECE - 2103) (Make Up) RCSDocument3 pagesNetwork Analysis (ECE - 2103) (Make Up) RCSNaveen KumarNo ratings yet

- B S F E, 2011: Achelor OF Cience Inal XaminationDocument3 pagesB S F E, 2011: Achelor OF Cience Inal XaminationSaikat PayraNo ratings yet

- 9A04402 Electronic Circuit AnalysisDocument4 pages9A04402 Electronic Circuit AnalysissivabharathamurthyNo ratings yet

- R5310204-Power ElectronicsDocument4 pagesR5310204-Power ElectronicssivabharathamurthyNo ratings yet

- EE402 Jan2006Document4 pagesEE402 Jan2006Amazing ElectricalNo ratings yet

- C1EC01-C1405 - ELECTRONIC CIRCUIT ANALYSIS & DESIGN MergedDocument18 pagesC1EC01-C1405 - ELECTRONIC CIRCUIT ANALYSIS & DESIGN Mergedchini_naniNo ratings yet

- IES - Electronics Engineering Paper 2 - 1997Document36 pagesIES - Electronics Engineering Paper 2 - 1997visitmajeedNo ratings yet

- Ae Mock Test Paper1 22 MCQDocument13 pagesAe Mock Test Paper1 22 MCQALLU ARJUNNo ratings yet

- 2019 May EE203-F - Ktu QbankDocument2 pages2019 May EE203-F - Ktu QbankFarooq KhandayNo ratings yet

- Ese 88Document8 pagesEse 88Prasanna KumarNo ratings yet

- CE/EE3311 Electronic Circuits HW3Document2 pagesCE/EE3311 Electronic Circuits HW3Get wNo ratings yet

- HW8 PDFDocument2 pagesHW8 PDFGet wNo ratings yet

- ELECTRICAL CIRCUIT ANALYSIS-II Oct-Nov 2020Document2 pagesELECTRICAL CIRCUIT ANALYSIS-II Oct-Nov 2020Vedula SudhakarNo ratings yet

- R.D. Enggineering College, Duhai, GZB: Deptt. of Electronics & Communication EnggDocument3 pagesR.D. Enggineering College, Duhai, GZB: Deptt. of Electronics & Communication EnggMohan SinghNo ratings yet

- Network Analysis (ECE - 2103) RCSDocument3 pagesNetwork Analysis (ECE - 2103) RCSNaveen KumarNo ratings yet

- IA2 Question PaperDocument18 pagesIA2 Question PaperravirayappaNo ratings yet

- EEE 207 Final Summer 2015Document3 pagesEEE 207 Final Summer 2015rj OpuNo ratings yet

- rr221401 Electronic Devices and CircuitsDocument8 pagesrr221401 Electronic Devices and CircuitsSRINIVASA RAO GANTANo ratings yet

- Analog ElectronicsDocument77 pagesAnalog ElectronicsramyaranganayakiNo ratings yet

- 133 BK 112017Document3 pages133 BK 1120172BL20EC096spoorti NidoniNo ratings yet

- 3054 PDFDocument9 pages3054 PDFpadmajasivaNo ratings yet

- 9A02405 Analog Electronic CircuitsDocument4 pages9A02405 Analog Electronic CircuitssivabharathamurthyNo ratings yet

- 3rd Sem Analog and LA Sem QPDocument5 pages3rd Sem Analog and LA Sem QP22u211No ratings yet

- Power System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)From EverandPower System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)No ratings yet

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsFrom EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsNo ratings yet

- HTTP ModuleDocument1 pageHTTP ModuledeevNo ratings yet

- Failed It How To Turn Mistakes Into Ideas and Other Advice For Successfully Screwing Up (Eric Kessels) (Z-Library)Document172 pagesFailed It How To Turn Mistakes Into Ideas and Other Advice For Successfully Screwing Up (Eric Kessels) (Z-Library)deevNo ratings yet

- TW) A - 15 (I T D: VN Xlgo AS Dop Lase Dauain S)Document3 pagesTW) A - 15 (I T D: VN Xlgo AS Dop Lase Dauain S)deevNo ratings yet

- Analog Electronics Circuit (ECE - 2101) (Make Up) RCSDocument2 pagesAnalog Electronics Circuit (ECE - 2101) (Make Up) RCSdeevNo ratings yet

- ICS Presentation 2021 26 03 2021Document192 pagesICS Presentation 2021 26 03 2021deevNo ratings yet

- Physical Constants: Handbook: Electromagnetic WaveDocument5 pagesPhysical Constants: Handbook: Electromagnetic WavedeevNo ratings yet

- Electronics and Communication Engineering: Course PlanDocument4 pagesElectronics and Communication Engineering: Course PlandeevNo ratings yet

- SKM Power Tools Electrical Engineering SoftwareDocument4 pagesSKM Power Tools Electrical Engineering SoftwareMariam Ayman Saber Mohamed AbdallahNo ratings yet

- CIGRE Green Books: Series Editor Cigre International Council On Large Electric Systems (CIGRE) Paris, FranceDocument45 pagesCIGRE Green Books: Series Editor Cigre International Council On Large Electric Systems (CIGRE) Paris, FranceEsel DimapilisNo ratings yet

- Smartplant+electrical+basic+user+training+guide v35 PDFDocument238 pagesSmartplant+electrical+basic+user+training+guide v35 PDFbhagyaraj123456No ratings yet

- Arkel MenuDocument1 pageArkel MenuNhạc Jazz KhoaNo ratings yet

- Moduflex Power Core (36kW) Rev00Document2 pagesModuflex Power Core (36kW) Rev00Denizhan AkınNo ratings yet

- Surveying and Leveling: Prismaticcompass Study of Instruments Area CalculationDocument19 pagesSurveying and Leveling: Prismaticcompass Study of Instruments Area CalculationManjeet CinghNo ratings yet

- Magnetic Properties of SolidsDocument1 pageMagnetic Properties of SolidsRitu B.ANo ratings yet

- Third Quarterly Test in Science 4Document10 pagesThird Quarterly Test in Science 4Jul Yiet SailNo ratings yet

- BP2328DDocument2 pagesBP2328DMaslikan AdemNo ratings yet

- 2 Acti 9 Mcbs RCCBDocument29 pages2 Acti 9 Mcbs RCCBapi-217894119No ratings yet

- Sensor LaserDocument3 pagesSensor LaserAbraham del Hoyo SotoNo ratings yet

- FVR C9SDocument40 pagesFVR C9SAnonymous GbfoQcCNo ratings yet

- TM - 11 5805 356 34 2Document66 pagesTM - 11 5805 356 34 2julio machadoNo ratings yet

- XS7C4A1MPP20Document6 pagesXS7C4A1MPP20IWONo ratings yet

- Technical SpecificationsDocument8 pagesTechnical SpecificationsvijaykhatavkarNo ratings yet

- Hybrid Solar Inverter PV1800-8-10KDocument1 pageHybrid Solar Inverter PV1800-8-10KAnonymous yugocxnNo ratings yet

- Power PDFDocument3 pagesPower PDFZachez MahabirNo ratings yet

- Helix Traveling-Wave Tubes (TWT'S)Document27 pagesHelix Traveling-Wave Tubes (TWT'S)adumbabu11_740375728No ratings yet

- Electrical Hazard and PreventionDocument24 pagesElectrical Hazard and PreventionDembelo DagimNo ratings yet

- 5S Workplace Organization-1 PDFDocument35 pages5S Workplace Organization-1 PDFIRSHAD PNo ratings yet

- Free Electrons: 7.1 Plasma Re EctivityDocument34 pagesFree Electrons: 7.1 Plasma Re EctivityNawaz KhanNo ratings yet

- SD Series 3 PhaseDocument2 pagesSD Series 3 PhaseVĂN THÀNH TRƯƠNGNo ratings yet

- Full Chapter Engineering Circuit Analysis 12Th Edition J David Irwin PDFDocument53 pagesFull Chapter Engineering Circuit Analysis 12Th Edition J David Irwin PDFjames.lay127100% (6)

- BEEE 2353 - 2354 - Lab 4 Wein-Bridge OscillatorDocument5 pagesBEEE 2353 - 2354 - Lab 4 Wein-Bridge OscillatorAina BalqisNo ratings yet

- T8451 Release NoteDocument17 pagesT8451 Release NoteleunamsayanNo ratings yet

- EXCAR Battery EX51878 Manual (Beta Version)Document11 pagesEXCAR Battery EX51878 Manual (Beta Version)Sayed KhlileNo ratings yet

- BR Phys 2022 2 enDocument4 pagesBR Phys 2022 2 enhiho343hhh100% (1)

Analog Electronic Circuits (ECE - 2101) RCS

Analog Electronic Circuits (ECE - 2101) RCS

Uploaded by

deevOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Analog Electronic Circuits (ECE - 2101) RCS

Analog Electronic Circuits (ECE - 2101) RCS

Uploaded by

deevCopyright:

Available Formats

Reg. No.

MANIPAL INSTITUTE OF TECHNOLOGY

Manipal University

THIRD SEMESTER B.TECH (E & C) DEGREE END SEMESTER EXAMINATION

NOV/DEC 2016

SUBJECT: ANALOG ELECTRONIC CIRCUITS (ECE - 2101)

TIME: 3 HOURS MAX. MARKS: 50

Instructions to candidates:

Answer ALL questions.

Missing data may be suitably assumed.

1A. Design a single stage amplifier which gives a voltage gain of 5 without any change in the phase of

the signal and an input impedance of 100Ω. Assume β=100, VCC=2.5V, Is=10-16A, VA= and

operating frequency of 700MHz.

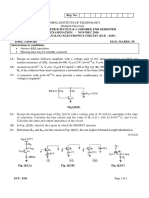

1B. In the circuit of Fig. Q1 (B), β=100 and VA=∞. Calculate the value of IS such that the base-collector

junction is forward biased by 200mV.

1C. A voltage dependent current source is constructed with K=20mA/V. What value of load resistance

in Fig. Q1 (C) is necessary to achieve a voltage gain of 15?

(5+3+2)

Fig. Q1 (B) Fig. Q1 (C)

2A. The circuit of Fig. Q2 (A) must be designed for an input impedance of greater than 10k and a gm

of at least 1/(260). If β=100, IS=2×10−17A, and VA=∞, determine the minimum allowable values

of R1 and R2. If the design is to be repeated for a gm of at least 1/(26), show that no solution exists.

2B. In Fig. Q2 (B), calculate the bias current of M1. Assume μn Cox = 100μA/V2 and VTH = 0.4V. Verify

if the device is operating in saturation. If the gate voltage increases by 10mV, what is the change in

the drain voltage? Determine the value of W/L that places M1 at the edge of saturation. Calculate

the drain voltage change for a 1mV change at the gate.

2C. In the ID–VG plot of Fig. Q2 (C), the arrow indicates (i) Decreasing channel length ‘L’ (ii)

Decreasing oxide thicknesses ‘tox’ (iii) Increasing channel width ‘W’. Identify the correct

statements. Correct the statements which are incorrect.

(5+3+2)

ECE –2101 Page 1 of 3

Fig. Q2 (A) Fig. Q2 (B) Fig. Q2 (C)

3A. For the amplifier circuit shown in Fig. Q3 (A), neglecting channel length modulation, derive the

expression for the voltage gain. Assuming a power budget of 1mW and an overdrive voltage of

200mV for M1, design the circuit for a voltage gain of 4.

3B. Using Miller’s theorem, determine the input capacitance of the circuit shown in Fig. Q3 (B).

Assume λ>0.

3C. Construct the MOSFET circuit using the small signal model shown in Fig. Q3 (C). Is your solution

unique?

(5+3+2)

Fig. Q3 (A) Fig. Q3 (B) Fig. Q3 (C)

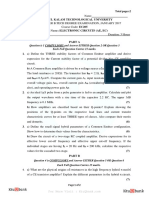

4A. Analyze the circuit shown in Fig. Q4 (A) at low and high frequencies and plot its frequency

response. The circuit is connected to a load capacitance of 10pF. Assume CGS=250fF, CGD=80fF,

CDB=100fF, λ=0, VGS=0.8V, VTH=0.5V and μnCox = 100μA/V2.

4B. Determine the closed loop gain, I/O impedances of the circuit shown in Fig. Q4 (B).

4C. Prove that negative feedback improves the bandwidth of the system.

(5+3+2)

ECE –2101 Page 2 of 3

Fig.Q4 (A) Fig.Q4 (B) Fig.Q5 (A) Fig.Q5 (C)

5A. Determine the oscillating frequency of RC phase shift oscillator shown in Fig. Q5 (A).

5B. Determine the power efficiency of class B push pull amplifier and list its merits and demerits.

5C. For the circuit shown in Fig. Q5 (C), if the input signal has a peak current of 1 mA, determine the

power efficiency. Assume β=50.

(5+3+2)

ECE –2101 Page 3 of 3

You might also like

- Cat 3508-B Electr - DiagramDocument2 pagesCat 3508-B Electr - DiagramCésar Pérez88% (8)

- Transformer Manual PDFDocument31 pagesTransformer Manual PDFpitamberverma56% (16)

- Analog Electronics Circuit (ECE - 2101) (Make Up) RCSDocument2 pagesAnalog Electronics Circuit (ECE - 2101) (Make Up) RCSdeevNo ratings yet

- NPTEL - Assignment - 11 - Travelling WaveDocument6 pagesNPTEL - Assignment - 11 - Travelling WaveAKSH0211No ratings yet

- Analog Electronic Circuits (ECE 201)Document3 pagesAnalog Electronic Circuits (ECE 201)Ankith Jai KrishnaNo ratings yet

- Basic Electronics (ECE 101) PDFDocument2 pagesBasic Electronics (ECE 101) PDFRahul PinnamaneniNo ratings yet

- Power Systems QuestionsDocument45 pagesPower Systems Questionssamg27No ratings yet

- Manipal Institute of Technology: Reg. NoDocument2 pagesManipal Institute of Technology: Reg. Nodreamivory29No ratings yet

- 01 Ee001 3 2 Ae Fe QPDocument5 pages01 Ee001 3 2 Ae Fe QPMohamed AltijaniNo ratings yet

- Answer Any Two Full Questions, Each Carries 15 Marks.: Reg No.: - NameDocument2 pagesAnswer Any Two Full Questions, Each Carries 15 Marks.: Reg No.: - Namesheena mNo ratings yet

- Scenario:: Internal Verification Form D1Document10 pagesScenario:: Internal Verification Form D1tanmoyr2001No ratings yet

- Question Paper: A Answer All The QuestionsDocument3 pagesQuestion Paper: A Answer All The QuestionsHarshita GauravNo ratings yet

- Analog Electronics (0500625) SET 1Document8 pagesAnalog Electronics (0500625) SET 1Avinash PandeyNo ratings yet

- 1534254762537-GDCE 2018 EngDocument200 pages1534254762537-GDCE 2018 EngNaveen KumarNo ratings yet

- Network Analysis (ECE 2103)Document3 pagesNetwork Analysis (ECE 2103)Shoumik DeyNo ratings yet

- Basic Electronics (ECE 1051)Document2 pagesBasic Electronics (ECE 1051)aryansorout1612No ratings yet

- WWW - Manaresults.Co - In: (Common To Ece, Eie, Etm)Document2 pagesWWW - Manaresults.Co - In: (Common To Ece, Eie, Etm)Dr Prateek AsthanaNo ratings yet

- Conventional Paper-II-2011 Part-1ADocument6 pagesConventional Paper-II-2011 Part-1ASoumyabrataPatraNo ratings yet

- PHY308 April 2019Document2 pagesPHY308 April 2019solomonfisaacNo ratings yet

- Network Analysis (ECE - 2103)Document3 pagesNetwork Analysis (ECE - 2103)Preeti SharmaNo ratings yet

- Ece 1071 - Ece-1071 - Basic ElectronicsDocument2 pagesEce 1071 - Ece-1071 - Basic ElectronicsChalla SaiNo ratings yet

- Ee141 HW2 3 PDFDocument5 pagesEe141 HW2 3 PDFVidhya DsNo ratings yet

- Elec1041y 1 2007 2 PDFDocument7 pagesElec1041y 1 2007 2 PDFchetsNo ratings yet

- Power System Mcqs PDFDocument5 pagesPower System Mcqs PDFHarith NawfelNo ratings yet

- Analog Circuits: Time Allotted: 3 Hrs Full Marks: 70Document4 pagesAnalog Circuits: Time Allotted: 3 Hrs Full Marks: 70Vikash KumarNo ratings yet

- Khwaja Yunus Ali University: Department of Electrical and Electronic Engineering Online Final Examination: Spring-2021Document3 pagesKhwaja Yunus Ali University: Department of Electrical and Electronic Engineering Online Final Examination: Spring-2021Abdullah SaikatNo ratings yet

- Test-1 (Mains) - Electrical EnggDocument5 pagesTest-1 (Mains) - Electrical EnggRitsheNo ratings yet

- Electronics Circuit AnalysisDocument8 pagesElectronics Circuit AnalysisrpramkmrNo ratings yet

- KTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedDocument16 pagesKTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedsunNo ratings yet

- Power System Protection DR - Prf.Mohammed Tawfeeq Tutorial Sheet No.3Document8 pagesPower System Protection DR - Prf.Mohammed Tawfeeq Tutorial Sheet No.3Irwan100% (1)

- IES - Electronics Engineering - Analog Electronic CircuitsDocument71 pagesIES - Electronics Engineering - Analog Electronic CircuitsVishwanath MalakarNo ratings yet

- I C Systems (ECE-2202) RCS (Makeup)Document2 pagesI C Systems (ECE-2202) RCS (Makeup)1x1pNo ratings yet

- WWW - Manaresults.Co - In: (Electrical and Electronics Engineering)Document3 pagesWWW - Manaresults.Co - In: (Electrical and Electronics Engineering)Anonymous MYbA037ikNo ratings yet

- Measurements and Instrumentation (ELE 3202)Document4 pagesMeasurements and Instrumentation (ELE 3202)JithinNo ratings yet

- Edc 3Document10 pagesEdc 329viswa12No ratings yet

- EE210A Assignment 4 IIT KanpurDocument2 pagesEE210A Assignment 4 IIT KanpurPriyanka Tiwari100% (1)

- Network Analysis (ECE - 2103) (Make Up) RCSDocument3 pagesNetwork Analysis (ECE - 2103) (Make Up) RCSNaveen KumarNo ratings yet

- B S F E, 2011: Achelor OF Cience Inal XaminationDocument3 pagesB S F E, 2011: Achelor OF Cience Inal XaminationSaikat PayraNo ratings yet

- 9A04402 Electronic Circuit AnalysisDocument4 pages9A04402 Electronic Circuit AnalysissivabharathamurthyNo ratings yet

- R5310204-Power ElectronicsDocument4 pagesR5310204-Power ElectronicssivabharathamurthyNo ratings yet

- EE402 Jan2006Document4 pagesEE402 Jan2006Amazing ElectricalNo ratings yet

- C1EC01-C1405 - ELECTRONIC CIRCUIT ANALYSIS & DESIGN MergedDocument18 pagesC1EC01-C1405 - ELECTRONIC CIRCUIT ANALYSIS & DESIGN Mergedchini_naniNo ratings yet

- IES - Electronics Engineering Paper 2 - 1997Document36 pagesIES - Electronics Engineering Paper 2 - 1997visitmajeedNo ratings yet

- Ae Mock Test Paper1 22 MCQDocument13 pagesAe Mock Test Paper1 22 MCQALLU ARJUNNo ratings yet

- 2019 May EE203-F - Ktu QbankDocument2 pages2019 May EE203-F - Ktu QbankFarooq KhandayNo ratings yet

- Ese 88Document8 pagesEse 88Prasanna KumarNo ratings yet

- CE/EE3311 Electronic Circuits HW3Document2 pagesCE/EE3311 Electronic Circuits HW3Get wNo ratings yet

- HW8 PDFDocument2 pagesHW8 PDFGet wNo ratings yet

- ELECTRICAL CIRCUIT ANALYSIS-II Oct-Nov 2020Document2 pagesELECTRICAL CIRCUIT ANALYSIS-II Oct-Nov 2020Vedula SudhakarNo ratings yet

- R.D. Enggineering College, Duhai, GZB: Deptt. of Electronics & Communication EnggDocument3 pagesR.D. Enggineering College, Duhai, GZB: Deptt. of Electronics & Communication EnggMohan SinghNo ratings yet

- Network Analysis (ECE - 2103) RCSDocument3 pagesNetwork Analysis (ECE - 2103) RCSNaveen KumarNo ratings yet

- IA2 Question PaperDocument18 pagesIA2 Question PaperravirayappaNo ratings yet

- EEE 207 Final Summer 2015Document3 pagesEEE 207 Final Summer 2015rj OpuNo ratings yet

- rr221401 Electronic Devices and CircuitsDocument8 pagesrr221401 Electronic Devices and CircuitsSRINIVASA RAO GANTANo ratings yet

- Analog ElectronicsDocument77 pagesAnalog ElectronicsramyaranganayakiNo ratings yet

- 133 BK 112017Document3 pages133 BK 1120172BL20EC096spoorti NidoniNo ratings yet

- 3054 PDFDocument9 pages3054 PDFpadmajasivaNo ratings yet

- 9A02405 Analog Electronic CircuitsDocument4 pages9A02405 Analog Electronic CircuitssivabharathamurthyNo ratings yet

- 3rd Sem Analog and LA Sem QPDocument5 pages3rd Sem Analog and LA Sem QP22u211No ratings yet

- Power System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)From EverandPower System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)No ratings yet

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsFrom EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsNo ratings yet

- HTTP ModuleDocument1 pageHTTP ModuledeevNo ratings yet

- Failed It How To Turn Mistakes Into Ideas and Other Advice For Successfully Screwing Up (Eric Kessels) (Z-Library)Document172 pagesFailed It How To Turn Mistakes Into Ideas and Other Advice For Successfully Screwing Up (Eric Kessels) (Z-Library)deevNo ratings yet

- TW) A - 15 (I T D: VN Xlgo AS Dop Lase Dauain S)Document3 pagesTW) A - 15 (I T D: VN Xlgo AS Dop Lase Dauain S)deevNo ratings yet

- Analog Electronics Circuit (ECE - 2101) (Make Up) RCSDocument2 pagesAnalog Electronics Circuit (ECE - 2101) (Make Up) RCSdeevNo ratings yet

- ICS Presentation 2021 26 03 2021Document192 pagesICS Presentation 2021 26 03 2021deevNo ratings yet

- Physical Constants: Handbook: Electromagnetic WaveDocument5 pagesPhysical Constants: Handbook: Electromagnetic WavedeevNo ratings yet

- Electronics and Communication Engineering: Course PlanDocument4 pagesElectronics and Communication Engineering: Course PlandeevNo ratings yet

- SKM Power Tools Electrical Engineering SoftwareDocument4 pagesSKM Power Tools Electrical Engineering SoftwareMariam Ayman Saber Mohamed AbdallahNo ratings yet

- CIGRE Green Books: Series Editor Cigre International Council On Large Electric Systems (CIGRE) Paris, FranceDocument45 pagesCIGRE Green Books: Series Editor Cigre International Council On Large Electric Systems (CIGRE) Paris, FranceEsel DimapilisNo ratings yet

- Smartplant+electrical+basic+user+training+guide v35 PDFDocument238 pagesSmartplant+electrical+basic+user+training+guide v35 PDFbhagyaraj123456No ratings yet

- Arkel MenuDocument1 pageArkel MenuNhạc Jazz KhoaNo ratings yet

- Moduflex Power Core (36kW) Rev00Document2 pagesModuflex Power Core (36kW) Rev00Denizhan AkınNo ratings yet

- Surveying and Leveling: Prismaticcompass Study of Instruments Area CalculationDocument19 pagesSurveying and Leveling: Prismaticcompass Study of Instruments Area CalculationManjeet CinghNo ratings yet

- Magnetic Properties of SolidsDocument1 pageMagnetic Properties of SolidsRitu B.ANo ratings yet

- Third Quarterly Test in Science 4Document10 pagesThird Quarterly Test in Science 4Jul Yiet SailNo ratings yet

- BP2328DDocument2 pagesBP2328DMaslikan AdemNo ratings yet

- 2 Acti 9 Mcbs RCCBDocument29 pages2 Acti 9 Mcbs RCCBapi-217894119No ratings yet

- Sensor LaserDocument3 pagesSensor LaserAbraham del Hoyo SotoNo ratings yet

- FVR C9SDocument40 pagesFVR C9SAnonymous GbfoQcCNo ratings yet

- TM - 11 5805 356 34 2Document66 pagesTM - 11 5805 356 34 2julio machadoNo ratings yet

- XS7C4A1MPP20Document6 pagesXS7C4A1MPP20IWONo ratings yet

- Technical SpecificationsDocument8 pagesTechnical SpecificationsvijaykhatavkarNo ratings yet

- Hybrid Solar Inverter PV1800-8-10KDocument1 pageHybrid Solar Inverter PV1800-8-10KAnonymous yugocxnNo ratings yet

- Power PDFDocument3 pagesPower PDFZachez MahabirNo ratings yet

- Helix Traveling-Wave Tubes (TWT'S)Document27 pagesHelix Traveling-Wave Tubes (TWT'S)adumbabu11_740375728No ratings yet

- Electrical Hazard and PreventionDocument24 pagesElectrical Hazard and PreventionDembelo DagimNo ratings yet

- 5S Workplace Organization-1 PDFDocument35 pages5S Workplace Organization-1 PDFIRSHAD PNo ratings yet

- Free Electrons: 7.1 Plasma Re EctivityDocument34 pagesFree Electrons: 7.1 Plasma Re EctivityNawaz KhanNo ratings yet

- SD Series 3 PhaseDocument2 pagesSD Series 3 PhaseVĂN THÀNH TRƯƠNGNo ratings yet

- Full Chapter Engineering Circuit Analysis 12Th Edition J David Irwin PDFDocument53 pagesFull Chapter Engineering Circuit Analysis 12Th Edition J David Irwin PDFjames.lay127100% (6)

- BEEE 2353 - 2354 - Lab 4 Wein-Bridge OscillatorDocument5 pagesBEEE 2353 - 2354 - Lab 4 Wein-Bridge OscillatorAina BalqisNo ratings yet

- T8451 Release NoteDocument17 pagesT8451 Release NoteleunamsayanNo ratings yet

- EXCAR Battery EX51878 Manual (Beta Version)Document11 pagesEXCAR Battery EX51878 Manual (Beta Version)Sayed KhlileNo ratings yet

- BR Phys 2022 2 enDocument4 pagesBR Phys 2022 2 enhiho343hhh100% (1)