Professional Documents

Culture Documents

N-Channel Enhancement-Mode Power MOSFET: SSM07N70CP, R-A

N-Channel Enhancement-Mode Power MOSFET: SSM07N70CP, R-A

Uploaded by

serrano.flia.coOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

N-Channel Enhancement-Mode Power MOSFET: SSM07N70CP, R-A

N-Channel Enhancement-Mode Power MOSFET: SSM07N70CP, R-A

Uploaded by

serrano.flia.coCopyright:

Available Formats

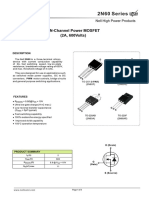

SSM07N70CP,R-A

N-channel Enhancement-mode Power MOSFET

Dynamic dv/dt rating BVDSS 675V

D

Repetitive Avalanche Rated R DS(ON) 1.2Ω

Fast Switching I D 7A

Simple Drive Requirement G

S

DESCRIPTION

The SSM07N70C series is specially designed as a main switching device

for universal 90~265VAC off-line AC/DC converter applications.

Both TO-220 and TO-262 type provide high blocking voltage to overcome G

D TO-220 (P)

voltage surge and sag in the toughest power system with the best S

combination of fast switching,ruggedized design and cost-effectiveness.

The TO-220 and TO-262 packages are widely preferred for all commercial

and industrial applications. The device is well suited for switch-mode

power supplies, AC-DC converters and high-current high-speed switching

circuits. G

D

S TO-262 (R)

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Rating Units

VDS Drain-Source Voltage 675 V

VGS Gate-Source Voltage ± 30 V

ID @ TC=25°C Continuous Drain Current, VGS @ 10V 7 A

ID @ TC=100°C Continuous Drain Current, VGS @ 10V 4.4 A

1

IDM Pulsed Drain Current 18 A

PD @ TC=25°C Total Power Dissipation 89 W

Linear Derating Factor 0.7 W/°C

2

EAS Single Pulse Avalanche Energy 140 mJ

IAR Avalanche Current 7 A

EAR Repetitive Avalanche Energy 7 mJ

TSTG Storage Temperature Range -55 to 150 °C

TJ Operating Junction Temperature Range -55 to 150 °C

THERMAL DATA

Symbol Parameter Value Unit

Rthj-c Thermal Resistance Junction-case Max. 1.4 °C/W

Rthj-a Thermal Resistance Junction-ambient Max. 62 °C/W

3/21/2005 Rev.2.01 www.SiliconStandard.com 1 of 6

SSM07N70CP,R-A

Electrical Characteristics@Tj=25oC(unless otherwise specified)

Symbol Parameter Test Conditions Min. Typ. Max. Units

BVDSS Drain-Source Breakdown Voltage VGS=0V, ID=1mA 675 - - V

∆ BV DSS/∆ Tj Breakdown Voltage Temperature Coefficient Reference to 25°C, ID=1mA - 0.6 - V/°C

RDS(ON) Static Drain-Source On-Resistance VGS=10V, ID=3.5A - - 1.2 Ω

VGS(th) Gate Threshold Voltage VDS=VGS, ID=250uA 2 - 4 V

gfs Forward Transconductance VDS=10V, ID=3.5A - 4.5 - S

o

IDSS Drain-Source Leakage Current (Tj=25 C) VDS=675V, VGS=0V - - 10 uA

o

Drain-Source Leakage Current (Tj=150 C) VDS=480V, VGS=0V - - 100 uA

IGSS Gate-Source Leakage VGS= ± 30V - - ±100 nA

3

Qg Total Gate Charge ID=7A - 32 - nC

Qgs Gate-Source Charge VDS=480V - 8.6 - nC

Qgd Gate-Drain ("Miller") Charge VGS=10V - 9 - nC

3

td(on) Turn-on Delay Time VDD=300V - 17 - ns

tr Rise Time ID=7A - 15 - ns

td(off) Turn-off Delay Time RG=10Ω, VGS=10V - 35 - ns

tf Fall Time RD=43Ω - 18 - ns

Ciss Input Capacitance VGS=0V - 2075 - pF

Coss Output Capacitance VDS=25V - 120 - pF

Crss Reverse Transfer Capacitance f=1.0MHz - 8 - pF

Source-Drain Diode

Symbol Parameter Test Conditions Min. Typ. Max. Units

IS Continuous Source Current ( Body Diode ) VD=VG=0V , VS=1.5V - - 7 A

1

ISM Pulsed Source Current ( Body Diode ) - - 18 A

3

VSD Forward On Voltage Tj=25°C, IS=7A, VGS=0V - - 1.5 V

Notes:

1.Pulse width limited by safe operating area.

2.Starting Tj=25oC , VDD=50V , L=5mH , RG=25Ω , IAS=7A.

3.Pulse width <300us , duty cycle <2%.

3/21/2005 Rev.2.01 www.SiliconStandard.com 2 of 6

SSM07N70CP,R-A

12

T C =25 o C V G =10V T C =150 o C

8

V G =10V

10

V G =6.0V V G =6.0V

V G =5.5V V G =5.5V

ID , Drain Current (A)

ID , Drain Current (A)

8 6

V G =5.0V

6

V G =5.0V 4

2

V G =4.0V

2

V G =4.0V

0 0

0 5 10 15 20 25 0 10 20 30 40

V DS , Drain-to-Source Voltage (V) V DS , Drain-to-Source Voltage (V)

Fig 1. Typical Output Characteristics Fig 2. Typical Output Characteristics

1.2 3

I D =3.5A

2.5 V G =10V

1.1

Normalized BVDSS (V)

2

Normalized R DS(ON)

1 1.5

0.9

0.5

0.8 0

-50 0 50 100 150 -50 0 50 100 150

T j , Junction Temperature ( o C) T j , Junction Temperature ( o C)

Fig 3. Normalized BVDSS vs. Junction Fig 4. Normalized On-Resistance

Temperature vs. Junction Temperature

3/21/2005 Rev.2.01 www.SiliconStandard.com 3 of 6

SSM07N70CP,R-A

8 100

80

6

ID , Drain Current (A)

5

60

PD (W)

4

40

3

20

0

0

25 50 75 100 125 150 0 50 100 150

o o

T c , Case Temperature ( C) Tc , Case Temperature( C)

Fig 5. Maximum Drain Current vs. Fig 6. Typical Power Dissipation

Case Temperature

1

100

DUTY=0.5

Normalized Thermal Response (R thjc)

0.2

10

10us 0.1

ID (A)

0.1

100us 0.05

PDM

1 0.02 SINGLE PULSE t

T

1ms 0.01

o

T c =25 C Duty factor = t/T

Single Pluse 10ms Peak Tj = P DM x Rthjc + TC

100ms

0 0.01

1 10 100 1000 10000 0.00001 0.0001 0.001 0.01 0.1 1 10

V DS (V) t , Pulse Width (s)

Fig 7. Maximum Safe Operating Area Fig 8. Effective Transient Thermal Impedance

3/21/2005 Rev.2.01 www.SiliconStandard.com 4 of 6

SSM07N70CP,R-A

f=1.0MHz

16 10000

14 I D =7A

Ciss

VGS , Gate to Source Voltage (V)

12

V DS =320V

V DS =400V

10

V DS =480V

Coss

C (pF)

8 100

Crss

2

0 1

0 5 10 15 20 25 30 35 40 45 50 1 5 9 13 17 21 25 29

Q G , Total Gate Charge (nC) V DS (V)

Fig 9. Gate Charge Characteristics Fig 10. Typical Capacitance Characteristics

100 5

10

T j = 150 o C T j = 25 o C

3

VGS(th) (V)

IS (A)

0.1

1

0.01 0

0.1 0.3 0.5 0.7 0.9 1.1 1.3 1.5 -50 0 50 100 150

V SD (V) T j , Junction Temperature ( o C)

Fig 11. Forward Characteristic of Fig 12. Gate Threshold Voltage vs.

Reverse Diode Junction Temperature

3/21/2005 Rev.2.01 www.SiliconStandard.com 5 of 6

SSM07N70CP,R-A

VDS

RD 90%

VDS TO THE

D OSCILLOSCOPE

0.5x RATED VDS

RG G

10%

+ S

10 V

VGS

VGS

-

td(on) tr td(off) tf

Fig 13. Switching Time Circuit Fig 14. Switching Time Waveform

VG

VDS

TO THE QG

D OSCILLOSCOPE

10V

0.8 x RATED VDS

G QGS QGD

S VGS

+

1~ 3 mA

-

IG ID

Charge Q

Fig 15. Gate Charge Circuit Fig 16. Gate Charge Waveform

Information furnished by Silicon Standard Corporation is believed to be accurate and reliable. However, Silicon Standard Corporation makes no

guarantee or warranty, express or implied, as to the reliability, accuracy, timeliness or completeness of such information and assumes no

responsibility for its use, or for infringement of any patent or other intellectual property rights of third parties that may result from its

use. Silicon Standard reserves the right to make changes as it deems necessary to any products described herein for any reason, including

without limitation enhancement in reliability, functionality or design. No license is granted, whether expressly or by implication, in relation to

the use of any products described herein or to the use of any information provided herein, under any patent or other intellectual property rights of

Silicon Standard Corporation or any third parties.

3/21/2005 Rev.2.01 www.SiliconStandard.com 6 of 6

You might also like

- Sell Ovens ManualDocument243 pagesSell Ovens Manuallakshmimurugesan100% (1)

- Acer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHDocument67 pagesAcer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHWilgen GarciaNo ratings yet

- GSM g20 Alarm System ManualDocument14 pagesGSM g20 Alarm System Manualmartig87No ratings yet

- 09 N 70 IDocument4 pages09 N 70 IIwan YogyaNo ratings yet

- Ap2761i H HFDocument4 pagesAp2761i H HFReeman432No ratings yet

- Advanced Power Electronics Corp.: N-Channel Enhancement-Mode Power MOSFETDocument6 pagesAdvanced Power Electronics Corp.: N-Channel Enhancement-Mode Power MOSFETruup2010 AlexNo ratings yet

- Datasheet - HK Ap09n90cw-Hf 7299617Document4 pagesDatasheet - HK Ap09n90cw-Hf 7299617TN EDM MusicNo ratings yet

- ap65sl600ahDocument7 pagesap65sl600ahMarco Antonio RomeroNo ratings yet

- Advanced Power Electronics Corp.: AP2761I-ADocument4 pagesAdvanced Power Electronics Corp.: AP2761I-AAbelito JesusNo ratings yet

- PDF04N65LDocument5 pagesPDF04N65LOtaku SlayerNo ratings yet

- Ap9997gh-Hf Power Mosfet NDocument4 pagesAp9997gh-Hf Power Mosfet NVictorManuelBernalBlancoNo ratings yet

- Advanced Power Electronics Corp.: AP2761I-HDocument4 pagesAdvanced Power Electronics Corp.: AP2761I-HAbelito JesusNo ratings yet

- IRF840 AdvancedPowerElectronicsDocument4 pagesIRF840 AdvancedPowerElectronicssheikh sheharyarNo ratings yet

- N-Channel Enhancement-Mode Power MOSFETDocument5 pagesN-Channel Enhancement-Mode Power MOSFETeverestoNo ratings yet

- 9997 GHDocument5 pages9997 GHsahmcoNo ratings yet

- Data SheetDocument6 pagesData SheetAlberto IsmaelNo ratings yet

- Advanced Power Electronics Corp.: AP2761I-ADocument4 pagesAdvanced Power Electronics Corp.: AP2761I-AM_YYYYNo ratings yet

- AP6680BGM HF 3 AdvancedPowerElectronicsDocument5 pagesAP6680BGM HF 3 AdvancedPowerElectronicsqwerty qwertyNo ratings yet

- AP9972GSPDocument6 pagesAP9972GSPSantiago DiosdadoNo ratings yet

- Advanced Power Electronics Corp.: N-Channel Enhancement-Mode Power MOSFETDocument6 pagesAdvanced Power Electronics Corp.: N-Channel Enhancement-Mode Power MOSFETsandstorm16No ratings yet

- Advanced Power Electronics Corp.: AP72T02GH/JDocument6 pagesAdvanced Power Electronics Corp.: AP72T02GH/JFrancisco MataNo ratings yet

- Hoja de Datos de Transistor AP2761Document4 pagesHoja de Datos de Transistor AP2761ingucvNo ratings yet

- Advanced Power Electronics Corp.: AP9997GH/J-HFDocument4 pagesAdvanced Power Electronics Corp.: AP9997GH/J-HFWelly CahyadiNo ratings yet

- PDP8974 Potens SemiconductorDocument5 pagesPDP8974 Potens SemiconductorСергей ТригубNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument5 pagesAdvanced Power Electronics Corp.: DescriptionVladimir DoyminNo ratings yet

- A 2763 IDocument5 pagesA 2763 Ifernando1123No ratings yet

- 100V N-Channel Mosfets: General DescriptionDocument5 pages100V N-Channel Mosfets: General DescriptionMariusNo ratings yet

- PDD6974 5Document5 pagesPDD6974 5Oscar Caetano FontNo ratings yet

- PDD6974 5 PotenssemiconductorDocument5 pagesPDD6974 5 PotenssemiconductorOscar Caetano FontNo ratings yet

- NCE8295A: Enhancement Mode Power MOSFETDocument7 pagesNCE8295A: Enhancement Mode Power MOSFETDarknezzNo ratings yet

- 72T02GH AdvancedPowerElectronicsDocument6 pages72T02GH AdvancedPowerElectronicsjose jesus arteaga gomezNo ratings yet

- 04N70BF H AdvancedPowerElectronicsDocument6 pages04N70BF H AdvancedPowerElectronicsMoises David Torres LamedaNo ratings yet

- 100V N-Channel Mosfets: General DescriptionDocument5 pages100V N-Channel Mosfets: General DescriptionMariusNo ratings yet

- Advanced Power Electronics Corp.: AP0403GHDocument5 pagesAdvanced Power Electronics Corp.: AP0403GHIulius CezarNo ratings yet

- IRLR2908 IRLU2908: Automotive MosfetDocument11 pagesIRLR2908 IRLU2908: Automotive MosfetAnhVũNo ratings yet

- AP9997GKDocument4 pagesAP9997GKcesar meriñoNo ratings yet

- Irlr3705Zpbf Irlu3705Zpbf: FeaturesDocument11 pagesIrlr3705Zpbf Irlu3705Zpbf: FeaturesGanNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument6 pagesAdvanced Power Electronics Corp.: DescriptionMaugrys CastilloNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument6 pagesAdvanced Power Electronics Corp.: DescriptionMaugrys CastilloNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument6 pagesAdvanced Power Electronics Corp.: DescriptionMaugrys CastilloNo ratings yet

- P-Channel Enhancement Mode Power Mosfet: Product SummaryDocument5 pagesP-Channel Enhancement Mode Power Mosfet: Product Summaryserrano.flia.coNo ratings yet

- S2PF380N65R: N-Channel 650V Enhancement Mode Power MOSFETDocument8 pagesS2PF380N65R: N-Channel 650V Enhancement Mode Power MOSFETMaikel Borges IglesiasNo ratings yet

- 4957agm Transitor Mofet PNPDocument5 pages4957agm Transitor Mofet PNPJheremy Sebastian TorresNo ratings yet

- Advanced Power Electronics Corp.: AP85U03GHDocument5 pagesAdvanced Power Electronics Corp.: AP85U03GHEduinMaracuchoFernandezChaparroNo ratings yet

- Features 12N65 650V N-Channel MOSFET: TO-220F PackageDocument7 pagesFeatures 12N65 650V N-Channel MOSFET: TO-220F Packageing.angelocmNo ratings yet

- Advanced Power Electronics Corp.: AP85U03GHDocument5 pagesAdvanced Power Electronics Corp.: AP85U03GHRamon JSNo ratings yet

- AP86T02GHJDocument6 pagesAP86T02GHJEsmelin AlvarezNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument5 pagesAdvanced Power Electronics Corp.: DescriptionSergio Daniel CaminoNo ratings yet

- Enhancement Mode Power MOSFET: NCE N-ChannelDocument7 pagesEnhancement Mode Power MOSFET: NCE N-ChannelErroz RosadiNo ratings yet

- Nce 8295 AkDocument7 pagesNce 8295 Akandre kressnerNo ratings yet

- AP9977GM Data SheetDocument5 pagesAP9977GM Data Sheetpermadi uyeNo ratings yet

- IRF450 Hexfet Transistors Jantx2N6770 Thru-Hole (To-204Aa/Ae) Jantxv2N6770 500V, N-CHANNELDocument7 pagesIRF450 Hexfet Transistors Jantx2N6770 Thru-Hole (To-204Aa/Ae) Jantxv2N6770 500V, N-CHANNELPohan 15No ratings yet

- ap65sl380diDocument8 pagesap65sl380diMarco Antonio RomeroNo ratings yet

- 100V N-Channel Mosfets: General DescriptionDocument5 pages100V N-Channel Mosfets: General DescriptionMariusNo ratings yet

- Irfp4668Pbf: V 200V R Typ. 8.0M: Max. 9.7M: I 130ADocument9 pagesIrfp4668Pbf: V 200V R Typ. 8.0M: Max. 9.7M: I 130ATeodor SerbanNo ratings yet

- Irf5210Spbf Irf5210Lpbf: Hexfet Power Mosfet V = -100V R = 60Mω I = -38ADocument10 pagesIrf5210Spbf Irf5210Lpbf: Hexfet Power Mosfet V = -100V R = 60Mω I = -38AOmar OmranNo ratings yet

- Advanced Power Electronics Corp.: AP18T10AGH/J-HFDocument4 pagesAdvanced Power Electronics Corp.: AP18T10AGH/J-HFAlejadro FierroNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Analog Dialogue Volume 46, Number 1: Analog Dialogue, #5From EverandAnalog Dialogue Volume 46, Number 1: Analog Dialogue, #5Rating: 5 out of 5 stars5/5 (1)

- 2N60 Series: N-Channel Power MOSFET (2A, 600volts)Document8 pages2N60 Series: N-Channel Power MOSFET (2A, 600volts)serrano.flia.coNo ratings yet

- 1PS76SB21 BAT721 Series: 1. Product ProfileDocument12 pages1PS76SB21 BAT721 Series: 1. Product Profileserrano.flia.coNo ratings yet

- HP 15-G Series AMD Compal LA-A996P ZSO51 ULC DIS Beema Kabini REV 4.0 SchematicsDocument47 pagesHP 15-G Series AMD Compal LA-A996P ZSO51 ULC DIS Beema Kabini REV 4.0 Schematicsserrano.flia.coNo ratings yet

- TK11A50D: Switching Regulator ApplicationsDocument6 pagesTK11A50D: Switching Regulator Applicationsserrano.flia.coNo ratings yet

- Charge, BAT PCH: LPC Gpio LPC GpioDocument1 pageCharge, BAT PCH: LPC Gpio LPC Gpioserrano.flia.coNo ratings yet

- Acer Aspire 8530 Wistron Big - Bear2A Rev-1 SchematicDocument54 pagesAcer Aspire 8530 Wistron Big - Bear2A Rev-1 Schematicserrano.flia.coNo ratings yet

- Single-Chip Solutions: QSC6010 /QSC6020 /QSC6030Document4 pagesSingle-Chip Solutions: QSC6010 /QSC6020 /QSC6030serrano.flia.coNo ratings yet

- General Description Product Summery: Bvdss Rdson IDDocument4 pagesGeneral Description Product Summery: Bvdss Rdson IDserrano.flia.coNo ratings yet

- WWW - Vinafix.vn: Appendix B: Schematic DiagramsDocument40 pagesWWW - Vinafix.vn: Appendix B: Schematic Diagramsserrano.flia.coNo ratings yet

- H4092-4 Bow Thruster StarterDocument38 pagesH4092-4 Bow Thruster StarteradinaNo ratings yet

- EasyIO30P FunctionalBlockV3.1.00Document137 pagesEasyIO30P FunctionalBlockV3.1.00HoàngTrầnNo ratings yet

- Thyssenkrupp Twin Elevator Planning GuideDocument5 pagesThyssenkrupp Twin Elevator Planning GuideFERNSNo ratings yet

- MF COMPACT-OPTIMUM EN E03.12Document102 pagesMF COMPACT-OPTIMUM EN E03.12felix camusNo ratings yet

- Consulting Application Guide by EatonDocument3 pagesConsulting Application Guide by EatonnayeemsidduNo ratings yet

- CISCO Important To Understand Gpon TechnologyDocument20 pagesCISCO Important To Understand Gpon TechnologyMoazzam TiwanaNo ratings yet

- Vol20no4 PDFDocument2 pagesVol20no4 PDFRICHARD100% (1)

- MELDAS Series: USA-E99960 - 015ADocument170 pagesMELDAS Series: USA-E99960 - 015AskyNo ratings yet

- SIKA Electronic Thermometers PDFDocument7 pagesSIKA Electronic Thermometers PDFMohamed ElsemanNo ratings yet

- BMI - 122 Important Short QuestionsDocument3 pagesBMI - 122 Important Short Questionsar8806993No ratings yet

- CFL & LED Bulbs: A ComparisonDocument4 pagesCFL & LED Bulbs: A Comparisonjoel_goh_3No ratings yet

- Probable Questions - EptdDocument3 pagesProbable Questions - EptdManas ChakrabortyNo ratings yet

- I V I 1/R I V/R V Ir: Department of Mechanical Engineering Djj20053: Electrical TechnologyDocument5 pagesI V I 1/R I V/R V Ir: Department of Mechanical Engineering Djj20053: Electrical TechnologyMohd ZahiruddinNo ratings yet

- DTC P0101 Mass Air Flow Circuit Range / Performance Problem: DescriptionDocument3 pagesDTC P0101 Mass Air Flow Circuit Range / Performance Problem: Descriptioncarlos gil100% (1)

- HPL Price ListDocument35 pagesHPL Price ListSandeep Deodhar0% (1)

- OM Narada NPFC Series Li Ion 0423 V8Document26 pagesOM Narada NPFC Series Li Ion 0423 V8UnstoppableNo ratings yet

- Considerations of Photovoltaic System Structure Design For Effective Lightning ProtectionDocument9 pagesConsiderations of Photovoltaic System Structure Design For Effective Lightning ProtectionRodrigoNo ratings yet

- Solar TrackerDocument38 pagesSolar TrackerAnonymous ytZsBOVNo ratings yet

- EMCP 3 1 Generator Controller SetDocument4 pagesEMCP 3 1 Generator Controller SetAziz ArrahalNo ratings yet

- VLC Install GuideDocument34 pagesVLC Install GuidevirtechNo ratings yet

- Genesys Logic, Inc.: Revision 1.02 Dec. 28, 2006Document23 pagesGenesys Logic, Inc.: Revision 1.02 Dec. 28, 2006Prasanth KaliNo ratings yet

- Fire Shield ManualDocument68 pagesFire Shield ManualMike SaundersNo ratings yet

- Dok TD MRD1 GeDocument56 pagesDok TD MRD1 GeheriberhuertaNo ratings yet

- Physics ProjectDocument10 pagesPhysics ProjectSukoon Sarin67% (3)

- Ser Manual M20.04: Digital System ControllerDocument22 pagesSer Manual M20.04: Digital System ControllerRiste Di MitrovNo ratings yet

- PMC 1001 (Small)Document1 pagePMC 1001 (Small)mye ryeNo ratings yet

- VM-6370 Vibration Meter Piezoelectric Sensor Displacement Velocity Acc - Gain ExpressDocument1 pageVM-6370 Vibration Meter Piezoelectric Sensor Displacement Velocity Acc - Gain ExpressMiguelNo ratings yet

- Sharp Photodevices Application CirquitsDocument7 pagesSharp Photodevices Application CirquitsbackvlackoNo ratings yet