Professional Documents

Culture Documents

Renesas R2A20113ASP#W5 Datasheet

Renesas R2A20113ASP#W5 Datasheet

Uploaded by

birricaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Renesas R2A20113ASP#W5 Datasheet

Renesas R2A20113ASP#W5 Datasheet

Uploaded by

birricaCopyright:

Available Formats

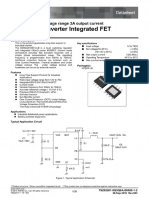

Preliminary Data Sheet

R2A20113ASP R03DS0026EJ0501

Rev.5.01

Critical Conduction Mode PFC Control IC Jan 08, 2016

Description

The R2A20113A controls a boost converter to provide an active power factor correction.

The R2A20113A adopts critical conduction mode for power factor correction and realizes high efficiency and a low

switching noise by zero current switching.

Because the zero current is detected by using the GND current, the ZCD Auxiliary winding is unnecessary.

The feedback loop open detection, two mode overvoltage protection, overcurrent protection are built in the R2A20113A,

and can constitute a power supply system of high reliability with few external parts.

Features

• Absolute Maximum Ratings

⎯ Supply voltage Vcc: 24 V

⎯ Junction temperature Tj: –40 to +150°C

• Electrical characteristics

⎯ UVLO operation start voltage VH: 12 V ± 0.8 V

⎯ UVLO operation shutdown voltage VL: 9.2 V ± 0.7 V

⎯ UVLO hysteresis voltage Hysuvl: 2.8 V ± 0.7 V

• Functions

⎯ Boost converter control with critical conduction mode

⎯ Two mode overvoltage protection

Mode 1: Dynamic OVP corresponding to a voltage rise by load change

Mode 2: Static OVP corresponding to overvoltage in stable.

⎯ Feedback loop open detection

⎯ Overcurrent protection

⎯ Dynamic UVP corresponding to a voltage fall by load change

⎯ Off Time Control function (Frequency Limitter)

⎯ Package lineup: Pb-free SOP-8 (JEDEC)

Ordering Information

Package Taping Abbreviation

Part No. Package Name Package Code Abbreviation (Quantity)

R2A20113ASP#W5 — PRSP0008DJ-A SP W (2,500 pcs/reel)

R03DS0026EJ0501 Rev.5.01 Page 1 of 12

Jan 08, 2016

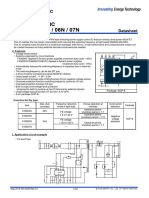

R2A20113ASP Preliminary

Pin Arrangement

FB 1 8 VCC

COMP 2 7 OUT

RT 3 6 GND

VREF 4 5 CS

(Top view)

Pin Function

Pin No. Pin Name Function

1 FB Error amplifier input terminal

2 COMP Error amplifier output terminal

3 RT A resistor connection terminal for RAMP current setting

4 VREF Reference voltage output terminal

5 CS Zero current detection and overcurrent detection input terminal

6 GND Ground

7 OUT Power MOSFET drive terminal

8 VCC Supply voltage terminal

R03DS0026EJ0501 Rev.5.01 Page 2 of 12

Jan 08, 2016

R2A20113ASP Preliminary

Block Diagram

VREF VCC

4 VREF: 5.02V UVLO 8

ON: 12V

VREF

OFF: 9.2V

40μA

+ OUT

– 7

0V

GND

CS 60k 6

5 – LOGIC BLOCK

+

5p

–0.6V

GD Disable (OVP & FB_LOW)

OVP & FB_LOW BLOCK

COMP

Discharge FB

VREF

–

+

RT ErrorAmp

3 FB

– 1

1V +

4.1V 2.51V

10p

COMP

2

Dynamic OVP

+

–

VFB × 1.04V

Ramp Control

Dynamic UVP

+ VFB × 0.92V

–

R03DS0026EJ0501 Rev.5.01 Page 3 of 12

Jan 08, 2016

R2A20113ASP Preliminary

Absolute Maximum Ratings

(Ta = 25°C)

Item Symbol Ratings Unit Note

Power Supply Voltage VCC –0.3 to +24 V

OUT terminal peak current Ipk-snk-out 0.9 A 3

Ipk-src-out –0.50

OUT terminal DC current Idc-snk-out 100 mA

Idc-src-out –50

COMP terminal current Icomp +1 mA

–1

RT terminal current Irt –60 to –2 μA

Vref terminal current Iref –5 mA

Vref terminal voltage Vt-ref –0.3 to Vref + 0.3 V

Vref terminal load capacitor Cref 0.1 to 1 μF

FB terminal voltage Vt-fb –0.3 to +5 V

CS terminal voltage Vcs –5 to +0.3 V

Power dissipation Pt 0.68 W 4

Operating ambient temperature Ta-opr –40 to +125 °C

Junction temperature Tj –40 to +150 °C 5

Storage temperature Tstg –55 to +150 °C

Notes: 1. Rated voltages are with reference to the GND terminal.

2. For rated currents, inflow to the IC is indicated by (+), and outflow by (–).

3. Shows the transient current when driving a capacitive load.

4. In case of R2A20113ASP (SOP): θja = 120°C/W

This value is a thing mounting on 40 × 40 × 1.6 [mm], a glass epoxy board of wiring density 10%.

5. Stresses exceeding the absolute maximum ratings may damage the device.

These are stress ratings only. Functional operation above the recommended operating ambient temperature

range is not implied.

Extended exposure to stresses above the absolute maximum ratings may affect device reliability.

R03DS0026EJ0501 Rev.5.01 Page 4 of 12

Jan 08, 2016

R2A20113ASP Preliminary

Electrical Characteristics

(Ta = 25°C, VCC = 12 V, CS = 0.1 V, FB = COMP, RRT = 200 kΩ)

Item Symbol Min Typ Max Unit Test Conditions

Supply UVLO turn-on threshold Vuvlh 11.2 12 12.8 V

UVLO turn-off threshold Vuvll 8.5 9.2 9.9 V

UVLO hysteresis Hysuvl 2.1 2.8 3.5 V

Standby current Istby — 130 250 μA VCC = Vuvlh – 0.2 V

Operating current Icc — 1.8 2.6 mA

VREF Reference voltage Vref 4.945 5.020 5.095 V Isource = 0 mA

Line regulation Vref-line — 5 20 mV Isource = 0 mA

Vcc = 10 V to 24 V

Load regulation Vref-load — 5 20 mV Isource = 0 mA to –5 mA

Temperature stability dVref — ±80 — ppm/°C Ta = –40 to +125°C *1

OVP-VREF threshold voltage ovp-vref Vref+ Vref+ Vref+ V

0.2 0.4 0.6

Error Feedback voltage Vfb 2.472 2.510 2.548 V FB-COMP short

amplifier Input bias current Ifb –0.40 –0.15 –0.05 μA Measured pin: FB

Open loop gain Av — 65 — dB *1

Upper clamp voltage Vclamp-comp 3.65 4.10 4.3 V FB = 2.0 V

COMP: Open

Low voltage Vl-comp — 0.1 0.3 V FB = 3.0 V

COMP: Open

Source current Isrc-comp –13.5 –10 –6 μA FB = 1 V

COMP = 2.5 V

Sink current Isnk-comp 6 10 13.5 μA FB = 3.5 V

COMP = 2.5 V

Transconductance gm 25 46 75 μs FB = 2.45V ↔ 2.55 V

COMP = 2.5 V

RT RAMP offset voltage Voff_ramp — 1.0 — V *1

RAMP amplitude dVramp 2.90 3.1 3.3 V *2

RT voltage V-rt 1.9 2.0 2.1 V

Zero ZCD threshold voltage Vzcd –4 0 4 mV

current Input bias current Ics –58 –42 –25 μA Vcs = 0 V

detector

Restart Restart time delay Tstart 75 150 330 μs FB = 2.0 V, COMP = 2.5 V

Off time Minimum off time Toff-min 1.0 1.4 1.8 μs

control

Notes: *1 Design spec

*2 dVramp = Vclamp_comp – Voff_ramp

R03DS0026EJ0501 Rev.5.01 Page 5 of 12

Jan 08, 2016

R2A20113ASP Preliminary

Electrical Characteristics (cont.)

(Ta = 25°C, VCC = 12 V, CS = 0.1 V, FB = COMP, RRT = 200 kΩ)

Item Symbol Min Typ Max Unit Test Conditions

Out Rise time tr-out — 35 100 ns CL = 1000 pF 90%

10%

tr

Fall time tf-out — 35 100 ns CL = 1000 pF 90%

10%

tf

Out low voltage Vol1-out — 0.08 0.2 V Isink = 20 mA

Vol2-out — 0.05 0.7 V Isink = 10 mA, VCC = 5 V

Out high voltage Voh-out 11.5 11.8 — V Isource = –20 mA

Over OCP threshold voltage Vocp –0.63 –0.6 –0.57 V

current

protection

Over & Dynamic OVP threshold voltage Vdovp — Vfb× — V *1

Under 1.040

voltage Dynamic UVP threshold voltage Vduvp — Vfb× — V *1

protection 0.920

Static OVP threshold voltage Vsovp Vfb× Vfb× Vfb× V

1.075 1.090 1.105

Static OVP hysteresis Hys-sovp 50 100 150 mV

FB low detect threshold voltage Vfblow 0.25 0.3 0.35 V

FB low detect hysteresis Hysfblow 0.16 0.20 0.24 V

Note: *1 Design spec

R03DS0026EJ0501 Rev.5.01 Page 6 of 12

Jan 08, 2016

R2A20113ASP Preliminary

Waveforms

1. Start-up

VCC 12V (Vuvlh)

5.02V (Vref)

3.6V

VREF

VREF GOOD

(Internal signal)

FB

0.5V (Vfblow + Hysfblow)

COMP 1.0V (Voff_ramp)

OUT

2. Shut-down

9.2V

(Vuvll)

VCC

OUT

Normal operation

R03DS0026EJ0501 Rev.5.01 Page 7 of 12

Jan 08, 2016

R2A20113ASP Preliminary

3. Gate Drive Output

COMP

RAMP+1V

(Internal signal)

RAMP

(Internal signal)

IL

0V (Vzcd)

CS

OUT

Enlargement around Zero-current detection

COMP

RAMP+1V

(Internal signal)

RAMP

(Internal signal)

IL

0mA

0V (Vzcd)

CS

0.44μs

OUT

R03DS0026EJ0501 Rev.5.01 Page 8 of 12

Jan 08, 2016

R2A20113ASP Preliminary

4. Overvoltage Protection (OVP)

Vsovp: Vfb × 1.09V

Hys-sovp: 100mV

VFB

OUT OFF

(Internal signal)

COMP

OUT

5. FB Low Detection

VFB

0.3V (Vfblow) 0.5V (Vfblow + Hysfblow)

FB LOW

(Internal signal)

COMP

OUT

R03DS0026EJ0501 Rev.5.01 Page 9 of 12

Jan 08, 2016

R2A20113ASP Preliminary

6. Overcurrent Protection (OCP)

COMP

RAMP+1V

(Internal signal)

RAMP

(Internal signal)

IL

0V

(Vzcd)

CS

–0.6V

(Vocp)

OUT

7. Off Time Control (Frequency Limiter)

IL

0A

ZCD_pulse

(Internal signal)

ZCD_mask

(Internal signal)

1.4μs 1.4μs 1.4μs

(Toff_min) (Toff_min) (Toff_min)

OUT

R03DS0026EJ0501 Rev.5.01 Page 10 of 12

Jan 08, 2016

R2A20113ASP Preliminary

System Diagram

L1 D1

PFC OUT

(390V dc)

6M

1.0μ Q1 220μ +

(450V)

From OUT VRB1

GND

0.05

(5W) AUX

VREF VCC

4 8

1μ

0.1μ

OUT

7

To

Q1 gate

GND

CS 6

5

100

1000p

R2A20113A

RT

3 FB

1

200k

COMP

2

200k

0.022μ

0.047μ

R03DS0026EJ0501 Rev.5.01 Page 11 of 12

Jan 08, 2016

R2A20113ASP Preliminary

Package Dimensions

JEITA Package Code RENESAS Code Previous Code MASS[Typ.]

P-SOP8-3.94x4.93-1.27 PRSP0008DJ-A — 0.073g

NOTE)

1. DIMENSIONS"*1 (Nom)"AND"*2"

*1 F DO NOT INCLUDE MOLD FLASH.

D

2. DIMENSION"*3"DOES NOT

INCLUDE TRIM OFFSET.

8 5

bp

HE

E

*2

c

Terminal cross section

Reference Dimension in Millimeters

Index mark (Ni/Pd/Au plating) Symbol

Min Nom Max

1 4 D 4.80 4.93 4.98

Z e *3

bp E 3.81 3.94 3.99

x M

A2 1.47

L1 A1 0.10 0.15 0.25

A 1.73

bp 0.35 0.41 0.49

b1

A

S

c 0.19 0.20 0.25

c1

θ

L θ 0° 8°

A1 HE 5.84 5.99 6.20

y S Detail F e 1.27

x 0.25

y 0.10

Z 0.56

L 0.41 0.64 0.89

L1 1.03

R03DS0026EJ0501 Rev.5.01 Page 12 of 12

Jan 08, 2016

Notice

1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for

the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the

use of these circuits, software, or information.

2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics

assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or

technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or

others.

4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or

third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on

the product's quality grade, as indicated below.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic

equipment; and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical

implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it

in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses

incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage

range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the

use of Renesas Electronics products beyond such specified ranges.

7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and

malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the

possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to

redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult,

please evaluate the safety of the final products or systems manufactured by you.

8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics

products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes

no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or

regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the

development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and

regulations and follow the procedures required by such laws and regulations.

10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the

contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics

products.

11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

(Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

(Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

SALES OFFICES http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information.

Renesas Electronics America Inc.

2801 Scott Boulevard Santa Clara, CA 95050-2549, U.S.A.

Tel: +1-408-588-6000, Fax: +1-408-588-6130

Renesas Electronics Canada Limited

9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3

Tel: +1-905-237-2004

Renesas Electronics Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K

Tel: +44-1628-585-100, Fax: +44-1628-585-900

Renesas Electronics Europe GmbH

Arcadiastrasse 10, 40472 Düsseldorf, Germany

Tel: +49-211-6503-0, Fax: +49-211-6503-1327

Renesas Electronics (China) Co., Ltd.

Room 1709, Quantum Plaza, No.27 ZhiChunLu Haidian District, Beijing 100191, P.R.China

Tel: +86-10-8235-1155, Fax: +86-10-8235-7679

Renesas Electronics (Shanghai) Co., Ltd.

Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, P. R. China 200333

Tel: +86-21-2226-0888, Fax: +86-21-2226-0999

Renesas Electronics Hong Kong Limited

Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong

Tel: +852-2265-6688, Fax: +852 2886-9022

Renesas Electronics Taiwan Co., Ltd.

13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan

Tel: +886-2-8175-9600, Fax: +886 2-8175-9670

Renesas Electronics Singapore Pte. Ltd.

80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949

Tel: +65-6213-0200, Fax: +65-6213-0300

Renesas Electronics Malaysia Sdn.Bhd.

Unit 1207, Block B, Menara Amcorp, Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia

Tel: +60-3-7955-9390, Fax: +60-3-7955-9510

Renesas Electronics India Pvt. Ltd.

No.777C, 100 Feet Road, HAL II Stage, Indiranagar, Bangalore, India

Tel: +91-80-67208700, Fax: +91-80-67208777

Renesas Electronics Korea Co., Ltd.

12F., 234 Teheran-ro, Gangnam-Gu, Seoul, 135-080, Korea

Tel: +82-2-558-3737, Fax: +82-2-558-5141

© 2016 Renesas Electronics Corporation. All rights reserved.

Colophon 5.0

You might also like

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- Chapter 5 Time Domain Response First Order SystemDocument11 pagesChapter 5 Time Domain Response First Order SystemZiad ObeidNo ratings yet

- R2A20133DDocument14 pagesR2A20133DLuiz Augusto Freitas SantosNo ratings yet

- 2A20112 PFC Fuentes LG Audio PFC CRITICALDocument9 pages2A20112 PFC Fuentes LG Audio PFC CRITICALAndres AlegriaNo ratings yet

- Bd9g341aefj LBDocument30 pagesBd9g341aefj LBFantazsta White Trash.No ratings yet

- Oscilador de PFC Fuente Toshiba 2A20112SPDocument8 pagesOscilador de PFC Fuente Toshiba 2A20112SPAntonio ChavezNo ratings yet

- Critical Conduction Mode PFC IC FA1A50N: DatasheetDocument26 pagesCritical Conduction Mode PFC IC FA1A50N: Datasheetdtftfernandes9099No ratings yet

- ML4812CPDocument17 pagesML4812CPIntan LianaNo ratings yet

- FP6321A FitiDocument14 pagesFP6321A FitiJob GarciaNo ratings yet

- KA2S0680 FairchildSemiconductor PDFDocument8 pagesKA2S0680 FairchildSemiconductor PDFLuisa AguileraNo ratings yet

- Datasheet PDFDocument8 pagesDatasheet PDFLuisa Aguilera100% (1)

- Ic Driver LCD HP G5121 5121M PDFDocument9 pagesIc Driver LCD HP G5121 5121M PDFBudi PrayitnoNo ratings yet

- 2A 23V Synchronous Buck Converter: General DescriptionDocument15 pages2A 23V Synchronous Buck Converter: General DescriptionmoftahNo ratings yet

- Control de Garganta TACDocument15 pagesControl de Garganta TACmario rosasNo ratings yet

- M62429P/FP: Serial Data Control Dual Electronic VolumeDocument8 pagesM62429P/FP: Serial Data Control Dual Electronic VolumeahmedNo ratings yet

- PDF Fairchild 430756Document14 pagesPDF Fairchild 430756Giovanni Carrillo VillegasNo ratings yet

- LD7575B DS 00 PDFDocument17 pagesLD7575B DS 00 PDFjeovanevsNo ratings yet

- General Description: 3A 27V Synchronous Buck ConverterDocument15 pagesGeneral Description: 3A 27V Synchronous Buck ConverterDario David DimaroNo ratings yet

- FAN4822Document10 pagesFAN482240818248No ratings yet

- FA5604 3slg6dr2bxDocument30 pagesFA5604 3slg6dr2bxWagner MenezesNo ratings yet

- Integrados KaDocument20 pagesIntegrados KaJosé Carlos de Barros MelloNo ratings yet

- Transition-Mode PFC Controller With Fault Condition ProtectionDocument16 pagesTransition-Mode PFC Controller With Fault Condition ProtectionAdailton SantosNo ratings yet

- LD7577 DS 01 PDFDocument18 pagesLD7577 DS 01 PDFLucilia Dos Santos100% (2)

- Acer Al1916w Psu-Inverter dt830Document55 pagesAcer Al1916w Psu-Inverter dt830LuisNo ratings yet

- Green-Mode PWM Controller With High-Voltage Start-Up CircuitDocument17 pagesGreen-Mode PWM Controller With High-Voltage Start-Up Circuitserrano.flia.coNo ratings yet

- KA3525A FairchildSemiconductorDocument7 pagesKA3525A FairchildSemiconductorA.hNo ratings yet

- 3843ANDocument8 pages3843ANinfosolutionNo ratings yet

- SD6834 - Datasheet: Current Mode PWM+PFM Controller With Built-In High Voltage MosfetDocument10 pagesSD6834 - Datasheet: Current Mode PWM+PFM Controller With Built-In High Voltage Mosfetحسین مشعلNo ratings yet

- General Description: Level Translating I C-Bus RepeaterDocument19 pagesGeneral Description: Level Translating I C-Bus RepeatersreekanthNo ratings yet

- Ka1m0880b DatasheetDocument8 pagesKa1m0880b DatasheetluisNo ratings yet

- SPS Ka1m0880: To-3p-5lDocument8 pagesSPS Ka1m0880: To-3p-5lAndrzej WojtalaNo ratings yet

- Usb Boost Optional U5 Lp6252Document8 pagesUsb Boost Optional U5 Lp6252Sergio SeelingNo ratings yet

- 5ch Power Driver For Cd-Rom, Dvd-Rom: BD7904FSDocument19 pages5ch Power Driver For Cd-Rom, Dvd-Rom: BD7904FSVeiko CastañedaNo ratings yet

- KA1L0380RDocument12 pagesKA1L0380Radisurya13.afNo ratings yet

- KA1L0380B/KA1L0380RB/KA1M0380RB/ KA1H0380RB: Fairchild Power Switch (SPS)Document12 pagesKA1L0380B/KA1L0380RB/KA1M0380RB/ KA1H0380RB: Fairchild Power Switch (SPS)Saad LehlouNo ratings yet

- LSP5526Document17 pagesLSP5526Hadi Habibi ShahandashtiNo ratings yet

- Training Msi MS-6+Document15 pagesTraining Msi MS-6+adaofisicoNo ratings yet

- Synchronous Buck PWM DC-DC Controller: Fitipower Integrated Technology LNCDocument14 pagesSynchronous Buck PWM DC-DC Controller: Fitipower Integrated Technology LNCEchefisEchefisNo ratings yet

- U P6103Document15 pagesU P6103Selmar CavalcantiNo ratings yet

- PowerOne - AC-DC 48v 600watts OutputDocument1 pagePowerOne - AC-DC 48v 600watts OutputImran YaminNo ratings yet

- LM5030 Application: DC - DC Converter Utilizing The Push-Pull TopologyDocument10 pagesLM5030 Application: DC - DC Converter Utilizing The Push-Pull TopologyEdoardoNo ratings yet

- Single-Ended To Differential Using A Two Op-Amp CircuiDocument9 pagesSingle-Ended To Differential Using A Two Op-Amp CircuiSanjay ParelkarNo ratings yet

- KA7552A/KA7553A: SMPS ControllerDocument8 pagesKA7552A/KA7553A: SMPS ControllerVergil OlteanuNo ratings yet

- 3842a DatasheetDocument8 pages3842a DatasheetVịnh DemoNo ratings yet

- KA3842AC/KA3842AE SMPS Controller: Features DescriptionDocument7 pagesKA3842AC/KA3842AE SMPS Controller: Features DescriptionJuan GomezNo ratings yet

- AX3161 AXEliteDocument12 pagesAX3161 AXEliteCristian CiocoiuNo ratings yet

- Datasheet IC 3771 PDFDocument20 pagesDatasheet IC 3771 PDFekodianirawanto100% (1)

- Fujitsu mb1502Document15 pagesFujitsu mb1502haha2012No ratings yet

- Taller 1Document5 pagesTaller 1Brayan JulianNo ratings yet

- Aec Lab TestDocument10 pagesAec Lab Testknighthood4allNo ratings yet

- Fan 7601Document12 pagesFan 7601Walter AlvarengaNo ratings yet

- Datasheet - HK lp6253 8406861Document11 pagesDatasheet - HK lp6253 8406861Boban CvetkovicNo ratings yet

- LD 7550Document15 pagesLD 7550Evanier Souza de AlencarNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- A Guide to Vintage Audio Equipment for the Hobbyist and AudiophileFrom EverandA Guide to Vintage Audio Equipment for the Hobbyist and AudiophileNo ratings yet

- Mappc2200-Eng V2.01Document277 pagesMappc2200-Eng V2.01birricaNo ratings yet

- G6N Sony KDL-40XBR9 EX2MDocument4 pagesG6N Sony KDL-40XBR9 EX2MbirricaNo ratings yet

- FP50R12KE3 InfineonDocument11 pagesFP50R12KE3 InfineonbirricaNo ratings yet

- 2 SK 3723Document2 pages2 SK 3723birricaNo ratings yet

- DS2000 Full Digital Servodrives For Brushless Motors Suitable For Universal Power SupplyDocument16 pagesDS2000 Full Digital Servodrives For Brushless Motors Suitable For Universal Power SupplybirricaNo ratings yet

- Description Features: For Most Current Data Sheet and Other ProductDocument14 pagesDescription Features: For Most Current Data Sheet and Other ProductbirricaNo ratings yet

- 2.software and Hardware Requirement SpecificationDocument3 pages2.software and Hardware Requirement Specificationnaba221085No ratings yet

- Bentley NevadaDocument4 pagesBentley NevadarenvouzNo ratings yet

- ch4 Lesson 5,6Document40 pagesch4 Lesson 5,6Abhi RokXsNo ratings yet

- Manage Tablespaces in A Container Database (CDB) and Pluggable Database (PDB)Document3 pagesManage Tablespaces in A Container Database (CDB) and Pluggable Database (PDB)Ahmed NagyNo ratings yet

- Loctite Stycast 2762: Technical Data SheetDocument3 pagesLoctite Stycast 2762: Technical Data SheetankitaNo ratings yet

- 0026-1394 41 1 001 PDFDocument8 pages0026-1394 41 1 001 PDFOmar PonsNo ratings yet

- F646 CompleteSampleDocument36 pagesF646 CompleteSampleraj4523No ratings yet

- 502 Evolved Has at The Are The Can and Or: RefineryDocument8 pages502 Evolved Has at The Are The Can and Or: RefineryKaranNo ratings yet

- PS3-2 - Sequences Series, Rates, and Equation TheoryDocument6 pagesPS3-2 - Sequences Series, Rates, and Equation TheoryJoseph AparisNo ratings yet

- Class 8 CH 5 Data Handling August 19Document3 pagesClass 8 CH 5 Data Handling August 19shayn budihardjoNo ratings yet

- Reasoning Key Coding Decoding Kanishk@MailDocument8 pagesReasoning Key Coding Decoding Kanishk@MailKainshk Gupta100% (1)

- Pfe Training AvDocument20 pagesPfe Training AvpankajNo ratings yet

- IR General Calibration InstructionsDocument1 pageIR General Calibration Instructionsw.ross.scott6185No ratings yet

- For All Sanfoundry MCQ (1000+ MCQ) JOIN Telegram GroupDocument472 pagesFor All Sanfoundry MCQ (1000+ MCQ) JOIN Telegram GroupRitesh DeshmukhNo ratings yet

- WSForcogsa Service Old 3Document4 pagesWSForcogsa Service Old 3Baltazar PazosNo ratings yet

- Introducing Spring Batch SlidesDocument20 pagesIntroducing Spring Batch SlidesKIRAKRATOSNo ratings yet

- Ace 202Document14 pagesAce 202leovotinh85No ratings yet

- AutoMax-80 LIS Manual PDFDocument51 pagesAutoMax-80 LIS Manual PDFDani Dwi PutraNo ratings yet

- ButterflyMX - Elevator Control Wiring DiagramDocument1 pageButterflyMX - Elevator Control Wiring DiagramSyed iliyasNo ratings yet

- Experiment 5 - Laplace and Inverse Laplace TransformDocument18 pagesExperiment 5 - Laplace and Inverse Laplace TransformTTK MARVINNo ratings yet

- Lecture 19 BDocument6 pagesLecture 19 BHongYu HuiNo ratings yet

- Is 13630 2 2006 PDFDocument8 pagesIs 13630 2 2006 PDFMazhar DhankotNo ratings yet

- 09 Displacement Method - Slope Deflection EquationsDocument29 pages09 Displacement Method - Slope Deflection EquationsZhwa 18No ratings yet

- Dojo 1 AjaxDocument37 pagesDojo 1 Ajaxmdshareef84No ratings yet

- 04 Alternate Process ControlDocument24 pages04 Alternate Process ControlRaja DuraiNo ratings yet

- Development of Asymmetries: Jan E. KronmillerDocument4 pagesDevelopment of Asymmetries: Jan E. KronmillerAdrian Silva SantosNo ratings yet

- Improper Rotation: 1 Three DimensionsDocument3 pagesImproper Rotation: 1 Three DimensionsManuel MensaNo ratings yet

- Programming Assignment I: 1 Overview of The Programming ProjectDocument3 pagesProgramming Assignment I: 1 Overview of The Programming ProjectHoussem NasriNo ratings yet

- Paper 3Document20 pagesPaper 3habtamu tamiruNo ratings yet