Professional Documents

Culture Documents

128K X 16 Static Ram: Cy62136V Mobl™

128K X 16 Static Ram: Cy62136V Mobl™

Uploaded by

Anh ĐườngOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

128K X 16 Static Ram: Cy62136V Mobl™

128K X 16 Static Ram: Cy62136V Mobl™

Uploaded by

Anh ĐườngCopyright:

Available Formats

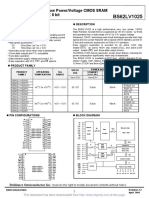

CY62136V MoBL™

128K x 16 Static RAM

Features HIGH), outputs are disabled (OE HIGH), BHE and BLE are

disabled (BHE, BLE HIGH), or during a write operation (CE

• Low voltage range: LOW, and WE LOW).

— CY62136V: 2.7V-3.6V Writing to the device is accomplished by taking Chip Enable

• Ultra-low active, standby power (CE) and Write Enable (WE) inputs LOW. If Byte Low Enable

• Easy memory expansion with CE and OE features (BLE) is LOW, then data from I/O pins (I/O0 through I/O7), is

written into the location specified on the address pins (A0

• TTL-compatible inputs and outputs through A16). If Byte High Enable (BHE) is LOW, then data

• Automatic power-down when deselected from I/O pins (I/O8 through I/O15) is written into the location

• CMOS for optimum speed/power specified on the address pins (A0 through A16).

Functional Description Reading from the device is accomplished by taking Chip En-

The CY62136V is a high-performance CMOS static RAM or- able (CE) and Output Enable (OE) LOW while forcing the Write

ganized as 131,072 words by 16 bits. This device features ad- Enable (WE) HIGH. If Byte Low Enable (BLE) is LOW, then

vanced circuit design to provide ultra-low active current. This data from the memory location specified by the address pins

is ideal for providing More Battery Life™ (MoBL™) in portable will appear on I/O0 to I/O7. If Byte High Enable (BHE) is LOW,

applications such as cellular telephones. The device also has then data from memory will appear on I/O8 to I/O15. See the

an automatic power-down feature that significantly reduces Truth Table at the back of this data sheet for a complete de-

power consumption by 99% when addresses are not toggling. scription of read and write modes.

The device can also be put into standby mode when deselect- The CY62136V is available in 48-ball FBGA and standard

ed (CE HIGH). The input/output pins (I/O0 through I/O15) are 44-pin TSOP Type II (forward pinout) packaging.

placed in a high-impedance state when: deselected (CE

Logic Block Diagram Pin Configurations

TSOP II (Forward)

Top View

A4 1 44 A5

A3 2 43 A6

DATA IN DRIVERS

A2 3 42 A7

A1 4 41 OE

A8 A0 5 40 BHE

A7 CE 6 39 BLE

ROW DECODER

A6 I/O0 38 I/O15

SENSE AMPS

7

A5 I/O1 8 37 I/O14

A4 128K x 16 I/O2 9 36 I/O13

RAM Array I/O0–I/O7 I/O3 10 35 I/O12

A3

1024 X 2048 VCC 11 34 VSS

A2 I/O8–I/O15 VSS 12 33 VCC

A1 I/O4 13 32 I/O11

A0 I/O5 14 31 I/O10

I/O6 15 30 I/O9

I/O7 16 29 I/O8

WE 17 28 NC

A16 18 27 A8

COLUMN DECODER A15 19 26 A9

A14 20 25 A10

A13 21 24 A11

A12 22 23 NC

BHE

WE

A11

A12

A13

A14

A15

A10

A9

CE

A16

OE

BLE

MoBL and More Battery Life are trademarks of Cypress Semiconductor Corporation.

Cypress Semiconductor Corporation • 3901 North First Street • San Jose • CA 95134 • 408-943-2600

Document #: 38-05087 Rev. ** Revised September 5, 2000

This datasheet has been downloaded from http://www.digchip.com at this page

CY62136V MoBL™

Pin Configurations (continued)

FBGA

Top View

1 2 3 4 5 6

BLE OE A0 A1 A2 NC A

I/O8 BHE A3 A4 CE I/O0 B

I/O9 I/O10 A5 A6 I/O1 I/O2 C

VSS I/O11 NC A7 I/O3 VCC D

VCC I/O12 NC A16 I/O4 VSS E

I/O14 I/O13 A14 A15 I/O5 I/O6 F

I/O15 NC A12 A13 WE I/O7 G

NC A8 A9 A10 A11 NC H

Maximum Ratings DC Voltage Applied to Outputs

in High Z State[1]....................................–0.5V to VCC + 0.5V

(Above which the useful life may be impaired. For user guide-

lines, not tested.) DC Input Voltage[1].................................–0.5V to VCC + 0.5V

Storage Temperature ..................................–65°C to +150°C Output Current into Outputs (LOW)..............................20 mA

Ambient Temperature with Static Discharge Voltage............................................>2001V

Power Applied............................................. –55°C to +125°C (per MIL-STD-883, Method 3015)

Supply Voltage to Ground Potential................–0.5V to +4.6V Latch-Up Current.....................................................>200 mA

Operating Range

Device Range Ambient Temperature VCC

CY62136V Industrial −40°C to +85°C 2.7V to 3.6V

Product Portfolio

Power Dissipation (Industrial)

VCC Range Operating (ICC) Standby (ISB2)

[2] [2] [2]

Product VCC(min.) VCC(typ.) VCC(max.) Power Typ. Maximum Typ. Maximum

CY62136V 2.7V 3.0V 3.6V LL 7 mA 15 mA 1 µA 15 µA

Notes:

1. VIL(min) = –2.0V for pulse durations less than 20 ns.

2. Typical values are included for reference only and are not guaranteed or tested. Typical values are measured at VCC = VCC Typ, TA = 25°C.

Document #: 38-05087 Rev. ** Page 2 of 12

CY62136V MoBL™

Electrical Characteristics Over the Operating Range

CY62136V

Parameter Description Test Conditions Min. Typ.[2] Max. Unit

VOH Output HIGH Voltage IOH = −1.0 mA VCC = 2.7V 2.4 V

VOL Output LOW Voltage IOL = 2.1 mA VCC = 2.7V 0.4 V

VIH Input HIGH Voltage VCC = 3.6V 2.2 VCC + 0.5V V

VIL Input LOW Voltage VCC = 2.7V −0.5 0.8 V

IIX Input Load Current GND < VI < VCC −1 +1 +1 µA

IOZ Output Leakage Current GND < VO < VCC, Output Disabled −1 +1 +1 µA

ICC VCC Operating Supply IOUT = 0 mA, VCC = 3.6V 7 15 mA

Current f = fMAX = 1/tRC,

CMOS levels

IOUT = 0 mA, 1 2 mA

f = 1 MHz,

CMOS Levels

ISB1 Automatic CE CE > VCC−0.3V, 100 µA

Power-Down Current— VIN > VCC−0.3V or

CMOS Inputs VIN < 0.3V, f = fMAX

ISB2 Automatic CE CE > VCC−0.3V VCC = LL 1 15 µA

Power-Down Current— VIN > VCC−0.3V 3.6V

CMOS Inputs or VIN < 0.3V, f = 0

Capacitance[3]

Parameter Description Test Conditions Max. Unit

CIN Input Capacitance TA = 25°C, f = 1 MHz, 6 pF

COUT Output Capacitance VCC= VCC(typ) 8 pF

Thermal Resistance

Description Test Conditions Symbol BGA TSOPII Unit

Thermal Resistance Still Air, soldered on a 4.25 x 1.125 inch, 4-layer ΘJA 55 60 °C/W

(Junction to Ambient)[3] printed circuit board

Thermal Resistance ΘJC 16 22 °C/W

(Junction to Case)[3]

Note:

3. Tested initially and after any design or process changes that may affect these parameters.

Document #: 38-05087 Rev. ** Page 3 of 12

CY62136V MoBL™

AC Test Loads and Waveforms

R1 R1 ALL INPUT PULSES

VCC VCC VCC Typ

90% 90%

OUTPUT OUTPUT 10% 10%

GND

30 pF R2 5 pF R2

Rise Time: Fall Time:

INCLUDING 1 V/ns 1 V/ns

INCLUDING

JIG AND JIG AND

SCOPE SCOPE

(a) (b) (c)

Equivalent to: THÉVENIN EQUIVALENT

RTH

OUTPUT V

Parameters 3.0V UNIT

R1 1105 Ohms

R2 1550 Ohms

RTH 645 Ohms

VTH 1.75V Volts

Data Retention Characteristics (Over the Operating Range)

Parameter Description Conditions[5] Min. Typ.[2] Max. Unit

VDR VCC for Data Retention 1.0 3.6 V

ICCDR Data Retention Current VCC = 1.0V LL 0.5 7.5 µA

CE > VCC − 0.3V,

VIN > VCC − 0.3V or

VIN < 0.3V

No input may exceed

VCC+0.3V

tCDR[3] Chip Deselect to Data 0 ns

Retention Time

tR[4] Operation Recovery Time 70 ns

Data Retention Waveform

DATA RETENTION MODE

VCC VCC(min.) VDR > 1.0 V VCC(min.)

tCDR tR

CE

Notes:

4. Full device operation requires linear VCC ramp from VDR to VCC(min) > 100 ms or stable at VCC(min) > 100 ms.

5. Test conditions assume signal transition time of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to VCC typ., and output loading of the specified

IOL/IOH and 30-pF load capacitance.

Document #: 38-05087 Rev. ** Page 4 of 12

CY62136V MoBL™

Switching Characteristics Over the Operating Range[5]

55 ns 70 ns

Parameter Description Min. Max. Min. Max. Unit

READ CYCLE

tRC Read Cycle Time 55 70 ns

tAA Address to Data Valid 55 70 ns

tOHA Data Hold from Address Change 10 10 ns

tACE CE LOW to Data Valid 55 70 ns

tDOE OE LOW to Data Valid 25 35 ns

[6]

tLZOE OE LOW to Low Z 5 5 ns

[6, 7]

tHZOE OE HIGH to High Z 25 25 ns

tLZCE CE LOW to Low Z[6] 10 10 ns

[6, 7]

tHZCE CE HIGH to High Z 25 25 ns

tPU CE LOW to Power-Up 0 0 ns

tPD CE HIGH to Power-Down 55 70 ns

tDBE BLE / BHE LOW to Data Valid 25 35 ns

[6, 7]

tLZBE BLE / BHE LOW to Low Z 5 5 ns

[8]

tHZBE BLE / BHE HIGH to High Z 25 25 ns

[8, 9]

WRITE CYCLE

tWC Write Cycle Time 55 70 ns

tSCE CE LOW to Write End 45 60 ns

tAW Address Set-Up to Write End 45 60 ns

tHA Address Hold from Write End 0 0 ns

tSA Address Set-Up to Write Start 0 0 ns

tPWE WE Pulse Width 40 50 ns

tBW BLE / BHE LOW to Write End 50 60 ns

tSD Data Set-Up to Write End 25 30 ns

tHD Data Hold from Write End 0 0 ns

[6, 7]

tHZWE WE LOW to High Z 20 25 ns

[6]

tLZWE WE HIGH to Low Z 5 10 ns

Switching Waveforms

Read Cycle No. 1 [10, 11]

tRC

ADDRESS

tAA

tOHA

DATA OUT PREVIOUS DATA VALID DATA VALID

Notes:

6. At any given temperature and voltage condition, tHZCE is less than tLZCE, tHZOE is less than tLZOE, and tHZWE is less than tLZWE for any given device.

7. tHZOE, tHZCE, and tHZWE are specified with CL = 5 pF as in part (b) of AC Test Loads. Transition is measured ±500 mV from steady-state voltage.

8. The internal write time of the memory is defined by the overlap of CE LOW and WE LOW. Both signals must be LOW to initiate a write and either signal can terminate

a write by going HIGH. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

9. The minimum write cycle time for write cycle #3 (WE controlled, OE LOW) is the sum of tHZWE and tSD.

10. Device is continuously selected. OE, CE = VIL.

11. WE is HIGH for read cycle.

Document #: 38-05087 Rev. ** Page 5 of 12

CY62136V MoBL™

Switching Waveforms (continued)

Read Cycle No. 2 [11, 12]

tRC

CE

tPD

tACE tHZCE

OE

tDOE tHZOE

BHE/BLE tLZOE

tHZBE

tDBE

tLZBE

HIGH

HIGH IMPEDANCE IMPEDANCE

DATA OUT DATA VALID

tLZCE

tPU

VCC ICC

SUPPLY 50% 50%

CURRENT ISB

[8, 13, 14]

Write Cycle No. 1 (WE Controlled)

tWC

ADDRESS

CE

tAW tHA

tSA tPWE

WE

BHE/BLE tBW

OE

tSD tHD

DATA I/O NOTE 15 DATAIN VALID

tHZOE

Notes:

12. Address valid prior to or coincident with CE transition LOW.

13. Data I/O is high impedance if OE = VIH.

14. If CE goes HIGH simultaneously with WE HIGH, the output remains in a high-impedance state.

15. During this period, the I/Os are in output state and input signals should not be applied.

Document #: 38-05087 Rev. ** Page 6 of 12

CY62136V MoBL™

Switching Waveforms (continued)

[8, 13, 14]

Write Cycle No. 2 (CE Controlled)

tWC

ADDRESS

CE tSCE

tSA

tAW tHA

BHE/BLE tBW

WE tPWE

tSD tHD

DATA I/O DATAIN VALID

[9, 14]

Write Cycle No. 3 (WE Controlled, OE LOW)

tWC

ADDRESS

CE

tAW tHA

BHE/BLE tBW

tSA

WE

tSD tHD

DATA I/O NOTE 15 DATAIN VALID

tHZWE tLZWE

Document #: 38-05087 Rev. ** Page 7 of 12

CY62136V MoBL™

Switching Waveforms (continued)

[15]

Write Cycle No. 4 (BHE/BLE Controlled, OE LOW)

tWC

ADDRESS

CE

tAW tHA

BHE/BLE tBW

tSA

WE

tSD tHD

DATA I/O NOTE 15 DATAIN VALID

tHZWE tLZWE

Document #: 38-05087 Rev. ** Page 8 of 12

CY62136V MoBL™

Typical DC and AC Characteristics

Normalized Operating Current Standby Current vs. Supply Voltage

vs. Supply Voltage 35

1.4

MoBL

30

1.2

MoBL 25

1.0

ISB (µA)

20

0.8

ICC

15

0.6

10

0.4

5

0.2

0

0.0 1.0 1.9 2.7 2.8 3.7

1.7 2.2 2.7 3.2 3.7

SUPPLY VOLTAGE (V)

SUPPLY VOLTAGE (V)

Access Time vs. Supply Voltage

80

MoBL

70

60

50

40

TAA (ns)

30

20

10

1.0 1.9 2.7 2.8 3.7

SUPPLY VOLTAGE (V)

Truth Table

CE WE OE BHE BLE Inputs/Outputs Mode Power

H X X X X High Z Deselect/Power-Down Standby (ISB)

L H L L L Data Out (I/OO–I/O15) Read Active (ICC)

L H L H L Data Out (I/OO–I/O7); Read Active (ICC)

I/O8–I/O15 in High Z

L H L L H Data Out (I/O8–I/O15); Read Active (ICC)

I/O0–I/O7 in High Z

L H L H H High Z Deselect/Output Disabled Active (ICC)

L H H L L High Z Deselect/Output Disabled Active (ICC)

L H H H L High Z Deselect/Output Disabled Active (ICC)

L H H L H High Z Deselect/Output Disabled Active (ICC)

L L X L L Data In (I/OO–I/O15) Write Active (ICC)

L L X H L Data In (I/OO–I/O7); Write Active (ICC)

I/O8–I/O15 in High Z

L L X L H Data In (I/O8–I/O15); Write Active (ICC)

I/O0 –I/O7 in High Z

Document #: 38-05087 Rev. ** Page 9 of 12

CY62136V MoBL™

Ordering Information

Speed Package Operating

(ns) Ordering Code Name Package Type Range

55 CY62136VLL-55ZI Z44 44-Pin TSOP II Industrial

CY62136VLL-55BAI BA48 48-Ball Fine Pitch BGA

70 CY62136VLL-70ZI Z44 44-Pin TSOP II

CY62136VLL-70BAI BA48 48-Ball Fine Pitch BGA

Package Diagrams

48-Ball (7.00 mm x 7.00 mm) FBGA BA48

51-85096-D

Document #: 38-05087 Rev. ** Page 10 of 12

62136V: 8/2000

Revision: February 2, 2001

CY62136V MoBL™

Package Diagrams (continued)

44-Pin TSOP II Z44

51-85087-A

Document #: 38-05087 Rev. ** Page 11 of 12

© Cypress Semiconductor Corporation, 2001. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use

of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize

its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress

Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

CY62136V MoBL™

Document Title: CY62136V MoBL™ 128K x 16 Static RAM

Document Number: 38-05087

REV. ECN NO. Issue Date Oreg. of Change Description of Change

** 107347 05/25/01 SZV Change from Spec #: 38-00728 to 38-05087

Document #: 38-05087 Rev. ** Page 12 of 12

You might also like

- 0831133473-CNC Programming Handbook, Third Edition by Peter SmidDocument5 pages0831133473-CNC Programming Handbook, Third Edition by Peter Smidwyzynucy0% (3)

- INFOBIP Solution Overview - WhatsAppDocument30 pagesINFOBIP Solution Overview - WhatsApphendro_suronoNo ratings yet

- HW 3Document7 pagesHW 3ZabinNo ratings yet

- Cy7c1019cv33 12zcDocument8 pagesCy7c1019cv33 12zcTuhin KarakNo ratings yet

- Memory DataSheetDocument10 pagesMemory DataSheetNguyễn Ngọc HuyNo ratings yet

- 6264Document8 pages6264api-3711187No ratings yet

- 256K X 4 Static RAM: PreliminaryDocument10 pages256K X 4 Static RAM: PreliminaryedgarlibanioNo ratings yet

- CY7C1021 15ZC Cypress SemiconductorDocument9 pagesCY7C1021 15ZC Cypress SemiconductorAkram KareemNo ratings yet

- IC6264 DatasheetDocument9 pagesIC6264 DatasheetMightyelectronics EquipmentsNo ratings yet

- FlashMemory-DataSheets Atmel Elenota - PLDocument13 pagesFlashMemory-DataSheets Atmel Elenota - PLriegerautoNo ratings yet

- CY62148EV3Document16 pagesCY62148EV3Dario Gabriel Coz RojasNo ratings yet

- HY628400 HynixSemiconductorDocument9 pagesHY628400 HynixSemiconductorHamidNo ratings yet

- 4-Mbit (256K X 16) Static RAM: Features Functional DescriptionDocument14 pages4-Mbit (256K X 16) Static RAM: Features Functional DescriptionPaulo SilvaNo ratings yet

- 1-Mbit (64 K × 16) Static RAM: Features Functional DescriptionDocument18 pages1-Mbit (64 K × 16) Static RAM: Features Functional DescriptionNisar AhmedNo ratings yet

- LH 511610Document11 pagesLH 511610Charly NitroNo ratings yet

- CY7C1011CV33 - 2-Mbit - (128 K X 16) - Static - RAMDocument18 pagesCY7C1011CV33 - 2-Mbit - (128 K X 16) - Static - RAMNesimi ÇiçekNo ratings yet

- 256-Kbit (32K × 8) Static RAM: Features Functional DescriptionDocument16 pages256-Kbit (32K × 8) Static RAM: Features Functional DescriptionMurilo Smse SmseNo ratings yet

- Eeprom At28c64Document14 pagesEeprom At28c64Manuel FonsecaNo ratings yet

- Atmel 29C256 MemoryDocument17 pagesAtmel 29C256 MemoryYoseth Jose Vasquez ParraNo ratings yet

- AT29C040A-p (FLASH)Document17 pagesAT29C040A-p (FLASH)abolfazlNo ratings yet

- Atmel AT49F040ADocument17 pagesAtmel AT49F040Aantaeus71No ratings yet

- 1-Megabit (128K X 8) 3-Volt Only Flash Memory AT29LV010A: FeaturesDocument16 pages1-Megabit (128K X 8) 3-Volt Only Flash Memory AT29LV010A: FeaturesDuc Luu VuNo ratings yet

- Sram - Cy7c199dDocument16 pagesSram - Cy7c199dbrunex000No ratings yet

- HN58C66 EEPROM DatasheetDocument19 pagesHN58C66 EEPROM Datasheetantony.briggsNo ratings yet

- Eeprom 29c040Document13 pagesEeprom 29c040api-3710567No ratings yet

- Hy628100alg 70Document9 pagesHy628100alg 70Claudiney BricksNo ratings yet

- Sram DesignDocument14 pagesSram DesignThanh Nguyễn xuânNo ratings yet

- Infineon-CY7C1011CV33 Automotive 2-Mbit (128 K 16) Static RAM Datasheet-AdditionalTechnicalInformation-v04 00-ENDocument16 pagesInfineon-CY7C1011CV33 Automotive 2-Mbit (128 K 16) Static RAM Datasheet-AdditionalTechnicalInformation-v04 00-ENМихаил НеизвестновичNo ratings yet

- 64K (8Kx8) Parallel Eeproms AT28C64 AT28C64X: FeaturesDocument12 pages64K (8Kx8) Parallel Eeproms AT28C64 AT28C64X: FeaturesbacagratisNo ratings yet

- 8 High Speed Cmos Static Ram: General DescriptionDocument11 pages8 High Speed Cmos Static Ram: General DescriptionDavidNo ratings yet

- Igh-Speed 256k-Bit Parallel Interface FRAM: MB85R256HDocument5 pagesIgh-Speed 256k-Bit Parallel Interface FRAM: MB85R256HAndy De ProdoNo ratings yet

- 1-Megabit (128K X 8) 5-Volt Only Flash Memory AT29C010A: FeaturesDocument19 pages1-Megabit (128K X 8) 5-Volt Only Flash Memory AT29C010A: FeaturesGeniuss JplNo ratings yet

- AT28HC256Document16 pagesAT28HC256Harris RaoNo ratings yet

- Infineon-CY62148E MoBL 4-Mbit (512 K 8) Static RAM-DataSheet-v20 00-ENDocument20 pagesInfineon-CY62148E MoBL 4-Mbit (512 K 8) Static RAM-DataSheet-v20 00-ENPurple HazeNo ratings yet

- General Description: Publication Release Date: March 1999 - 1 - Revision A7Document10 pagesGeneral Description: Publication Release Date: March 1999 - 1 - Revision A7algnben1746No ratings yet

- 4-Megabit (512K X 8) 5-Volt Only 256-Byte Sector Flash Memory AT29C040ADocument17 pages4-Megabit (512K X 8) 5-Volt Only 256-Byte Sector Flash Memory AT29C040AJames wooNo ratings yet

- 1-Megabit (128K X 8) Paged Parallel Eeprom AT28C010: FeaturesDocument16 pages1-Megabit (128K X 8) Paged Parallel Eeprom AT28C010: FeaturesMario BozicevicNo ratings yet

- Doc0353i 1108110Document17 pagesDoc0353i 1108110ChrisNo ratings yet

- AT49F512Document11 pagesAT49F512Jaroslav AcsNo ratings yet

- 4-Megabit (512K X 8) 3-Volt Only 256-Byte Sector Flash Memory AT29LV040ADocument17 pages4-Megabit (512K X 8) 3-Volt Only 256-Byte Sector Flash Memory AT29LV040A01666754614No ratings yet

- UM61512A Series: 64K X 8 Bit High Speed Cmos SramDocument16 pagesUM61512A Series: 64K X 8 Bit High Speed Cmos SramCarlos ReisNo ratings yet

- 32-Mbit (2 M × 16 / 4 M × 8) Static RAM: Features Functional DescriptionDocument18 pages32-Mbit (2 M × 16 / 4 M × 8) Static RAM: Features Functional DescriptionMank UduyNo ratings yet

- 256K (32K X 8) Paged Parallel Eeprom AT28C256: FeaturesDocument27 pages256K (32K X 8) Paged Parallel Eeprom AT28C256: FeaturesAhmed AlsheikhNo ratings yet

- 2-Mbit (128 K × 16) Static RAM: Features Functional DescriptionDocument16 pages2-Mbit (128 K × 16) Static RAM: Features Functional DescriptionChinicuas Jose Manuel Maldonado MendozaNo ratings yet

- 256K (32K X 8) High-Speed Parallel Eeprom AT28HC256: FeaturesDocument24 pages256K (32K X 8) High-Speed Parallel Eeprom AT28HC256: FeaturesABDUL QADIRNo ratings yet

- IS61LV2568L: 256K X 8 High-Speed Cmos Static RamDocument14 pagesIS61LV2568L: 256K X 8 High-Speed Cmos Static RamTan Hung LuuNo ratings yet

- IC17 HM62864-HitachiDocument15 pagesIC17 HM62864-HitachiWinston WolfNo ratings yet

- 256K (32K X 8) Paged Parallel Eeprom AT28C256: FeaturesDocument18 pages256K (32K X 8) Paged Parallel Eeprom AT28C256: FeaturesaerknbznmisdovdzooNo ratings yet

- R1LV1616H-I Series: Wide Temperature Range Version 16 M SRAM (1-Mword × 16-Bit / 2-Mword × 8-Bit)Document21 pagesR1LV1616H-I Series: Wide Temperature Range Version 16 M SRAM (1-Mword × 16-Bit / 2-Mword × 8-Bit)samsularief03No ratings yet

- GalatmelDocument26 pagesGalatmelNacho RomanelloNo ratings yet

- AT28C010 Military P 128kbyteDocument16 pagesAT28C010 Military P 128kbyteabolfazlNo ratings yet

- IS63LV1024 IS63LV1024L: 128K X 8 High-Speed Cmos Static Ram 3.3V Revolutionary PinoutDocument16 pagesIS63LV1024 IS63LV1024L: 128K X 8 High-Speed Cmos Static Ram 3.3V Revolutionary PinoutTan Hung LuuNo ratings yet

- R1LP0408CSB 5siDocument14 pagesR1LP0408CSB 5sisolitecppNo ratings yet

- 32kx8bit CMOS SRAM: HY62256A SeriesDocument9 pages32kx8bit CMOS SRAM: HY62256A SeriesHernan KisielNo ratings yet

- Is62c256al 45vliDocument13 pagesIs62c256al 45vliRichard HungNo ratings yet

- Doc0006 1108095Document26 pagesDoc0006 1108095ChrisNo ratings yet

- Fast Read Access Time - 150 Ns - AutomaticDocument27 pagesFast Read Access Time - 150 Ns - Automaticthanhhai7622No ratings yet

- 4-Mbit (256K × 16) Static RAM: Features Functional DescriptionDocument17 pages4-Mbit (256K × 16) Static RAM: Features Functional DescriptionEduardo Brayan Melchor BricenoNo ratings yet

- 128K X 8 Low Power Cmos Static Ram: Description FeaturesDocument11 pages128K X 8 Low Power Cmos Static Ram: Description Featuresvanhuong87No ratings yet

- AT28C010 ATMELCorporationDocument17 pagesAT28C010 ATMELCorporationShaun Van HeerdenNo ratings yet

- Neo Geo Architecture: Architecture of Consoles: A Practical Analysis, #23From EverandNeo Geo Architecture: Architecture of Consoles: A Practical Analysis, #23No ratings yet

- Obsolete: Ad1854 Stereo, 96 KHZ, MultibitDocument12 pagesObsolete: Ad1854 Stereo, 96 KHZ, MultibitAnh ĐườngNo ratings yet

- Service Manual: IndexDocument29 pagesService Manual: IndexAnh ĐườngNo ratings yet

- IR6210 Intelligent High Side Mosfet Power Switch: Features Product SummaryDocument6 pagesIR6210 Intelligent High Side Mosfet Power Switch: Features Product SummaryAnh ĐườngNo ratings yet

- TPS54331 3-A, 28-V Input, Step Down DC-DC Converter With Eco-Mode™Document39 pagesTPS54331 3-A, 28-V Input, Step Down DC-DC Converter With Eco-Mode™Anh ĐườngNo ratings yet

- Stm8S007C8: Value Line, 24 MHZ Stm8S 8-Bit Mcu, 64 Kbytes Flash, True Data Eeprom, 10-Bit Adc, Timers, 2 Uarts, Spi, I CDocument93 pagesStm8S007C8: Value Line, 24 MHZ Stm8S 8-Bit Mcu, 64 Kbytes Flash, True Data Eeprom, 10-Bit Adc, Timers, 2 Uarts, Spi, I CAnh ĐườngNo ratings yet

- FlashcatUSB ManualDocument39 pagesFlashcatUSB ManualAnh ĐườngNo ratings yet

- BS62LV1025: Very Low Power/Voltage CMOS SRAM 128K X 8 BitDocument10 pagesBS62LV1025: Very Low Power/Voltage CMOS SRAM 128K X 8 BitAnh ĐườngNo ratings yet

- Sony.: Television ReleviseurDocument67 pagesSony.: Television ReleviseurAnh ĐườngNo ratings yet

- MBM29PL12LM: 128 M (16M 8/8M 16) BitDocument73 pagesMBM29PL12LM: 128 M (16M 8/8M 16) BitAnh ĐườngNo ratings yet

- Thermal Protection: MZ 6 - 101R T100 ADocument1 pageThermal Protection: MZ 6 - 101R T100 AAnh ĐườngNo ratings yet

- Enhanced Dual Bit 20bit ADC: General DescriptionDocument20 pagesEnhanced Dual Bit 20bit ADC: General DescriptionAnh ĐườngNo ratings yet

- Pa1000 User Manual v15 EDocument1,080 pagesPa1000 User Manual v15 EAnh ĐườngNo ratings yet

- ULN2801A, ULN2802A, ULN2803A, ULN2804A: DescriptionDocument14 pagesULN2801A, ULN2802A, ULN2803A, ULN2804A: DescriptionAnh ĐườngNo ratings yet

- Service Manual: PSR-S550 PSR-S550BDocument69 pagesService Manual: PSR-S550 PSR-S550BAnh ĐườngNo ratings yet

- Document 1674024.1 Oracle E-Business SQL Trace and TKPROF GuideDocument27 pagesDocument 1674024.1 Oracle E-Business SQL Trace and TKPROF GuideDarwin SusantoNo ratings yet

- x-86 FamilyDocument14 pagesx-86 FamilyPrince VegetaNo ratings yet

- Learner Resource ICTNWK509Document56 pagesLearner Resource ICTNWK509manpreet kaurNo ratings yet

- WORKSHEET 1 (Chapter 1,2 & 3)Document55 pagesWORKSHEET 1 (Chapter 1,2 & 3)Bolt FFNo ratings yet

- Technical Paper Abdmr Final123Document5 pagesTechnical Paper Abdmr Final123anirudhaNo ratings yet

- 15A04601 Microprocessors & MicrocontrollersDocument1 page15A04601 Microprocessors & Microcontrollers17BF1A04L7 kalyanNo ratings yet

- A10 5.1.0 AdpDocument94 pagesA10 5.1.0 Adp李潇No ratings yet

- 10.1 10. Ansible RolesDocument11 pages10.1 10. Ansible RolesAbdoulaye Andillo MahamadouNo ratings yet

- Maze Generation AlgorithmDocument3 pagesMaze Generation AlgorithmMeiki MUNo ratings yet

- H3C UniServer R4900 G3 Rack Server DatasheetDocument4 pagesH3C UniServer R4900 G3 Rack Server Datasheetdavid.gtaNo ratings yet

- BPN Sas3 216elDocument28 pagesBPN Sas3 216elANo ratings yet

- Problem With SolutionDocument100 pagesProblem With SolutionTom KnobNo ratings yet

- Chapter 2 Creating and Editing Screens: 2.1 Scredit (Screen Editor) SetupDocument4 pagesChapter 2 Creating and Editing Screens: 2.1 Scredit (Screen Editor) SetupryoNo ratings yet

- String Manipulation FunctionsDocument11 pagesString Manipulation Functionsblessie balagtasNo ratings yet

- 5-Port 10/100/1000T VPN Security Router: HardwareDocument5 pages5-Port 10/100/1000T VPN Security Router: HardwareGuy PoakaNo ratings yet

- Sortly Sortly Pro Is A Super Simple Inventory App That Enables You To VisuallyDocument9 pagesSortly Sortly Pro Is A Super Simple Inventory App That Enables You To VisuallyMike AntolinoNo ratings yet

- Module 5 - Pentium Processors - FinalDocument43 pagesModule 5 - Pentium Processors - FinalKEVINNo ratings yet

- Home Automation Literature ReviewDocument7 pagesHome Automation Literature Reviewea7gjrm5100% (1)

- Bresenham'S Ellipse Drawing Algorithm: / REGION 1Document3 pagesBresenham'S Ellipse Drawing Algorithm: / REGION 1Karthik KeyanNo ratings yet

- Docu88911 PowerMax and VMAX 9.0 Events and Alerts User GuideDocument166 pagesDocu88911 PowerMax and VMAX 9.0 Events and Alerts User GuideHamid Reza AhmadpourNo ratings yet

- Text File NotesDocument25 pagesText File Notesrandomotaku780No ratings yet

- Advanced View Arduino Projects List - Use Arduino For ProjectsDocument49 pagesAdvanced View Arduino Projects List - Use Arduino For ProjectsBilal AfzalNo ratings yet

- Philips-1547963414-Ppa5650 000 PssDocument2 pagesPhilips-1547963414-Ppa5650 000 PssDavid SamveljanNo ratings yet

- 2011 Access Control Software User Manual1Document29 pages2011 Access Control Software User Manual1Javier Perez TitoNo ratings yet

- Linked ListDocument104 pagesLinked ListMadhur.Mahajan Btech2021No ratings yet

- R2RDocument2 pagesR2RWilson JhNo ratings yet

- Azure Repos DocumentationDocument838 pagesAzure Repos DocumentationLagerström EmpreendimentosNo ratings yet