Professional Documents

Culture Documents

DSD Syllabus - Calicut University

DSD Syllabus - Calicut University

Uploaded by

iammanuprasadCopyright:

Available Formats

You might also like

- Institute of Aeronautical Engineering: Mid Semester TestDocument8 pagesInstitute of Aeronautical Engineering: Mid Semester TestNaresh BopparathiNo ratings yet

- CS202 Computer Organisation and Architecture KTU S4 SyllabusDocument3 pagesCS202 Computer Organisation and Architecture KTU S4 SyllabusRishabh100% (1)

- Ece 2003Document3 pagesEce 2003gokulNo ratings yet

- MG Btech 3rd Sem Cs SyllabusDocument44 pagesMG Btech 3rd Sem Cs SyllabusJinu MadhavanNo ratings yet

- CS202 Computer Organisation and ArchitectureDocument3 pagesCS202 Computer Organisation and ArchitectureGokul Krishna MNo ratings yet

- Kannur University BTech.S7 CS SyllabusDocument17 pagesKannur University BTech.S7 CS SyllabusManu K MNo ratings yet

- s8 Syllabus CSE 2008 SchemeDocument9 pagess8 Syllabus CSE 2008 SchemeAbhilash NairNo ratings yet

- FALLSEM2022-23 BECE102L TH VL2022230104438 Reference Material I 21-07-2022 BECE102LDocument3 pagesFALLSEM2022-23 BECE102L TH VL2022230104438 Reference Material I 21-07-2022 BECE102LUrjoshi AichNo ratings yet

- Minor 2 Digital EDA Tools SyllabusDocument2 pagesMinor 2 Digital EDA Tools SyllabusGennyNo ratings yet

- Introduction To DLDDocument23 pagesIntroduction To DLDDaniaNo ratings yet

- Lecture 1: Introduction: CS-216: Digital Logic DesignDocument23 pagesLecture 1: Introduction: CS-216: Digital Logic DesignDaniaNo ratings yet

- Cse2001 Computer-Architecture-And-Organization TH 1.0 37 Cse2001Document2 pagesCse2001 Computer-Architecture-And-Organization TH 1.0 37 Cse2001devipriyaNo ratings yet

- EE 421-Digital System Design-Dr. Shahid Masud-Updated PDFDocument4 pagesEE 421-Digital System Design-Dr. Shahid Masud-Updated PDFUbaid UmarNo ratings yet

- Eee4024 Computer-Architecture-And-Organization TH 1.0 37 Eee4024Document3 pagesEee4024 Computer-Architecture-And-Organization TH 1.0 37 Eee4024Anbarasan SubramaniyanNo ratings yet

- Kerala University s8 Syllabus 2008 SchemeDocument29 pagesKerala University s8 Syllabus 2008 SchemeJijo PJNo ratings yet

- Course DescriptionDocument8 pagesCourse DescriptionKiranKumarNo ratings yet

- ADSD SyllabusDocument2 pagesADSD SyllabuswroxtarNo ratings yet

- Regulations - 2009: Affiliated Institutions Anna University, ChennaiDocument44 pagesRegulations - 2009: Affiliated Institutions Anna University, ChennaiThenmozhi RavichandranNo ratings yet

- CS 4th Semester SyllabusDocument13 pagesCS 4th Semester SyllabusManish KumarNo ratings yet

- Mca Calicut 4 To 6 SemesterDocument26 pagesMca Calicut 4 To 6 SemesterJinu MadhavanNo ratings yet

- Eee646 Fpga-based-system-Design Ela 2.00 Ac29Document2 pagesEee646 Fpga-based-system-Design Ela 2.00 Ac29Ranjith M KumarNo ratings yet

- B.Sc. Computer Science 2004-2005Document32 pagesB.Sc. Computer Science 2004-2005vimalnandiNo ratings yet

- B.sc.I Computer ScienceDocument9 pagesB.sc.I Computer SciencePreet SainiNo ratings yet

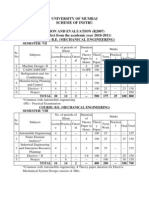

- BE Mechanical-Mumbai UniversityDocument82 pagesBE Mechanical-Mumbai UniversityJayesh NavareNo ratings yet

- ME VLSI SyllabusDocument33 pagesME VLSI Syllabusps0208No ratings yet

- ECE419 Digital Vlsi Design 16937::tapsi Singh 3.0 1.0 0.0 4.0 Courses With Numerical and Conceptual FocusDocument8 pagesECE419 Digital Vlsi Design 16937::tapsi Singh 3.0 1.0 0.0 4.0 Courses With Numerical and Conceptual FocusanakshaNo ratings yet

- Kannur University BTech CS VIII Sem. Syllabus.Document16 pagesKannur University BTech CS VIII Sem. Syllabus.Manu K MNo ratings yet

- s7 MG University Computer Science SyllabusDocument16 pagess7 MG University Computer Science SyllabusaryamenonNo ratings yet

- Master of Computer ApplicationsDocument35 pagesMaster of Computer ApplicationsRahul KumarNo ratings yet

- EEDG/CE 6301: Advanced Digital Logic: Mehrdad NouraniDocument44 pagesEEDG/CE 6301: Advanced Digital Logic: Mehrdad NouraniGowtham HariNo ratings yet

- Cse Iitkgp Ac in Oldlook Syllabus HTMLDocument65 pagesCse Iitkgp Ac in Oldlook Syllabus HTMLvidyasagarNo ratings yet

- Vit Ece 5th Year SyllabusDocument16 pagesVit Ece 5th Year Syllabuspranavateja12399No ratings yet

- Bharathidasan University, Tiruchirappalli - 620 024. Master of Computer Application (M.C.A) - Course Structure Under CBCSDocument54 pagesBharathidasan University, Tiruchirappalli - 620 024. Master of Computer Application (M.C.A) - Course Structure Under CBCSB. Srini VasanNo ratings yet

- Sub1 1 Theory IC Design Flow NguyenHungQuan 201309Document52 pagesSub1 1 Theory IC Design Flow NguyenHungQuan 201309Nguyễn Văn HảoNo ratings yet

- CST202 - Ktu QbankDocument12 pagesCST202 - Ktu QbankYaseen 777No ratings yet

- It Syllabus 2010 Sem 4Document12 pagesIt Syllabus 2010 Sem 4Shibin MathewNo ratings yet

- Final Updated New Syllabus Mtech BPUT 2009-10 VLSI Embeded System DesignDocument11 pagesFinal Updated New Syllabus Mtech BPUT 2009-10 VLSI Embeded System Designarunbinay04No ratings yet

- 7 Ths em Comp ScienceDocument28 pages7 Ths em Comp SciencePrachiChoudharyNo ratings yet

- MCADocument39 pagesMCAidealajayNo ratings yet

- Scheme of Examination For Master of Computer APPLICATIONS (M.C.A.) W.E.F. Academic Session 2014-15Document11 pagesScheme of Examination For Master of Computer APPLICATIONS (M.C.A.) W.E.F. Academic Session 2014-15Siddharth JainNo ratings yet

- UntitledDocument12 pagesUntitledSathiyaraj MurugarajNo ratings yet

- Cs 227 DLD Nceac SPR 19Document5 pagesCs 227 DLD Nceac SPR 19i201757 Khawaja Razzi Ul IslamNo ratings yet

- EENG115-InFE115 Course Description - 5Document3 pagesEENG115-InFE115 Course Description - 5Mohammad Al MestiraihiNo ratings yet

- Analog and Digital ElectronicsDocument19 pagesAnalog and Digital ElectronicsRuthwik S GowdaNo ratings yet

- Cs010 702: Compiler Construction: Teaching Scheme Credits: 4 2 Hours Lecture and 2 Hours Tutorial Per WeekDocument2 pagesCs010 702: Compiler Construction: Teaching Scheme Credits: 4 2 Hours Lecture and 2 Hours Tutorial Per WeeklijoNo ratings yet

- EET 3350 Digital Systems DesignDocument4 pagesEET 3350 Digital Systems DesignM Lukman HakimNo ratings yet

- DSD Course outlineDocument3 pagesDSD Course outlinepurushotham.kNo ratings yet

- Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDLFrom EverandIntroduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDLNo ratings yet

- Object –Oriented Analysis and Design Using UMLFrom EverandObject –Oriented Analysis and Design Using UMLRating: 5 out of 5 stars5/5 (1)

- Models and Analysis for Distributed SystemsFrom EverandModels and Analysis for Distributed SystemsSerge HaddadNo ratings yet

- Digital Logic Test Questions For InterviewDocument53 pagesDigital Logic Test Questions For InterviewDwaraka OrugantiNo ratings yet

- Textbook: Digital Design, 6 - Edition: M. Morris Mano and Michael D. CilettiDocument74 pagesTextbook: Digital Design, 6 - Edition: M. Morris Mano and Michael D. Ciletti林愷威No ratings yet

- ECE-E434 Digital ElectronicsDocument15 pagesECE-E434 Digital ElectronicsPhuoc VuNo ratings yet

- KNL 1253 Digital Electronics: CountersDocument44 pagesKNL 1253 Digital Electronics: CountersjuzsuicideNo ratings yet

- Chapter 8-Differential and Multistage AmplifiersDocument85 pagesChapter 8-Differential and Multistage Amplifiersf94106070No ratings yet

- Home AutomationDocument27 pagesHome AutomationK.anirudh SinghNo ratings yet

- KDI 572-573-574 Mant. ManualDocument164 pagesKDI 572-573-574 Mant. ManualmglemNo ratings yet

- 5 A 0105 EE486 DigitalDocument1 page5 A 0105 EE486 DigitalNagarjuna MalladhiNo ratings yet

- Chapter 11 - 15Document230 pagesChapter 11 - 15pradeep bhardwajNo ratings yet

- Atmel 7810 Automotive Microcontrollers ATmega328P - DatasheetDocument298 pagesAtmel 7810 Automotive Microcontrollers ATmega328P - Datasheetmiguel quisbertNo ratings yet

- 16/32 BIT Microcontroller: TLCS-900Document68 pages16/32 BIT Microcontroller: TLCS-900Cesar SaucedoNo ratings yet

- Flash MemoriesDocument52 pagesFlash MemoriesJeff GicharuNo ratings yet

- RTL Design Verification Engineer in Austin TX Resume Sumaira KhowajaDocument3 pagesRTL Design Verification Engineer in Austin TX Resume Sumaira KhowajaSumairaKhowaja3No ratings yet

- MOTHERBOARDDocument17 pagesMOTHERBOARDANAND100% (2)

- List of 7400 Series Integrated Circuits PDFDocument22 pagesList of 7400 Series Integrated Circuits PDFduriiNo ratings yet

- Flip Flop and LatchDocument7 pagesFlip Flop and LatchAnn RazonNo ratings yet

- Piksi Schematics v2.3.1Document7 pagesPiksi Schematics v2.3.1Danut StanciuNo ratings yet

- MNDCS-2024 New3 - 231101 - 003728Document3 pagesMNDCS-2024 New3 - 231101 - 003728Dr. Farida Ashraf AliNo ratings yet

- MC14014B, MC14021B 8 Bit Static Shift Register: Marking DiagramsDocument8 pagesMC14014B, MC14021B 8 Bit Static Shift Register: Marking Diagramsdaniel ortegaNo ratings yet

- Advanced VLSI Design Lab (EC17203) : Experiment No. 7Document4 pagesAdvanced VLSI Design Lab (EC17203) : Experiment No. 7Huzaifa AhmedNo ratings yet

- Computer RamDocument3 pagesComputer RamTech RecipeNo ratings yet

- Arduino Uno r3Document9 pagesArduino Uno r3Danies Forensky IrawanNo ratings yet

- ASIC Design Flow How To Design Your Own Chip: Frank K. G UrkaynakDocument77 pagesASIC Design Flow How To Design Your Own Chip: Frank K. G UrkaynakpdnoobNo ratings yet

- Ch5 - Basic Computer Organization and DesignDocument44 pagesCh5 - Basic Computer Organization and DesignGagan ChandelNo ratings yet

- Jntu Vlsi Systems DesignDocument5 pagesJntu Vlsi Systems Design9010469071No ratings yet

- Lesson 1 - Evolution of Microprocessor PDFDocument59 pagesLesson 1 - Evolution of Microprocessor PDFFrancis del RosarioNo ratings yet

- Basic Engineering Circuit Analysis 10thDocument185 pagesBasic Engineering Circuit Analysis 10thdiogo millnitzNo ratings yet

- CoE111 2009outlineDocument2 pagesCoE111 2009outlineJohn Keithley DifuntorumNo ratings yet

- DG Lab - 2019-20 PDFDocument61 pagesDG Lab - 2019-20 PDFGopinathan MNo ratings yet

- Digital Electronics Multiple Choice Questions 3Document7 pagesDigital Electronics Multiple Choice Questions 3nirishkumar50% (4)

DSD Syllabus - Calicut University

DSD Syllabus - Calicut University

Uploaded by

iammanuprasadOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DSD Syllabus - Calicut University

DSD Syllabus - Calicut University

Uploaded by

iammanuprasadCopyright:

Available Formats

EE09 505: DIGITAL SYSTEM DESIGN

Teaching scheme Credits: 4

3 hours lecture and 1 hour tutorial per week

Objectives

· To make students able to design and build real digital circuits

· To make students able to do VHDL programming

Module I (14 hours)

Hardware description languages-HDL based digital design-VHDL hardware description

language- Program structure-Types, constants and arrays-Functions and procedures libraries

and packages-structural design elements-data flow design elements- behavioural design

elements-time dimension-simulation –test benches-VHDL features for sequential logic design.

Module II (13 hours)

Combinational logic design-analysis procedure-design procedure-documentation-block

diagram-gate symbols-signal names and active levels-bubble-to- bubble logic design-signal

namings in HDL programs-schematic structures. Circuit timing- timing diagrams propagation

delay- timing specifications. Design using VHDL-decoders-encoders-tri state devices-

multiplexer-parity generators comparators- adders- subtractors and ALUs –combinational

multiplexers.

Module III (13 hours)

Sequential logic design-clocked synchronous state machine analysis-state machine structure-

output logic-characteristic equations-state table-state equations-state diagram Flip-Flop input

equations-Analysis of state machines with D Flip-Flops, JK Flip-Flops. Synchronous state

machine design- state table design example- state minimisation- state assignment- synthesis

using D and JK Flip-Flops- Clocked sequential circuit design using VHDL- state machine

design-state assignment-pipelined outputs.

Module IV (14 hours)

Feedback sequential circuit-basic analysis-analysing circuits with multiple feedback

loopsraces- state tables and flow tables Design of feedback sequential circuits-latches-

designing fundamental-mode flow tables flow table minimisation-race-free state assignment-

excitation equations-design using VHDL. Algorithmic state machine-introduction-components

of ASM chart-salient features examples. Complex programmable logic devices and FPGAs-

Xilinx XC 9500 CPLD family-function block architecture- nput output block architecture-

switch matrix. FPGAs-Xilinx XC4000 FPGA family-configurable logic block-input output

block programmable interconnect.

Text Books

1. John F Wakerly, Digital Design, Pearson Education, Delhi, 2002

2. Morris Mano,Digital Design, Pearson Education, Delhi, 2002

3. A Anandakumar, Digital Electronics,Prentice Hall India Feb 2009.(Module IV)

Reference Books

1. Ian Grout, Digital Systems Design with FPGAs,Elsevier.

2. Volnei A Pedroni Digital Electronics and Design with VHDL,Elsevier

3. R Padmanabhan, B Bala Tripura Sundari, Design through Verilog HDL,Wiley India

4. David Money Harris and Sarah L Harris, Digital Design and Computer Archiecture,

Elsevier

5. James R Armstrong, F Gail Gray, VHDL Design/Representation and Synthesis, Pearson

Education, Delhi, 2002

6. Charles S. Roth, Fundamentals of Logic Design, Jaico Publishing House, 1999

7. Stephen Brown and Zvonoko Vranesic, Fundamentals of Digital Logic with VHDL Design,

McGraw Hill

8. B.Holdsworth, R.C Woods, Digital Logic Design, Newnes, Elsevier

9. Mohammad A. Karim, Xinghao Chen, Digital Design. Basic Concepts and Principles

Internal Continuous Assessment (Maximum Marks-30)

60% - Tests (minimum 2)

30% - Assignments (minimum 2) such as home work, problem solving, group discussions,

quiz, literature survey, seminar, term-project, software exercises, etc.

10% - Regularity in the class

University Examination Pattern

PART A: Short answer questions (one/two sentences) 5 x 2 marks=10 marks

All questions are compulsory. There should be at least one question from each

Module and not more than two questions from any Module.

PART B: Analytical/Problem solving questions 4 x 5 marks=20 marks

Candidates have to answer four questions out of six. There should be at least one

question from each Module and not more than two questions from any Module.

PART C: Descriptive/Analytical/Problem solving questions 4 x 10 marks=40

Two questions from each Module with choice to answer one question.

Maximum Total Marks: 70

You might also like

- Institute of Aeronautical Engineering: Mid Semester TestDocument8 pagesInstitute of Aeronautical Engineering: Mid Semester TestNaresh BopparathiNo ratings yet

- CS202 Computer Organisation and Architecture KTU S4 SyllabusDocument3 pagesCS202 Computer Organisation and Architecture KTU S4 SyllabusRishabh100% (1)

- Ece 2003Document3 pagesEce 2003gokulNo ratings yet

- MG Btech 3rd Sem Cs SyllabusDocument44 pagesMG Btech 3rd Sem Cs SyllabusJinu MadhavanNo ratings yet

- CS202 Computer Organisation and ArchitectureDocument3 pagesCS202 Computer Organisation and ArchitectureGokul Krishna MNo ratings yet

- Kannur University BTech.S7 CS SyllabusDocument17 pagesKannur University BTech.S7 CS SyllabusManu K MNo ratings yet

- s8 Syllabus CSE 2008 SchemeDocument9 pagess8 Syllabus CSE 2008 SchemeAbhilash NairNo ratings yet

- FALLSEM2022-23 BECE102L TH VL2022230104438 Reference Material I 21-07-2022 BECE102LDocument3 pagesFALLSEM2022-23 BECE102L TH VL2022230104438 Reference Material I 21-07-2022 BECE102LUrjoshi AichNo ratings yet

- Minor 2 Digital EDA Tools SyllabusDocument2 pagesMinor 2 Digital EDA Tools SyllabusGennyNo ratings yet

- Introduction To DLDDocument23 pagesIntroduction To DLDDaniaNo ratings yet

- Lecture 1: Introduction: CS-216: Digital Logic DesignDocument23 pagesLecture 1: Introduction: CS-216: Digital Logic DesignDaniaNo ratings yet

- Cse2001 Computer-Architecture-And-Organization TH 1.0 37 Cse2001Document2 pagesCse2001 Computer-Architecture-And-Organization TH 1.0 37 Cse2001devipriyaNo ratings yet

- EE 421-Digital System Design-Dr. Shahid Masud-Updated PDFDocument4 pagesEE 421-Digital System Design-Dr. Shahid Masud-Updated PDFUbaid UmarNo ratings yet

- Eee4024 Computer-Architecture-And-Organization TH 1.0 37 Eee4024Document3 pagesEee4024 Computer-Architecture-And-Organization TH 1.0 37 Eee4024Anbarasan SubramaniyanNo ratings yet

- Kerala University s8 Syllabus 2008 SchemeDocument29 pagesKerala University s8 Syllabus 2008 SchemeJijo PJNo ratings yet

- Course DescriptionDocument8 pagesCourse DescriptionKiranKumarNo ratings yet

- ADSD SyllabusDocument2 pagesADSD SyllabuswroxtarNo ratings yet

- Regulations - 2009: Affiliated Institutions Anna University, ChennaiDocument44 pagesRegulations - 2009: Affiliated Institutions Anna University, ChennaiThenmozhi RavichandranNo ratings yet

- CS 4th Semester SyllabusDocument13 pagesCS 4th Semester SyllabusManish KumarNo ratings yet

- Mca Calicut 4 To 6 SemesterDocument26 pagesMca Calicut 4 To 6 SemesterJinu MadhavanNo ratings yet

- Eee646 Fpga-based-system-Design Ela 2.00 Ac29Document2 pagesEee646 Fpga-based-system-Design Ela 2.00 Ac29Ranjith M KumarNo ratings yet

- B.Sc. Computer Science 2004-2005Document32 pagesB.Sc. Computer Science 2004-2005vimalnandiNo ratings yet

- B.sc.I Computer ScienceDocument9 pagesB.sc.I Computer SciencePreet SainiNo ratings yet

- BE Mechanical-Mumbai UniversityDocument82 pagesBE Mechanical-Mumbai UniversityJayesh NavareNo ratings yet

- ME VLSI SyllabusDocument33 pagesME VLSI Syllabusps0208No ratings yet

- ECE419 Digital Vlsi Design 16937::tapsi Singh 3.0 1.0 0.0 4.0 Courses With Numerical and Conceptual FocusDocument8 pagesECE419 Digital Vlsi Design 16937::tapsi Singh 3.0 1.0 0.0 4.0 Courses With Numerical and Conceptual FocusanakshaNo ratings yet

- Kannur University BTech CS VIII Sem. Syllabus.Document16 pagesKannur University BTech CS VIII Sem. Syllabus.Manu K MNo ratings yet

- s7 MG University Computer Science SyllabusDocument16 pagess7 MG University Computer Science SyllabusaryamenonNo ratings yet

- Master of Computer ApplicationsDocument35 pagesMaster of Computer ApplicationsRahul KumarNo ratings yet

- EEDG/CE 6301: Advanced Digital Logic: Mehrdad NouraniDocument44 pagesEEDG/CE 6301: Advanced Digital Logic: Mehrdad NouraniGowtham HariNo ratings yet

- Cse Iitkgp Ac in Oldlook Syllabus HTMLDocument65 pagesCse Iitkgp Ac in Oldlook Syllabus HTMLvidyasagarNo ratings yet

- Vit Ece 5th Year SyllabusDocument16 pagesVit Ece 5th Year Syllabuspranavateja12399No ratings yet

- Bharathidasan University, Tiruchirappalli - 620 024. Master of Computer Application (M.C.A) - Course Structure Under CBCSDocument54 pagesBharathidasan University, Tiruchirappalli - 620 024. Master of Computer Application (M.C.A) - Course Structure Under CBCSB. Srini VasanNo ratings yet

- Sub1 1 Theory IC Design Flow NguyenHungQuan 201309Document52 pagesSub1 1 Theory IC Design Flow NguyenHungQuan 201309Nguyễn Văn HảoNo ratings yet

- CST202 - Ktu QbankDocument12 pagesCST202 - Ktu QbankYaseen 777No ratings yet

- It Syllabus 2010 Sem 4Document12 pagesIt Syllabus 2010 Sem 4Shibin MathewNo ratings yet

- Final Updated New Syllabus Mtech BPUT 2009-10 VLSI Embeded System DesignDocument11 pagesFinal Updated New Syllabus Mtech BPUT 2009-10 VLSI Embeded System Designarunbinay04No ratings yet

- 7 Ths em Comp ScienceDocument28 pages7 Ths em Comp SciencePrachiChoudharyNo ratings yet

- MCADocument39 pagesMCAidealajayNo ratings yet

- Scheme of Examination For Master of Computer APPLICATIONS (M.C.A.) W.E.F. Academic Session 2014-15Document11 pagesScheme of Examination For Master of Computer APPLICATIONS (M.C.A.) W.E.F. Academic Session 2014-15Siddharth JainNo ratings yet

- UntitledDocument12 pagesUntitledSathiyaraj MurugarajNo ratings yet

- Cs 227 DLD Nceac SPR 19Document5 pagesCs 227 DLD Nceac SPR 19i201757 Khawaja Razzi Ul IslamNo ratings yet

- EENG115-InFE115 Course Description - 5Document3 pagesEENG115-InFE115 Course Description - 5Mohammad Al MestiraihiNo ratings yet

- Analog and Digital ElectronicsDocument19 pagesAnalog and Digital ElectronicsRuthwik S GowdaNo ratings yet

- Cs010 702: Compiler Construction: Teaching Scheme Credits: 4 2 Hours Lecture and 2 Hours Tutorial Per WeekDocument2 pagesCs010 702: Compiler Construction: Teaching Scheme Credits: 4 2 Hours Lecture and 2 Hours Tutorial Per WeeklijoNo ratings yet

- EET 3350 Digital Systems DesignDocument4 pagesEET 3350 Digital Systems DesignM Lukman HakimNo ratings yet

- DSD Course outlineDocument3 pagesDSD Course outlinepurushotham.kNo ratings yet

- Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDLFrom EverandIntroduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDLNo ratings yet

- Object –Oriented Analysis and Design Using UMLFrom EverandObject –Oriented Analysis and Design Using UMLRating: 5 out of 5 stars5/5 (1)

- Models and Analysis for Distributed SystemsFrom EverandModels and Analysis for Distributed SystemsSerge HaddadNo ratings yet

- Digital Logic Test Questions For InterviewDocument53 pagesDigital Logic Test Questions For InterviewDwaraka OrugantiNo ratings yet

- Textbook: Digital Design, 6 - Edition: M. Morris Mano and Michael D. CilettiDocument74 pagesTextbook: Digital Design, 6 - Edition: M. Morris Mano and Michael D. Ciletti林愷威No ratings yet

- ECE-E434 Digital ElectronicsDocument15 pagesECE-E434 Digital ElectronicsPhuoc VuNo ratings yet

- KNL 1253 Digital Electronics: CountersDocument44 pagesKNL 1253 Digital Electronics: CountersjuzsuicideNo ratings yet

- Chapter 8-Differential and Multistage AmplifiersDocument85 pagesChapter 8-Differential and Multistage Amplifiersf94106070No ratings yet

- Home AutomationDocument27 pagesHome AutomationK.anirudh SinghNo ratings yet

- KDI 572-573-574 Mant. ManualDocument164 pagesKDI 572-573-574 Mant. ManualmglemNo ratings yet

- 5 A 0105 EE486 DigitalDocument1 page5 A 0105 EE486 DigitalNagarjuna MalladhiNo ratings yet

- Chapter 11 - 15Document230 pagesChapter 11 - 15pradeep bhardwajNo ratings yet

- Atmel 7810 Automotive Microcontrollers ATmega328P - DatasheetDocument298 pagesAtmel 7810 Automotive Microcontrollers ATmega328P - Datasheetmiguel quisbertNo ratings yet

- 16/32 BIT Microcontroller: TLCS-900Document68 pages16/32 BIT Microcontroller: TLCS-900Cesar SaucedoNo ratings yet

- Flash MemoriesDocument52 pagesFlash MemoriesJeff GicharuNo ratings yet

- RTL Design Verification Engineer in Austin TX Resume Sumaira KhowajaDocument3 pagesRTL Design Verification Engineer in Austin TX Resume Sumaira KhowajaSumairaKhowaja3No ratings yet

- MOTHERBOARDDocument17 pagesMOTHERBOARDANAND100% (2)

- List of 7400 Series Integrated Circuits PDFDocument22 pagesList of 7400 Series Integrated Circuits PDFduriiNo ratings yet

- Flip Flop and LatchDocument7 pagesFlip Flop and LatchAnn RazonNo ratings yet

- Piksi Schematics v2.3.1Document7 pagesPiksi Schematics v2.3.1Danut StanciuNo ratings yet

- MNDCS-2024 New3 - 231101 - 003728Document3 pagesMNDCS-2024 New3 - 231101 - 003728Dr. Farida Ashraf AliNo ratings yet

- MC14014B, MC14021B 8 Bit Static Shift Register: Marking DiagramsDocument8 pagesMC14014B, MC14021B 8 Bit Static Shift Register: Marking Diagramsdaniel ortegaNo ratings yet

- Advanced VLSI Design Lab (EC17203) : Experiment No. 7Document4 pagesAdvanced VLSI Design Lab (EC17203) : Experiment No. 7Huzaifa AhmedNo ratings yet

- Computer RamDocument3 pagesComputer RamTech RecipeNo ratings yet

- Arduino Uno r3Document9 pagesArduino Uno r3Danies Forensky IrawanNo ratings yet

- ASIC Design Flow How To Design Your Own Chip: Frank K. G UrkaynakDocument77 pagesASIC Design Flow How To Design Your Own Chip: Frank K. G UrkaynakpdnoobNo ratings yet

- Ch5 - Basic Computer Organization and DesignDocument44 pagesCh5 - Basic Computer Organization and DesignGagan ChandelNo ratings yet

- Jntu Vlsi Systems DesignDocument5 pagesJntu Vlsi Systems Design9010469071No ratings yet

- Lesson 1 - Evolution of Microprocessor PDFDocument59 pagesLesson 1 - Evolution of Microprocessor PDFFrancis del RosarioNo ratings yet

- Basic Engineering Circuit Analysis 10thDocument185 pagesBasic Engineering Circuit Analysis 10thdiogo millnitzNo ratings yet

- CoE111 2009outlineDocument2 pagesCoE111 2009outlineJohn Keithley DifuntorumNo ratings yet

- DG Lab - 2019-20 PDFDocument61 pagesDG Lab - 2019-20 PDFGopinathan MNo ratings yet

- Digital Electronics Multiple Choice Questions 3Document7 pagesDigital Electronics Multiple Choice Questions 3nirishkumar50% (4)