Professional Documents

Culture Documents

EECS240 - Spring 2008 Comparator Gain-Bandwidth: Lecture 20: Comparators

EECS240 - Spring 2008 Comparator Gain-Bandwidth: Lecture 20: Comparators

Uploaded by

nadeemjuttCopyright:

Available Formats

You might also like

- Procreate Pocketbook PDFDocument69 pagesProcreate Pocketbook PDFhadydevcont100% (3)

- Questions & Answers On Transmission LinesDocument43 pagesQuestions & Answers On Transmission Lineskibrom atsbha100% (3)

- EE247 Lecture 20Document30 pagesEE247 Lecture 20maqadarNo ratings yet

- MRF393Document4 pagesMRF393andreasmonNo ratings yet

- BCV27Document6 pagesBCV27RaduNo ratings yet

- Irgb 4062 DPBFDocument13 pagesIrgb 4062 DPBFCarlos OliveiraNo ratings yet

- EECS240 - Spring 2009 Speed of Light: Both Send Info Back and ForthDocument3 pagesEECS240 - Spring 2009 Speed of Light: Both Send Info Back and ForthnadeemjuttNo ratings yet

- High Frequency Amplifier Applications FM, RF, MIX, IF Amplifier ApplicationsDocument7 pagesHigh Frequency Amplifier Applications FM, RF, MIX, IF Amplifier ApplicationsJose VelasquezNo ratings yet

- 2SC3950Document2 pages2SC3950mroocx1000No ratings yet

- IRGIB10B60KD1: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodeDocument12 pagesIRGIB10B60KD1: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodeSmain BendeddoucheNo ratings yet

- DatasheetDocument5 pagesDatasheetQoons CelavegnaNo ratings yet

- FM, RF, MIX, IF Amplifier, High-Frequency General-Purpose Amplifier ApplicationsDocument3 pagesFM, RF, MIX, IF Amplifier, High-Frequency General-Purpose Amplifier ApplicationsSahil SakatNo ratings yet

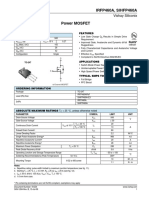

- Irfp460A, Sihfp460A: Vishay SiliconixDocument11 pagesIrfp460A, Sihfp460A: Vishay SiliconixАлексей АндрияшNo ratings yet

- Vishay IRFP460APBF Datasheet PDFDocument8 pagesVishay IRFP460APBF Datasheet PDFkamel keddarNo ratings yet

- 2 S 1Document8 pages2 S 1Nelson Naval CabingasNo ratings yet

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDocument3 pagesSilicon NPN Power Transistors: Savantic Semiconductor Product SpecificationVitorio LogoNo ratings yet

- C3675-Sanyo Semicon DeviceDocument3 pagesC3675-Sanyo Semicon DeviceMa LhNo ratings yet

- Irgp 4066Document10 pagesIrgp 4066rennybenitezNo ratings yet

- Driver-Stage Audio Amplifier Applications High-Voltage Switching ApplicationsDocument4 pagesDriver-Stage Audio Amplifier Applications High-Voltage Switching ApplicationsMichael KovalNo ratings yet

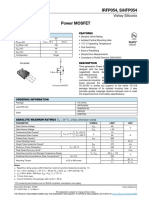

- Irfbc40, Sihfbc40: Vishay SiliconixDocument9 pagesIrfbc40, Sihfbc40: Vishay SiliconixStefan CorneaNo ratings yet

- Irfpc60Lc, Sihfpc60Lc: Vishay SiliconixDocument11 pagesIrfpc60Lc, Sihfpc60Lc: Vishay Siliconixkotak kardusNo ratings yet

- Irfpc60Lc, Sihfpc60Lc: Vishay SiliconixDocument9 pagesIrfpc60Lc, Sihfpc60Lc: Vishay Siliconixابو حميد ابو حميدNo ratings yet

- Irf 840aDocument9 pagesIrf 840aPareNo ratings yet

- 2SA1469/2SC3746: 60V/5A High-Speed Switching ApplicationsDocument3 pages2SA1469/2SC3746: 60V/5A High-Speed Switching ApplicationsJavier Mendoza CastroNo ratings yet

- Bfr91a Transistor RF Vishay (To-50)Document8 pagesBfr91a Transistor RF Vishay (To-50)Jesus Hung RodriguezNo ratings yet

- C3807-Sanyo Semicon DeviceDocument4 pagesC3807-Sanyo Semicon DeviceNur AminNo ratings yet

- 2sc3263 Ds enDocument8 pages2sc3263 Ds enNam TàoNo ratings yet

- 2SB892/2SD1207: Large-Current Switching ApplicationsDocument4 pages2SB892/2SD1207: Large-Current Switching ApplicationsIrwantoirwanNo ratings yet

- Unisonic Technologies Co., LTD: NPN General Purpose AmplifierDocument4 pagesUnisonic Technologies Co., LTD: NPN General Purpose AmplifierDavid Carrillo BarrosoNo ratings yet

- Irgp 4066 DPBFDocument11 pagesIrgp 4066 DPBFbahmanNo ratings yet

- 2 SC 2670Document5 pages2 SC 2670RahmatNo ratings yet

- Irfp054, Sihfp054: Vishay SiliconixDocument10 pagesIrfp054, Sihfp054: Vishay SiliconixEmanuelLanNo ratings yet

- Irgp4063Dpbf: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodeDocument11 pagesIrgp4063Dpbf: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodesebaNo ratings yet

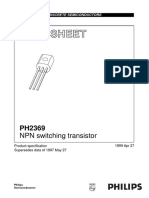

- PH2369 3Document9 pagesPH2369 3Nacho ConsolaniNo ratings yet

- Irfp23N50L, Sihfp23N50L: Vishay SiliconixDocument9 pagesIrfp23N50L, Sihfp23N50L: Vishay Siliconixалексей ЛфNo ratings yet

- DatasheetDocument6 pagesDatasheetLot UxNo ratings yet

- 2N5038 ZalecanyDocument2 pages2N5038 ZalecanyEdzNo ratings yet

- mp1526 Ds enDocument8 pagesmp1526 Ds enRUBEN D. MARIN G.No ratings yet

- Transistor D1406-SavantICDocument4 pagesTransistor D1406-SavantICEdgar MartinezNo ratings yet

- Solar DiagrameDocument10 pagesSolar DiagrameIshtaiq AhmedNo ratings yet

- Latched Comparator: ADC Converters (Continued)Document28 pagesLatched Comparator: ADC Converters (Continued)shriniwas ghadyaljiNo ratings yet

- BLF861ADocument16 pagesBLF861AK.S. BalasubramaniamNo ratings yet

- Sija58Adp: Vishay SiliconixDocument9 pagesSija58Adp: Vishay SiliconixReza RezaNo ratings yet

- 800V/3A Switching Regulator Applications: Package Dimensions FeaturesDocument4 pages800V/3A Switching Regulator Applications: Package Dimensions FeaturesЦанко МарковскиNo ratings yet

- DatasheetDocument4 pagesDatasheetŞener GüneyliNo ratings yet

- Data Sheet: BC636 BC638 BC640Document8 pagesData Sheet: BC636 BC638 BC640Jose M PeresNo ratings yet

- Designed: JfetsDocument1 pageDesigned: JfetsLuis Carlos OrtegaNo ratings yet

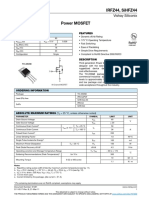

- Irfz44, Sihfz44: Vishay SiliconixDocument9 pagesIrfz44, Sihfz44: Vishay SiliconixherrysugarNo ratings yet

- Irfz44, Sihfz44: Vishay SiliconixDocument9 pagesIrfz44, Sihfz44: Vishay SiliconixAkhilesh Kumar MishraNo ratings yet

- ADC ArchitecturesDocument32 pagesADC ArchitecturesMurali ShettyNo ratings yet

- 2SC3987 NPN Planar Silicon Darlington TransistorDocument5 pages2SC3987 NPN Planar Silicon Darlington Transistoradda chariNo ratings yet

- Irgp4063Pbf Irgp4063-Epbf: Insulated Gate Bipolar TransistorDocument10 pagesIrgp4063Pbf Irgp4063-Epbf: Insulated Gate Bipolar TransistorBuitinės Technikos RemontasNo ratings yet

- G4PC50UDDocument10 pagesG4PC50UDcarlos amayaNo ratings yet

- 2n3904 PDFDocument8 pages2n3904 PDFFrantsiskoNo ratings yet

- Sija52Adp: Vishay SiliconixDocument9 pagesSija52Adp: Vishay SiliconixtemarioNo ratings yet

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDocument4 pagesSilicon NPN Power Transistors: Savantic Semiconductor Product SpecificationTitoNo ratings yet

- Data Sheet: NPN Switching TransistorDocument8 pagesData Sheet: NPN Switching TransistorJoao JesusNo ratings yet

- Data Schedule KD3000889Document2 pagesData Schedule KD3000889Jhoaquino HamachiNo ratings yet

- Transistor PNP B817 PDFDocument4 pagesTransistor PNP B817 PDFEstudiantes MacGregorNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Lecture22 Offset Cancel 6upDocument4 pagesLecture22 Offset Cancel 6upnadeemjuttNo ratings yet

- Lecture23 MOS SH 6upDocument3 pagesLecture23 MOS SH 6upnadeemjuttNo ratings yet

- Lecture21 Matching 6upDocument4 pagesLecture21 Matching 6upnadeemjuttNo ratings yet

- Lecture24 PLL CDR 6upDocument3 pagesLecture24 PLL CDR 6upnadeemjuttNo ratings yet

- EECS240 - Spring 2009 Speed of Light: Both Send Info Back and ForthDocument3 pagesEECS240 - Spring 2009 Speed of Light: Both Send Info Back and ForthnadeemjuttNo ratings yet

- LNH LNL LNQ and LNX Series Remote Condenser Installation Operation ManualDocument20 pagesLNH LNL LNQ and LNX Series Remote Condenser Installation Operation ManualMohamed IbrahimNo ratings yet

- 2ci5 Lab 4Document5 pages2ci5 Lab 4Ibrahim TannirNo ratings yet

- Configuring VTP: Finding Feature InformationDocument26 pagesConfiguring VTP: Finding Feature InformationBui Hong MyNo ratings yet

- FR3449 Plan and ApproachDocument20 pagesFR3449 Plan and ApproachLana Can HandzicNo ratings yet

- Bowtie Diagram Template PPT (1) .PPTX AutoRecoveredDocument3 pagesBowtie Diagram Template PPT (1) .PPTX AutoRecoveredqasrina.aisyahxNo ratings yet

- Journal of CatalysisDocument13 pagesJournal of CatalysisNur KhasanahNo ratings yet

- How To Manage of A Large ClassDocument6 pagesHow To Manage of A Large ClasspaxdheeNo ratings yet

- Study On Sales Promotion Activities of Automobile IndustryDocument2 pagesStudy On Sales Promotion Activities of Automobile IndustryAnil BatraNo ratings yet

- Corporate EnterpreneurshipDocument407 pagesCorporate EnterpreneurshipDenislav DyakovNo ratings yet

- ITMS 6xmigration GuideDocument199 pagesITMS 6xmigration Guidekeithdavid33No ratings yet

- Apl Nov 2022Document9 pagesApl Nov 2022Taufiq SetyaNo ratings yet

- Architectural Elements of RajasthanDocument27 pagesArchitectural Elements of RajasthanSmeet PanchalNo ratings yet

- Outstanding Entries As On 24 Jan 2023 998Document2 pagesOutstanding Entries As On 24 Jan 2023 998Hussain MerchantNo ratings yet

- Ms Meganorm Linha Ampliada A2742 8 1e 2Document13 pagesMs Meganorm Linha Ampliada A2742 8 1e 2yutNo ratings yet

- Alibaba New RetailDocument2 pagesAlibaba New RetailMarsha ReginaNo ratings yet

- Aturan Persembahan Dinner 2019Document4 pagesAturan Persembahan Dinner 2019Tufah ZakariaNo ratings yet

- 36 มยผ.8116-52 มาตรฐานแผงควบคุมเครื่องสูบน้ำดับเพลิงDocument21 pages36 มยผ.8116-52 มาตรฐานแผงควบคุมเครื่องสูบน้ำดับเพลิงappril26No ratings yet

- Screenprinted Waterslide Transfers: The Basics: Basic Principles of Screen-Printing in GeneralDocument5 pagesScreenprinted Waterslide Transfers: The Basics: Basic Principles of Screen-Printing in GeneralParaSemore VivendoNo ratings yet

- Course: CCNA-Cisco Certified Network Associate: Exam Code: CCNA 640-802 Duration: 70 HoursDocument7 pagesCourse: CCNA-Cisco Certified Network Associate: Exam Code: CCNA 640-802 Duration: 70 HoursVasanthbabu Natarajan NNo ratings yet

- Jandy Aqualink RS Owners ManualDocument88 pagesJandy Aqualink RS Owners ManualAeres707No ratings yet

- Module No: 05 Interfacing 8051 To LCD: Course Coordinator:Prof - Mahesh P.YanagimathDocument32 pagesModule No: 05 Interfacing 8051 To LCD: Course Coordinator:Prof - Mahesh P.YanagimathUday shankar B LNo ratings yet

- Iso5455 79Document4 pagesIso5455 79Sebastian PopNo ratings yet

- Abstract: Air Powered CarDocument17 pagesAbstract: Air Powered CarmohammedNo ratings yet

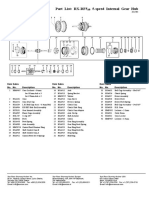

- Part List: RX-RF5 5-Speed Internal Gear HubDocument2 pagesPart List: RX-RF5 5-Speed Internal Gear HubTomislav KoprekNo ratings yet

- History of Linux Operating SystemDocument18 pagesHistory of Linux Operating SystemshahedusaNo ratings yet

- 420 Holiday: Pre 420 Sale! Pre 420 Sale! Pre 420 Sale!Document12 pages420 Holiday: Pre 420 Sale! Pre 420 Sale! Pre 420 Sale!liz6085No ratings yet

- Bomba Electro HidráulicaDocument19 pagesBomba Electro HidráulicaOrlando DíazNo ratings yet

- Apeosportiii c7600Document369 pagesApeosportiii c7600robertNo ratings yet

EECS240 - Spring 2008 Comparator Gain-Bandwidth: Lecture 20: Comparators

EECS240 - Spring 2008 Comparator Gain-Bandwidth: Lecture 20: Comparators

Uploaded by

nadeemjuttOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

EECS240 - Spring 2008 Comparator Gain-Bandwidth: Lecture 20: Comparators

EECS240 - Spring 2008 Comparator Gain-Bandwidth: Lecture 20: Comparators

Uploaded by

nadeemjuttCopyright:

Available Formats

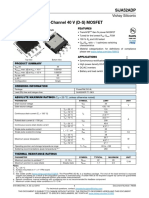

Comparator Gain-Bandwidth

EECS240 – Spring 2008 Example:

• 4Gb/s link

Lecture 20: Comparators • Minimum ∆V: 1mV

• Vdd = 1V

Æ Av > 1V / 1mV = 1000 in < 250ps!

Elad Alon

Dept. of EECS

EECS240 Lecture 20 4

Comparator Operational Amplifier?

+

- fu 2 1

f −3dB = =

clk Avo 3 Tbit

• Specs and issues:

2 Avo

fu =

• Clock rate fs • Power dissipation 3Tbit

• Offset • CM rejection 1000

= = 1.33THz

• Resolution • Kickback noise 3 × 250ps

• Hysteresis • …

• Input cap

EECS240 Lecture 20 2 EECS240 Lecture 20 5

Flash Converter Open-Loop Amplifier Cascade

VREF VIN

• Fast: one clock cycle R/2

per conversion R

• High complexity:

R

Digital

2B-1 comparators Encoder

Output

• High input R

capacitance

R/2

EECS240 Lecture 20 3 EECS240 Lecture 20 6

Cascaded Amplifier Power Consumption

• Simplified bandwidth analysis:

• Open-circuit time constants

• (Not most accurate, but leads to nearly the right

answer for design optimization)

EECS240 Lecture 20 7 EECS240 Lecture 20 10

Bandwidth/Gain Optimization Regenerative Latch

EECS240 Lecture 20 8 EECS240 Lecture 20 11

Bandwidth/Gain Optimization CML Comparator (Latch)

EECS240 Lecture 20 9 EECS240 Lecture 20 12

StrongArm Latch Overdrive Recovery

EECS240 Lecture 20 13 EECS240 Lecture 20 16

Another CMOS Comparator Kickback

EECS240 Lecture 20 14 EECS240 Lecture 20 17

Hysteresis Kickback cont’d

EECS240 Lecture 20 15 EECS240 Lecture 20 18

Kickback cont’d

EECS240 Lecture 20 19

You might also like

- Procreate Pocketbook PDFDocument69 pagesProcreate Pocketbook PDFhadydevcont100% (3)

- Questions & Answers On Transmission LinesDocument43 pagesQuestions & Answers On Transmission Lineskibrom atsbha100% (3)

- EE247 Lecture 20Document30 pagesEE247 Lecture 20maqadarNo ratings yet

- MRF393Document4 pagesMRF393andreasmonNo ratings yet

- BCV27Document6 pagesBCV27RaduNo ratings yet

- Irgb 4062 DPBFDocument13 pagesIrgb 4062 DPBFCarlos OliveiraNo ratings yet

- EECS240 - Spring 2009 Speed of Light: Both Send Info Back and ForthDocument3 pagesEECS240 - Spring 2009 Speed of Light: Both Send Info Back and ForthnadeemjuttNo ratings yet

- High Frequency Amplifier Applications FM, RF, MIX, IF Amplifier ApplicationsDocument7 pagesHigh Frequency Amplifier Applications FM, RF, MIX, IF Amplifier ApplicationsJose VelasquezNo ratings yet

- 2SC3950Document2 pages2SC3950mroocx1000No ratings yet

- IRGIB10B60KD1: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodeDocument12 pagesIRGIB10B60KD1: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodeSmain BendeddoucheNo ratings yet

- DatasheetDocument5 pagesDatasheetQoons CelavegnaNo ratings yet

- FM, RF, MIX, IF Amplifier, High-Frequency General-Purpose Amplifier ApplicationsDocument3 pagesFM, RF, MIX, IF Amplifier, High-Frequency General-Purpose Amplifier ApplicationsSahil SakatNo ratings yet

- Irfp460A, Sihfp460A: Vishay SiliconixDocument11 pagesIrfp460A, Sihfp460A: Vishay SiliconixАлексей АндрияшNo ratings yet

- Vishay IRFP460APBF Datasheet PDFDocument8 pagesVishay IRFP460APBF Datasheet PDFkamel keddarNo ratings yet

- 2 S 1Document8 pages2 S 1Nelson Naval CabingasNo ratings yet

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDocument3 pagesSilicon NPN Power Transistors: Savantic Semiconductor Product SpecificationVitorio LogoNo ratings yet

- C3675-Sanyo Semicon DeviceDocument3 pagesC3675-Sanyo Semicon DeviceMa LhNo ratings yet

- Irgp 4066Document10 pagesIrgp 4066rennybenitezNo ratings yet

- Driver-Stage Audio Amplifier Applications High-Voltage Switching ApplicationsDocument4 pagesDriver-Stage Audio Amplifier Applications High-Voltage Switching ApplicationsMichael KovalNo ratings yet

- Irfbc40, Sihfbc40: Vishay SiliconixDocument9 pagesIrfbc40, Sihfbc40: Vishay SiliconixStefan CorneaNo ratings yet

- Irfpc60Lc, Sihfpc60Lc: Vishay SiliconixDocument11 pagesIrfpc60Lc, Sihfpc60Lc: Vishay Siliconixkotak kardusNo ratings yet

- Irfpc60Lc, Sihfpc60Lc: Vishay SiliconixDocument9 pagesIrfpc60Lc, Sihfpc60Lc: Vishay Siliconixابو حميد ابو حميدNo ratings yet

- Irf 840aDocument9 pagesIrf 840aPareNo ratings yet

- 2SA1469/2SC3746: 60V/5A High-Speed Switching ApplicationsDocument3 pages2SA1469/2SC3746: 60V/5A High-Speed Switching ApplicationsJavier Mendoza CastroNo ratings yet

- Bfr91a Transistor RF Vishay (To-50)Document8 pagesBfr91a Transistor RF Vishay (To-50)Jesus Hung RodriguezNo ratings yet

- C3807-Sanyo Semicon DeviceDocument4 pagesC3807-Sanyo Semicon DeviceNur AminNo ratings yet

- 2sc3263 Ds enDocument8 pages2sc3263 Ds enNam TàoNo ratings yet

- 2SB892/2SD1207: Large-Current Switching ApplicationsDocument4 pages2SB892/2SD1207: Large-Current Switching ApplicationsIrwantoirwanNo ratings yet

- Unisonic Technologies Co., LTD: NPN General Purpose AmplifierDocument4 pagesUnisonic Technologies Co., LTD: NPN General Purpose AmplifierDavid Carrillo BarrosoNo ratings yet

- Irgp 4066 DPBFDocument11 pagesIrgp 4066 DPBFbahmanNo ratings yet

- 2 SC 2670Document5 pages2 SC 2670RahmatNo ratings yet

- Irfp054, Sihfp054: Vishay SiliconixDocument10 pagesIrfp054, Sihfp054: Vishay SiliconixEmanuelLanNo ratings yet

- Irgp4063Dpbf: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodeDocument11 pagesIrgp4063Dpbf: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodesebaNo ratings yet

- PH2369 3Document9 pagesPH2369 3Nacho ConsolaniNo ratings yet

- Irfp23N50L, Sihfp23N50L: Vishay SiliconixDocument9 pagesIrfp23N50L, Sihfp23N50L: Vishay Siliconixалексей ЛфNo ratings yet

- DatasheetDocument6 pagesDatasheetLot UxNo ratings yet

- 2N5038 ZalecanyDocument2 pages2N5038 ZalecanyEdzNo ratings yet

- mp1526 Ds enDocument8 pagesmp1526 Ds enRUBEN D. MARIN G.No ratings yet

- Transistor D1406-SavantICDocument4 pagesTransistor D1406-SavantICEdgar MartinezNo ratings yet

- Solar DiagrameDocument10 pagesSolar DiagrameIshtaiq AhmedNo ratings yet

- Latched Comparator: ADC Converters (Continued)Document28 pagesLatched Comparator: ADC Converters (Continued)shriniwas ghadyaljiNo ratings yet

- BLF861ADocument16 pagesBLF861AK.S. BalasubramaniamNo ratings yet

- Sija58Adp: Vishay SiliconixDocument9 pagesSija58Adp: Vishay SiliconixReza RezaNo ratings yet

- 800V/3A Switching Regulator Applications: Package Dimensions FeaturesDocument4 pages800V/3A Switching Regulator Applications: Package Dimensions FeaturesЦанко МарковскиNo ratings yet

- DatasheetDocument4 pagesDatasheetŞener GüneyliNo ratings yet

- Data Sheet: BC636 BC638 BC640Document8 pagesData Sheet: BC636 BC638 BC640Jose M PeresNo ratings yet

- Designed: JfetsDocument1 pageDesigned: JfetsLuis Carlos OrtegaNo ratings yet

- Irfz44, Sihfz44: Vishay SiliconixDocument9 pagesIrfz44, Sihfz44: Vishay SiliconixherrysugarNo ratings yet

- Irfz44, Sihfz44: Vishay SiliconixDocument9 pagesIrfz44, Sihfz44: Vishay SiliconixAkhilesh Kumar MishraNo ratings yet

- ADC ArchitecturesDocument32 pagesADC ArchitecturesMurali ShettyNo ratings yet

- 2SC3987 NPN Planar Silicon Darlington TransistorDocument5 pages2SC3987 NPN Planar Silicon Darlington Transistoradda chariNo ratings yet

- Irgp4063Pbf Irgp4063-Epbf: Insulated Gate Bipolar TransistorDocument10 pagesIrgp4063Pbf Irgp4063-Epbf: Insulated Gate Bipolar TransistorBuitinės Technikos RemontasNo ratings yet

- G4PC50UDDocument10 pagesG4PC50UDcarlos amayaNo ratings yet

- 2n3904 PDFDocument8 pages2n3904 PDFFrantsiskoNo ratings yet

- Sija52Adp: Vishay SiliconixDocument9 pagesSija52Adp: Vishay SiliconixtemarioNo ratings yet

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDocument4 pagesSilicon NPN Power Transistors: Savantic Semiconductor Product SpecificationTitoNo ratings yet

- Data Sheet: NPN Switching TransistorDocument8 pagesData Sheet: NPN Switching TransistorJoao JesusNo ratings yet

- Data Schedule KD3000889Document2 pagesData Schedule KD3000889Jhoaquino HamachiNo ratings yet

- Transistor PNP B817 PDFDocument4 pagesTransistor PNP B817 PDFEstudiantes MacGregorNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Lecture22 Offset Cancel 6upDocument4 pagesLecture22 Offset Cancel 6upnadeemjuttNo ratings yet

- Lecture23 MOS SH 6upDocument3 pagesLecture23 MOS SH 6upnadeemjuttNo ratings yet

- Lecture21 Matching 6upDocument4 pagesLecture21 Matching 6upnadeemjuttNo ratings yet

- Lecture24 PLL CDR 6upDocument3 pagesLecture24 PLL CDR 6upnadeemjuttNo ratings yet

- EECS240 - Spring 2009 Speed of Light: Both Send Info Back and ForthDocument3 pagesEECS240 - Spring 2009 Speed of Light: Both Send Info Back and ForthnadeemjuttNo ratings yet

- LNH LNL LNQ and LNX Series Remote Condenser Installation Operation ManualDocument20 pagesLNH LNL LNQ and LNX Series Remote Condenser Installation Operation ManualMohamed IbrahimNo ratings yet

- 2ci5 Lab 4Document5 pages2ci5 Lab 4Ibrahim TannirNo ratings yet

- Configuring VTP: Finding Feature InformationDocument26 pagesConfiguring VTP: Finding Feature InformationBui Hong MyNo ratings yet

- FR3449 Plan and ApproachDocument20 pagesFR3449 Plan and ApproachLana Can HandzicNo ratings yet

- Bowtie Diagram Template PPT (1) .PPTX AutoRecoveredDocument3 pagesBowtie Diagram Template PPT (1) .PPTX AutoRecoveredqasrina.aisyahxNo ratings yet

- Journal of CatalysisDocument13 pagesJournal of CatalysisNur KhasanahNo ratings yet

- How To Manage of A Large ClassDocument6 pagesHow To Manage of A Large ClasspaxdheeNo ratings yet

- Study On Sales Promotion Activities of Automobile IndustryDocument2 pagesStudy On Sales Promotion Activities of Automobile IndustryAnil BatraNo ratings yet

- Corporate EnterpreneurshipDocument407 pagesCorporate EnterpreneurshipDenislav DyakovNo ratings yet

- ITMS 6xmigration GuideDocument199 pagesITMS 6xmigration Guidekeithdavid33No ratings yet

- Apl Nov 2022Document9 pagesApl Nov 2022Taufiq SetyaNo ratings yet

- Architectural Elements of RajasthanDocument27 pagesArchitectural Elements of RajasthanSmeet PanchalNo ratings yet

- Outstanding Entries As On 24 Jan 2023 998Document2 pagesOutstanding Entries As On 24 Jan 2023 998Hussain MerchantNo ratings yet

- Ms Meganorm Linha Ampliada A2742 8 1e 2Document13 pagesMs Meganorm Linha Ampliada A2742 8 1e 2yutNo ratings yet

- Alibaba New RetailDocument2 pagesAlibaba New RetailMarsha ReginaNo ratings yet

- Aturan Persembahan Dinner 2019Document4 pagesAturan Persembahan Dinner 2019Tufah ZakariaNo ratings yet

- 36 มยผ.8116-52 มาตรฐานแผงควบคุมเครื่องสูบน้ำดับเพลิงDocument21 pages36 มยผ.8116-52 มาตรฐานแผงควบคุมเครื่องสูบน้ำดับเพลิงappril26No ratings yet

- Screenprinted Waterslide Transfers: The Basics: Basic Principles of Screen-Printing in GeneralDocument5 pagesScreenprinted Waterslide Transfers: The Basics: Basic Principles of Screen-Printing in GeneralParaSemore VivendoNo ratings yet

- Course: CCNA-Cisco Certified Network Associate: Exam Code: CCNA 640-802 Duration: 70 HoursDocument7 pagesCourse: CCNA-Cisco Certified Network Associate: Exam Code: CCNA 640-802 Duration: 70 HoursVasanthbabu Natarajan NNo ratings yet

- Jandy Aqualink RS Owners ManualDocument88 pagesJandy Aqualink RS Owners ManualAeres707No ratings yet

- Module No: 05 Interfacing 8051 To LCD: Course Coordinator:Prof - Mahesh P.YanagimathDocument32 pagesModule No: 05 Interfacing 8051 To LCD: Course Coordinator:Prof - Mahesh P.YanagimathUday shankar B LNo ratings yet

- Iso5455 79Document4 pagesIso5455 79Sebastian PopNo ratings yet

- Abstract: Air Powered CarDocument17 pagesAbstract: Air Powered CarmohammedNo ratings yet

- Part List: RX-RF5 5-Speed Internal Gear HubDocument2 pagesPart List: RX-RF5 5-Speed Internal Gear HubTomislav KoprekNo ratings yet

- History of Linux Operating SystemDocument18 pagesHistory of Linux Operating SystemshahedusaNo ratings yet

- 420 Holiday: Pre 420 Sale! Pre 420 Sale! Pre 420 Sale!Document12 pages420 Holiday: Pre 420 Sale! Pre 420 Sale! Pre 420 Sale!liz6085No ratings yet

- Bomba Electro HidráulicaDocument19 pagesBomba Electro HidráulicaOrlando DíazNo ratings yet

- Apeosportiii c7600Document369 pagesApeosportiii c7600robertNo ratings yet