Professional Documents

Culture Documents

EEE440CA-Spring BCS-7A, B, C-Sessional-II

EEE440CA-Spring BCS-7A, B, C-Sessional-II

Uploaded by

Samiya AhsanCopyright:

Available Formats

You might also like

- Practice Final ExamDocument3 pagesPractice Final ExamThành ThảoNo ratings yet

- Structured Digital System Design Question PaperDocument1 pageStructured Digital System Design Question PaperSatish Bojjawar50% (2)

- Assignment TwoDocument2 pagesAssignment TwoEliza CaramanNo ratings yet

- University of Ghana: This Paper Contains Two Parts (PART I and PART II) Answer All Questions From Both PARTSDocument3 pagesUniversity of Ghana: This Paper Contains Two Parts (PART I and PART II) Answer All Questions From Both PARTSPhilip Pearce-PearsonNo ratings yet

- CSA 2022 Sess2Document2 pagesCSA 2022 Sess2ahmed khanNo ratings yet

- Fall 2023 - CS704 - 4Document3 pagesFall 2023 - CS704 - 4Muhammad Fahad NaeemNo ratings yet

- Coa Ese Q (2022)Document2 pagesCoa Ese Q (2022)Aayush Kumar DubeyNo ratings yet

- Operating System Assignment - II2023-24 - IT B V SEMESTERDocument11 pagesOperating System Assignment - II2023-24 - IT B V SEMESTERRajarapu ChaitanyaNo ratings yet

- Semester IDocument17 pagesSemester IAnnantNo ratings yet

- Computer Organization Jan 2010Document2 pagesComputer Organization Jan 2010Prasad C MNo ratings yet

- CAO 2018 T3 Question PaperDocument2 pagesCAO 2018 T3 Question Paperharsh guptaNo ratings yet

- Indian Institute of Technology Guwahati: Department of Computer Science and EngineeringDocument5 pagesIndian Institute of Technology Guwahati: Department of Computer Science and EngineeringPalashAhujaNo ratings yet

- Quiz For Chapter 7 With SolutionsDocument8 pagesQuiz For Chapter 7 With SolutionsThịi ÁnhhNo ratings yet

- CN1 - ISA1 - 23-24-ver1.1SCHEME Temp - KLETECHDocument14 pagesCN1 - ISA1 - 23-24-ver1.1SCHEME Temp - KLETECH01fe21bcs030No ratings yet

- Architecture Design of A Coarse-Grain Reconfigurable Multiply-Accumulate Unit For Data-Intensive ApplicationsDocument20 pagesArchitecture Design of A Coarse-Grain Reconfigurable Multiply-Accumulate Unit For Data-Intensive ApplicationsCharan MsdNo ratings yet

- JNTUK Computer Organization Nov 2015 Question PaperDocument4 pagesJNTUK Computer Organization Nov 2015 Question PaperTSRKNo ratings yet

- Jbrec CN Lab ManualDocument52 pagesJbrec CN Lab ManualsantoshkumargangaNo ratings yet

- Barani Institute of Management Sciences: BS (CS) - 5B & 5D Computer Architecture CS-532Document1 pageBarani Institute of Management Sciences: BS (CS) - 5B & 5D Computer Architecture CS-532Yaseen ShahidNo ratings yet

- Computer Science Paper 1 SL 1Document6 pagesComputer Science Paper 1 SL 1Amin HasanzadaNo ratings yet

- Cse 317 MidDocument2 pagesCse 317 MidMohammadullahNo ratings yet

- Assignments Unit-3Document1 pageAssignments Unit-3Anil VastavNo ratings yet

- VLSI LAB MANUAL (18ECL77) - Analog dt14-01-2022Document148 pagesVLSI LAB MANUAL (18ECL77) - Analog dt14-01-2022Aamish PriyamNo ratings yet

- DAA Mini ProjectDocument15 pagesDAA Mini ProjectAjinkya SomawanshiNo ratings yet

- Iare Co Ece QP 1Document2 pagesIare Co Ece QP 1harshit playboyNo ratings yet

- CSE 3701 A Moderated FHSDocument1 pageCSE 3701 A Moderated FHSMd. Abdus ShahidNo ratings yet

- PS-IMC A 2385.7-TOPS W B Precision Scalable In-Memory Computing Macro With Bit-Parallel Inputs and Decomposable Weights For DNNsDocument4 pagesPS-IMC A 2385.7-TOPS W B Precision Scalable In-Memory Computing Macro With Bit-Parallel Inputs and Decomposable Weights For DNNsmeg.huangNo ratings yet

- Project 2Document2 pagesProject 2Gopi Reddy RanabothuNo ratings yet

- CC INDEX Merged (1) MergedDocument18 pagesCC INDEX Merged (1) MergedLokesh RajNo ratings yet

- HCT222 - 22computer Architecture and Organization 2021 July Test1Document6 pagesHCT222 - 22computer Architecture and Organization 2021 July Test1Nyasha ChiroroNo ratings yet

- bt31R07 P1 10 11 2009rahulDocument31 pagesbt31R07 P1 10 11 2009rahulashok1261No ratings yet

- NB:-Write The Answers in Your Own Way and Do Not Copy From OtherDocument2 pagesNB:-Write The Answers in Your Own Way and Do Not Copy From OtherSayanMaitiNo ratings yet

- COMPUTER SC. SL PAPER ONE in ENGLISHDocument5 pagesCOMPUTER SC. SL PAPER ONE in ENGLISHOliver NixNo ratings yet

- Cloud Computing Question PaperDocument1 pageCloud Computing Question PapermamathamNo ratings yet

- Lab Assignment-2Document1 pageLab Assignment-2chanduNo ratings yet

- WWW - Manaresults.co - In: (Common To CSE, IT)Document2 pagesWWW - Manaresults.co - In: (Common To CSE, IT)Fker FkerNo ratings yet

- Mca (Management) 2019 PatternDocument67 pagesMca (Management) 2019 PatternKartikeyan BallaNo ratings yet

- EC604 Assignment - 1682053761Document1 pageEC604 Assignment - 1682053761Gopi PawarNo ratings yet

- B.E. Electronics and Communication Engineering: VLSI LAB (0:0:3) 1.5Document3 pagesB.E. Electronics and Communication Engineering: VLSI LAB (0:0:3) 1.5Amit ShetNo ratings yet

- COA Sessional - II - 2018 With SolutionsDocument4 pagesCOA Sessional - II - 2018 With SolutionspoonamNo ratings yet

- Course Title: Computer Architecture and Organization, Course Code: CSTE-2205 Time: 04 HoursDocument2 pagesCourse Title: Computer Architecture and Organization, Course Code: CSTE-2205 Time: 04 HoursMostakim RedoyNo ratings yet

- Sir Syed University of Engineering and TechnologyDocument4 pagesSir Syed University of Engineering and TechnologyFahad SiddiquiNo ratings yet

- Assignment 5 - OpenCL OptimizationsDocument2 pagesAssignment 5 - OpenCL OptimizationsAbdulahi Abebe100% (1)

- Section-A: Time: 2 Hours. Date of ExaminationDocument2 pagesSection-A: Time: 2 Hours. Date of ExaminationAnuj KumarNo ratings yet

- K. J. Somaiya College of Engineering, Mumbai-77Document8 pagesK. J. Somaiya College of Engineering, Mumbai-77Saraunsh JadhavNo ratings yet

- Data Structures & Algorithm - Final TermDocument4 pagesData Structures & Algorithm - Final Termm.zulaid.motivationNo ratings yet

- 2022-BitBlade - Energy-Efficient - Variable - Bit-Precision - Hardware - Accelerator - For - Quantized - Neural - NetworksDocument12 pages2022-BitBlade - Energy-Efficient - Variable - Bit-Precision - Hardware - Accelerator - For - Quantized - Neural - NetworksSohan SaiNo ratings yet

- Se, All Branches. C A - oDocument2 pagesSe, All Branches. C A - oanuragnair377No ratings yet

- Csizg527 Sat09 AnDocument1 pageCsizg527 Sat09 AnAjay GowthamNo ratings yet

- CN Final Spring 22 TheoryDocument1 pageCN Final Spring 22 TheoryWajid AbbasNo ratings yet

- University of Mauritius Faculty of Engineering: Paper No Examination Second Semester 2002/2003 DateDocument6 pagesUniversity of Mauritius Faculty of Engineering: Paper No Examination Second Semester 2002/2003 Datemy pcNo ratings yet

- Sessional1 - Subjective - SolutionDocument2 pagesSessional1 - Subjective - SolutionRao Nauman AhmadNo ratings yet

- Semester - IIDocument20 pagesSemester - IIsahil vermaNo ratings yet

- CN - Journall - 2020 - V - SEM (Exp 5-8)Document22 pagesCN - Journall - 2020 - V - SEM (Exp 5-8)vatsal pathakNo ratings yet

- Vedic-BasedSquaringCircuitUsingParallelPrefixAddersDocument6 pagesVedic-BasedSquaringCircuitUsingParallelPrefixAddershrosingh13579No ratings yet

- Vlsi Lab Manual (18ecl77) - 2022-23Document226 pagesVlsi Lab Manual (18ecl77) - 2022-23Prajwal KoppaNo ratings yet

- COMSATS University Islamabad: Sahiwal Campus (Department of Computer Science)Document3 pagesCOMSATS University Islamabad: Sahiwal Campus (Department of Computer Science)Binte ZahraNo ratings yet

- CN Lab Manual Cse DepartmentDocument49 pagesCN Lab Manual Cse Departmentvvvcxzzz3754No ratings yet

- VLSI Course Based Project Report Batch-2Document18 pagesVLSI Course Based Project Report Batch-2ECE BNo ratings yet

- BCN1043 Computer Arc & Org S1 0119Document6 pagesBCN1043 Computer Arc & Org S1 0119m-868020No ratings yet

- Assignment 1Document3 pagesAssignment 1Samiya AhsanNo ratings yet

- Assignment 3Document2 pagesAssignment 3Samiya AhsanNo ratings yet

- MTH-206 Statistics and Probability TheoryDocument10 pagesMTH-206 Statistics and Probability TheorySamiya AhsanNo ratings yet

- Eee440ca Bcs Bee Bce A4Document1 pageEee440ca Bcs Bee Bce A4Samiya AhsanNo ratings yet

- Human Computer InteractionDocument34 pagesHuman Computer InteractionSamiya AhsanNo ratings yet

- Eee440ca Bcs Bee Bce A4Document1 pageEee440ca Bcs Bee Bce A4Samiya AhsanNo ratings yet

EEE440CA-Spring BCS-7A, B, C-Sessional-II

EEE440CA-Spring BCS-7A, B, C-Sessional-II

Uploaded by

Samiya AhsanOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

EEE440CA-Spring BCS-7A, B, C-Sessional-II

EEE440CA-Spring BCS-7A, B, C-Sessional-II

Uploaded by

Samiya AhsanCopyright:

Available Formats

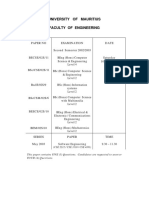

COMSATS University Islamabad

Spring 2021

EEE440 Computer Architecture

Sessional-II

Program: BCS-7A, B, C Total Marks: 15

Semester: Spring 2021 Date: 06 May, 2021

Instructor: M. Dilshad Sabir Time: 60 min

Question No. 01 Consider the following code, which multiplies two vectors that contain single-

precision complex values:

for (i=0;i<300;i++) {

c_re[i] = a_re[i] * b_re[i] – a_im[i] * b_im[i];

c_im[i] = a_re[i] * b_im[i] + a_im[i] * b_re[i];

}

Assume that the processor runs at 700 MHz and has a maximum vector length of 64. The load/store

unit has a start-up overhead of 15 cycles; the multiply unit, 8 cycles; and the add/subtract unit, 5

cycles.

a. What is the arithmetic intensity of this kernel? [2.5]

b. Convert this loop into VMIPS assembly code using strip mining. [2.5]

c. Assuming chaining and a single memory pipeline, how many chimes are required?

How many clock cycles are required per complex result value, including start-up

overhead? [2.5]

d. If the vector sequence is chained, how many clock cycles are required per complex

result value, including overhead? [2.5]

Question No. 02 Consider a 32-bit microprocessor that has an on-chip 16 K-byte

four-way set-associative cache. Assume that the cache has a line size of four 32-bit

works. Draw a block diagram of this cache showing its organization and how

different address fields are used to determine a cache hit/miss. [5]

You might also like

- Practice Final ExamDocument3 pagesPractice Final ExamThành ThảoNo ratings yet

- Structured Digital System Design Question PaperDocument1 pageStructured Digital System Design Question PaperSatish Bojjawar50% (2)

- Assignment TwoDocument2 pagesAssignment TwoEliza CaramanNo ratings yet

- University of Ghana: This Paper Contains Two Parts (PART I and PART II) Answer All Questions From Both PARTSDocument3 pagesUniversity of Ghana: This Paper Contains Two Parts (PART I and PART II) Answer All Questions From Both PARTSPhilip Pearce-PearsonNo ratings yet

- CSA 2022 Sess2Document2 pagesCSA 2022 Sess2ahmed khanNo ratings yet

- Fall 2023 - CS704 - 4Document3 pagesFall 2023 - CS704 - 4Muhammad Fahad NaeemNo ratings yet

- Coa Ese Q (2022)Document2 pagesCoa Ese Q (2022)Aayush Kumar DubeyNo ratings yet

- Operating System Assignment - II2023-24 - IT B V SEMESTERDocument11 pagesOperating System Assignment - II2023-24 - IT B V SEMESTERRajarapu ChaitanyaNo ratings yet

- Semester IDocument17 pagesSemester IAnnantNo ratings yet

- Computer Organization Jan 2010Document2 pagesComputer Organization Jan 2010Prasad C MNo ratings yet

- CAO 2018 T3 Question PaperDocument2 pagesCAO 2018 T3 Question Paperharsh guptaNo ratings yet

- Indian Institute of Technology Guwahati: Department of Computer Science and EngineeringDocument5 pagesIndian Institute of Technology Guwahati: Department of Computer Science and EngineeringPalashAhujaNo ratings yet

- Quiz For Chapter 7 With SolutionsDocument8 pagesQuiz For Chapter 7 With SolutionsThịi ÁnhhNo ratings yet

- CN1 - ISA1 - 23-24-ver1.1SCHEME Temp - KLETECHDocument14 pagesCN1 - ISA1 - 23-24-ver1.1SCHEME Temp - KLETECH01fe21bcs030No ratings yet

- Architecture Design of A Coarse-Grain Reconfigurable Multiply-Accumulate Unit For Data-Intensive ApplicationsDocument20 pagesArchitecture Design of A Coarse-Grain Reconfigurable Multiply-Accumulate Unit For Data-Intensive ApplicationsCharan MsdNo ratings yet

- JNTUK Computer Organization Nov 2015 Question PaperDocument4 pagesJNTUK Computer Organization Nov 2015 Question PaperTSRKNo ratings yet

- Jbrec CN Lab ManualDocument52 pagesJbrec CN Lab ManualsantoshkumargangaNo ratings yet

- Barani Institute of Management Sciences: BS (CS) - 5B & 5D Computer Architecture CS-532Document1 pageBarani Institute of Management Sciences: BS (CS) - 5B & 5D Computer Architecture CS-532Yaseen ShahidNo ratings yet

- Computer Science Paper 1 SL 1Document6 pagesComputer Science Paper 1 SL 1Amin HasanzadaNo ratings yet

- Cse 317 MidDocument2 pagesCse 317 MidMohammadullahNo ratings yet

- Assignments Unit-3Document1 pageAssignments Unit-3Anil VastavNo ratings yet

- VLSI LAB MANUAL (18ECL77) - Analog dt14-01-2022Document148 pagesVLSI LAB MANUAL (18ECL77) - Analog dt14-01-2022Aamish PriyamNo ratings yet

- DAA Mini ProjectDocument15 pagesDAA Mini ProjectAjinkya SomawanshiNo ratings yet

- Iare Co Ece QP 1Document2 pagesIare Co Ece QP 1harshit playboyNo ratings yet

- CSE 3701 A Moderated FHSDocument1 pageCSE 3701 A Moderated FHSMd. Abdus ShahidNo ratings yet

- PS-IMC A 2385.7-TOPS W B Precision Scalable In-Memory Computing Macro With Bit-Parallel Inputs and Decomposable Weights For DNNsDocument4 pagesPS-IMC A 2385.7-TOPS W B Precision Scalable In-Memory Computing Macro With Bit-Parallel Inputs and Decomposable Weights For DNNsmeg.huangNo ratings yet

- Project 2Document2 pagesProject 2Gopi Reddy RanabothuNo ratings yet

- CC INDEX Merged (1) MergedDocument18 pagesCC INDEX Merged (1) MergedLokesh RajNo ratings yet

- HCT222 - 22computer Architecture and Organization 2021 July Test1Document6 pagesHCT222 - 22computer Architecture and Organization 2021 July Test1Nyasha ChiroroNo ratings yet

- bt31R07 P1 10 11 2009rahulDocument31 pagesbt31R07 P1 10 11 2009rahulashok1261No ratings yet

- NB:-Write The Answers in Your Own Way and Do Not Copy From OtherDocument2 pagesNB:-Write The Answers in Your Own Way and Do Not Copy From OtherSayanMaitiNo ratings yet

- COMPUTER SC. SL PAPER ONE in ENGLISHDocument5 pagesCOMPUTER SC. SL PAPER ONE in ENGLISHOliver NixNo ratings yet

- Cloud Computing Question PaperDocument1 pageCloud Computing Question PapermamathamNo ratings yet

- Lab Assignment-2Document1 pageLab Assignment-2chanduNo ratings yet

- WWW - Manaresults.co - In: (Common To CSE, IT)Document2 pagesWWW - Manaresults.co - In: (Common To CSE, IT)Fker FkerNo ratings yet

- Mca (Management) 2019 PatternDocument67 pagesMca (Management) 2019 PatternKartikeyan BallaNo ratings yet

- EC604 Assignment - 1682053761Document1 pageEC604 Assignment - 1682053761Gopi PawarNo ratings yet

- B.E. Electronics and Communication Engineering: VLSI LAB (0:0:3) 1.5Document3 pagesB.E. Electronics and Communication Engineering: VLSI LAB (0:0:3) 1.5Amit ShetNo ratings yet

- COA Sessional - II - 2018 With SolutionsDocument4 pagesCOA Sessional - II - 2018 With SolutionspoonamNo ratings yet

- Course Title: Computer Architecture and Organization, Course Code: CSTE-2205 Time: 04 HoursDocument2 pagesCourse Title: Computer Architecture and Organization, Course Code: CSTE-2205 Time: 04 HoursMostakim RedoyNo ratings yet

- Sir Syed University of Engineering and TechnologyDocument4 pagesSir Syed University of Engineering and TechnologyFahad SiddiquiNo ratings yet

- Assignment 5 - OpenCL OptimizationsDocument2 pagesAssignment 5 - OpenCL OptimizationsAbdulahi Abebe100% (1)

- Section-A: Time: 2 Hours. Date of ExaminationDocument2 pagesSection-A: Time: 2 Hours. Date of ExaminationAnuj KumarNo ratings yet

- K. J. Somaiya College of Engineering, Mumbai-77Document8 pagesK. J. Somaiya College of Engineering, Mumbai-77Saraunsh JadhavNo ratings yet

- Data Structures & Algorithm - Final TermDocument4 pagesData Structures & Algorithm - Final Termm.zulaid.motivationNo ratings yet

- 2022-BitBlade - Energy-Efficient - Variable - Bit-Precision - Hardware - Accelerator - For - Quantized - Neural - NetworksDocument12 pages2022-BitBlade - Energy-Efficient - Variable - Bit-Precision - Hardware - Accelerator - For - Quantized - Neural - NetworksSohan SaiNo ratings yet

- Se, All Branches. C A - oDocument2 pagesSe, All Branches. C A - oanuragnair377No ratings yet

- Csizg527 Sat09 AnDocument1 pageCsizg527 Sat09 AnAjay GowthamNo ratings yet

- CN Final Spring 22 TheoryDocument1 pageCN Final Spring 22 TheoryWajid AbbasNo ratings yet

- University of Mauritius Faculty of Engineering: Paper No Examination Second Semester 2002/2003 DateDocument6 pagesUniversity of Mauritius Faculty of Engineering: Paper No Examination Second Semester 2002/2003 Datemy pcNo ratings yet

- Sessional1 - Subjective - SolutionDocument2 pagesSessional1 - Subjective - SolutionRao Nauman AhmadNo ratings yet

- Semester - IIDocument20 pagesSemester - IIsahil vermaNo ratings yet

- CN - Journall - 2020 - V - SEM (Exp 5-8)Document22 pagesCN - Journall - 2020 - V - SEM (Exp 5-8)vatsal pathakNo ratings yet

- Vedic-BasedSquaringCircuitUsingParallelPrefixAddersDocument6 pagesVedic-BasedSquaringCircuitUsingParallelPrefixAddershrosingh13579No ratings yet

- Vlsi Lab Manual (18ecl77) - 2022-23Document226 pagesVlsi Lab Manual (18ecl77) - 2022-23Prajwal KoppaNo ratings yet

- COMSATS University Islamabad: Sahiwal Campus (Department of Computer Science)Document3 pagesCOMSATS University Islamabad: Sahiwal Campus (Department of Computer Science)Binte ZahraNo ratings yet

- CN Lab Manual Cse DepartmentDocument49 pagesCN Lab Manual Cse Departmentvvvcxzzz3754No ratings yet

- VLSI Course Based Project Report Batch-2Document18 pagesVLSI Course Based Project Report Batch-2ECE BNo ratings yet

- BCN1043 Computer Arc & Org S1 0119Document6 pagesBCN1043 Computer Arc & Org S1 0119m-868020No ratings yet

- Assignment 1Document3 pagesAssignment 1Samiya AhsanNo ratings yet

- Assignment 3Document2 pagesAssignment 3Samiya AhsanNo ratings yet

- MTH-206 Statistics and Probability TheoryDocument10 pagesMTH-206 Statistics and Probability TheorySamiya AhsanNo ratings yet

- Eee440ca Bcs Bee Bce A4Document1 pageEee440ca Bcs Bee Bce A4Samiya AhsanNo ratings yet

- Human Computer InteractionDocument34 pagesHuman Computer InteractionSamiya AhsanNo ratings yet

- Eee440ca Bcs Bee Bce A4Document1 pageEee440ca Bcs Bee Bce A4Samiya AhsanNo ratings yet