Professional Documents

Culture Documents

Netlist For SRAM

Netlist For SRAM

Uploaded by

Proyash SahaCopyright:

Available Formats

You might also like

- Alif E1 Datasheet v2.5-1Document161 pagesAlif E1 Datasheet v2.5-1alex.gurioNo ratings yet

- 2023 02 Ansys General Hardware RecommendationsDocument24 pages2023 02 Ansys General Hardware RecommendationsDayvid Melo BrittoNo ratings yet

- Basic Cell HSpice CodeDocument4 pagesBasic Cell HSpice CodeWaqar IshaqNo ratings yet

- Hspice Simulation of SRAMDocument65 pagesHspice Simulation of SRAMYatheesh Kaggere100% (1)

- Device Monte Carlo Simulation Methodology of Two-Dimensional FinFET SlicesDocument8 pagesDevice Monte Carlo Simulation Methodology of Two-Dimensional FinFET SlicesGracia Meliolla Sitorus100% (1)

- Mosfet AtlasDocument2 pagesMosfet AtlasAnonymous eWMnRr70qNo ratings yet

- Timer Tc100d2 SGL Line 0908 (Tecalemit)Document6 pagesTimer Tc100d2 SGL Line 0908 (Tecalemit)NovakurniawanNo ratings yet

- Training Manual: Rev. Date DateDocument150 pagesTraining Manual: Rev. Date DateVision COMNo ratings yet

- HW6 Solution PDFDocument16 pagesHW6 Solution PDFYgor AguiarNo ratings yet

- Hspice Simulation of SRAM PDFDocument65 pagesHspice Simulation of SRAM PDFYatheesh KaggereNo ratings yet

- Seminar Report: Submitted By: Amena Tarique (16BEC027)Document25 pagesSeminar Report: Submitted By: Amena Tarique (16BEC027)Moon SkyNo ratings yet

- Lect8 SpiceDocument27 pagesLect8 SpiceishantNo ratings yet

- Thesis Report - Exploring Memristor TopologiesDocument59 pagesThesis Report - Exploring Memristor TopologiesSerdar BenderliNo ratings yet

- 018 RF Model Document V2d2Document91 pages018 RF Model Document V2d2Rogelio Manuel Higuera GonzalezNo ratings yet

- Introduction To Sentaurus TCADDocument47 pagesIntroduction To Sentaurus TCADvijayNo ratings yet

- Computer ArchitectureDocument104 pagesComputer ArchitectureapuurvaNo ratings yet

- Basic ARM9 Block DiagramDocument2 pagesBasic ARM9 Block Diagramhumtum_shriNo ratings yet

- ARM ArchitectureDocument6 pagesARM ArchitectureCarlos AraujoNo ratings yet

- ARM CORTEX M4 Memory LayoutDocument11 pagesARM CORTEX M4 Memory LayoutGurram KishoreNo ratings yet

- New Cortex-R Processors For Lte and 4g Mobile BasebandDocument6 pagesNew Cortex-R Processors For Lte and 4g Mobile BasebandSaiteja ReddyNo ratings yet

- 1st Interview Questions-QualcommDocument1 page1st Interview Questions-QualcommSandya VemuriNo ratings yet

- Eetop - CN Emx Virtuoso ManualDocument35 pagesEetop - CN Emx Virtuoso Manualhuyadong1234No ratings yet

- ESARM Unit-III and IV Slides MergedDocument301 pagesESARM Unit-III and IV Slides MergedShashipreetham LakkakulaNo ratings yet

- 14 NMDocument23 pages14 NMNikhilAKothariNo ratings yet

- Lab 10 NSGDocument3 pagesLab 10 NSGMuhammad Awais ShahNo ratings yet

- Aulas15 16Document16 pagesAulas15 16Pramod Reddy RNo ratings yet

- CMOS Process FlowDocument35 pagesCMOS Process Flowag21937570No ratings yet

- Sram 6TDocument5 pagesSram 6Taashish kumarNo ratings yet

- Cadence Redhat 6 InstallationDocument8 pagesCadence Redhat 6 InstallationBahram RN100% (1)

- Lecture 2 - ARM Instruction SetDocument42 pagesLecture 2 - ARM Instruction SetSuhaib AbugderaNo ratings yet

- A 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliDocument4 pagesA 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliAnika TahsinNo ratings yet

- Timeline AMDDocument6 pagesTimeline AMDRey DumpitNo ratings yet

- Sensori A Stato Solido LS Presentazione TCAD Sentaurus PDFDocument27 pagesSensori A Stato Solido LS Presentazione TCAD Sentaurus PDFBharath KumarNo ratings yet

- Chapter 4Document100 pagesChapter 4khgvouy hvogyflNo ratings yet

- On-Chip Bus: Speaker: Tian-Sheuan Chang July, 2004Document40 pagesOn-Chip Bus: Speaker: Tian-Sheuan Chang July, 2004Tarun GhoshNo ratings yet

- EE4S23 - ASIC Technology and Test SystemsDocument39 pagesEE4S23 - ASIC Technology and Test Systemsfahadmas872070No ratings yet

- 8k Bit Using 6t SramDocument8 pages8k Bit Using 6t SramSwati Navdeep AggarwalNo ratings yet

- Kunci Jawaban Soal Buku Computer and Communication Networks Nader F Mir Chapter 1Document8 pagesKunci Jawaban Soal Buku Computer and Communication Networks Nader F Mir Chapter 1Aditya IrawanNo ratings yet

- Vlsi Mtech Jntu Kakinada SyllabusDocument11 pagesVlsi Mtech Jntu Kakinada Syllabusaditya414No ratings yet

- 8257 DMA Controller:: To Fetch The Instruction To Decode The Instruction and To Execute The InstructionDocument25 pages8257 DMA Controller:: To Fetch The Instruction To Decode The Instruction and To Execute The Instructionsatyanarayana12No ratings yet

- Level 54 Bsim4Document13 pagesLevel 54 Bsim4Georgios SarrisNo ratings yet

- Unit Ii ArmDocument243 pagesUnit Ii ArmMani BharathiNo ratings yet

- Understanding About CMOS Fabrication TechnologyDocument4 pagesUnderstanding About CMOS Fabrication TechnologyJayesh RaghuwanshiNo ratings yet

- XilinxDocument20 pagesXilinxAvila Cruz JaimeNo ratings yet

- Wireless Sensor Network Simulators A Survey and Comparisons: Harsh SundaniDocument17 pagesWireless Sensor Network Simulators A Survey and Comparisons: Harsh Sundanisafdar-abbasNo ratings yet

- How To Use JTAG With ARM7 MCUDocument20 pagesHow To Use JTAG With ARM7 MCUGurpreet SinghNo ratings yet

- Cortex R4 White PaperDocument20 pagesCortex R4 White PaperRAJARAMNo ratings yet

- DVD2 JNTU Set1 SolutionsDocument12 pagesDVD2 JNTU Set1 Solutionsకిరణ్ కుమార్ పగడాలNo ratings yet

- Ec6111 - Vlsi DesignDocument9 pagesEc6111 - Vlsi DesignMegha SrivastavaNo ratings yet

- CN Lab Manual PDFDocument62 pagesCN Lab Manual PDFsandhiya .vNo ratings yet

- 8x4 SRAM in TSMC 0.25 M Technology: NtroductionDocument6 pages8x4 SRAM in TSMC 0.25 M Technology: NtroductionAdib NahiyanNo ratings yet

- Solid State Device Modeling 1Document199 pagesSolid State Device Modeling 1DarwinNo ratings yet

- Unit V Processes and Operating SystemsDocument37 pagesUnit V Processes and Operating SystemsManikandan Annamalai100% (1)

- 2011 - Advanced Technology For High Performance & Low Power ApplicationsDocument12 pages2011 - Advanced Technology For High Performance & Low Power Applicationsambica207No ratings yet

- Fifo DepthDocument1 pageFifo DepthSameer BadachiNo ratings yet

- Lab 05 To Perform Signal Companding in SimulinkDocument15 pagesLab 05 To Perform Signal Companding in SimulinkArshad AliNo ratings yet

- SRPWMC FinalDocument7 pagesSRPWMC Finalapi-340769184No ratings yet

- Timer 1Document6 pagesTimer 1joxenoNo ratings yet

- DSP Test1 CheatsheetDocument3 pagesDSP Test1 Cheatsheet201003489No ratings yet

- 71r-A14hmo-9h10 A14hm0-Ab10Document40 pages71r-A14hmo-9h10 A14hm0-Ab10Camila GuimarãesNo ratings yet

- Appendix E - CALPUFF Input FileDocument26 pagesAppendix E - CALPUFF Input FilewillygansNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Data Sheet 6ES7221-1BF32-0XB0: General InformationDocument3 pagesData Sheet 6ES7221-1BF32-0XB0: General InformationzeeshanNo ratings yet

- MM30 743 ManualDocument31 pagesMM30 743 ManualpadmawarNo ratings yet

- Panasonic KX-T2375MXW Service ManualDocument39 pagesPanasonic KX-T2375MXW Service Manualnifiyeb189No ratings yet

- LI-PO SizesDocument17 pagesLI-PO SizesmariorossiNo ratings yet

- HVAC Instruments: Clamp-On Ammeter VoltmeterDocument8 pagesHVAC Instruments: Clamp-On Ammeter VoltmeterMuhammad Jamshaid KhanNo ratings yet

- High Pressure Pure Air Generator (Hippag)Document2 pagesHigh Pressure Pure Air Generator (Hippag)BarisNo ratings yet

- v8 Sy PDFDocument12 pagesv8 Sy PDFozzy123No ratings yet

- Electronic Devices (Group-8)Document32 pagesElectronic Devices (Group-8)Saloni GargNo ratings yet

- Ad7606b 1623783Document73 pagesAd7606b 1623783Jeferson AlvesNo ratings yet

- Antm5&Eec廿: Professional AntennaDocument16 pagesAntm5&Eec廿: Professional AntennaabcdefghiklNo ratings yet

- High Fidelity Loudspeaker EnclosuresDocument52 pagesHigh Fidelity Loudspeaker EnclosuresEduardoNo ratings yet

- Mission 77 ManualDocument2 pagesMission 77 ManualPaulo Coutinho100% (1)

- Fundamentals of Vibration Measurement and Analysis ExplainedDocument13 pagesFundamentals of Vibration Measurement and Analysis ExplainedRLE2014No ratings yet

- Act Sheet For RoboticsDocument4 pagesAct Sheet For RoboticsErah Kim GomezNo ratings yet

- Tunstall Flamenco IP - WANTZ SOLUTION R1Document24 pagesTunstall Flamenco IP - WANTZ SOLUTION R1muhd faizNo ratings yet

- Door BellDocument12 pagesDoor Belliram fatimaNo ratings yet

- Dell S4112-ON Series Installation GuideDocument44 pagesDell S4112-ON Series Installation GuideLarryNo ratings yet

- Final Year SyllabusDocument12 pagesFinal Year SyllabusArvNo ratings yet

- A030A102 I8 201406 PartesDocument68 pagesA030A102 I8 201406 PartesMiguel Cabezas100% (1)

- Substation Engineering & LayoutDocument4 pagesSubstation Engineering & Layoutgulatimanish1985No ratings yet

- Accounting Seligram CaseDocument2 pagesAccounting Seligram CaseNadia Iqbal100% (1)

- B302 - LOAD LIST IPS Station For SEB DTD 04.10.2023Document1 pageB302 - LOAD LIST IPS Station For SEB DTD 04.10.2023Abdul Wajid AliNo ratings yet

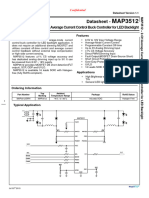

- MAP3512Document15 pagesMAP3512KhalidNo ratings yet

- Construction of 500w12vinverter ChargerDocument12 pagesConstruction of 500w12vinverter ChargerAbba SaadNo ratings yet

- EE KonodiaDocument453 pagesEE KonodiaAaryan RajNo ratings yet

- Sony str-k760pDocument44 pagesSony str-k760pValtemir OliveiraNo ratings yet

- Connectores EatonDocument56 pagesConnectores EatonLeandro BustamanteNo ratings yet

- Design and Construction of Fuelless AC Generator Using Alternator Interfaced With An InverterDocument5 pagesDesign and Construction of Fuelless AC Generator Using Alternator Interfaced With An InverterEditor IJTSRDNo ratings yet

Netlist For SRAM

Netlist For SRAM

Uploaded by

Proyash SahaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Netlist For SRAM

Netlist For SRAM

Uploaded by

Proyash SahaCopyright:

Available Formats

How to write netlist for SRAM

Shantonu Debnath

Department of CST, IIEST, Shibpur

Code

***Inverter SRAM***

***Read Operation***

*initial conditions stored for read operation

.ic v(Q)=1

.ic v(QR)=1

*data control

.ic v(bl)=1

.ic v(blb)=1

*** NETLIST Description ***

Name Drain Gate Source Bulk Model name Parameter (width and length)

** Bulk: 1. For pmos Source

2. For nmos Ground

3. For data access Bit/Bit bar.

** Follow the picture for clear about mentioned point

***Now we are add Voltage***

Name Drain Ground Type of voltage Pulse

**that’s applicable for Vdd and WL and for Vdd and Wl pulse is 1.

Name Drain Ground PULSE (V1 V2 <TD> <TR> <TF> <PW> <PER>)

The parameters are:

V1 = the initial value (volts or amps)

V2 = the pulsed value (volts or amps)

<TD>= the seconds before the first pulsed value

<TR>= the seconds it takes the pulse to rise from V1 to V2

<TF>= the seconds it takes the pulse to fall from V2 to V1

<PW>= the number of seconds the signal stays at V2

<PER>= the time between each rising edge of the pulse after the first initial pulse

***Transient Analysis (.TRAN)***

.tran TSTEP TSTOP <TSTART <TMAX>>

The parameters are:

TSTEP = the time between each sample in the simulation

TSTOP = the stop time in the simulation which starts at 0 seconds.

TSTART = the start time to save data for later analysis (useful when memory is

limited)

TMAX = the maximum step size that WinSpice3 uses

*** MODEL Descriptions ***

Add model for pmos

Add model for nmos

**PTM link: http://ptm.asu.edu/

**source: PTM

*** Option ***

.option post accurate nomod brief

.option post_version=9007

.option runlvl = 5

.op

**or

.options POST=2

.options AUTOSTOP

.options INGOLD=2 DCON=1

.options GSHUNT=1e-12 RMIN=1e-15

.options ABSTOL=1e-5 ABSVDC=1e-4

.options RELTOL=1e-2 RELVDC=1e-2

.options NUMDGT=4 PIVOT=13

.options runlvl=6

***End of Simulation (.END)

.end

Example Code

*SRAM*

mpgl 4 1 5 5 nmos w=45 n l=45n

mpgr 6 1 3 6 nmos w=45n l =45n

mpdl 4 3 0 0 nmos w=45n l=45n

mpdr 3 4 0 0 nmos w=45n l=45n

mpul 2 3 4 2 pmos w=90n l=45n

mpur 2 4 3 2 pmos w=90n l=45n

v1 1 0 1 *this is word line "WL*

V2 5 0 pulse (0 1 0 0.01n 0.01n 10n 20n) *this is Bit line*

v3 6 0 pulse (0 1 10n 0.01n 0.01n 10n 28n) *this is for BitBar "BLB"*

V4 2 0 1 *this is for VDD*

.tran 0.1n 20n start = 0

.model nmos

.model pmos

**from ptm site (congf 45nm , vdd= 1 )

.option post accurate nomod brief

.option post_version=9007

.option runlvl = 5

.op

.end

You might also like

- Alif E1 Datasheet v2.5-1Document161 pagesAlif E1 Datasheet v2.5-1alex.gurioNo ratings yet

- 2023 02 Ansys General Hardware RecommendationsDocument24 pages2023 02 Ansys General Hardware RecommendationsDayvid Melo BrittoNo ratings yet

- Basic Cell HSpice CodeDocument4 pagesBasic Cell HSpice CodeWaqar IshaqNo ratings yet

- Hspice Simulation of SRAMDocument65 pagesHspice Simulation of SRAMYatheesh Kaggere100% (1)

- Device Monte Carlo Simulation Methodology of Two-Dimensional FinFET SlicesDocument8 pagesDevice Monte Carlo Simulation Methodology of Two-Dimensional FinFET SlicesGracia Meliolla Sitorus100% (1)

- Mosfet AtlasDocument2 pagesMosfet AtlasAnonymous eWMnRr70qNo ratings yet

- Timer Tc100d2 SGL Line 0908 (Tecalemit)Document6 pagesTimer Tc100d2 SGL Line 0908 (Tecalemit)NovakurniawanNo ratings yet

- Training Manual: Rev. Date DateDocument150 pagesTraining Manual: Rev. Date DateVision COMNo ratings yet

- HW6 Solution PDFDocument16 pagesHW6 Solution PDFYgor AguiarNo ratings yet

- Hspice Simulation of SRAM PDFDocument65 pagesHspice Simulation of SRAM PDFYatheesh KaggereNo ratings yet

- Seminar Report: Submitted By: Amena Tarique (16BEC027)Document25 pagesSeminar Report: Submitted By: Amena Tarique (16BEC027)Moon SkyNo ratings yet

- Lect8 SpiceDocument27 pagesLect8 SpiceishantNo ratings yet

- Thesis Report - Exploring Memristor TopologiesDocument59 pagesThesis Report - Exploring Memristor TopologiesSerdar BenderliNo ratings yet

- 018 RF Model Document V2d2Document91 pages018 RF Model Document V2d2Rogelio Manuel Higuera GonzalezNo ratings yet

- Introduction To Sentaurus TCADDocument47 pagesIntroduction To Sentaurus TCADvijayNo ratings yet

- Computer ArchitectureDocument104 pagesComputer ArchitectureapuurvaNo ratings yet

- Basic ARM9 Block DiagramDocument2 pagesBasic ARM9 Block Diagramhumtum_shriNo ratings yet

- ARM ArchitectureDocument6 pagesARM ArchitectureCarlos AraujoNo ratings yet

- ARM CORTEX M4 Memory LayoutDocument11 pagesARM CORTEX M4 Memory LayoutGurram KishoreNo ratings yet

- New Cortex-R Processors For Lte and 4g Mobile BasebandDocument6 pagesNew Cortex-R Processors For Lte and 4g Mobile BasebandSaiteja ReddyNo ratings yet

- 1st Interview Questions-QualcommDocument1 page1st Interview Questions-QualcommSandya VemuriNo ratings yet

- Eetop - CN Emx Virtuoso ManualDocument35 pagesEetop - CN Emx Virtuoso Manualhuyadong1234No ratings yet

- ESARM Unit-III and IV Slides MergedDocument301 pagesESARM Unit-III and IV Slides MergedShashipreetham LakkakulaNo ratings yet

- 14 NMDocument23 pages14 NMNikhilAKothariNo ratings yet

- Lab 10 NSGDocument3 pagesLab 10 NSGMuhammad Awais ShahNo ratings yet

- Aulas15 16Document16 pagesAulas15 16Pramod Reddy RNo ratings yet

- CMOS Process FlowDocument35 pagesCMOS Process Flowag21937570No ratings yet

- Sram 6TDocument5 pagesSram 6Taashish kumarNo ratings yet

- Cadence Redhat 6 InstallationDocument8 pagesCadence Redhat 6 InstallationBahram RN100% (1)

- Lecture 2 - ARM Instruction SetDocument42 pagesLecture 2 - ARM Instruction SetSuhaib AbugderaNo ratings yet

- A 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliDocument4 pagesA 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliAnika TahsinNo ratings yet

- Timeline AMDDocument6 pagesTimeline AMDRey DumpitNo ratings yet

- Sensori A Stato Solido LS Presentazione TCAD Sentaurus PDFDocument27 pagesSensori A Stato Solido LS Presentazione TCAD Sentaurus PDFBharath KumarNo ratings yet

- Chapter 4Document100 pagesChapter 4khgvouy hvogyflNo ratings yet

- On-Chip Bus: Speaker: Tian-Sheuan Chang July, 2004Document40 pagesOn-Chip Bus: Speaker: Tian-Sheuan Chang July, 2004Tarun GhoshNo ratings yet

- EE4S23 - ASIC Technology and Test SystemsDocument39 pagesEE4S23 - ASIC Technology and Test Systemsfahadmas872070No ratings yet

- 8k Bit Using 6t SramDocument8 pages8k Bit Using 6t SramSwati Navdeep AggarwalNo ratings yet

- Kunci Jawaban Soal Buku Computer and Communication Networks Nader F Mir Chapter 1Document8 pagesKunci Jawaban Soal Buku Computer and Communication Networks Nader F Mir Chapter 1Aditya IrawanNo ratings yet

- Vlsi Mtech Jntu Kakinada SyllabusDocument11 pagesVlsi Mtech Jntu Kakinada Syllabusaditya414No ratings yet

- 8257 DMA Controller:: To Fetch The Instruction To Decode The Instruction and To Execute The InstructionDocument25 pages8257 DMA Controller:: To Fetch The Instruction To Decode The Instruction and To Execute The Instructionsatyanarayana12No ratings yet

- Level 54 Bsim4Document13 pagesLevel 54 Bsim4Georgios SarrisNo ratings yet

- Unit Ii ArmDocument243 pagesUnit Ii ArmMani BharathiNo ratings yet

- Understanding About CMOS Fabrication TechnologyDocument4 pagesUnderstanding About CMOS Fabrication TechnologyJayesh RaghuwanshiNo ratings yet

- XilinxDocument20 pagesXilinxAvila Cruz JaimeNo ratings yet

- Wireless Sensor Network Simulators A Survey and Comparisons: Harsh SundaniDocument17 pagesWireless Sensor Network Simulators A Survey and Comparisons: Harsh Sundanisafdar-abbasNo ratings yet

- How To Use JTAG With ARM7 MCUDocument20 pagesHow To Use JTAG With ARM7 MCUGurpreet SinghNo ratings yet

- Cortex R4 White PaperDocument20 pagesCortex R4 White PaperRAJARAMNo ratings yet

- DVD2 JNTU Set1 SolutionsDocument12 pagesDVD2 JNTU Set1 Solutionsకిరణ్ కుమార్ పగడాలNo ratings yet

- Ec6111 - Vlsi DesignDocument9 pagesEc6111 - Vlsi DesignMegha SrivastavaNo ratings yet

- CN Lab Manual PDFDocument62 pagesCN Lab Manual PDFsandhiya .vNo ratings yet

- 8x4 SRAM in TSMC 0.25 M Technology: NtroductionDocument6 pages8x4 SRAM in TSMC 0.25 M Technology: NtroductionAdib NahiyanNo ratings yet

- Solid State Device Modeling 1Document199 pagesSolid State Device Modeling 1DarwinNo ratings yet

- Unit V Processes and Operating SystemsDocument37 pagesUnit V Processes and Operating SystemsManikandan Annamalai100% (1)

- 2011 - Advanced Technology For High Performance & Low Power ApplicationsDocument12 pages2011 - Advanced Technology For High Performance & Low Power Applicationsambica207No ratings yet

- Fifo DepthDocument1 pageFifo DepthSameer BadachiNo ratings yet

- Lab 05 To Perform Signal Companding in SimulinkDocument15 pagesLab 05 To Perform Signal Companding in SimulinkArshad AliNo ratings yet

- SRPWMC FinalDocument7 pagesSRPWMC Finalapi-340769184No ratings yet

- Timer 1Document6 pagesTimer 1joxenoNo ratings yet

- DSP Test1 CheatsheetDocument3 pagesDSP Test1 Cheatsheet201003489No ratings yet

- 71r-A14hmo-9h10 A14hm0-Ab10Document40 pages71r-A14hmo-9h10 A14hm0-Ab10Camila GuimarãesNo ratings yet

- Appendix E - CALPUFF Input FileDocument26 pagesAppendix E - CALPUFF Input FilewillygansNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Data Sheet 6ES7221-1BF32-0XB0: General InformationDocument3 pagesData Sheet 6ES7221-1BF32-0XB0: General InformationzeeshanNo ratings yet

- MM30 743 ManualDocument31 pagesMM30 743 ManualpadmawarNo ratings yet

- Panasonic KX-T2375MXW Service ManualDocument39 pagesPanasonic KX-T2375MXW Service Manualnifiyeb189No ratings yet

- LI-PO SizesDocument17 pagesLI-PO SizesmariorossiNo ratings yet

- HVAC Instruments: Clamp-On Ammeter VoltmeterDocument8 pagesHVAC Instruments: Clamp-On Ammeter VoltmeterMuhammad Jamshaid KhanNo ratings yet

- High Pressure Pure Air Generator (Hippag)Document2 pagesHigh Pressure Pure Air Generator (Hippag)BarisNo ratings yet

- v8 Sy PDFDocument12 pagesv8 Sy PDFozzy123No ratings yet

- Electronic Devices (Group-8)Document32 pagesElectronic Devices (Group-8)Saloni GargNo ratings yet

- Ad7606b 1623783Document73 pagesAd7606b 1623783Jeferson AlvesNo ratings yet

- Antm5&Eec廿: Professional AntennaDocument16 pagesAntm5&Eec廿: Professional AntennaabcdefghiklNo ratings yet

- High Fidelity Loudspeaker EnclosuresDocument52 pagesHigh Fidelity Loudspeaker EnclosuresEduardoNo ratings yet

- Mission 77 ManualDocument2 pagesMission 77 ManualPaulo Coutinho100% (1)

- Fundamentals of Vibration Measurement and Analysis ExplainedDocument13 pagesFundamentals of Vibration Measurement and Analysis ExplainedRLE2014No ratings yet

- Act Sheet For RoboticsDocument4 pagesAct Sheet For RoboticsErah Kim GomezNo ratings yet

- Tunstall Flamenco IP - WANTZ SOLUTION R1Document24 pagesTunstall Flamenco IP - WANTZ SOLUTION R1muhd faizNo ratings yet

- Door BellDocument12 pagesDoor Belliram fatimaNo ratings yet

- Dell S4112-ON Series Installation GuideDocument44 pagesDell S4112-ON Series Installation GuideLarryNo ratings yet

- Final Year SyllabusDocument12 pagesFinal Year SyllabusArvNo ratings yet

- A030A102 I8 201406 PartesDocument68 pagesA030A102 I8 201406 PartesMiguel Cabezas100% (1)

- Substation Engineering & LayoutDocument4 pagesSubstation Engineering & Layoutgulatimanish1985No ratings yet

- Accounting Seligram CaseDocument2 pagesAccounting Seligram CaseNadia Iqbal100% (1)

- B302 - LOAD LIST IPS Station For SEB DTD 04.10.2023Document1 pageB302 - LOAD LIST IPS Station For SEB DTD 04.10.2023Abdul Wajid AliNo ratings yet

- MAP3512Document15 pagesMAP3512KhalidNo ratings yet

- Construction of 500w12vinverter ChargerDocument12 pagesConstruction of 500w12vinverter ChargerAbba SaadNo ratings yet

- EE KonodiaDocument453 pagesEE KonodiaAaryan RajNo ratings yet

- Sony str-k760pDocument44 pagesSony str-k760pValtemir OliveiraNo ratings yet

- Connectores EatonDocument56 pagesConnectores EatonLeandro BustamanteNo ratings yet

- Design and Construction of Fuelless AC Generator Using Alternator Interfaced With An InverterDocument5 pagesDesign and Construction of Fuelless AC Generator Using Alternator Interfaced With An InverterEditor IJTSRDNo ratings yet