Professional Documents

Culture Documents

MPC5554 Microcontroller Product Brief

MPC5554 Microcontroller Product Brief

Uploaded by

h_878236333Copyright:

Available Formats

You might also like

- DES-3611.prepaway - Premium.exam.65q: Number: DES-3611 Passing Score: 800 Time Limit: 120 Min File Version: 1.1Document22 pagesDES-3611.prepaway - Premium.exam.65q: Number: DES-3611 Passing Score: 800 Time Limit: 120 Min File Version: 1.1Emre Halit POLATNo ratings yet

- E600 Core Product BriefDocument44 pagesE600 Core Product BriefaNo ratings yet

- Product Brief: MPC565PB/D Rev. 3, 2/2003 MPC565/MPC566 Product BriefDocument16 pagesProduct Brief: MPC565PB/D Rev. 3, 2/2003 MPC565/MPC566 Product BriefMohamedNo ratings yet

- SKEA64PB, Product Brief - Product BriefDocument14 pagesSKEA64PB, Product Brief - Product BriefMayank VyasNo ratings yet

- Pentium Processor Family: Benjamin Nicomedes For-Ian SandovalDocument32 pagesPentium Processor Family: Benjamin Nicomedes For-Ian SandovalIan John MontalboNo ratings yet

- KMC7457RX1000NC DatasheetzDocument72 pagesKMC7457RX1000NC DatasheetzRSX SNo ratings yet

- Familiariztion of Msp430 Launchpad (Repaired)Document38 pagesFamiliariztion of Msp430 Launchpad (Repaired)Aliya GNo ratings yet

- In-Circuit Emulator For MC68020/30: MC68020 MC68030 MC68EC020 MC68EC030Document21 pagesIn-Circuit Emulator For MC68020/30: MC68020 MC68030 MC68EC020 MC68EC030errNo ratings yet

- AVRONEDocument11 pagesAVRONEmekki1No ratings yet

- PIC18F66K80Document20 pagesPIC18F66K80Fernando PeixeiroNo ratings yet

- Module 2: ArchitectureDocument18 pagesModule 2: Architectureabs4everonlineNo ratings yet

- Module - 02 ArchitectureDocument18 pagesModule - 02 ArchitectureMaria MEKLINo ratings yet

- Embedded System Application: Serial CommunicationDocument71 pagesEmbedded System Application: Serial CommunicationMULLAIVANESH A VNo ratings yet

- Embedded Systems Embedded Processors-1Document7 pagesEmbedded Systems Embedded Processors-1Puspala ManojkumarNo ratings yet

- PIC24HJ128GP502Document390 pagesPIC24HJ128GP502Shaun Van HeerdenNo ratings yet

- PIC18 F45 K 50Document536 pagesPIC18 F45 K 50duknow2No ratings yet

- PIC18 (L) F2X/45K50: 28/40/44-Pin, Low-Power, High-Performance Microcontrollers With XLP TechnologyDocument536 pagesPIC18 (L) F2X/45K50: 28/40/44-Pin, Low-Power, High-Performance Microcontrollers With XLP TechnologyElías CeaNo ratings yet

- TMS 320C 54x - DSP Functional OverviewDocument52 pagesTMS 320C 54x - DSP Functional OverviewMuthu MadhavanNo ratings yet

- Ice 08Document21 pagesIce 08Google EyeNo ratings yet

- 32-Bit Power Architecture MCU For Automotive General Purpose Applications - Chorus FamilyDocument139 pages32-Bit Power Architecture MCU For Automotive General Purpose Applications - Chorus FamilyEcus ElectronicsNo ratings yet

- SPC 584 C 70 e 3Document153 pagesSPC 584 C 70 e 3sajeetverma047No ratings yet

- ELEC3300 - 04-Embedded System StructureDocument47 pagesELEC3300 - 04-Embedded System StructureKeith wongNo ratings yet

- Arm Cortex-M4 Processor DatasheetDocument10 pagesArm Cortex-M4 Processor DatasheetWajahat Riaz MirzaNo ratings yet

- Microprocessor and Microcontroller Module 5Document19 pagesMicroprocessor and Microcontroller Module 5dshyam1991No ratings yet

- MPC5643LDocument136 pagesMPC5643LNavya SreeNo ratings yet

- Tas 3202Document68 pagesTas 3202giang tranvanNo ratings yet

- PIC18 (L) F2X/45K50 USB Flash MCU Product BriefDocument10 pagesPIC18 (L) F2X/45K50 USB Flash MCU Product BriefkrishnaboopathyjNo ratings yet

- Silo - Tips - Alcatel Lucent Omnipcx Enterprise Communication Server RmabDocument12 pagesSilo - Tips - Alcatel Lucent Omnipcx Enterprise Communication Server RmabTallat MasoodNo ratings yet

- MPC7448 RISC Microprocessor Hardware Specifications: Freescale SemiconductorDocument60 pagesMPC7448 RISC Microprocessor Hardware Specifications: Freescale SemiconductorMurat GörükmezNo ratings yet

- Ocb Exchange PPT by Aadyant (India)Document11 pagesOcb Exchange PPT by Aadyant (India)aaadyant100% (2)

- Freescale Semiconductor MC68376BGVFT25 DatasheetDocument18 pagesFreescale Semiconductor MC68376BGVFT25 DatasheetAhmed Sherif CupoNo ratings yet

- Slas 396 DDocument66 pagesSlas 396 DAmin KhanNo ratings yet

- EFM8 Busy Bee Family EFM8BB1 Reference ManualDocument231 pagesEFM8 Busy Bee Family EFM8BB1 Reference ManualFrancesco MenichelliNo ratings yet

- Pentium Generations 2004Document19 pagesPentium Generations 2004Divya VinodNo ratings yet

- Digital Input / Output: F2833x Block DiagramDocument32 pagesDigital Input / Output: F2833x Block DiagramMaria MEKLINo ratings yet

- spc563m64l5Document128 pagesspc563m64l598x6f3rzNo ratings yet

- Efm 32 GGDocument1 pageEfm 32 GGJavier Pueyo SerranoNo ratings yet

- PLC FX3G MitsubishiDocument4 pagesPLC FX3G MitsubishiAnonymous T0KltPNo ratings yet

- EG4S20 DataSheet V1.5 EnglishDocument26 pagesEG4S20 DataSheet V1.5 EnglishspamNo ratings yet

- ELEC3300 06 InterruptDocument38 pagesELEC3300 06 InterruptKeith wongNo ratings yet

- DatasheetDocument120 pagesDatasheetSendi IndartoNo ratings yet

- A0b36apo Prednaska03 Memory enDocument90 pagesA0b36apo Prednaska03 Memory enLEONARDONo ratings yet

- PB 0135Document9 pagesPB 0135Ermanno LanzellottoNo ratings yet

- Sensorless Motor Control IC For Appliances: IRMCK343Document35 pagesSensorless Motor Control IC For Appliances: IRMCK343Gilvana Cristina FerreiraNo ratings yet

- Arm Cortex-M3 Processor DatasheetDocument10 pagesArm Cortex-M3 Processor DatasheetthuhienktvNo ratings yet

- Ecm S12X 070 1001: Motohawk Control SolutionsDocument13 pagesEcm S12X 070 1001: Motohawk Control SolutionsrfffffNo ratings yet

- Silicon Labs Efm8ub20f64g B QFP48R - C2053313Document57 pagesSilicon Labs Efm8ub20f64g B QFP48R - C2053313TNo ratings yet

- CS305 MPMC - Module-1Document44 pagesCS305 MPMC - Module-1anusumaNo ratings yet

- ELEC3300 - 03-Embedded System StructureDocument27 pagesELEC3300 - 03-Embedded System StructureKwun Hok ChongNo ratings yet

- Arm Cortex M7 Processor DatasheetDocument12 pagesArm Cortex M7 Processor DatasheetAlfonso Hernández MagdalenoNo ratings yet

- Am29F400AT/Am29F400AB: 4 Megabit (524,288 X 8-Bit/262,144 X 16-Bit) CMOS 5.0 Volt-Only, Sector Erase Flash MemoryDocument35 pagesAm29F400AT/Am29F400AB: 4 Megabit (524,288 X 8-Bit/262,144 X 16-Bit) CMOS 5.0 Volt-Only, Sector Erase Flash MemoryAndrey OliveiraNo ratings yet

- Marvell Armada 7040 Quad-Core Ca72 Processor With Marvell MochiDocument3 pagesMarvell Armada 7040 Quad-Core Ca72 Processor With Marvell MochiWu WeNo ratings yet

- Sistema Electronico Del Motor A Gas HyundaiDocument18 pagesSistema Electronico Del Motor A Gas HyundaiJusto PaniaguaNo ratings yet

- A29l160atv 70FDocument42 pagesA29l160atv 70Farond5318No ratings yet

- Parts Not Suitable For New DesignsDocument7 pagesParts Not Suitable For New DesignsGabriel RacovskyNo ratings yet

- WPC8765L WPC8769L Mobile Embedded Controller With SPI Flash Interface and MC-Compliant CIR Port (Revisions A4 and A5)Document5 pagesWPC8765L WPC8769L Mobile Embedded Controller With SPI Flash Interface and MC-Compliant CIR Port (Revisions A4 and A5)Jose FuentesNo ratings yet

- Spartan-3A DSP Platform Additional FeaturesDocument1 pageSpartan-3A DSP Platform Additional FeaturesThiện KhiêmNo ratings yet

- 8086 & 8088 Microprocessors: Spring 2013Document4 pages8086 & 8088 Microprocessors: Spring 2013Muhammad Fawad AbbasiNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- PlayStation 2 Architecture: Architecture of Consoles: A Practical Analysis, #12From EverandPlayStation 2 Architecture: Architecture of Consoles: A Practical Analysis, #12No ratings yet

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipFrom EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNo ratings yet

- EcoCoder Manual - 4.9.1Document227 pagesEcoCoder Manual - 4.9.1h_878236333No ratings yet

- EcoFlash User Manual - v1.1Document21 pagesEcoFlash User Manual - v1.1h_878236333No ratings yet

- Ecocal Manual: All Rights ReservedDocument93 pagesEcocal Manual: All Rights Reservedh_878236333No ratings yet

- f1 BH1747NUC E2Document372 pagesf1 BH1747NUC E2h_878236333No ratings yet

- Capacitors: David Frazier and John IngramDocument25 pagesCapacitors: David Frazier and John Ingramh_878236333No ratings yet

- Feel The Difference: The Proven Choice. Every TimeDocument12 pagesFeel The Difference: The Proven Choice. Every Timeh_878236333No ratings yet

- The Specifications of BX6680H: Details PDFDocument1 pageThe Specifications of BX6680H: Details PDFh_878236333No ratings yet

- wts Knowles - Fundamentals Capacitor book هامDocument52 pageswts Knowles - Fundamentals Capacitor book هامh_878236333No ratings yet

- WEG 10005056250 Ac Capacitors Safety and Application Manual enDocument32 pagesWEG 10005056250 Ac Capacitors Safety and Application Manual enh_878236333No ratings yet

- By The Soldering Experts: Highest Precision. Superior Reliability. Increased Productivity. All From One SourceDocument7 pagesBy The Soldering Experts: Highest Precision. Superior Reliability. Increased Productivity. All From One Sourceh_878236333No ratings yet

- WX Team: One Platform - Up To Every ChallengeDocument40 pagesWX Team: One Platform - Up To Every Challengeh_878236333No ratings yet

- 2016 PI Zero Smog EL GBDocument2 pages2016 PI Zero Smog EL GBh_878236333No ratings yet

- WX Team: One Platform - Up To Every ChallengeDocument21 pagesWX Team: One Platform - Up To Every Challengeh_878236333No ratings yet

- Series Configuration Package Channel VDS (V) VGS (V) ID Max. (A) PD Max. (W) RDS (On) at 10 V (Ohms)Document3 pagesSeries Configuration Package Channel VDS (V) VGS (V) ID Max. (A) PD Max. (W) RDS (On) at 10 V (Ohms)h_878236333No ratings yet

- Series Configuration Package Channel VDS (V) VGS (V) ID Max. (A) PD Max. (W) RDS (On) at 10 V (Ohms)Document3 pagesSeries Configuration Package Channel VDS (V) VGS (V) ID Max. (A) PD Max. (W) RDS (On) at 10 V (Ohms)h_878236333No ratings yet

- SQ1440EH Product BundleDocument19 pagesSQ1440EH Product Bundleh_878236333No ratings yet

- On-Line Thermograhpic IR Camera: Features and Benefits IntroduceDocument2 pagesOn-Line Thermograhpic IR Camera: Features and Benefits Introduceh_878236333No ratings yet

- Series Configuration Package Channel VDS (V) VGS (V) ID Max. (A) PD Max. (W) RDS (On) at 10 V (Ohms)Document3 pagesSeries Configuration Package Channel VDS (V) VGS (V) ID Max. (A) PD Max. (W) RDS (On) at 10 V (Ohms)h_878236333No ratings yet

- Powerpak® So-8l PackageDocument9 pagesPowerpak® So-8l Packageh_878236333No ratings yet

- Series Configuration Package Channel VDS (V) VGS (V) ID Max. (A) PD Max. (W)Document3 pagesSeries Configuration Package Channel VDS (V) VGS (V) ID Max. (A) PD Max. (W)h_878236333No ratings yet

- Computr List SepDocument3 pagesComputr List SepМиљан МиљанићNo ratings yet

- Fire Alarm Systems - Panel ControllerDocument4 pagesFire Alarm Systems - Panel ControllerĐức Thương VũNo ratings yet

- The Advanced Way of Data Recovery PDFDocument7 pagesThe Advanced Way of Data Recovery PDFPrince TreasureNo ratings yet

- Intelligent Single and Double Loop Fire Alarm Panel: GST200-2/NDocument3 pagesIntelligent Single and Double Loop Fire Alarm Panel: GST200-2/NheshamNo ratings yet

- SiFive U500 vc707 Gettingstarted v0.2Document24 pagesSiFive U500 vc707 Gettingstarted v0.2Shiva prasadNo ratings yet

- Horizontal Vs Vertical Micro-ProgramDocument3 pagesHorizontal Vs Vertical Micro-Programtanishqshukla17pixelNo ratings yet

- Edc Lab: 4. Facilities and Technical SupportDocument3 pagesEdc Lab: 4. Facilities and Technical SupportTirumalarao PechettyNo ratings yet

- 1200 - Parts and DiagramsDocument16 pages1200 - Parts and Diagramsetc_lctNo ratings yet

- IBM System Storage DS8000 Series: - Virtualization ConceptsDocument16 pagesIBM System Storage DS8000 Series: - Virtualization ConceptssreenathonwebNo ratings yet

- Digital Design: Register-Transfer Level (RTL) DesignDocument88 pagesDigital Design: Register-Transfer Level (RTL) DesignmasrinaNo ratings yet

- Cobra LS 1900 Series: Smart LineDocument2 pagesCobra LS 1900 Series: Smart LineBradNo ratings yet

- Release Notes 5.8 SR1.EnDocument24 pagesRelease Notes 5.8 SR1.EndachronicmasterNo ratings yet

- cg-500 Quick-GuideDocument120 pagescg-500 Quick-Guideapi-270816603No ratings yet

- 3.2.qr-Code Based Information Access System in Shopping MallDocument4 pages3.2.qr-Code Based Information Access System in Shopping MallHaris AsrofiNo ratings yet

- ATXW-5520 High Performance Westmere Long Life EATX Industrial Motherboard DatasheetDocument4 pagesATXW-5520 High Performance Westmere Long Life EATX Industrial Motherboard DatasheetDavid LippincottNo ratings yet

- Instruction Set, Addressing Modes, Assembler DirectivesDocument9 pagesInstruction Set, Addressing Modes, Assembler Directivessiddharth singhNo ratings yet

- DualCam Update Procedure - V3Document2 pagesDualCam Update Procedure - V3Benjamim LangaNo ratings yet

- Toshiba Satellite M645Document4 pagesToshiba Satellite M645hectorhscNo ratings yet

- Stm32f401re User ManualDocument54 pagesStm32f401re User Manualdanz1994No ratings yet

- Chapter 6 PipeliningDocument58 pagesChapter 6 Pipeliningvinoliamanohar100% (1)

- Tablet Study Compatible Devices and Device Check - February 2023Document4 pagesTablet Study Compatible Devices and Device Check - February 2023Aladino BernaldezNo ratings yet

- MFT Remote Controller: User's ManualDocument9 pagesMFT Remote Controller: User's ManualGhallab AlsadehNo ratings yet

- Experiment No. 05Document3 pagesExperiment No. 05Eayashen ArafatNo ratings yet

- Configuration Control With The S7-1500 and ET 200SPDocument37 pagesConfiguration Control With The S7-1500 and ET 200SPalan083No ratings yet

- CISCO IOS UpgradationDocument3 pagesCISCO IOS UpgradationSundaramoorthi JNo ratings yet

- Basic ICT Skills Class 9 Questions and AnswersDocument5 pagesBasic ICT Skills Class 9 Questions and AnswersTauheed KhanNo ratings yet

- Ss90-Installation GuideDocument87 pagesSs90-Installation Guidealoysobeck1988No ratings yet

- MM Computer Journal 143 2006 JanuaryDocument170 pagesMM Computer Journal 143 2006 JanuaryTechne PhobosNo ratings yet

- Monitor - HarmonyWolrd 2Document15 pagesMonitor - HarmonyWolrd 2Sebastian100% (1)

MPC5554 Microcontroller Product Brief

MPC5554 Microcontroller Product Brief

Uploaded by

h_878236333Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

MPC5554 Microcontroller Product Brief

MPC5554 Microcontroller Product Brief

Uploaded by

h_878236333Copyright:

Available Formats

Freescale Semiconductor MPC5554PB

Rev. 2.2, 02/2006

Product Brief

MPC5554 Microcontroller

Product Brief

The MPC5554 is the first member of a family of next Table of Contents

generation microcontrollers based on the PowerPC 1 Block Diagram .....................................................3

2 Features ..............................................................4

Book E architecture that enhances the PowerPC

architecture’s fit in embedded applications. It is 100%

user mode compatible (with floating point library) with

the classic PowerPC instruction set. This document

provides an overview of the MPC5554 microcontroller

features, including the major functional components.

The MPC5554 device’s on-chip modules include the

following:

• Single issue, 32-bit PowerPC Book E-compliant

e200z6 CPU core complex

• 64-channel enhanced direct memory access

controller (eDMA)

• Interrupt controller (INTC) capable of handling

286 selectable-priority interrupt sources

• Frequency modulated phase-locked loop

(FMPLL)

• External bus interface (EBI) with error

correction status module (ECSM)

• System integration unit (SIU)

© Freescale Semiconductor, Inc., 2005. All rights reserved.

• 2 Mbytes on-chip Flash with Flash bus interface unit (FBIU)

• 64 Kbytes on-chip static RAM

• Boot assist module (BAM)

• 24-channel enhanced modular I/O system (eMIOS)

• 2 enhanced time processor unit (eTPU) engines. Each eTPU engine controls 32 hardware

channels.

• Enhanced queued analog-to-digital converter (eQADC)

• 4 deserial serial peripheral interface (DSPI) modules

• 2 enhanced serial communication interface (eSCI) modules

• 3 controller area network (FlexCAN) modules

• Nexus development interface (NDI) per IEEE-ISTO 5001-2003 standard

• Device/board test support per Joint Test Action Group (JTAG) of IEEE (IEEE 1149.1)

To locate any published errata or updates for this document, refer to the web site at

http://www.freescale.com.

MPC5554 Microcontroller Product Brief, Rev. 2.2

2 Freescale Semiconductor

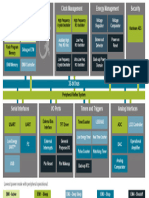

Block Diagram

1 Block Diagram

Figure 1 shows a top-level block diagram of the MPC5554.

e200z6 Core

1.5V

Signal 64-bit General Core Timers

Regulator

Processing Purpose Unit

Control

Engine Registers (FIT, TB, DEC)

Integer

Execution Special Exception Interrupt Controller

Unit Purpose Handler

FMPLL Registers

Multiply

Unit Instruction

Unit Unified 32-Kbyte

Cache

JTAG

Branch

Nexus Prediction Unit Memory

Interface Nexus Management

Load/Store Unit Unit

eDMA External

Master

External Bus Interface

64

channels Interface

Master Master Master

Crossbar Switch (XBAR)

Slave Slave Slave Slave Slave

Flash SRAM

2Mbyte 64 Kbyte Boot

Assist

System/Bus Module

Integration

Peripheral Bridge A (PBRIDGE_A) Peripheral Bridge B (PBRIDGE_B)

3K Data eQADC

FlexCAN

FlexCAN

FlexCAN

eTPU RAM eTPU eMIOS ADCi

DSPI

DSPI

DSPI

DSPI

eSCI

eSCI

32 32 24

ADC

ADC

channel 16K Code channel channel

RAM

AMUX

LEGEND

MPC5500 Device Module Acronyms e200z6 Core Component Acronyms

CAN – Controller area network (FlexCAN) DEC – Decrementer

DSPI – Deserial/serial peripheral interface FIT – Fixed interval timer

DMA – Enhanced direct memory access TB – Time base

eMIOS – Enhanced modular I/O system WDT – Watchdog timer

eQADC – Enhanced queued analog/digital converter

eSCI – Enhanced serial communications interface

eTPU – Enhanced time processing units

FMPLL – Frequency modulated phase-locked loop

SRAM – Static RAM

Figure 1. MPC5554 Block Diagram

MPC5554 Microcontroller Product Brief, Rev. 2.2

Freescale Semiconductor 3

Features

2 Features

This section provides a high-level description of the major features of the MPC5554.

• High performance e200z6 core processor

— 32-bit PowerPC Book E compliant CPU

— 32 64-bit general-purpose registers (GPRs)

— Memory management unit (MMU) with 32-entry, fully-associative translation look-aside

buffer (TLB)

— Branch processing unit

— Fully pipelined load/store unit

— 32-Kbyte unified cache with line locking

– 8-way set associative

– 2 32-bit fetches per clock

– 8-entry store buffer

– Way locking

– Supports assigning cache as instruction or data only on a per way basis

– Supports tag and data parity

— Vectored interrupt support

— Interrupt latency < 70 ns @132MHz (measured from interrupt request to execution of first

instruction of interrupt exception handler)

— Reservation instructions for implementing read-modify-write constructs (internal SRAM and

Flash)

— Signal processing engine (SPE) auxiliary processing unit (APU) operating on 64-bit GPRs

— Floating point

– IEEE 754 compatible with software wrapper

– Single precision in hardware and double precision with software library

– Conversion instructions between single precision floating point and fixed point

— Long cycle time instructions, except for guarded loads, do not increase interrupt latency in the

MPC5554. To reduce latency, long cycle time instructions are aborted upon interrupt requests.

— Extensive system development support through Nexus debug module

• Crossbar switch (XBAR)

— 3 master ports; 5 slave ports

— 32-bit address bus; 64-bit data bus

— Simultaneous accesses from different masters to different slaves (there is no clock penalty

when a parked master accesses a slave)

MPC5554 Microcontroller Product Brief, Rev. 2.2

4 Freescale Semiconductor

Features

• Enhanced direct memory access (eDMA) controller

— 64 channels support independent 8-, 16-, 32-, or 64-bit single value or block transfers

— Supports variable sized queues and circular queues

— Source and destination address registers are independently configured to post-increment or

remain constant

— Each transfer is initiated by a peripheral, CPU, or eDMA channel request

— Each eDMA channel can optionally send an interrupt request to the CPU on completion of a

single value or block transfer

• Interrupt controller (INTC)

— 308 total interrupt vectors

– 278 peripheral interrupt requests

– plus 8 software setable sources

– plus 22 reserved interrupts

— Unique 9-bit vector per interrupt source

— 16 priority levels with fixed hardware arbitration within priority levels for each interrupt

source

— Priority elevation for shared resources

• Frequency modulated phase-locked loop (FMPLL)

— Input clock frequency from 8 MHz to 20 MHz

— Current controlled oscillator (ICO) range from 50 MHz to maximum device frequency

— Reduced frequency divider (RFD) for reduced frequency operation without re-lock

— 4 selectable modes of operation

— Programmable frequency modulation

— Lock detect circuitry continuously monitors lock status

— Loss of clock (LOC) detection for reference and feedback clocks

— Self-clocked mode (SCM) operation

— On-chip loop filter (reduces number of external components required)

— Engineering clock output

• External bus interface (EBI)

— 1.8V–3.3V I/O nominal I/O voltage

— Memory controller with support for various memory types

— 32-bit data bus and 24-bit address bus with transfer size indication

— Selectable drive strength

— Configurable bus speed modes

— Support for external master accesses to internal addresses

— Burst support

MPC5554 Microcontroller Product Brief, Rev. 2.2

Freescale Semiconductor 5

Features

— Bus monitor

— Chip selects: 4 chip select (CS[0:3]) signals

— Configurable wait states

• System integration unit (SIU)

— Centralized GPIO control of 214 I/O and bus pins

— Centralized pad control on a per-pin basis

— System reset monitoring and generation

— External interrupt inputs, filtering, and control

• Error correction status module (ECSM)

— Configurable error-correcting codes (ECC) reporting for internal SRAM and Flash memories

• On-chip Flash

— 2 Mbytes burst Flash memory

— 256K × 64 bit configuration

— Censorship protection scheme to prevent Flash content visibility

— Hardware read-while-write feature that allows blocks to be erased/programmed while other

blocks are being read (used for EEPROM emulation and data calibration)

— 20 blocks, ranging from 16 Kbytes to 128 Kbytes, to support features such as boot block,

operating system block, and EEPROM emulation

— Read while write with multiple partitions

— Parallel programming mode to support rapid end of line programming

— Hardware programming state machine

• Configurable cache memory, 32-Kbyte

— 8-way set-associative, unified (instruction and data) cache

• On-chip, internal static RAM (SRAM)

— 64-Kbyte general-purpose RAM; 32 Kbytes on standby power

— ECC performs single bit correction, double bit error detection

• Boot assist module (BAM)

— Enables and manages the transition of MCU from reset to user code execution in the

following configurations:

– User application can boot from internal or external Flash memory

– Download and execution of code via FlexCAN or eSCI

• Enhanced modular I/O system (eMIOS)

— 24 orthogonal channels with double action, PWM, and modulus counter functionality

— Supports all DASM and PWM modes of MIOS14 (MPC5xx)

— 4 selectable time bases plus shared time or angle counter bus

— DMA and interrupt request support

MPC5554 Microcontroller Product Brief, Rev. 2.2

6 Freescale Semiconductor

Features

— Motor control capability

• Enhanced time processor unit (eTPU)

— MPC5554 has 2 eTPU engines

— Each eTPU engine is an event-triggered timer subsystem

— High level assembler/compiler

— 32 channels per engine

— 24-bit timer resolution

— 16-Kbyte shared code memory

— 3-Kbyte shared data memory

— Variable number of parameters allocatable per channel

— Double match/capture channels

— Angle clock hardware support

— Shared time or angle counter bus for all eTPU and eMIOS modules

— DMA and interrupt request support

— Nexus Class 3 Debug support (with some Class 4 support)

• Enhanced queued analog/digital converter (eQADC)

— 2 independent ADCs with 12-bit A/D resolution

— Common mode conversion range of 0–5V

— 40 single-ended inputs channels, expandable to 65 channels with external multiplexers

— 4 pairs of differential analog input channels.

— 10-bit accuracy at 400 ksamples/s, 8-bit accuracy at 800 ksamples/s

— Supports 6 FIFO queues with fixed priority.

— Queue modes with priority-based preemption; initiated by software command, internal (eTPU

and eMIOS), or external triggers

— DMA and interrupt request support

— Supports all functional modes from QADC (MPC5xx family)

• 4 Deserial serial peripheral interface modules (DSPI)

— Serial peripheral interface (SPI)

– Full duplex communication ports with interrupt and eDMA request support

– Supports all functional modes from QSPI submodule of QSMCM (MPC5xx family)

– Support for queues in RAM

– 6 chip selects, expandable to 64 with external demultiplexers

– Programmable frame size, baud rate, clock delay, and clock phase on a per frame basis

– Modified SPI mode for interfacing to peripherals with longer setup time requirements

— Deserial serial interface (DSI)

– Pin reduction by hardware serialization and deserialization of eTPU and eMIOS channels

MPC5554 Microcontroller Product Brief, Rev. 2.2

Freescale Semiconductor 7

Features

– Chaining of DSI submodules

– Triggered transfer control and change in data transfer control (for reduced EMI)

• 2 enhanced serial communication interface (eSCI) modules

— UART mode provides NRZ format and half or full duplex interface

— eSCI bit rate up to 1 Mbps

— Advanced error detection, and optional parity generation and detection

— Word length programmable as 8 or 9 bits

— Separately enabled transmitter and receiver

— LIN Support

— DMA support

— Interrupt request support

• 3 FlexCANs

— 64 message buffers each

— Full implementation of the CAN protocol specification, Version 2.0B

— Based on and including all existing features of the Freescale TouCAN module

— Programmable acceptance filters

— Short latency time for high priority transmit messages

— Arbitration scheme according to message ID or message buffer number

— Listen only mode capabilities

— Programmable clock source: system clock or oscillator clock

• Nexus development interface (NDI)

— Per IEEE-ISTO 5001-2003

— Real time development support for e200z6 core and eTPU engines through Nexus Class 3

(some Class 4 support)

— Data trace of eDMA accesses

— Read and write access

— Configured via the IEEE 1149.1 (JTAG) port

— High bandwidth mode for fast message transmission

— Reduced bandwidth mode for reduced pin usage

• IEEE 1149.1 JTAG controller (JTAGC)

— IEEE 1149.1-2001 Test Access Port (TAP) interface

— A JCOMP input that provides the ability to share the TAP. Selectable modes of operation

include JTAGC/debug or normal system operation.

— A 5-bit instruction register that supports IEEE 1149.1-2001 defined instructions

— A 5-bit instruction register that supports additional public instructions

— 3 test data registers: bypass, boundary scan, and device identification

MPC5554 Microcontroller Product Brief, Rev. 2.2

8 Freescale Semiconductor

Features

— A TAP controller state machine that controls the operation of the data registers, instruction

register and associated circuitry

• Voltage regulator controller

— Provides a low cost solution to power the core logic. It reduces the number of power supplies

required from the customer power supply chip.

• POR block

— Provides initial reset condition up to the voltage at which pins (RESET) can be read safely. It

does not guarantee the safe operation of the chip at specified minimum operating voltages.

MPC5554 Microcontroller Product Brief, Rev. 2.2

Freescale Semiconductor 9

How to Reach Us:

Home Page:

www.freescale.com

E-mail:

support@freescale.com

USA/Europe or Locations Not Listed:

Freescale Semiconductor

Technical Information Center, CH370

1300 N. Alma School Road

Chandler, Arizona 85224

+1-800-521-6274 or +1-480-768-2130

support@freescale.com

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center

Schatzbogen 7

81829 Muenchen, Germany

+44 1296 380 456 (English)

+46 8 52200080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

support@freescale.com

Japan:

Freescale Semiconductor Japan Ltd. Information in this document is provided solely to enable system and

Headquarters software implementers to use Freescale Semiconductor products. There are

ARCO Tower 15F no express or implied copyright licenses granted hereunder to design or

1-8-1, Shimo-Meguro, Meguro-ku, fabricate any integrated circuits or integrated circuits based on the

Tokyo 153-0064, Japan information in this document.

0120 191014 or +81 3 5437 9125

support.japan@freescale.com Freescale Semiconductor reserves the right to make changes without further

notice to any products herein. Freescale Semiconductor makes no warranty,

Asia/Pacific: representation or guarantee regarding the suitability of its products for any

Freescale Semiconductor Hong Kong Ltd. particular purpose, nor does Freescale Semiconductor assume any liability

arising out of the application or use of any product or circuit, and specifically

Technical Information Center

disclaims any and all liability, including without limitation consequential or

2 Dai King Street incidental damages. “Typical” parameters that may be provided in Freescale

Tai Po Industrial Estate Semiconductor data sheets and/or specifications can and do vary in different

Tai Po, N.T., Hong Kong applications and actual performance may vary over time. All operating

+800 2666 8080 parameters, including “Typicals”, must be validated for each customer

support.asia@freescale.com application by customer’s technical experts. Freescale Semiconductor does

not convey any license under its patent rights nor the rights of others.

For Literature Requests Only: Freescale Semiconductor products are not designed, intended, or authorized

for use as components in systems intended for surgical implant into the body,

Freescale Semiconductor Literature Distribution Center

or other applications intended to support or sustain life, or for any other

P.O. Box 5405 application in which the failure of the Freescale Semiconductor product could

Denver, Colorado 80217 create a situation where personal injury or death may occur. Should Buyer

1-800-441-2447 or 303-675-2140 purchase or use Freescale Semiconductor products for any such unintended

Fax: 303-675-2150 or unauthorized application, Buyer shall indemnify and hold Freescale

LDCForFreescaleSemiconductor@hibbertgroup.com Semiconductor and its officers, employees, subsidiaries, affiliates, and

distributors harmless against all claims, costs, damages, and expenses, and

reasonable attorney fees arising out of, directly or indirectly, any claim of

personal injury or death associated with such unintended or unauthorized

use, even if such claim alleges that Freescale Semiconductor was negligent

regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale

Semiconductor, Inc. All other product or service names are the property

of their respective owners. The described product contains a

PowerPC processor core. The PowerPC name is a trademark of IBM Corp.

and used under license.

© Freescale Semiconductor, Inc. 2005. All rights reserved.

MPC5554PB

Rev. 2.2

02/2006

You might also like

- DES-3611.prepaway - Premium.exam.65q: Number: DES-3611 Passing Score: 800 Time Limit: 120 Min File Version: 1.1Document22 pagesDES-3611.prepaway - Premium.exam.65q: Number: DES-3611 Passing Score: 800 Time Limit: 120 Min File Version: 1.1Emre Halit POLATNo ratings yet

- E600 Core Product BriefDocument44 pagesE600 Core Product BriefaNo ratings yet

- Product Brief: MPC565PB/D Rev. 3, 2/2003 MPC565/MPC566 Product BriefDocument16 pagesProduct Brief: MPC565PB/D Rev. 3, 2/2003 MPC565/MPC566 Product BriefMohamedNo ratings yet

- SKEA64PB, Product Brief - Product BriefDocument14 pagesSKEA64PB, Product Brief - Product BriefMayank VyasNo ratings yet

- Pentium Processor Family: Benjamin Nicomedes For-Ian SandovalDocument32 pagesPentium Processor Family: Benjamin Nicomedes For-Ian SandovalIan John MontalboNo ratings yet

- KMC7457RX1000NC DatasheetzDocument72 pagesKMC7457RX1000NC DatasheetzRSX SNo ratings yet

- Familiariztion of Msp430 Launchpad (Repaired)Document38 pagesFamiliariztion of Msp430 Launchpad (Repaired)Aliya GNo ratings yet

- In-Circuit Emulator For MC68020/30: MC68020 MC68030 MC68EC020 MC68EC030Document21 pagesIn-Circuit Emulator For MC68020/30: MC68020 MC68030 MC68EC020 MC68EC030errNo ratings yet

- AVRONEDocument11 pagesAVRONEmekki1No ratings yet

- PIC18F66K80Document20 pagesPIC18F66K80Fernando PeixeiroNo ratings yet

- Module 2: ArchitectureDocument18 pagesModule 2: Architectureabs4everonlineNo ratings yet

- Module - 02 ArchitectureDocument18 pagesModule - 02 ArchitectureMaria MEKLINo ratings yet

- Embedded System Application: Serial CommunicationDocument71 pagesEmbedded System Application: Serial CommunicationMULLAIVANESH A VNo ratings yet

- Embedded Systems Embedded Processors-1Document7 pagesEmbedded Systems Embedded Processors-1Puspala ManojkumarNo ratings yet

- PIC24HJ128GP502Document390 pagesPIC24HJ128GP502Shaun Van HeerdenNo ratings yet

- PIC18 F45 K 50Document536 pagesPIC18 F45 K 50duknow2No ratings yet

- PIC18 (L) F2X/45K50: 28/40/44-Pin, Low-Power, High-Performance Microcontrollers With XLP TechnologyDocument536 pagesPIC18 (L) F2X/45K50: 28/40/44-Pin, Low-Power, High-Performance Microcontrollers With XLP TechnologyElías CeaNo ratings yet

- TMS 320C 54x - DSP Functional OverviewDocument52 pagesTMS 320C 54x - DSP Functional OverviewMuthu MadhavanNo ratings yet

- Ice 08Document21 pagesIce 08Google EyeNo ratings yet

- 32-Bit Power Architecture MCU For Automotive General Purpose Applications - Chorus FamilyDocument139 pages32-Bit Power Architecture MCU For Automotive General Purpose Applications - Chorus FamilyEcus ElectronicsNo ratings yet

- SPC 584 C 70 e 3Document153 pagesSPC 584 C 70 e 3sajeetverma047No ratings yet

- ELEC3300 - 04-Embedded System StructureDocument47 pagesELEC3300 - 04-Embedded System StructureKeith wongNo ratings yet

- Arm Cortex-M4 Processor DatasheetDocument10 pagesArm Cortex-M4 Processor DatasheetWajahat Riaz MirzaNo ratings yet

- Microprocessor and Microcontroller Module 5Document19 pagesMicroprocessor and Microcontroller Module 5dshyam1991No ratings yet

- MPC5643LDocument136 pagesMPC5643LNavya SreeNo ratings yet

- Tas 3202Document68 pagesTas 3202giang tranvanNo ratings yet

- PIC18 (L) F2X/45K50 USB Flash MCU Product BriefDocument10 pagesPIC18 (L) F2X/45K50 USB Flash MCU Product BriefkrishnaboopathyjNo ratings yet

- Silo - Tips - Alcatel Lucent Omnipcx Enterprise Communication Server RmabDocument12 pagesSilo - Tips - Alcatel Lucent Omnipcx Enterprise Communication Server RmabTallat MasoodNo ratings yet

- MPC7448 RISC Microprocessor Hardware Specifications: Freescale SemiconductorDocument60 pagesMPC7448 RISC Microprocessor Hardware Specifications: Freescale SemiconductorMurat GörükmezNo ratings yet

- Ocb Exchange PPT by Aadyant (India)Document11 pagesOcb Exchange PPT by Aadyant (India)aaadyant100% (2)

- Freescale Semiconductor MC68376BGVFT25 DatasheetDocument18 pagesFreescale Semiconductor MC68376BGVFT25 DatasheetAhmed Sherif CupoNo ratings yet

- Slas 396 DDocument66 pagesSlas 396 DAmin KhanNo ratings yet

- EFM8 Busy Bee Family EFM8BB1 Reference ManualDocument231 pagesEFM8 Busy Bee Family EFM8BB1 Reference ManualFrancesco MenichelliNo ratings yet

- Pentium Generations 2004Document19 pagesPentium Generations 2004Divya VinodNo ratings yet

- Digital Input / Output: F2833x Block DiagramDocument32 pagesDigital Input / Output: F2833x Block DiagramMaria MEKLINo ratings yet

- spc563m64l5Document128 pagesspc563m64l598x6f3rzNo ratings yet

- Efm 32 GGDocument1 pageEfm 32 GGJavier Pueyo SerranoNo ratings yet

- PLC FX3G MitsubishiDocument4 pagesPLC FX3G MitsubishiAnonymous T0KltPNo ratings yet

- EG4S20 DataSheet V1.5 EnglishDocument26 pagesEG4S20 DataSheet V1.5 EnglishspamNo ratings yet

- ELEC3300 06 InterruptDocument38 pagesELEC3300 06 InterruptKeith wongNo ratings yet

- DatasheetDocument120 pagesDatasheetSendi IndartoNo ratings yet

- A0b36apo Prednaska03 Memory enDocument90 pagesA0b36apo Prednaska03 Memory enLEONARDONo ratings yet

- PB 0135Document9 pagesPB 0135Ermanno LanzellottoNo ratings yet

- Sensorless Motor Control IC For Appliances: IRMCK343Document35 pagesSensorless Motor Control IC For Appliances: IRMCK343Gilvana Cristina FerreiraNo ratings yet

- Arm Cortex-M3 Processor DatasheetDocument10 pagesArm Cortex-M3 Processor DatasheetthuhienktvNo ratings yet

- Ecm S12X 070 1001: Motohawk Control SolutionsDocument13 pagesEcm S12X 070 1001: Motohawk Control SolutionsrfffffNo ratings yet

- Silicon Labs Efm8ub20f64g B QFP48R - C2053313Document57 pagesSilicon Labs Efm8ub20f64g B QFP48R - C2053313TNo ratings yet

- CS305 MPMC - Module-1Document44 pagesCS305 MPMC - Module-1anusumaNo ratings yet

- ELEC3300 - 03-Embedded System StructureDocument27 pagesELEC3300 - 03-Embedded System StructureKwun Hok ChongNo ratings yet

- Arm Cortex M7 Processor DatasheetDocument12 pagesArm Cortex M7 Processor DatasheetAlfonso Hernández MagdalenoNo ratings yet

- Am29F400AT/Am29F400AB: 4 Megabit (524,288 X 8-Bit/262,144 X 16-Bit) CMOS 5.0 Volt-Only, Sector Erase Flash MemoryDocument35 pagesAm29F400AT/Am29F400AB: 4 Megabit (524,288 X 8-Bit/262,144 X 16-Bit) CMOS 5.0 Volt-Only, Sector Erase Flash MemoryAndrey OliveiraNo ratings yet

- Marvell Armada 7040 Quad-Core Ca72 Processor With Marvell MochiDocument3 pagesMarvell Armada 7040 Quad-Core Ca72 Processor With Marvell MochiWu WeNo ratings yet

- Sistema Electronico Del Motor A Gas HyundaiDocument18 pagesSistema Electronico Del Motor A Gas HyundaiJusto PaniaguaNo ratings yet

- A29l160atv 70FDocument42 pagesA29l160atv 70Farond5318No ratings yet

- Parts Not Suitable For New DesignsDocument7 pagesParts Not Suitable For New DesignsGabriel RacovskyNo ratings yet

- WPC8765L WPC8769L Mobile Embedded Controller With SPI Flash Interface and MC-Compliant CIR Port (Revisions A4 and A5)Document5 pagesWPC8765L WPC8769L Mobile Embedded Controller With SPI Flash Interface and MC-Compliant CIR Port (Revisions A4 and A5)Jose FuentesNo ratings yet

- Spartan-3A DSP Platform Additional FeaturesDocument1 pageSpartan-3A DSP Platform Additional FeaturesThiện KhiêmNo ratings yet

- 8086 & 8088 Microprocessors: Spring 2013Document4 pages8086 & 8088 Microprocessors: Spring 2013Muhammad Fawad AbbasiNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- PlayStation 2 Architecture: Architecture of Consoles: A Practical Analysis, #12From EverandPlayStation 2 Architecture: Architecture of Consoles: A Practical Analysis, #12No ratings yet

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipFrom EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNo ratings yet

- EcoCoder Manual - 4.9.1Document227 pagesEcoCoder Manual - 4.9.1h_878236333No ratings yet

- EcoFlash User Manual - v1.1Document21 pagesEcoFlash User Manual - v1.1h_878236333No ratings yet

- Ecocal Manual: All Rights ReservedDocument93 pagesEcocal Manual: All Rights Reservedh_878236333No ratings yet

- f1 BH1747NUC E2Document372 pagesf1 BH1747NUC E2h_878236333No ratings yet

- Capacitors: David Frazier and John IngramDocument25 pagesCapacitors: David Frazier and John Ingramh_878236333No ratings yet

- Feel The Difference: The Proven Choice. Every TimeDocument12 pagesFeel The Difference: The Proven Choice. Every Timeh_878236333No ratings yet

- The Specifications of BX6680H: Details PDFDocument1 pageThe Specifications of BX6680H: Details PDFh_878236333No ratings yet

- wts Knowles - Fundamentals Capacitor book هامDocument52 pageswts Knowles - Fundamentals Capacitor book هامh_878236333No ratings yet

- WEG 10005056250 Ac Capacitors Safety and Application Manual enDocument32 pagesWEG 10005056250 Ac Capacitors Safety and Application Manual enh_878236333No ratings yet

- By The Soldering Experts: Highest Precision. Superior Reliability. Increased Productivity. All From One SourceDocument7 pagesBy The Soldering Experts: Highest Precision. Superior Reliability. Increased Productivity. All From One Sourceh_878236333No ratings yet

- WX Team: One Platform - Up To Every ChallengeDocument40 pagesWX Team: One Platform - Up To Every Challengeh_878236333No ratings yet

- 2016 PI Zero Smog EL GBDocument2 pages2016 PI Zero Smog EL GBh_878236333No ratings yet

- WX Team: One Platform - Up To Every ChallengeDocument21 pagesWX Team: One Platform - Up To Every Challengeh_878236333No ratings yet

- Series Configuration Package Channel VDS (V) VGS (V) ID Max. (A) PD Max. (W) RDS (On) at 10 V (Ohms)Document3 pagesSeries Configuration Package Channel VDS (V) VGS (V) ID Max. (A) PD Max. (W) RDS (On) at 10 V (Ohms)h_878236333No ratings yet

- Series Configuration Package Channel VDS (V) VGS (V) ID Max. (A) PD Max. (W) RDS (On) at 10 V (Ohms)Document3 pagesSeries Configuration Package Channel VDS (V) VGS (V) ID Max. (A) PD Max. (W) RDS (On) at 10 V (Ohms)h_878236333No ratings yet

- SQ1440EH Product BundleDocument19 pagesSQ1440EH Product Bundleh_878236333No ratings yet

- On-Line Thermograhpic IR Camera: Features and Benefits IntroduceDocument2 pagesOn-Line Thermograhpic IR Camera: Features and Benefits Introduceh_878236333No ratings yet

- Series Configuration Package Channel VDS (V) VGS (V) ID Max. (A) PD Max. (W) RDS (On) at 10 V (Ohms)Document3 pagesSeries Configuration Package Channel VDS (V) VGS (V) ID Max. (A) PD Max. (W) RDS (On) at 10 V (Ohms)h_878236333No ratings yet

- Powerpak® So-8l PackageDocument9 pagesPowerpak® So-8l Packageh_878236333No ratings yet

- Series Configuration Package Channel VDS (V) VGS (V) ID Max. (A) PD Max. (W)Document3 pagesSeries Configuration Package Channel VDS (V) VGS (V) ID Max. (A) PD Max. (W)h_878236333No ratings yet

- Computr List SepDocument3 pagesComputr List SepМиљан МиљанићNo ratings yet

- Fire Alarm Systems - Panel ControllerDocument4 pagesFire Alarm Systems - Panel ControllerĐức Thương VũNo ratings yet

- The Advanced Way of Data Recovery PDFDocument7 pagesThe Advanced Way of Data Recovery PDFPrince TreasureNo ratings yet

- Intelligent Single and Double Loop Fire Alarm Panel: GST200-2/NDocument3 pagesIntelligent Single and Double Loop Fire Alarm Panel: GST200-2/NheshamNo ratings yet

- SiFive U500 vc707 Gettingstarted v0.2Document24 pagesSiFive U500 vc707 Gettingstarted v0.2Shiva prasadNo ratings yet

- Horizontal Vs Vertical Micro-ProgramDocument3 pagesHorizontal Vs Vertical Micro-Programtanishqshukla17pixelNo ratings yet

- Edc Lab: 4. Facilities and Technical SupportDocument3 pagesEdc Lab: 4. Facilities and Technical SupportTirumalarao PechettyNo ratings yet

- 1200 - Parts and DiagramsDocument16 pages1200 - Parts and Diagramsetc_lctNo ratings yet

- IBM System Storage DS8000 Series: - Virtualization ConceptsDocument16 pagesIBM System Storage DS8000 Series: - Virtualization ConceptssreenathonwebNo ratings yet

- Digital Design: Register-Transfer Level (RTL) DesignDocument88 pagesDigital Design: Register-Transfer Level (RTL) DesignmasrinaNo ratings yet

- Cobra LS 1900 Series: Smart LineDocument2 pagesCobra LS 1900 Series: Smart LineBradNo ratings yet

- Release Notes 5.8 SR1.EnDocument24 pagesRelease Notes 5.8 SR1.EndachronicmasterNo ratings yet

- cg-500 Quick-GuideDocument120 pagescg-500 Quick-Guideapi-270816603No ratings yet

- 3.2.qr-Code Based Information Access System in Shopping MallDocument4 pages3.2.qr-Code Based Information Access System in Shopping MallHaris AsrofiNo ratings yet

- ATXW-5520 High Performance Westmere Long Life EATX Industrial Motherboard DatasheetDocument4 pagesATXW-5520 High Performance Westmere Long Life EATX Industrial Motherboard DatasheetDavid LippincottNo ratings yet

- Instruction Set, Addressing Modes, Assembler DirectivesDocument9 pagesInstruction Set, Addressing Modes, Assembler Directivessiddharth singhNo ratings yet

- DualCam Update Procedure - V3Document2 pagesDualCam Update Procedure - V3Benjamim LangaNo ratings yet

- Toshiba Satellite M645Document4 pagesToshiba Satellite M645hectorhscNo ratings yet

- Stm32f401re User ManualDocument54 pagesStm32f401re User Manualdanz1994No ratings yet

- Chapter 6 PipeliningDocument58 pagesChapter 6 Pipeliningvinoliamanohar100% (1)

- Tablet Study Compatible Devices and Device Check - February 2023Document4 pagesTablet Study Compatible Devices and Device Check - February 2023Aladino BernaldezNo ratings yet

- MFT Remote Controller: User's ManualDocument9 pagesMFT Remote Controller: User's ManualGhallab AlsadehNo ratings yet

- Experiment No. 05Document3 pagesExperiment No. 05Eayashen ArafatNo ratings yet

- Configuration Control With The S7-1500 and ET 200SPDocument37 pagesConfiguration Control With The S7-1500 and ET 200SPalan083No ratings yet

- CISCO IOS UpgradationDocument3 pagesCISCO IOS UpgradationSundaramoorthi JNo ratings yet

- Basic ICT Skills Class 9 Questions and AnswersDocument5 pagesBasic ICT Skills Class 9 Questions and AnswersTauheed KhanNo ratings yet

- Ss90-Installation GuideDocument87 pagesSs90-Installation Guidealoysobeck1988No ratings yet

- MM Computer Journal 143 2006 JanuaryDocument170 pagesMM Computer Journal 143 2006 JanuaryTechne PhobosNo ratings yet

- Monitor - HarmonyWolrd 2Document15 pagesMonitor - HarmonyWolrd 2Sebastian100% (1)