Professional Documents

Culture Documents

X62303 (CS1251 Cs1202a)

X62303 (CS1251 Cs1202a)

Uploaded by

tamilarasi87thulasiCopyright:

Available Formats

You might also like

- Wireline and Perforating Services Catalog PDFDocument423 pagesWireline and Perforating Services Catalog PDFFady El-Dabi100% (1)

- Toyota High-Voltage BatteryDocument14 pagesToyota High-Voltage Batteryclcasal100% (1)

- Parts List RA750 / RA850: Hydraulic / Electrical SchematicsDocument79 pagesParts List RA750 / RA850: Hydraulic / Electrical SchematicsFenix MechanicsNo ratings yet

- (1900-1915) IHC Mogul Oil EnginesDocument42 pages(1900-1915) IHC Mogul Oil EnginesHerbert Hillary Booker 2nd100% (2)

- Clap Switch Report EditedDocument47 pagesClap Switch Report EditedKeshav Krishna60% (5)

- Computer Architecture Question BankDocument10 pagesComputer Architecture Question BankMalk Malik0% (1)

- EC2303 Computer Architecture and Organization QUESTION PAPERDocument4 pagesEC2303 Computer Architecture and Organization QUESTION PAPERJayagopal JaiNo ratings yet

- Computer Architecture Question BankDocument10 pagesComputer Architecture Question BankaniprahalNo ratings yet

- Erts - Model 1Document3 pagesErts - Model 1Ece DeptNo ratings yet

- Computer Architecture and OrganizationDocument6 pagesComputer Architecture and OrganizationRahmantic SwatzNo ratings yet

- CS2354 Advanced Computer Architecture Anna University Question Paper For MEDocument2 pagesCS2354 Advanced Computer Architecture Anna University Question Paper For MEpraveenaprabhuNo ratings yet

- Anna University QP COADocument3 pagesAnna University QP COAAbirami Satheesh KumarNo ratings yet

- B - E / B - T E C H (Full-Time) D E G R E E Examinations, April/May 2012Document2 pagesB - E / B - T E C H (Full-Time) D E G R E E Examinations, April/May 2012krithikgokul selvamNo ratings yet

- PART A - (10 × 2 20 Marks)Document2 pagesPART A - (10 × 2 20 Marks)Deepak TirunelveliNo ratings yet

- CS2253 - Computer Organization and Architecture PDFDocument2 pagesCS2253 - Computer Organization and Architecture PDFvelkarthi92100% (1)

- MCS 12Document5 pagesMCS 12Divya KumariNo ratings yet

- WWW - Indiastudents.in: Question Paper CodeDocument2 pagesWWW - Indiastudents.in: Question Paper CodeBehin SamNo ratings yet

- Anna University:: Chennai - 600 025 Model Question PaperDocument2 pagesAnna University:: Chennai - 600 025 Model Question PaperSwathi RajagopalNo ratings yet

- CO QuestionsDocument4 pagesCO QuestionsAshok ReddyNo ratings yet

- ArchitectureDocument3 pagesArchitecturesamueljamespeterNo ratings yet

- Computer Architecture Question Anna UniversityDocument2 pagesComputer Architecture Question Anna UniversitymashaNo ratings yet

- Cao Previous QNDocument9 pagesCao Previous QNanusha deviNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.IT GirlsNo ratings yet

- CS 2354 - Advanced Computer Architecture PDFDocument2 pagesCS 2354 - Advanced Computer Architecture PDFvelkarthi92100% (1)

- MCS 012Document4 pagesMCS 012rajatkumar.codingNo ratings yet

- Question Paper Code:: Reg. No.Document4 pagesQuestion Paper Code:: Reg. No.krithikgokul selvamNo ratings yet

- F Computer Architecture and Organization CSE205 F1-2Document4 pagesF Computer Architecture and Organization CSE205 F1-2Akash SharmaNo ratings yet

- Ec 2303iec 53 - Computer Architecture Organization: B.E.Fb - Tech. Degree Examination, Novemberjdecember 2012Document2 pagesEc 2303iec 53 - Computer Architecture Organization: B.E.Fb - Tech. Degree Examination, Novemberjdecember 2012Somasundaram RamuNo ratings yet

- CS9211-Computer Architecture QuestionDocument7 pagesCS9211-Computer Architecture Questionrvsamy80No ratings yet

- CSA_2009Document2 pagesCSA_2009Ms.SS.Sudha - PSGCTNo ratings yet

- MCS 012Document4 pagesMCS 012trial versionNo ratings yet

- Question Paper Code:: Sri Vidya College of Engineering & Technology, VirudhunagarDocument2 pagesQuestion Paper Code:: Sri Vidya College of Engineering & Technology, Virudhunagarrajesh5500No ratings yet

- Mca 1 Sem Computer Organization and Architecture Rca104 2019Document2 pagesMca 1 Sem Computer Organization and Architecture Rca104 2019sandeepsm321No ratings yet

- s4 CAM July 2022Document2 pagess4 CAM July 2022rensiNo ratings yet

- Cao Imp QuestionsDocument1 pageCao Imp QuestionsYuvaperiyasamy MayilsamyNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.rajkumarsacNo ratings yet

- 2020 09 14SupplementaryCS405CS405 D Ktu QbankDocument3 pages2020 09 14SupplementaryCS405CS405 D Ktu QbankCigi ManojNo ratings yet

- MCS 012Document118 pagesMCS 012SongYak YamNo ratings yet

- Ece-Nd-2021-Ec 8552-Computer Architecture and Organization-807537160-40450 (Ec8552)Document3 pagesEce-Nd-2021-Ec 8552-Computer Architecture and Organization-807537160-40450 (Ec8552)AwantikNo ratings yet

- Question Paper Code:: Sri Vidya College of Engineering & Technology, Virudhunagar Course Material (University Question)Document2 pagesQuestion Paper Code:: Sri Vidya College of Engineering & Technology, Virudhunagar Course Material (University Question)rajesh5500No ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.saran_neoNo ratings yet

- Question Paper CodeDocument2 pagesQuestion Paper CodesaipriyaNo ratings yet

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- MCS 012june2020Document8 pagesMCS 012june2020kk2760057No ratings yet

- MCS-012 J-20Document8 pagesMCS-012 J-20ps34778jNo ratings yet

- COA Question PaperDocument2 pagesCOA Question PaperwahidNo ratings yet

- 2020DECDocument7 pages2020DECAnupam GyawaliNo ratings yet

- Computer Architecture Question BankDocument7 pagesComputer Architecture Question BankSalma Mehajabeen ShajahanNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)HOD ECE KNCETNo ratings yet

- Os ND06Document3 pagesOs ND06kevinbtechNo ratings yet

- Embedded System DesignDocument23 pagesEmbedded System DesignlosssssssssNo ratings yet

- CS2253 - Coa - Univ QNSDocument6 pagesCS2253 - Coa - Univ QNSKristyn BlackNo ratings yet

- CO Previous Year O.UDocument7 pagesCO Previous Year O.UVistasNo ratings yet

- MCS 203Document3 pagesMCS 203riaiitbNo ratings yet

- Bscit 101Document2 pagesBscit 101api-3782519No ratings yet

- Answer All Questions, Each Carries 4 MarksDocument3 pagesAnswer All Questions, Each Carries 4 MarksCigi ManojNo ratings yet

- Answer All The Questions Part-A (10x2 20)Document2 pagesAnswer All The Questions Part-A (10x2 20)pasuarjNo ratings yet

- Question Paper Code: X10375: Reg. NoDocument2 pagesQuestion Paper Code: X10375: Reg. NoSamraj JebasinghNo ratings yet

- Mr3492 Esp Model QN PaperDocument3 pagesMr3492 Esp Model QN PaperKeerthana SahadevanNo ratings yet

- Computer Architecture & OrganizationDocument4 pagesComputer Architecture & OrganizationUma MaheswariNo ratings yet

- Computer Architecture and Parallel Processing June 2012Document3 pagesComputer Architecture and Parallel Processing June 2012kanchanaNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document3 pagesQuestion Paper Code:: (10×2 20 Marks)Sinduja BaskaranNo ratings yet

- Chi PDFDocument13 pagesChi PDFVaibhav RodeNo ratings yet

- Ca Ap9222 PDFDocument4 pagesCa Ap9222 PDFVenkataLakshmi KrishnasamyNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.tamilarasi87thulasiNo ratings yet

- 172M20042P00660 320Document27 pages172M20042P00660 320tamilarasi87thulasiNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document3 pagesQuestion Paper Code:: (10×2 20 Marks)tamilarasi87thulasiNo ratings yet

- Oo LabDocument327 pagesOo Labtamilarasi87thulasiNo ratings yet

- CS8381 SyllabusDocument1 pageCS8381 Syllabustamilarasi87thulasiNo ratings yet

- 146 - CS8494, CS6403 Software Engineering - Question BankDocument5 pages146 - CS8494, CS6403 Software Engineering - Question Banktamilarasi87thulasiNo ratings yet

- Fail Safe Unit FQM 05.1 - FQM 12.1 Fqmex 05.1 - Fqmex 12.1: Assembly, Operation, Commissioning Operation InstructionsDocument40 pagesFail Safe Unit FQM 05.1 - FQM 12.1 Fqmex 05.1 - Fqmex 12.1: Assembly, Operation, Commissioning Operation Instructionsmani_208eeNo ratings yet

- Outdoor CabinetDocument6 pagesOutdoor Cabinetapi-3764472No ratings yet

- Cong. Allan Butch Francisco 10.45 HYB 20KWH BATDocument4 pagesCong. Allan Butch Francisco 10.45 HYB 20KWH BATJohn Kenneth ViernesNo ratings yet

- AL65 Driver Led DatasheetDocument21 pagesAL65 Driver Led DatasheetR̳̿e̳̿n̳̿o̳̿s̳̿ ̳̿S̳̿a̳̿i̳̿n̳̿t̳̿No ratings yet

- MAN3059-0 Odyssey Programming ManualDocument52 pagesMAN3059-0 Odyssey Programming Manualsqamar68No ratings yet

- JUSTIFICATION For Acquisition of Motor VehicleDocument1 pageJUSTIFICATION For Acquisition of Motor VehicleRace Patam KiNo ratings yet

- ABB - Comutatoare Cu CameDocument60 pagesABB - Comutatoare Cu CameoscarilyesNo ratings yet

- Ae 036884 008Document1 pageAe 036884 008RanielNo ratings yet

- CLA 2023 BrochureDocument75 pagesCLA 2023 BrochureGiovan Maria Catalan BelmonteNo ratings yet

- Technical Information Passat ENGDocument2 pagesTechnical Information Passat ENGGeorge StanNo ratings yet

- 65162e PDFDocument658 pages65162e PDFSergio Trujillo CerroNo ratings yet

- Pengadaan Tiang JTM PLTM Titab 1Document6 pagesPengadaan Tiang JTM PLTM Titab 1Mulyana YNNo ratings yet

- Instruction Book': Ladder7,4MDocument117 pagesInstruction Book': Ladder7,4MNikolay KirovNo ratings yet

- Ys 6235Document2 pagesYs 6235pabloperezmtz1No ratings yet

- ComputerDocument5 pagesComputermehran kabirNo ratings yet

- 1212-02-15kV Delta Delta Padmount TransformerDocument11 pages1212-02-15kV Delta Delta Padmount TransformerpraveenniteenNo ratings yet

- Data Book-CVT PDFDocument97 pagesData Book-CVT PDFĐỗ Hồng Sơn100% (2)

- Atlas Copco Xahs 186 36,37Document2 pagesAtlas Copco Xahs 186 36,37AkmalNo ratings yet

- Henry Schein Brand HandpiecesDocument20 pagesHenry Schein Brand HandpiecesmohammedNo ratings yet

- TM300 EN 20141111manual PDFDocument18 pagesTM300 EN 20141111manual PDFbenjaminjiaNo ratings yet

- How To Use A 1W Star LEDDocument2 pagesHow To Use A 1W Star LEDRamon JaraNo ratings yet

- Engines 1000.3.4 W EuroiiiDocument192 pagesEngines 1000.3.4 W EuroiiiAkos FeherNo ratings yet

- Manual SIRIUS Innovations Overload Relay 3RU2 3RB3Document120 pagesManual SIRIUS Innovations Overload Relay 3RU2 3RB3sanjay sharmaNo ratings yet

- KRF-V5560 5060 4060D (En) PDFDocument36 pagesKRF-V5560 5060 4060D (En) PDFJános Apáti100% (1)

- Data Sheet Módulo HTRIDocument8 pagesData Sheet Módulo HTRIAbimael SantosNo ratings yet

X62303 (CS1251 Cs1202a)

X62303 (CS1251 Cs1202a)

Uploaded by

tamilarasi87thulasiOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

X62303 (CS1251 Cs1202a)

X62303 (CS1251 Cs1202a)

Uploaded by

tamilarasi87thulasiCopyright:

Available Formats

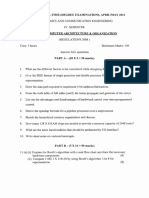

*X62303*

Reg. No. :

Question Paper Code : X 62303

B.E./B.Tech. DEgREE ExamiNaTioNs, NoVEmBER/DECEmBER 2020

Third/Fourth/sixth/Seventh semester

Electronics and Communication Engineering

Cs 1251/Cs 1202 a – CompuTER aRChiTECTuRE

(Common to Computer science and Engineering,Electrical and Electronics Engineering

and Information Technology)

(Regulations 2004/2007)

(Common to CS1251 for B.E (part–Time) Third semester-Computer science and

Engineering and Fifth semester – Electronics and Communication

Engineering – Regulations 2005)

Time : Three hours maximum : 100 marks

Answer all questions

Part – A (10�2=20 Marks)

1. What is meant by Central Processing Unit (CPU) ?

2. Define Control Bus.

3. Draw the block diagram of n-bit ripple-carry adder.

4. What do you understand about von Neumann rounding ?

5. Compare horizontal and vertical format.

6. When does imprecise exception arise ?

7. Design a 1m × 16 memory using 512 k × 8 static memory chips.

8. Find average memory access time if the hit rate is 90% and access time for main

memory is 50 ns and cache is 5 ns. Find performance improvement.

9. Compare between memory mapped I/O and I/O mapped I/O.

10. What is an interrupt ? State its significance.

X 62303 *X62303*

Part – B (5�16=80 Marks)

11. a) Explain the different types of addressing modes with necessary example. (16)

(OR)

b) i) With necessary diagram, explain the basic functional units of a computer. (8)

ii) Write short notes on performance of a computer. (8)

12. a) i) Perform 25 × (–16) using booth’s multiplication algorithm. (8)

ii) What are the problems in floating point arithmetic ? (8)

(OR)

b) Describe the algorithm for integer division with suitable example. (16)

13. a) i) What are superscalar processors ? Explain the structure of a typical superscalar

processor. (10)

ii) Draw and explain the timing diagram for memory read operation. (6)

(OR)

b) i) Explain the basic organization of a microprogrammed control unit

and what modification is required in the basic organization to support

microprogram branching. (8)

ii) What are the three types of hazards that cause performance degradation

in pipelined processors ? Explain them in detail. (8)

14. a) Explain virtual memory and its management. (16)

(OR)

b) Explain in detail about cache memory and its mapping functions. (16)

15. a) What is the use of DMA controller ? Explain the function of DMA controller

with necessary diagram. (16)

(OR)

b) Describe in detail about standard I/O interfaces with necessary diagram. (16)

–––––––––––––

You might also like

- Wireline and Perforating Services Catalog PDFDocument423 pagesWireline and Perforating Services Catalog PDFFady El-Dabi100% (1)

- Toyota High-Voltage BatteryDocument14 pagesToyota High-Voltage Batteryclcasal100% (1)

- Parts List RA750 / RA850: Hydraulic / Electrical SchematicsDocument79 pagesParts List RA750 / RA850: Hydraulic / Electrical SchematicsFenix MechanicsNo ratings yet

- (1900-1915) IHC Mogul Oil EnginesDocument42 pages(1900-1915) IHC Mogul Oil EnginesHerbert Hillary Booker 2nd100% (2)

- Clap Switch Report EditedDocument47 pagesClap Switch Report EditedKeshav Krishna60% (5)

- Computer Architecture Question BankDocument10 pagesComputer Architecture Question BankMalk Malik0% (1)

- EC2303 Computer Architecture and Organization QUESTION PAPERDocument4 pagesEC2303 Computer Architecture and Organization QUESTION PAPERJayagopal JaiNo ratings yet

- Computer Architecture Question BankDocument10 pagesComputer Architecture Question BankaniprahalNo ratings yet

- Erts - Model 1Document3 pagesErts - Model 1Ece DeptNo ratings yet

- Computer Architecture and OrganizationDocument6 pagesComputer Architecture and OrganizationRahmantic SwatzNo ratings yet

- CS2354 Advanced Computer Architecture Anna University Question Paper For MEDocument2 pagesCS2354 Advanced Computer Architecture Anna University Question Paper For MEpraveenaprabhuNo ratings yet

- Anna University QP COADocument3 pagesAnna University QP COAAbirami Satheesh KumarNo ratings yet

- B - E / B - T E C H (Full-Time) D E G R E E Examinations, April/May 2012Document2 pagesB - E / B - T E C H (Full-Time) D E G R E E Examinations, April/May 2012krithikgokul selvamNo ratings yet

- PART A - (10 × 2 20 Marks)Document2 pagesPART A - (10 × 2 20 Marks)Deepak TirunelveliNo ratings yet

- CS2253 - Computer Organization and Architecture PDFDocument2 pagesCS2253 - Computer Organization and Architecture PDFvelkarthi92100% (1)

- MCS 12Document5 pagesMCS 12Divya KumariNo ratings yet

- WWW - Indiastudents.in: Question Paper CodeDocument2 pagesWWW - Indiastudents.in: Question Paper CodeBehin SamNo ratings yet

- Anna University:: Chennai - 600 025 Model Question PaperDocument2 pagesAnna University:: Chennai - 600 025 Model Question PaperSwathi RajagopalNo ratings yet

- CO QuestionsDocument4 pagesCO QuestionsAshok ReddyNo ratings yet

- ArchitectureDocument3 pagesArchitecturesamueljamespeterNo ratings yet

- Computer Architecture Question Anna UniversityDocument2 pagesComputer Architecture Question Anna UniversitymashaNo ratings yet

- Cao Previous QNDocument9 pagesCao Previous QNanusha deviNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.IT GirlsNo ratings yet

- CS 2354 - Advanced Computer Architecture PDFDocument2 pagesCS 2354 - Advanced Computer Architecture PDFvelkarthi92100% (1)

- MCS 012Document4 pagesMCS 012rajatkumar.codingNo ratings yet

- Question Paper Code:: Reg. No.Document4 pagesQuestion Paper Code:: Reg. No.krithikgokul selvamNo ratings yet

- F Computer Architecture and Organization CSE205 F1-2Document4 pagesF Computer Architecture and Organization CSE205 F1-2Akash SharmaNo ratings yet

- Ec 2303iec 53 - Computer Architecture Organization: B.E.Fb - Tech. Degree Examination, Novemberjdecember 2012Document2 pagesEc 2303iec 53 - Computer Architecture Organization: B.E.Fb - Tech. Degree Examination, Novemberjdecember 2012Somasundaram RamuNo ratings yet

- CS9211-Computer Architecture QuestionDocument7 pagesCS9211-Computer Architecture Questionrvsamy80No ratings yet

- CSA_2009Document2 pagesCSA_2009Ms.SS.Sudha - PSGCTNo ratings yet

- MCS 012Document4 pagesMCS 012trial versionNo ratings yet

- Question Paper Code:: Sri Vidya College of Engineering & Technology, VirudhunagarDocument2 pagesQuestion Paper Code:: Sri Vidya College of Engineering & Technology, Virudhunagarrajesh5500No ratings yet

- Mca 1 Sem Computer Organization and Architecture Rca104 2019Document2 pagesMca 1 Sem Computer Organization and Architecture Rca104 2019sandeepsm321No ratings yet

- s4 CAM July 2022Document2 pagess4 CAM July 2022rensiNo ratings yet

- Cao Imp QuestionsDocument1 pageCao Imp QuestionsYuvaperiyasamy MayilsamyNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.rajkumarsacNo ratings yet

- 2020 09 14SupplementaryCS405CS405 D Ktu QbankDocument3 pages2020 09 14SupplementaryCS405CS405 D Ktu QbankCigi ManojNo ratings yet

- MCS 012Document118 pagesMCS 012SongYak YamNo ratings yet

- Ece-Nd-2021-Ec 8552-Computer Architecture and Organization-807537160-40450 (Ec8552)Document3 pagesEce-Nd-2021-Ec 8552-Computer Architecture and Organization-807537160-40450 (Ec8552)AwantikNo ratings yet

- Question Paper Code:: Sri Vidya College of Engineering & Technology, Virudhunagar Course Material (University Question)Document2 pagesQuestion Paper Code:: Sri Vidya College of Engineering & Technology, Virudhunagar Course Material (University Question)rajesh5500No ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.saran_neoNo ratings yet

- Question Paper CodeDocument2 pagesQuestion Paper CodesaipriyaNo ratings yet

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- MCS 012june2020Document8 pagesMCS 012june2020kk2760057No ratings yet

- MCS-012 J-20Document8 pagesMCS-012 J-20ps34778jNo ratings yet

- COA Question PaperDocument2 pagesCOA Question PaperwahidNo ratings yet

- 2020DECDocument7 pages2020DECAnupam GyawaliNo ratings yet

- Computer Architecture Question BankDocument7 pagesComputer Architecture Question BankSalma Mehajabeen ShajahanNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)HOD ECE KNCETNo ratings yet

- Os ND06Document3 pagesOs ND06kevinbtechNo ratings yet

- Embedded System DesignDocument23 pagesEmbedded System DesignlosssssssssNo ratings yet

- CS2253 - Coa - Univ QNSDocument6 pagesCS2253 - Coa - Univ QNSKristyn BlackNo ratings yet

- CO Previous Year O.UDocument7 pagesCO Previous Year O.UVistasNo ratings yet

- MCS 203Document3 pagesMCS 203riaiitbNo ratings yet

- Bscit 101Document2 pagesBscit 101api-3782519No ratings yet

- Answer All Questions, Each Carries 4 MarksDocument3 pagesAnswer All Questions, Each Carries 4 MarksCigi ManojNo ratings yet

- Answer All The Questions Part-A (10x2 20)Document2 pagesAnswer All The Questions Part-A (10x2 20)pasuarjNo ratings yet

- Question Paper Code: X10375: Reg. NoDocument2 pagesQuestion Paper Code: X10375: Reg. NoSamraj JebasinghNo ratings yet

- Mr3492 Esp Model QN PaperDocument3 pagesMr3492 Esp Model QN PaperKeerthana SahadevanNo ratings yet

- Computer Architecture & OrganizationDocument4 pagesComputer Architecture & OrganizationUma MaheswariNo ratings yet

- Computer Architecture and Parallel Processing June 2012Document3 pagesComputer Architecture and Parallel Processing June 2012kanchanaNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document3 pagesQuestion Paper Code:: (10×2 20 Marks)Sinduja BaskaranNo ratings yet

- Chi PDFDocument13 pagesChi PDFVaibhav RodeNo ratings yet

- Ca Ap9222 PDFDocument4 pagesCa Ap9222 PDFVenkataLakshmi KrishnasamyNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.tamilarasi87thulasiNo ratings yet

- 172M20042P00660 320Document27 pages172M20042P00660 320tamilarasi87thulasiNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document3 pagesQuestion Paper Code:: (10×2 20 Marks)tamilarasi87thulasiNo ratings yet

- Oo LabDocument327 pagesOo Labtamilarasi87thulasiNo ratings yet

- CS8381 SyllabusDocument1 pageCS8381 Syllabustamilarasi87thulasiNo ratings yet

- 146 - CS8494, CS6403 Software Engineering - Question BankDocument5 pages146 - CS8494, CS6403 Software Engineering - Question Banktamilarasi87thulasiNo ratings yet

- Fail Safe Unit FQM 05.1 - FQM 12.1 Fqmex 05.1 - Fqmex 12.1: Assembly, Operation, Commissioning Operation InstructionsDocument40 pagesFail Safe Unit FQM 05.1 - FQM 12.1 Fqmex 05.1 - Fqmex 12.1: Assembly, Operation, Commissioning Operation Instructionsmani_208eeNo ratings yet

- Outdoor CabinetDocument6 pagesOutdoor Cabinetapi-3764472No ratings yet

- Cong. Allan Butch Francisco 10.45 HYB 20KWH BATDocument4 pagesCong. Allan Butch Francisco 10.45 HYB 20KWH BATJohn Kenneth ViernesNo ratings yet

- AL65 Driver Led DatasheetDocument21 pagesAL65 Driver Led DatasheetR̳̿e̳̿n̳̿o̳̿s̳̿ ̳̿S̳̿a̳̿i̳̿n̳̿t̳̿No ratings yet

- MAN3059-0 Odyssey Programming ManualDocument52 pagesMAN3059-0 Odyssey Programming Manualsqamar68No ratings yet

- JUSTIFICATION For Acquisition of Motor VehicleDocument1 pageJUSTIFICATION For Acquisition of Motor VehicleRace Patam KiNo ratings yet

- ABB - Comutatoare Cu CameDocument60 pagesABB - Comutatoare Cu CameoscarilyesNo ratings yet

- Ae 036884 008Document1 pageAe 036884 008RanielNo ratings yet

- CLA 2023 BrochureDocument75 pagesCLA 2023 BrochureGiovan Maria Catalan BelmonteNo ratings yet

- Technical Information Passat ENGDocument2 pagesTechnical Information Passat ENGGeorge StanNo ratings yet

- 65162e PDFDocument658 pages65162e PDFSergio Trujillo CerroNo ratings yet

- Pengadaan Tiang JTM PLTM Titab 1Document6 pagesPengadaan Tiang JTM PLTM Titab 1Mulyana YNNo ratings yet

- Instruction Book': Ladder7,4MDocument117 pagesInstruction Book': Ladder7,4MNikolay KirovNo ratings yet

- Ys 6235Document2 pagesYs 6235pabloperezmtz1No ratings yet

- ComputerDocument5 pagesComputermehran kabirNo ratings yet

- 1212-02-15kV Delta Delta Padmount TransformerDocument11 pages1212-02-15kV Delta Delta Padmount TransformerpraveenniteenNo ratings yet

- Data Book-CVT PDFDocument97 pagesData Book-CVT PDFĐỗ Hồng Sơn100% (2)

- Atlas Copco Xahs 186 36,37Document2 pagesAtlas Copco Xahs 186 36,37AkmalNo ratings yet

- Henry Schein Brand HandpiecesDocument20 pagesHenry Schein Brand HandpiecesmohammedNo ratings yet

- TM300 EN 20141111manual PDFDocument18 pagesTM300 EN 20141111manual PDFbenjaminjiaNo ratings yet

- How To Use A 1W Star LEDDocument2 pagesHow To Use A 1W Star LEDRamon JaraNo ratings yet

- Engines 1000.3.4 W EuroiiiDocument192 pagesEngines 1000.3.4 W EuroiiiAkos FeherNo ratings yet

- Manual SIRIUS Innovations Overload Relay 3RU2 3RB3Document120 pagesManual SIRIUS Innovations Overload Relay 3RU2 3RB3sanjay sharmaNo ratings yet

- KRF-V5560 5060 4060D (En) PDFDocument36 pagesKRF-V5560 5060 4060D (En) PDFJános Apáti100% (1)

- Data Sheet Módulo HTRIDocument8 pagesData Sheet Módulo HTRIAbimael SantosNo ratings yet