Professional Documents

Culture Documents

Transistor 2021 Pag 1

Transistor 2021 Pag 1

Uploaded by

Stuxnet0 ratings0% found this document useful (0 votes)

9 views2 pagesThe document provides details about the CP305 process for manufacturing NPN high current transistor chips at Central Semiconductor Corp. It describes the process details such as the epitaxial planar process, die size of 31 x 31 mils and thickness of 9 mils. It also lists the principal device types produced using this process as 2N3019, CMPT3019, CXT3019, and CZT3019.

Original Description:

Transistor2021Pag1 (14)

Original Title

Transistor2021Pag1 (14)

Copyright

© Public Domain

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThe document provides details about the CP305 process for manufacturing NPN high current transistor chips at Central Semiconductor Corp. It describes the process details such as the epitaxial planar process, die size of 31 x 31 mils and thickness of 9 mils. It also lists the principal device types produced using this process as 2N3019, CMPT3019, CXT3019, and CZT3019.

Copyright:

Public Domain

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

9 views2 pagesTransistor 2021 Pag 1

Transistor 2021 Pag 1

Uploaded by

StuxnetThe document provides details about the CP305 process for manufacturing NPN high current transistor chips at Central Semiconductor Corp. It describes the process details such as the epitaxial planar process, die size of 31 x 31 mils and thickness of 9 mils. It also lists the principal device types produced using this process as 2N3019, CMPT3019, CXT3019, and CZT3019.

Copyright:

Public Domain

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 2

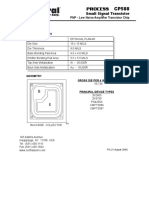

PROCESS CP305

Central

TM

Small Signal Transistor Semiconductor Corp.

NPN - High Current Transistor Chip

PROCESS DETAILS

Process EPITAXIAL PLANAR

Die Size 31 x 31 MILS

Die Thickness 9.0 MILS

Base Bonding Pad Area 5.9 x 11.8 MILS

Emitter Bonding Pad Area 6.5 x 13.8 MILS

Top Side Metalization Al - 30,000Å

Back Side Metalization Au - 18,000Å

GEOMETRY

GROSS DIE PER 4 INCH WAFER

11,300

PRINCIPAL DEVICE TYPES

2N3019

CMPT3019

CXT3019

CZT3019

BACKSIDE COLLECTOR

145 Adams Avenue

Hauppauge, NY 11788 USA

Tel: (631) 435-1110

Fax: (631) 435-1824

www.centralsemi.com R2 (1-August 2002)

CP305

Central PROCESS

TM

Semiconductor Corp. Typical Electrical Characteristics

145 Adams Avenue

Hauppauge, NY 11788 USA

Tel: (631) 435-1110

Fax: (631) 435-1824

www.centralsemi.com R2 (1-August 2002)

You might also like

- Korg SP-100 Service ManualDocument23 pagesKorg SP-100 Service ManualKolja80% (5)

- CD30/35 MANUAL & Start Guide: For Use On PPM Electromagnetic Equipment VF Advance VF Premier Mini VF VFX MagnatronDocument21 pagesCD30/35 MANUAL & Start Guide: For Use On PPM Electromagnetic Equipment VF Advance VF Premier Mini VF VFX Magnatronkawa saki75% (4)

- Kakanj AirDocument95 pagesKakanj AirAnonymous snYQBSUNdyNo ratings yet

- Path15R SManualDocument8 pagesPath15R SManualSteve Dallman0% (1)

- CP309Document2 pagesCP309Victor HemzNo ratings yet

- Central: ProcessDocument2 pagesCentral: ProcessNelson antonioNo ratings yet

- Datasheetsvf PDFDocument2 pagesDatasheetsvf PDFarjetaNo ratings yet

- Process: Small Signal TransistorDocument2 pagesProcess: Small Signal TransistorVictor HemzNo ratings yet

- Central: ProcessDocument2 pagesCentral: ProcessNelson antonioNo ratings yet

- Central Central: ProcessDocument2 pagesCentral Central: ProcessNelson antonioNo ratings yet

- Datasheet TRDocument2 pagesDatasheet TRitssna consulting servicesNo ratings yet

- Transistor 2021 Pag 3Document2 pagesTransistor 2021 Pag 3StuxnetNo ratings yet

- Process: Small Signal TransistorDocument2 pagesProcess: Small Signal TransistorVictor HemzNo ratings yet

- Transistor 2021 Pag 1Document2 pagesTransistor 2021 Pag 1StuxnetNo ratings yet

- Process: Small Signal TransistorDocument2 pagesProcess: Small Signal TransistorVictor HemzNo ratings yet

- CP211Document2 pagesCP211Victor HemzNo ratings yet

- CP230Document2 pagesCP230Victor HemzNo ratings yet

- Process: Small Signal TransistorDocument2 pagesProcess: Small Signal TransistorVictor HemzNo ratings yet

- 3com End of Sale 20dates PDFDocument110 pages3com End of Sale 20dates PDFRodrigo SenadorNo ratings yet

- Service Manual: CFD-C1000Document20 pagesService Manual: CFD-C1000Giovanni MendozaNo ratings yet

- LM2907 and LM2917 Frequency To Voltage Converter: FeaturesDocument42 pagesLM2907 and LM2917 Frequency To Voltage Converter: FeaturesHariman PurbaNo ratings yet

- $1330PZT-9141C/I04-A : Construction Check SheetDocument3 pages$1330PZT-9141C/I04-A : Construction Check SheetAnonymous W939WdINo ratings yet

- Alternates TO Surface Mount Tantalum Electrolytic CapacitorsDocument21 pagesAlternates TO Surface Mount Tantalum Electrolytic CapacitorsGuGazNo ratings yet

- 3 Storey Stall SLDDocument3 pages3 Storey Stall SLDLAWRENCE KIM N. SACRISTANNo ratings yet

- Datasheet Bu941zpDocument9 pagesDatasheet Bu941zpNoel Alejandro Cordova RangelNo ratings yet

- Item Num Item Description Qty in Bin Manufacturer Manufacturer PartDocument2 pagesItem Num Item Description Qty in Bin Manufacturer Manufacturer PartadamdudeNo ratings yet

- Simple Forward AC-DC Bom - ReportDocument11 pagesSimple Forward AC-DC Bom - ReportSwaminathan RajaramNo ratings yet

- PT2313L PDFDocument3 pagesPT2313L PDFMaugrys Castillo100% (1)

- Cables, Adapters, Accessories - 1Document8 pagesCables, Adapters, Accessories - 1Nguyen Danh HuyNo ratings yet

- TWOTREES Catalog (Including Spare Parts)Document208 pagesTWOTREES Catalog (Including Spare Parts)Esteban OrtegaNo ratings yet

- CP283Document1 pageCP283zero cloudNo ratings yet

- BU941ZT/BU941ZTFP BUB941ZT: High Voltage Ignition Coil Driver NPN Power DarlingtonDocument9 pagesBU941ZT/BU941ZTFP BUB941ZT: High Voltage Ignition Coil Driver NPN Power DarlingtonEduardo Segundo Gonzalez MuñozNo ratings yet

- System1000 Bill of Materials: Country: Macedonia Ref: Project Macedonia Design Ref: Project Macedonia - LPDDocument1 pageSystem1000 Bill of Materials: Country: Macedonia Ref: Project Macedonia Design Ref: Project Macedonia - LPDcezarmkdNo ratings yet

- Spare Parts List Desktop Printers GX430t - GX43-1X2XXX-XXX (Document3 pagesSpare Parts List Desktop Printers GX430t - GX43-1X2XXX-XXX (joseito741258No ratings yet

- Electrical PlanDocument22 pagesElectrical PlanEstifane VelosoNo ratings yet

- BOQ Labor Cost - Engr. GonzalesDocument1 pageBOQ Labor Cost - Engr. GonzalesAJ TaylanNo ratings yet

- MTDM10-U09 Chap12 SPARE PARTSDocument5 pagesMTDM10-U09 Chap12 SPARE PARTSByron CuevasNo ratings yet

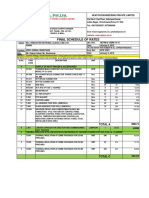

- Final Schedule of Rates-R6Document2 pagesFinal Schedule of Rates-R6Yogesh BadheNo ratings yet

- American Special Tele (011-5802-3XX) : Parts LayoutDocument4 pagesAmerican Special Tele (011-5802-3XX) : Parts LayoutnosoyninjaNo ratings yet

- GE AMX4 (+) Rotor PCB FixDocument4 pagesGE AMX4 (+) Rotor PCB FixMarlon Detera100% (1)

- Spare Parts List: WarningDocument6 pagesSpare Parts List: WarningblaisejeanNo ratings yet

- P7373 2Document6 pagesP7373 2tinov61820No ratings yet

- BU941ZPDocument9 pagesBU941ZPAlejandro Borrego DominguezNo ratings yet

- Customer Telma MG Site Id: DIA054 Telma Madagascar Site Name: Betsiaka Delivery Adress: Betsiaka Tel: Tel: Fax FaxDocument3 pagesCustomer Telma MG Site Id: DIA054 Telma Madagascar Site Name: Betsiaka Delivery Adress: Betsiaka Tel: Tel: Fax FaxPamela RatsimbazafyNo ratings yet

- Digital Input BarrierDocument27 pagesDigital Input Barriermostafa eshmawyNo ratings yet

- Hfe Quad 909 ServiceDocument11 pagesHfe Quad 909 ServiceremelefeleNo ratings yet

- Pump Part 2pdfDocument2 pagesPump Part 2pdfDaniel TekleNo ratings yet

- Shutdown SIS: Excavator 319D LN Excavator FMH 319D L & 319D LN Excavators FMH00001-UP (MACHINE) POWERED BY C4.2 EngineDocument3 pagesShutdown SIS: Excavator 319D LN Excavator FMH 319D L & 319D LN Excavators FMH00001-UP (MACHINE) POWERED BY C4.2 EngineANDREI26No ratings yet

- Cn207a DaewooDocument7 pagesCn207a Daewoo77jacki77No ratings yet

- CGD EQ Qualified Parts Catalog ManufacturerDocument401 pagesCGD EQ Qualified Parts Catalog ManufacturerARUNANo ratings yet

- Toshiba Dp3580 Service ManualDocument200 pagesToshiba Dp3580 Service Manualnazmi100% (1)

- Customer Telma MG Site Id: VAK065 Telma Madagascar Site Name: Anjazafotsy Delivery Adress: Anjazafotsy Tel: Tel: Fax FaxDocument3 pagesCustomer Telma MG Site Id: VAK065 Telma Madagascar Site Name: Anjazafotsy Delivery Adress: Anjazafotsy Tel: Tel: Fax FaxPamela RatsimbazafyNo ratings yet

- Moulded Case Circuit Breakers: New DU Series 20 A To 250 ADocument8 pagesMoulded Case Circuit Breakers: New DU Series 20 A To 250 AtanushagrNo ratings yet

- Operation & Maintenance Manual: Section 7 Technical Drawings and Bill of Materials (Bom)Document3 pagesOperation & Maintenance Manual: Section 7 Technical Drawings and Bill of Materials (Bom)Mohammed BasionyNo ratings yet

- Radio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142From EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142No ratings yet

- Wireless Power Transfer: Using Magnetic and Electric Resonance Coupling TechniquesFrom EverandWireless Power Transfer: Using Magnetic and Electric Resonance Coupling TechniquesNo ratings yet

- Noise in Nanoscale Semiconductor DevicesFrom EverandNoise in Nanoscale Semiconductor DevicesTibor GrasserNo ratings yet

- DatasheetDocument11 pagesDatasheetStuxnetNo ratings yet

- High Efficiency, Three-Digit Numeric Displays: LB-303AK SeriesDocument4 pagesHigh Efficiency, Three-Digit Numeric Displays: LB-303AK SeriesStuxnetNo ratings yet

- DatasheetDocument7 pagesDatasheetStuxnetNo ratings yet

- 37mm (1.4 INCH) 5x8 SINGLE COLOR DOT Matrix Displays: Mechanically RuggedDocument5 pages37mm (1.4 INCH) 5x8 SINGLE COLOR DOT Matrix Displays: Mechanically RuggedStuxnetNo ratings yet

- STTH10LCD06: Turbo2 Ultrafast - High Voltage Rectifier For Flat Panel DisplaysDocument10 pagesSTTH10LCD06: Turbo2 Ultrafast - High Voltage Rectifier For Flat Panel DisplaysStuxnetNo ratings yet

- High Efficiency, Three-Digit Numeric Displays: LB-203BL SeriesDocument2 pagesHigh Efficiency, Three-Digit Numeric Displays: LB-203BL SeriesStuxnetNo ratings yet

- DatasheetDocument2 pagesDatasheetStuxnetNo ratings yet

- Hexadecimal and Numeric Displays For Industrial ApplicationsDocument8 pagesHexadecimal and Numeric Displays For Industrial ApplicationsStuxnetNo ratings yet

- Everlight Electronics Co.,Ltd.: Model No: ELS-512EWADocument5 pagesEverlight Electronics Co.,Ltd.: Model No: ELS-512EWAStuxnetNo ratings yet

- Everlight Electronics Co.,Ltd.: Technical Data Sheet 0.36" Single Digit DisplaysDocument6 pagesEverlight Electronics Co.,Ltd.: Technical Data Sheet 0.36" Single Digit DisplaysStuxnetNo ratings yet

- Black Surface Seven Segment Displays: Technical DataDocument14 pagesBlack Surface Seven Segment Displays: Technical DataStuxnetNo ratings yet

- High Efficiency, Single-Digit Numeric Displays: LA-101AK SeriesDocument2 pagesHigh Efficiency, Single-Digit Numeric Displays: LA-101AK SeriesStuxnetNo ratings yet

- Everlight Electronics Co.,Ltd.: Technical Data Sheet 1.0" Single Digit DisplaysDocument6 pagesEverlight Electronics Co.,Ltd.: Technical Data Sheet 1.0" Single Digit DisplaysStuxnetNo ratings yet

- Agilent HDSP-B58x Series 53.3 MM (2.1 Inch) General Purpose 5 X 8 Dot Matrix Bi-Color Alphanumeric DisplaysDocument8 pagesAgilent HDSP-B58x Series 53.3 MM (2.1 Inch) General Purpose 5 X 8 Dot Matrix Bi-Color Alphanumeric DisplaysStuxnetNo ratings yet

- Everlight Electronics Co.,Ltd.: Technical Data Sheet 0.56" Dual Digit DisplaysDocument5 pagesEverlight Electronics Co.,Ltd.: Technical Data Sheet 0.56" Dual Digit DisplaysStuxnetNo ratings yet

- Everlight Electronics Co.,Ltd.: Technical Data Sheet 0.39" Single Digit DisplaysDocument5 pagesEverlight Electronics Co.,Ltd.: Technical Data Sheet 0.39" Single Digit DisplaysStuxnetNo ratings yet

- Everlight Electronics Co.,Ltd.: Technical Data Sheet 0.56" Dual Digit DisplaysDocument6 pagesEverlight Electronics Co.,Ltd.: Technical Data Sheet 0.56" Dual Digit DisplaysStuxnetNo ratings yet

- Technical Data Sheet 0.56" Triple Digit SMD Displays: ELST-511SYGWA/S530-E2/S290Document8 pagesTechnical Data Sheet 0.56" Triple Digit SMD Displays: ELST-511SYGWA/S530-E2/S290StuxnetNo ratings yet

- 10 MM (0.40 Inch) Seven Segment Displays: Technical DataDocument11 pages10 MM (0.40 Inch) Seven Segment Displays: Technical DataStuxnetNo ratings yet

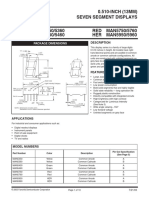

- 0.510-INCH (13MM) Seven Segment Displays: Package DimensionsDocument10 pages0.510-INCH (13MM) Seven Segment Displays: Package DimensionsStuxnetNo ratings yet

- DatasheetDocument17 pagesDatasheetStuxnetNo ratings yet

- Data Sheet: ReceivedDocument7 pagesData Sheet: ReceivedStuxnetNo ratings yet

- Everlight Electronics Co.,Ltd.: Technical Data Sheet 0.4" Dual Digit DisplaysDocument5 pagesEverlight Electronics Co.,Ltd.: Technical Data Sheet 0.4" Dual Digit DisplaysStuxnetNo ratings yet

- DatasheetDocument74 pagesDatasheetStuxnetNo ratings yet

- DatasheetDocument12 pagesDatasheetStuxnetNo ratings yet

- Data Sheet: ReceivedDocument7 pagesData Sheet: ReceivedStuxnetNo ratings yet

- Everlight Electronics Co.,Ltd.: Technical Data Sheet 0.5" Dual Digit DisplaysDocument6 pagesEverlight Electronics Co.,Ltd.: Technical Data Sheet 0.5" Dual Digit DisplaysStuxnetNo ratings yet

- Everlight Electronics Co.,Ltd.: Technical Data Sheet 0.39" Single Digit DisplaysDocument5 pagesEverlight Electronics Co.,Ltd.: Technical Data Sheet 0.39" Single Digit DisplaysStuxnetNo ratings yet

- Data Sheet: LCD Row/column Driver For Dot Matrix Graphic DisplaysDocument48 pagesData Sheet: LCD Row/column Driver For Dot Matrix Graphic DisplaysStuxnetNo ratings yet

- Everlight Electronics Co.,Ltd.: Technical Data Sheet 2.3" 8 8 Dot Matrix DisplaysDocument5 pagesEverlight Electronics Co.,Ltd.: Technical Data Sheet 2.3" 8 8 Dot Matrix DisplaysStuxnetNo ratings yet