Professional Documents

Culture Documents

Field-Effect (FET) Transistors: ECE60L Lecture Notes, Spring 2003

Field-Effect (FET) Transistors: ECE60L Lecture Notes, Spring 2003

Uploaded by

harshCopyright:

Available Formats

You might also like

- Std. 115 - 1995 - IEEE Guide, Test Procedures For Synchronous Machines PartIIDocument108 pagesStd. 115 - 1995 - IEEE Guide, Test Procedures For Synchronous Machines PartIIflywheel2006100% (2)

- Experiment-3:: Cadence Virtuoso 6.1.7 - 64bDocument9 pagesExperiment-3:: Cadence Virtuoso 6.1.7 - 64bSrujan MulkaNo ratings yet

- 100 KWDocument16 pages100 KWRajaNo ratings yet

- Electronic II-1Document10 pagesElectronic II-1Isaac DanielNo ratings yet

- Both Bjts and Fets, Are Equally Important and Each Offers Distinct Advantages and Has Unique Areas of Application.)Document19 pagesBoth Bjts and Fets, Are Equally Important and Each Offers Distinct Advantages and Has Unique Areas of Application.)Maxwell LumorNo ratings yet

- The Basic Structure: Field Effect TransistorDocument10 pagesThe Basic Structure: Field Effect TransistormokhaladNo ratings yet

- MOSFET Course Notes - MMA HAKIMDocument22 pagesMOSFET Course Notes - MMA HAKIMAdnan HossainNo ratings yet

- Junction Field Effect Transistor (JFET) : Gate Terminal. The Other Two Contacts, The Drain and Source, Are Placed atDocument8 pagesJunction Field Effect Transistor (JFET) : Gate Terminal. The Other Two Contacts, The Drain and Source, Are Placed atkingboyNo ratings yet

- Regulation - 2018: Basic Electronics-18ELN14Document12 pagesRegulation - 2018: Basic Electronics-18ELN14DaisyQueenNo ratings yet

- Chapter 8: Field Effect Transistors: A. Introduction To FetsDocument10 pagesChapter 8: Field Effect Transistors: A. Introduction To FetsBmanNo ratings yet

- ElectronicsDocument22 pagesElectronicsVARSHITH REDDY JNo ratings yet

- IV. Field Effect Transistor CompleteDocument42 pagesIV. Field Effect Transistor Completegarlic breadNo ratings yet

- Mosfet: Device StructureDocument15 pagesMosfet: Device StructureNoorullah ShariffNo ratings yet

- B.E. FETs and Other Components NotesDocument12 pagesB.E. FETs and Other Components NotesLaxman SalianNo ratings yet

- MEC Notes by Swamy PDFDocument217 pagesMEC Notes by Swamy PDFRajeevSangamNo ratings yet

- Anotes 6Document7 pagesAnotes 6Angie MaldonadoNo ratings yet

- Unit I - FETDocument19 pagesUnit I - FETJadhav BhagavatNo ratings yet

- Field Effect Transistor, Ujt, SCR, Triac: Scope of The ChapterDocument8 pagesField Effect Transistor, Ujt, SCR, Triac: Scope of The ChapterAkhilesh PandeNo ratings yet

- Unit 3 Field Effect Transistor JfetDocument21 pagesUnit 3 Field Effect Transistor Jfetrakesh hudedNo ratings yet

- 04 - Second-Order Effects On MOSFET Small Signal ModelDocument27 pages04 - Second-Order Effects On MOSFET Small Signal ModelWinnie LahNo ratings yet

- Mosfet Notes 1Document9 pagesMosfet Notes 1Anil SaiNo ratings yet

- Observations: Experimental ValuesDocument7 pagesObservations: Experimental ValuesShibeshwar MandalNo ratings yet

- Lecture Note 1Document120 pagesLecture Note 1LinhHoàngTrươngNo ratings yet

- 368463600-JFET-Summary - PPT 20240314 132059 0000Document91 pages368463600-JFET-Summary - PPT 20240314 132059 0000Yanis SlimaniNo ratings yet

- 7 JFET CharacteristicsDocument22 pages7 JFET CharacteristicsAnsar AnsarNo ratings yet

- Field-Effect Transistors - Part 1: Reference Book: Electronic Devices and Circuit Theory (11 Edition) Robert F. BoylestadDocument27 pagesField-Effect Transistors - Part 1: Reference Book: Electronic Devices and Circuit Theory (11 Edition) Robert F. BoylestadKazi TanvirNo ratings yet

- Regulation - 2018 Basic Electronics-18ELN14Document12 pagesRegulation - 2018 Basic Electronics-18ELN14Fairoz FairozNo ratings yet

- JFET TouhidDocument32 pagesJFET TouhidA.K.M.TOUHIDUR RAHMANNo ratings yet

- Unit - Vi Field Effect TransistorDocument16 pagesUnit - Vi Field Effect TransistorBhavaniPrasadNo ratings yet

- Experiment No:: Date: AIM: To Obtain Transfer Characteristics of Field Effect Transistor (FET) TheoryDocument2 pagesExperiment No:: Date: AIM: To Obtain Transfer Characteristics of Field Effect Transistor (FET) TheoryDharmistha VishwakarmaNo ratings yet

- E MosfetDocument5 pagesE MosfetSRMEA SAN RAFAEL BULACANNo ratings yet

- CH 63 PDFDocument26 pagesCH 63 PDFJawad Ul Hassan ShahNo ratings yet

- L-6 (DK) (Pe) ( (Ee) Nptel) 4Document3 pagesL-6 (DK) (Pe) ( (Ee) Nptel) 4GagneNo ratings yet

- EDC (JFETs-2)Document17 pagesEDC (JFETs-2)Narinder MauryaNo ratings yet

- Final MosfetDocument33 pagesFinal MosfetabdallaNo ratings yet

- ELN-Module 2 Notes VtuDocument12 pagesELN-Module 2 Notes VtuFariya TasneemNo ratings yet

- My Lec MOSFET All F MineDocument25 pagesMy Lec MOSFET All F MineArun JagaNo ratings yet

- Edc 4 UnitDocument26 pagesEdc 4 UnitAnonymous 6Ts3r7dwNo ratings yet

- MOSFET Physical Operation (Cont'd) MOSFET Current/Voltage CharacteristicsDocument16 pagesMOSFET Physical Operation (Cont'd) MOSFET Current/Voltage CharacteristicsSuleman KhanNo ratings yet

- Electronics Hons C3 FET Field Effect TransistorDocument21 pagesElectronics Hons C3 FET Field Effect TransistorGawrav BaishyaNo ratings yet

- Unit 2Document69 pagesUnit 2KISHAN SHUKLANo ratings yet

- Metal Oxide Semiconductor TransistorsDocument39 pagesMetal Oxide Semiconductor TransistorsK MukundNo ratings yet

- 30 Mosfet TheoryDocument6 pages30 Mosfet TheoryAruna KumarasiriNo ratings yet

- Chapter 10 Field Effect TransistorsDocument48 pagesChapter 10 Field Effect TransistorsanjugaduNo ratings yet

- Assignment 1Document9 pagesAssignment 1Taslima Rahman MiliNo ratings yet

- Chapter 4Document16 pagesChapter 4firomsaguteta12No ratings yet

- Field-Effect TransistorsDocument50 pagesField-Effect TransistorsMUHAMMAD SMITHNo ratings yet

- Electronics Chapter 4Document16 pagesElectronics Chapter 4YidnekachewNo ratings yet

- Mosfet SDocument25 pagesMosfet SZZZZZ5No ratings yet

- AnalogEl 2 FETDocument38 pagesAnalogEl 2 FETAlbert GenceNo ratings yet

- Unit 4 JFETDocument13 pagesUnit 4 JFETpranjaldesai453No ratings yet

- Mosfet Characteristics Mosfets Are Tri-Terminal, Unipolar, Voltage-Controlled, High Input Impedance DevicesDocument5 pagesMosfet Characteristics Mosfets Are Tri-Terminal, Unipolar, Voltage-Controlled, High Input Impedance DeviceseswaranNo ratings yet

- PH3007 Logic Families L 29 - 31Document33 pagesPH3007 Logic Families L 29 - 31Nethmi LokusuriyaNo ratings yet

- Controlled Devices FET, BJT, IGBTDocument51 pagesControlled Devices FET, BJT, IGBTHolloGramNo ratings yet

- FET TransistorsDocument19 pagesFET TransistorsOmer BallakNo ratings yet

- Mos Transistor TheoryDocument144 pagesMos Transistor TheorymailtolokiNo ratings yet

- Mosfet CharacteristicsDocument10 pagesMosfet CharacteristicsAnonymous eWMnRr70qNo ratings yet

- MOSFET Characteristics (ECE126: Laboratory 1)Document13 pagesMOSFET Characteristics (ECE126: Laboratory 1)Klinn Cabresos100% (1)

- Chapter 4 Ele IDocument16 pagesChapter 4 Ele Ibiruk satnawNo ratings yet

- Experiment 3: N-Channel Jfet Characteristics: ED Sem IiiDocument6 pagesExperiment 3: N-Channel Jfet Characteristics: ED Sem IiiDipankar PokhrelNo ratings yet

- Field Effect Transistors (FET) : Comparison Between BJT and FETDocument9 pagesField Effect Transistors (FET) : Comparison Between BJT and FETpranavraikar1No ratings yet

- Egr CycloidDocument1 pageEgr CycloidharshNo ratings yet

- MCQ Test Fac-Sy (Cca) : EmailDocument7 pagesMCQ Test Fac-Sy (Cca) : EmailharshNo ratings yet

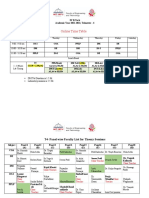

- SY BTech CSE T4 Online Time TableDocument3 pagesSY BTech CSE T4 Online Time TableharshNo ratings yet

- Solid State NumericalsDocument4 pagesSolid State NumericalsharshNo ratings yet

- ECE Events ScheduleDocument1 pageECE Events ScheduleharshNo ratings yet

- Trimester II - DivB (ECE)Document1 pageTrimester II - DivB (ECE)harshNo ratings yet

- Experiment No: 01: Trimester: VI Subject: Communication SystemsDocument4 pagesExperiment No: 01: Trimester: VI Subject: Communication SystemsharshNo ratings yet

- Student Examination Manual - CodetantraDocument56 pagesStudent Examination Manual - CodetantraharshNo ratings yet

- Assignment 4 Implementation (PPS)Document8 pagesAssignment 4 Implementation (PPS)harshNo ratings yet

- IESA SAEISS Advanced Battery Technologies BrochureDocument1 pageIESA SAEISS Advanced Battery Technologies BrochureharshNo ratings yet

- Faculty of Engineering School of Polytechnic & Skill DevelopmentDocument3 pagesFaculty of Engineering School of Polytechnic & Skill DevelopmentharshNo ratings yet

- Op-Amps Experiment Theory: 1. ObjectiveDocument14 pagesOp-Amps Experiment Theory: 1. ObjectiveharshNo ratings yet

- FY SY TY Integrated B TechDocument1 pageFY SY TY Integrated B TechharshNo ratings yet

- Recitation 11: Small Signal Model of MOSFET/MOSFET in Digital CircuitsDocument9 pagesRecitation 11: Small Signal Model of MOSFET/MOSFET in Digital CircuitsharshNo ratings yet

- Homogeneous TransformDocument12 pagesHomogeneous TransformharshNo ratings yet

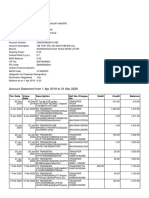

- Account Statement From 1 Apr 2019 To 31 Mar 2020: TXN Date Value Date Description Ref No./Cheque No. Debit Credit BalanceDocument3 pagesAccount Statement From 1 Apr 2019 To 31 Mar 2020: TXN Date Value Date Description Ref No./Cheque No. Debit Credit BalanceharshNo ratings yet

- MT-063 Tutorial: Basic Three Op Amp In-Amp ConfigurationDocument5 pagesMT-063 Tutorial: Basic Three Op Amp In-Amp ConfigurationharshNo ratings yet

- Booking Details: What Documents I Need To Board My Bus?Document2 pagesBooking Details: What Documents I Need To Board My Bus?harshNo ratings yet

- TD830Document47 pagesTD830edomaldoNo ratings yet

- Inversor - PV35 PRO - 6KDocument1 pageInversor - PV35 PRO - 6KPaolo Cesar Castro DiazNo ratings yet

- EGS300BS-6: Generator Set PerformanceDocument8 pagesEGS300BS-6: Generator Set PerformancefajarputraNo ratings yet

- DG Set PF CorrectionDocument22 pagesDG Set PF CorrectionPRIYANK ARORANo ratings yet

- IV Year Syllabus-2023-24Document34 pagesIV Year Syllabus-2023-24yashwanth h nNo ratings yet

- Diomedes: Inno Vation T Ha T Lif Tsy OuDocument2 pagesDiomedes: Inno Vation T Ha T Lif Tsy Outhanggimme.phanNo ratings yet

- ADC Lab3 PDFDocument11 pagesADC Lab3 PDFFarhan NitrateNo ratings yet

- Ikhtiyar Ali Khan PDFDocument2 pagesIkhtiyar Ali Khan PDFikhtiyar ali khan ikhtiyarNo ratings yet

- "Automatic Solar Energy Tracking System": Project Presentation ONDocument15 pages"Automatic Solar Energy Tracking System": Project Presentation ONPawan GuptaNo ratings yet

- Smoke Detector 2351EC HoneywellDocument2 pagesSmoke Detector 2351EC HoneywellFAMYA FIRE SAFETY SYSTEMSNo ratings yet

- 12V To 120V DC DC Converter Using Power Electronics For Higher Efficiency and Reliable Operation PDFDocument23 pages12V To 120V DC DC Converter Using Power Electronics For Higher Efficiency and Reliable Operation PDFAndy Espinosa GutiérrezNo ratings yet

- Lecture # 1Document28 pagesLecture # 1PhD EENo ratings yet

- Vin FastDocument4 pagesVin FastHạnh TrươngNo ratings yet

- Samson Servo 120 - Power Amplifier ManualDocument13 pagesSamson Servo 120 - Power Amplifier ManualTiestoworld CrewNo ratings yet

- Eee 2021Document16 pagesEee 2021Marami BaishyaNo ratings yet

- Weidmuller Cat10 ShortForm SmartDocument164 pagesWeidmuller Cat10 ShortForm SmartCesar Solis TarangoNo ratings yet

- Service Manual: CDX-L480XDocument40 pagesService Manual: CDX-L480XjohnnybiliNo ratings yet

- Silver Engineering Co Solar PanelDocument1 pageSilver Engineering Co Solar PanelPankaj JaiswalNo ratings yet

- Charger Ripple Current Effect v2Document4 pagesCharger Ripple Current Effect v2diyitNo ratings yet

- Simulation of Inverter Fed Induction Motor Drive With LabviewDocument5 pagesSimulation of Inverter Fed Induction Motor Drive With LabviewRAVIKANTH BALIVADANo ratings yet

- Payback CalculationDocument2 pagesPayback CalculationVenkat CherukuriNo ratings yet

- 1MRK511310-UUS A en Application Manual Bay Control REC670 2.0 ANSIDocument570 pages1MRK511310-UUS A en Application Manual Bay Control REC670 2.0 ANSIGilcimar DiasNo ratings yet

- Assignment Topics: Dominant ModeDocument67 pagesAssignment Topics: Dominant ModeXyzNo ratings yet

- Termistor NTC Mf73t-1Document4 pagesTermistor NTC Mf73t-1Tatys SoleNo ratings yet

- DatasheetDocument48 pagesDatasheetIng Salinas RodriguezNo ratings yet

- MTH 103e050719revisedDocument2 pagesMTH 103e050719revisedAchmad Jauhar EfendiNo ratings yet

- 01 Laboratory Exercise 2Document4 pages01 Laboratory Exercise 2ruzzelNo ratings yet

- F-MPC60B Series: User's ManualDocument146 pagesF-MPC60B Series: User's Manualpika100% (1)

Field-Effect (FET) Transistors: ECE60L Lecture Notes, Spring 2003

Field-Effect (FET) Transistors: ECE60L Lecture Notes, Spring 2003

Uploaded by

harshOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Field-Effect (FET) Transistors: ECE60L Lecture Notes, Spring 2003

Field-Effect (FET) Transistors: ECE60L Lecture Notes, Spring 2003

Uploaded by

harshCopyright:

Available Formats

Field-Effect (FET) transistors

References: Barbow (Chapter 8), Rizzoni (chapters 8 & 9)

In a field-effect transistor (FET), the width of a conducting channel in a semiconductor and,

therefore, its current-carrying capability, is varied by the application of an electric field (thus,

the name field-effect transistor). As such, a FET is a “voltage-controlled” device. The most

widely used FETs are Metal-Oxide-Semiconductor FETs (or MOSFET). MOSFET can be

manufactured as enhancement-type or depletion-type MOSFETs. Another type of FET is

the Junction Field-Effect Transistors (JFET) which is not based on metal-oxide fabrication

technique. FETs in each of these three categories can be fabricated either as a n-channel

device or a p-channel device. As transistors in these 6 FET categories behave in a very

similar fashion, we will focus below on the operation of enhancement MOSFETs that are

the most popular.

n-Channel Enhancement-Type MOSFET (NMOS)

The physical structure of a n-Channel Enhancement-Type MOSFET (NMOS) is shown.

The device is fabricated on a p-type substrate (or Body). Two heavily doped n-type re-

gions (Source and Drain) are created in the substrate. A thin (fraction of micron) layer

of SiO2 , which is an excellent electrical insulator, is deposited between source and drain

region. Metal is deposited on the insulator to form the Gate of the device (thus, metal-oxide

semiconductor). Metal contacts are also made to the source, drain, and body region.

To see the operation of a NMOS, let’s ground the source and the body and apply a voltage

vGS between the gate and the source, as is shown above. This voltage repels the holes

in the p-type substrate near the gate region, lowering the concentration of the holes. As

vGS increases, hole concentration decreases, and the region near gate behaves progressively

more like intrinsic semiconductor material (when excess hole concentration is zero) and then,

finally, like a n-type material as electrons from n+ electrodes (source and drain) enter this

region. As a result, when vGS become larger than a threshold voltage, Vt , a narrow layer

ECE60L Lecture Notes, Spring 2003 68

between source and drain regions is created that is populated with n-type charges (see figure).

The thickness of this channel is controlled by the applied vGS (it is proportional to vGS − Vt ).

As can be seen, this device works as a channel is induced in the semiconductor and this

channel contains n-type charges (thus, n-channel MOSFET). In addition, increasing vGS

increases channel width (enhances it). Therefore, this is an n-channel Enhancement-type

MOSFET or Enhancement-type NMOS.

Now for a given values of vGS > Vt (so

that the channel is formed), let’s apply

a small and positive voltage vDS between

drain and source. Then, electrons from n+

source region enter the channel and reach

the drain. If vDS is increased, current iD

flowing through the channel increases. Ef-

fectively, the device acts like a resistor; its

resistance is set by the dimension of the

channel and its n-type charge concentra-

tion. In this regime, plot of iD versus

vDS is a straight line (for a given values

of vGS > Vt ) as is shown.

The slope of iD versus vDS line is the conductance of the channel. For vGS ≤ Vt no channel

exists (zero conductance). As value of vGS − Vt increases, channel becomes wider and its

conductivity increases (because its n-type charge concentration increases). Therefore, the

channel conductance (slope of iD versus vDS line) increases with any increase in vGS − Vt as

is shown above.

The above description is correct for small

values of vDS as in that case, vGD = vGS −

vDS ≈ vGS and the induced channel is

fairly uniform (i.e., has the same width

near the drain as it has near the source).

For a given vGS > Vt , if we now increase

vDS , vGD = vGS − vDS becomes smaller

than vGS . As such the size of channel near

drain becomes smaller compared to its size

near the source, as is shown. As the size

of channel become smaller, its resistance

increases and the curve of iD versus vDS

starts to roll over, as is shown below.

ECE60L Lecture Notes, Spring 2003 69

For values of vGD = Vt (or vDS = vGS − Vt ), width of the channel approaches zero near the

drain (channel is “pinched” off). Increasing vDS beyond this value has little effect (no effect

in our simple picture) on the channel shape, and the current through the channel remains

constant at the value reached when vDS = vGS − Vt . So when the channel is pinched off, iD

only depends on vGS (right figure below).

NMOS Characteristic Curves iD versus vGS in the active (or saturation) regime

In sum, a FET can operate in three regimes:

1) Cut-off regime in which no channel exists (vGS < Vt for NMOS) and iD = 0 for any vDS .

2) Ohmic or Triode regime in which the channel is formed and not pinched off (vGS > Vt

and vDS ≤ vGS − Vt for NMOS) and FET behaves as a “voltage-controlled” resistor.

3) Active or Saturation regime in which the channel is pinched off (vGS ≥ Vt and vDS >

vGS − Vt for NMOS) and iD does not change with vDS .

Several important point should be noted:

1) No current flows into the gate, iG = 0 (note the insulator between gate and the body).

2) FET acts as a “voltage-controlled” resistor in the ohmic region. In addition, when v DS

vGS , FET would act as a linear resistor.

3) When FET is in cut-off, iD = 0. However, if iD = 0, this does not mean that FET is

in cut-off. FET is in cut-off only when a channel does not exist (vGS < Vt ) and iD = 0

for any applied vDS . On the other hand, FET can be in ohmic region, i.e., a channel is

formed, but iD = 0 because vDS = 0.

ECE60L Lecture Notes, Spring 2003 70

4) The third regime is called “saturation” in most electronic books because iD is “saturated”

in this regime and does not increase further. This is a rather unfortunate name as “satura-

tion” regime in a FET means very different thing than it does in a BJT. Some newer books

call this regime “active” (as it equivalent to “active-linear” regime of a BJT).

5) The transition between ohmic and active region is clearly defined by vDS = vGS − Vt the

point where the channel is pinched off.

The iD versus vDS characteristic curves of a FET look very similar to iC versus vCE char-

acteristics curves of a BJT. In fact, as there is a unique relationship between iB and vBE ,

the iC versus vCE characteristic curves of a BJT can be “labeled” with different values of

vBE instead of iB , making the characteristic curves of the two devices even more similar.

In FET vGS control device behavior and in BJT vBE . Both devices are in cut-off when the

“input” voltage is below a threshold value: vBE < vγ for BJT and vGS < Vt for NMOS. They

exhibit an “active” regime in which the “output” current (iC or iD ) is roughly constant as

the “output” voltage (vCE or vDS ) is changed. There are, however, major differences. Most

importantly, a BJT requires iB to operate but in a FET iG = 0 (actually very small). These

differences become clearer as we explore FETs.

As can be seen from NMOS physical structure,

D

the device is symmetric, that is position of drain

and source can be replaced without any change in

device properties. The circuit symbol for a NMOS G B

is shown on the right. For most applications, how-

ever, the body is connected to the source, leading S

to a 3-terminal element. In that case, source and

D D

drain are not interchangeable. A simplified circuit iD iD

symbol for this configuration is usually used. By

convention, current iD flows into the drain for a G G

NMOS (see figure). As iG = 0, the same current

will flow out of the source. S S

Direction of “arrows” used to identify semiconductor types in a transistor may appear con-

fusing. The arrows do NOT represent the direction of current flow in the device. Rather,

they denote the direction of the underlying pn junction. For a NMOS, the arrow is placed

on the body and pointing inward as the body is made of p-type material. (Arrow is not

on source or drain as they are interchangeable.) In the simplified symbol for the case when

body and source is connected, arrow is on the source (device is not symmetric now) and is

pointing outward as the source is made of n-type materials. (i.,e. arrow pointing inward for

p-type, arrow pointing outward for n-type).

ECE60L Lecture Notes, Spring 2003 71

NMOS iD versus vDS Characteristics Equations

Like BJT, a NMOS (with source connected to body) has six parameters (three voltages and

three currents), two of which (iS and vGD ) can be found in terms of the other four by KVL

and KCL. NMOS is simpler than BJT because iG = 0 (and iS = iD ). Therefore, three

parameters describe behavior of a NMOS (vGS , iD , and vDS ). NMOS has one characteristics

equation that relates these three parameters. Again, situation is simpler than BJT as simple

but accurate characteristics equations exist.

Cut-off: vGS < Vt , iD = 0 for any vDS

2

Ohmic: vGS > Vt , iD = K[2vDS (vGS − Vt ) − vDS ] for vDS < vGS − Vt

Active: vGS > Vt , iD = K(vGS − Vt )2 for vDS > vGS − Vt

In the above, K and Vt are constants that depend on manufacturing of the NMOS (given in

manufacturer spec sheets). As mentioned above, for small values of vDS (vDS vGS − Vt ),

NMOS behaves as resistor, rDS , and the value of rDS is controlled by vGS − Vt . This can be

2

seen by dropping vDS in iD equation of ohmic regime:

vDS 1

rDS = ≈

iD 2K(vGS − Vt )

How to Solve NMOS Circuits:

Solution method is very similar to BJT circuit (actually simpler because iG = 0). To solve,

we assume that NMOS is in a particular state, use NMOS model for that state to solve the

circuit and check the validity of our assumption by checking the inequalities in the model

for that state. A formal procedure is:

1) Write down a KVL including GS terminals (call it GS-KVL).

2) Write down a KVL including DS terminals (call it DS-KVL).

3) From GS-KVL, compute vGS (using iG = 0)

3a) If vGS < Vt , NMOS is in cut-off. Let iD = 0, solve for vDS from DS-KVL. We are done.

3b) If vGS > Vt , NMOS is not in cut-off. Go to step 4.

4) Assume NMOS is in active region. Compute iD from iD = K(vGS − Vt )2 . Then, use

DS-KVL to compute vDS . If vDS > vGS − Vt , we are done. Otherwise go to step 5.

2

5) NMOS has to be in ohmic region. Substitute for iD from iD = K[2vDS (vGS − Vt ) − vDS ]

in DS-KVL. You will get a quadratic equation in vDS . Find vDS (one of the two roots of the

equation will be unphysical). Check to make sure that vDS < vGS − Vt . Substitute vDS in

DS-KVL to find iD .

ECE60L Lecture Notes, Spring 2003 72

Example: Consider NMOS circuit below with K = 0.25 mA/V2 and Vt = 2 V. Find vo

when vi = 0, 6, and 12 V for RD = 1 KΩ and VDD = 12 V.

VDD

GS-KVL: vGS = vi

DS-KVL: VDD = RD iD + vDS RD

vo

A) vi = 0 V. From GS-KVL, we get vGS = vi = 0. As vGS < Vt = D iD

vi G

2 V, NMOS is in cut-off, iD = 0, and vDS is found from DS-KVL:

DS-KVL: vo = vDS = VDD − RD iD = 12 V S

B) vi = 6 V. From GS-KVL, we get vGS = vi = 6 V. Since vGS = 6 > Vt = 2, NMOS is

not in cut-off. Assume NMOS in active region. Then:

iD = K(vGS − Vt )2 = 0.25 × 10−3 (6 − 2)2 = 4 mA

DS-KVL: vDS = VDD − RD iD = 12 − 4 × 103 × 10−3 = 8 V

Since vDS = 8 > vGS − Vt = 2, NMOS is indeed in active region and iD = 4 mA and

vo = vDS = 8 V.

C) vi = 12 V. From GS-KVL, we get vGS = 12 V. Since vGS > Vt , NMOS is not in

cut-off. Assume NMOS in active region. Then:

iD = K(vGS − Vt )2 = 0.25 × 10−3 (12 − 2)2 = 25 mA

DS-KVL: vDS = VDD − RD iD = 12 − 25 × 103 × 10−3 = −13 V

Since vDS = −13 < vGS − Vt = 12 − 2 = 10, NMOS is NOT in active region.

Assume NMOS in ohmic region. Then:

2 2

iD = K[2vDS (vGS − Vt ) − vDS ] = 0.25 × 10−3 [2vDS (12 − 2) − vDS ]

2

iD = 0.25 × 10−3 [20vDS − vDS ]

Substituting for iD in DS-KVL, we get:

DS-KVL: VDD = RD iD + vDS → 12 = 103 × 0.25 × 10−3 [20vDS − vDS

2

] + vDS

2

vDS − 24vDS + 48 = 0

ECE60L Lecture Notes, Spring 2003 73

This is a quadratic equation in vDS . The two roots are: vDS = 2.2 V and vDS = 21.8 V. The

second root is not physical as the circuit is powered by a 12 V supply. Therefore, vDS = 2.2 V.

As vDS = 2.2 < vGS − Vt = 10, NMOS is indeed in ohmic region with vo = vDS = 2.2 V and

12 − 2.2

DS-KVL: vDS = VDD − RD iD → iD = = 9.8 mA

1, 000

Load Line: Operation of NMOS circuits can be better understood using the concept of

load line. Similar to BJT, load line is basically the line representing DS-KVL in iD versus

vDS space. Load line of the example circuit is shown here.

Exercise: Mark the Q-points of the previous example for vi = 0, 6, and 12 V on the load

line figure below.

Body Effect

In deriving NMOS (and other MOS) iD versus vDS characteristics, we had assumed that

the body and source are connected. This is not possible in an integrated chip which has

a common body and a large number of MOS devices (connection of body to source for all

devices means that all sources are connected). The common practice is to attach the body

of the chip to the smallest voltage available from the power supply (zero or negative). In

this case, the pn junction between the body and source of all devices will be reversed biased.

The impact of this to lower threshold voltage for the MOS devices slightly and its called the

body effect. Body effect can degrade device performance. For analysis here, we will assume

that body effect is negligible.

ECE60L Lecture Notes, Spring 2003 74

p-Channel Enhancement-Type MOSFET (PMOS)

D

The physical structure of a PMOS is identical to a

NMOS except that the semiconductor types are in-

terchanged, i.e., body and gate are made of n-type G B

material and source and drain are made of p-type ma-

terial and a p-type channel is formed. As the sign of S

the charge carriers are reversed, all voltages and cur-

rents in a PMOS are reversed. By convention, the D D

iD iD

drain current is flowing out of the drain as is shown.

With this, all of the NMOS discussion above applies G G

to PMOS as long as we multiply all voltages by a

minus sign: S S

Cut-off: vGS > Vt , iD = 0 for any vDS

2

Ohmic: vGS < Vt , iD = K[2vDS (vGS − Vt ) − vDS ] for vDS > vGS − Vt

Active: vGS < Vt , iD = K(vGS − Vt )2 for vDS < vGS − Vt

Note that Vt is negative for a PMOS.

Complementary MOS (CMOS)

Complementary MOS technology employs MOS transistors of both polarites as is shown

below. CMOS devices are more difficult to fabricate than NMOS, but many more powerful

circuits are possible with CMOS configuration. As such, most of MOS circuits today employ

CMOS configuration and CMOS technology is rapildy taking over many applications that

were possible only with bipolar devices a few years ago.

S2

G2

iD2

vi D2

vo

D1 iD1

G1

S1

ECE60L Lecture Notes, Spring 2003 75

Depletion-Type MOSFET

The depletion-type MOSFET has a structure similar to the enhancement-type MOSFET

with only one important difference; depletion-type MOSFET has a physically implanted

channel. Thus, a n-type depletion-type MOSFET has already a n-type channel between

drain and source. When a voltage vDS is applied to the device, a current iD = IDSS flows

even for vGS = 0. (Show IDDS = KVt2 .) Similar to NMOS, if vGS is increased, the channel

become wider and iD increases. However, in a n-type depletion-type MOSFET, a negative

vGS can also be applied to the device, which makes the channel smaller and reduces iD .

As such, negative vGS “depletes” the channels from n-type carriers leading to the name

depletion-type MOSFET. If vGS is reduced further, at some threshold value Vt (which is

negative), the channel disappears and iD = 0, as is seen in the figure. It should be obvious

that a depletion-type MOSFET can be operated either in enhancement mode or in depletion

mode. p-type depletion MOSFET operate similarly to p-type enhancement MOSFET expect

that Vt > 0 for depletion type and Vt < 0 for the enhancement type. Figure below shows

iD versus vGS of four types of MOSFET devices in the active region. Circuit symbols for

depletion-type MOSFET devices are also shown.

D D

G B G B

S S

D D D D

iD iD iD iD

G G G G

S S S S

n-type Depletion MOSFET p-type Depletion MOSFET

ECE60L Lecture Notes, Spring 2003 76

NMOS Inverter and Switch

VDD

The basic NMOS inverter circuit is shown; the circuit is

very similar to a BJT inverter. This circuit was solved

RD

in page 65 for VDD = 12 and RD = 1 kΩ. We found that

vo

if vi = 0 (in fact vi < Vt ), NMOS will be in cut-off with

D iD

iD = 0 and vo = VDD . When vi = 12 V, NMOS will

vi G

be in ohmic region with iD = 10 mA and vDS = 2.2 V.

Therefore, the circuit is an inverter gate. It can also be

S

used as switch.

There are some important difference between NMOS and BJT inverter gates. First, BJT

needs a resistor RB . This resistor “converts” the input voltages into an iB and keep vBE ≈ vγ .

NMOS does not need a resistor between the source and the input voltage as iG = 0 and

vi = vGS can be directly applied to the gate. Second, if the input voltage is “high,” the BJT

will go into saturation with vo = vCE = Vsat = 0.2 V. In the NMOS gate, if the input voltage

is “high,” NMOS is in the ohmic region. In this case, vDS can have any value between 0 and

vGS − Vt ; the value of vo = vDS is set by the value of the resistor RD . This effect is shown

in the transfer function of the inverter gate for two different values of RD .

Exercise: Compute vo for the above circuit with VDD = 12 and RD = 10 kΩ when vi = 12 V.

ECE60L Lecture Notes, Spring 2003 77

CMOS Inverter

The CMOS inverter, the building block of CMOS logic gates, is shown below. The “low”

and “high”states for this circuit correspond to 0 and VDD , respectively. CMOS gates are

built on the same chip such that both NMOS and PMOS have the same threshold voltage

Vtn = V̄t , Vtp = −V̄t and same K (one needs different channel length and width to get the

same K for PMOS and NMOS). In this case, the CMOS will have a “symmetric” transfer

characteristics, i.e., vo = 0.5VDD when vi = 0.5VDD as is shown below. This circuit works

only if VDD > 2Vt by a comfortable margin.

vi = 0 Since vGS1 = vi = 0 < V̄t , NMOS will be in cut-off. Therefore, iD1 = 0. But

vGS2 = vi −VDD = −VDD < −V̄t , thus, PMOS will be ON. Recall iD versus vDS characteristic

curves of a NMOS (page 63), each labeled with a values of VGS . As vGS2 = VDD is a constant,

operating point of PMOS will be on one of the curves. But iD1 = iD2 = 0 and the only point

that satisfies this condition is vDS2 = 0. Note that PMOS is NOT in cut-off, it is in ohmic

region and acts like a resistor. vDS2 = 0 because iD2 = 0. Output voltage can now be found

by KVL: vo = VDD − vDS2 = VDD . So, when vi = 0, vo = VDD .

vi = VDD Since vGS1 = vi = VDD > V̄t , NMOS will be ON. But since vGS2 = vi − VDD =

0 > −V̄t , PMOS will be in cut-off and iD2 = 0. Since iD1 = iD2 , iD1 = 0. Since NMOS is

on and iD1 = 0, NMOS should be in ohmic region with vDS1 = 0. Then vo = vDS1 = 0. So,

when vi = VDD , vo = 0

vi = 0.5VDD In this case, vGS1 = vi = 0.5VDD and vGS2 = vi − VDD = −0.5VDD . Since,

vGS1 > V̄t and vGS2 < −V̄t , both transistors will be ON. Furthermore, as transistors have

same threshold voltage, same K, iD1 = iD2 , and vGS1 = |vGS2 |, both transistor will be in

the same state (either ohmic or active) and will have identical vDS : vDS1 = −vDS2 . Since

vDS1 − vDS2 = VDD , then vDS1 = 0.5VDD , vDS2 = −0.5VDD , and vo = 0.5VDD . Note that

since VDD > 2Vt , both transistors are in the active region.

The transfer function of the CMOS inverter is shown below.

VDD NMOS Off

Vo PMOS Ohmic

S2 NMOS Active

G2 PMOS Ohmic

iD2

vi D2 NMOS Active

vo PMOS Active

D1 iD1 NMOS Ohmic

G1

PMOS Active

NMOS Ohmic

S1 PMOS Off

Vi

ECE60L Lecture Notes, Spring 2003 78

CMOS inverter has many advantages compared to the NMOS inverter. Its transfer function

is much closer to an ideal inverter transfer function. The “low” and high” states are clearly

defined (low state of NMOS depended on the value of RD ). It does not include any resistors

and thus takes less area on the chip. Lastly, iD1 = iD2 = 0 for both cases of output being low

or high. This means that the gate consumes very little power (theoretically zero) in either

state. A non-zero iD1 = iD2 , however, flows in the circuit when the gate is transitioning from

one state to another as is seen in the figure.

The maximum value of iD that flows through the gate during the transition can be easily

calculated as this maximum current flows when vi = 0.5VDD and vo = 0.5VDD .

For example, consider the CMOS inverter with VDD = 12 V, V̄t = 2 V, and K = 0.25 mA/V2 .

Maximum iD flows when vi = vGS1 = 0.5VDD = 6 V. At this point, vDS1 = vo = 0.5VDD =

6 V. As, vDS1 = 6 > vGS1 − vt = 4 V, NMOS is in active regime. Then:

iD1 = K(vGS1 − Vt )2 = 0.25 × 10−3 (6 − 2)2 = 4 mA

ECE60L Lecture Notes, Spring 2003 79

CMOS NAND Gate

As mentioned before CMOS logic gates have VDD

“low” and “high” states of 0 and VDD , respec-

M3 M4

tively. We need to consider all possible cases to

show that this a NAND gate. To start, we can iD3 iD4

several general observations: vo

v2 iD2

1) by KVL vGS1 = v1 , vGS2 = v2 − vDS1 , vGS3 =

v1 − VDD , and vGS4 = v2 − VDD , M2

iD1

2) by KCL iD1 = iD2 = iD3 + iD4 v1

3) by KVL vo = vDS1 + vDS2 = VDD + vDS3 and M1

vDS3 = vDS4 .

The procedure to solve/analyze CMOS gates are as follows: // A) For a given set of input

voltages, use KVLs (similar to 1 above) to find vGS of all transistors and find which ones

are ON or OFF.// B) Set iD = 0 for all transistors that are OFF. Use KCLs (similar to

2 above) to find iD for other transistors.// C) Look for transistors that are ON and have

iD = 0. These transistors have to be in Ohmic region with vDS = 0. D) Use KVLs (similar

to 3 above) to find vo based on vDS .

v1 = 0, v2 = 0

We first find vGS and state of all transistors by using KVLS in no. 1 above.

vGS1 = v1 = 0 < V̄t → M1 is OFF → iD1 = 0

vGS2 = v2 − vDS1 = −vDS1 → M2 is ?

vGS3 = v1 − VDD = −VDD < −V̄t → M3 is ON

vGS4 = v2 − VDD = −VDD < −V̄t → M4 is ON

Since iD1 = 0, by KCLs in no. 2 above , iD2 = iD1 = 0 and iD3 + iD4 = iD1 = 0. Since

iD ≥ 0 for both PMOS and NMOS, the last equation can be only satisfied if iD3 = iD4 = 0.

We add the value of iD to the table above and look for transistors that are ON and have

iD = 0. These transistors have to be in Ohmic region with vDS = 0.

vGS1 = v1 = 0 < V̄t → M1 is OFF → iD1 =0

vGS2 = v2 − vDS1 = −vDS1 → M2 is ? iD2 =0

vGS3 = v1 − VDD = −VDD < −V̄t → M3 is ON iD3 = 0 → vDS3 = 0

vGS4 = v2 − VDD = −VDD < −V̄t → M4 is ON iD4 = 0 → vDS4 = 0

Finally, from KVLs in no. 3. above, we have vo = VDD + vDS3 = VDD . So, when both inputs

are low, the output is HIGH.

ECE60L Lecture Notes, Spring 2003 80

If needed, we can go back and find the state of M2. Assume M2 is ON. This requires

vGS2 > V̄t . Since iD2 = 0 and M2 is ON, vDS2 = 0 (M2 in Ohmic). From KVLs in no. 3.

above, we have vo = vDS1 + vDS2 = VDD . This gives vDS1 = VDD and vGS2 = v2 − vDS1 =

VDD − VDD = 0 < V̄t , a contradiction of our assumption of M2 being ON. Therefore, M2

should be OFF.

v1 = 0, v2 = VDD

We first find vGS and state of all transistors by using KVLS in no. 1 above.

vGS1 = v1 = 0 < V̄t → M1 is OFF → iD1 = 0

vGS2 = v2 − vDS1 = VDD − vDS1 → M2 is ?

vGS3 = v1 − VDD = −VDD < −V̄t → M3 is ON

vGS4 = v2 − VDD = 0 > −V̄t → M4 is OFF → iD4 = 0

Since iD1 = 0, by KCLs in no. 2 above , iD2 = iD1 = 0. Also, iD3 + iD4 = iD1 = 0 leading

to iD4 = 0. We add the value of iD to the table above and look for transistors that are ON

and have iD = 0. These transistors have to be in Ohmic region with vDS = 0.

vGS1 = v1 = 0 < V̄t → M1 is OFF → iD1 =0

vGS2 = v2 − vDS1 = VDD − vDS1 → M2 is ? iD2 =0

vGS3 = v1 − VDD = −VDD < −V̄t → M3 is ON iD3 = 0 → vDS3 = 0

vGS4 = v2 − VDD = 0 > −V̄t → M4 is OFF → iD4 =0

Finally, from KVLs in no. 3. above, we have vo = VDD + vDS3 = VDD . So, when v1 is LOW

and v2 is HIGH, the output is HIGH.

We can go back and find the state of M2. We will find M2 to be ON (left for students).

v1 = VDD , v2 = 0

We first find vGS and state of all transistors by using KVLS in no. 1 above.

vGS1 = v1 = VDD > V̄t → M1 is ON

vGS2 = v2 − vDS1 = −vDS1 < V̄t → M2 is OFF → iD2 = 0

vGS3 = v1 − VDD = 0 > −V̄t → M3 is OFF → iD3 = 0

vGS4 = v2 − VDD = −VDD < −V̄t → M4 is ON

In the above, we used the fact that vDS1 ≥ 0. Since iD2 = 0, by KCLs in no. 2 above ,

iD1 = iD2 = 0. Also, iD3 + iD4 = iD2 = 0 leading to iD4 = 0. We add the value of iD to the

ECE60L Lecture Notes, Spring 2003 81

table above and look for transistors that are ON and have iD = 0. These transistors have to

be in Ohmic region with vDS = 0.

vGS1 = v1 = VDD > V̄t → M1 is ON

vGS2 = v2 − vDS1 = −vDS1 < V̄t → M2 is OFF → iD2 = 0 → vDS2 = 0

vGS3 = v1 − VDD = 0 > −V̄t → M3 is OFF → iD3 = 0 → vDS3 = 0

vGS4 = v2 − VDD = −VDD < −V̄t → M4 is ON

Finally, from KVLs in no. 3. above, we have vo = VDD + vDS3 = VDD . So, when v1 is HIGH

and v2 is LOW, the output is HIGH.

v1 = VDD , v2 = VDD

We first find vGS and state of all transistors by using KVLS in no. 1 above.

vGS1 = v1 = VDD > V̄t → M1 is ON

vGS2 = v2 − vDS1 = VDD − vDS1 → M2 is ?

vGS3 = v1 − VDD = 0 > −V̄t → M3 is OFF → iD3 = 0

vGS4 = v2 − VDD = 0 > −V̄t → M4 is OFF → iD4 = 0

From KCLs in no. 2 above , iD2 = iD1 = iD3 + iD4 = 0. We add the value of iD to the table

above and look for transistors that are ON and have iD = 0. These transistors have to be

in Ohmic region with vDS = 0.

vGS1 = v1 = VDD > V̄t → M1 is ON iD1 = 0 → vDS1 = 0

vGS2 = v2 − vDS1 = VDD − vDS1 = VDD > V̄t → M2 is ON iD2 = 0 → vDS2 = 0

vGS3 = v1 − VDD = 0 > −V̄t → M3 is OFF → iD3 =0

vGS4 = v2 − VDD = 0 > −V̄t → M4 is OFF → iD4 =0

In the above, we used vDS1 = 0 to find the state of M2 leading to vDS2 = 0. Finally, from

KVLs in no. 3. above, we have vo = vDS1 + vDS1 = 0. So, when v1 is HIGH and v2 is HIGH,

the output is LOW.

From the “truth table,” the output of this gate is LOW only if both input states are HIGH.

Therefore, this is a NAND gate.

CMOS NOR Gate

ECE60L Lecture Notes, Spring 2003 82

VDD

Exercise: Show that this is a NOR gate. M4

v2 iD4

M3

iD3 vo

v1 iD1 iD2

M2

M1

ECE60L Lecture Notes, Spring 2003 83

You might also like

- Std. 115 - 1995 - IEEE Guide, Test Procedures For Synchronous Machines PartIIDocument108 pagesStd. 115 - 1995 - IEEE Guide, Test Procedures For Synchronous Machines PartIIflywheel2006100% (2)

- Experiment-3:: Cadence Virtuoso 6.1.7 - 64bDocument9 pagesExperiment-3:: Cadence Virtuoso 6.1.7 - 64bSrujan MulkaNo ratings yet

- 100 KWDocument16 pages100 KWRajaNo ratings yet

- Electronic II-1Document10 pagesElectronic II-1Isaac DanielNo ratings yet

- Both Bjts and Fets, Are Equally Important and Each Offers Distinct Advantages and Has Unique Areas of Application.)Document19 pagesBoth Bjts and Fets, Are Equally Important and Each Offers Distinct Advantages and Has Unique Areas of Application.)Maxwell LumorNo ratings yet

- The Basic Structure: Field Effect TransistorDocument10 pagesThe Basic Structure: Field Effect TransistormokhaladNo ratings yet

- MOSFET Course Notes - MMA HAKIMDocument22 pagesMOSFET Course Notes - MMA HAKIMAdnan HossainNo ratings yet

- Junction Field Effect Transistor (JFET) : Gate Terminal. The Other Two Contacts, The Drain and Source, Are Placed atDocument8 pagesJunction Field Effect Transistor (JFET) : Gate Terminal. The Other Two Contacts, The Drain and Source, Are Placed atkingboyNo ratings yet

- Regulation - 2018: Basic Electronics-18ELN14Document12 pagesRegulation - 2018: Basic Electronics-18ELN14DaisyQueenNo ratings yet

- Chapter 8: Field Effect Transistors: A. Introduction To FetsDocument10 pagesChapter 8: Field Effect Transistors: A. Introduction To FetsBmanNo ratings yet

- ElectronicsDocument22 pagesElectronicsVARSHITH REDDY JNo ratings yet

- IV. Field Effect Transistor CompleteDocument42 pagesIV. Field Effect Transistor Completegarlic breadNo ratings yet

- Mosfet: Device StructureDocument15 pagesMosfet: Device StructureNoorullah ShariffNo ratings yet

- B.E. FETs and Other Components NotesDocument12 pagesB.E. FETs and Other Components NotesLaxman SalianNo ratings yet

- MEC Notes by Swamy PDFDocument217 pagesMEC Notes by Swamy PDFRajeevSangamNo ratings yet

- Anotes 6Document7 pagesAnotes 6Angie MaldonadoNo ratings yet

- Unit I - FETDocument19 pagesUnit I - FETJadhav BhagavatNo ratings yet

- Field Effect Transistor, Ujt, SCR, Triac: Scope of The ChapterDocument8 pagesField Effect Transistor, Ujt, SCR, Triac: Scope of The ChapterAkhilesh PandeNo ratings yet

- Unit 3 Field Effect Transistor JfetDocument21 pagesUnit 3 Field Effect Transistor Jfetrakesh hudedNo ratings yet

- 04 - Second-Order Effects On MOSFET Small Signal ModelDocument27 pages04 - Second-Order Effects On MOSFET Small Signal ModelWinnie LahNo ratings yet

- Mosfet Notes 1Document9 pagesMosfet Notes 1Anil SaiNo ratings yet

- Observations: Experimental ValuesDocument7 pagesObservations: Experimental ValuesShibeshwar MandalNo ratings yet

- Lecture Note 1Document120 pagesLecture Note 1LinhHoàngTrươngNo ratings yet

- 368463600-JFET-Summary - PPT 20240314 132059 0000Document91 pages368463600-JFET-Summary - PPT 20240314 132059 0000Yanis SlimaniNo ratings yet

- 7 JFET CharacteristicsDocument22 pages7 JFET CharacteristicsAnsar AnsarNo ratings yet

- Field-Effect Transistors - Part 1: Reference Book: Electronic Devices and Circuit Theory (11 Edition) Robert F. BoylestadDocument27 pagesField-Effect Transistors - Part 1: Reference Book: Electronic Devices and Circuit Theory (11 Edition) Robert F. BoylestadKazi TanvirNo ratings yet

- Regulation - 2018 Basic Electronics-18ELN14Document12 pagesRegulation - 2018 Basic Electronics-18ELN14Fairoz FairozNo ratings yet

- JFET TouhidDocument32 pagesJFET TouhidA.K.M.TOUHIDUR RAHMANNo ratings yet

- Unit - Vi Field Effect TransistorDocument16 pagesUnit - Vi Field Effect TransistorBhavaniPrasadNo ratings yet

- Experiment No:: Date: AIM: To Obtain Transfer Characteristics of Field Effect Transistor (FET) TheoryDocument2 pagesExperiment No:: Date: AIM: To Obtain Transfer Characteristics of Field Effect Transistor (FET) TheoryDharmistha VishwakarmaNo ratings yet

- E MosfetDocument5 pagesE MosfetSRMEA SAN RAFAEL BULACANNo ratings yet

- CH 63 PDFDocument26 pagesCH 63 PDFJawad Ul Hassan ShahNo ratings yet

- L-6 (DK) (Pe) ( (Ee) Nptel) 4Document3 pagesL-6 (DK) (Pe) ( (Ee) Nptel) 4GagneNo ratings yet

- EDC (JFETs-2)Document17 pagesEDC (JFETs-2)Narinder MauryaNo ratings yet

- Final MosfetDocument33 pagesFinal MosfetabdallaNo ratings yet

- ELN-Module 2 Notes VtuDocument12 pagesELN-Module 2 Notes VtuFariya TasneemNo ratings yet

- My Lec MOSFET All F MineDocument25 pagesMy Lec MOSFET All F MineArun JagaNo ratings yet

- Edc 4 UnitDocument26 pagesEdc 4 UnitAnonymous 6Ts3r7dwNo ratings yet

- MOSFET Physical Operation (Cont'd) MOSFET Current/Voltage CharacteristicsDocument16 pagesMOSFET Physical Operation (Cont'd) MOSFET Current/Voltage CharacteristicsSuleman KhanNo ratings yet

- Electronics Hons C3 FET Field Effect TransistorDocument21 pagesElectronics Hons C3 FET Field Effect TransistorGawrav BaishyaNo ratings yet

- Unit 2Document69 pagesUnit 2KISHAN SHUKLANo ratings yet

- Metal Oxide Semiconductor TransistorsDocument39 pagesMetal Oxide Semiconductor TransistorsK MukundNo ratings yet

- 30 Mosfet TheoryDocument6 pages30 Mosfet TheoryAruna KumarasiriNo ratings yet

- Chapter 10 Field Effect TransistorsDocument48 pagesChapter 10 Field Effect TransistorsanjugaduNo ratings yet

- Assignment 1Document9 pagesAssignment 1Taslima Rahman MiliNo ratings yet

- Chapter 4Document16 pagesChapter 4firomsaguteta12No ratings yet

- Field-Effect TransistorsDocument50 pagesField-Effect TransistorsMUHAMMAD SMITHNo ratings yet

- Electronics Chapter 4Document16 pagesElectronics Chapter 4YidnekachewNo ratings yet

- Mosfet SDocument25 pagesMosfet SZZZZZ5No ratings yet

- AnalogEl 2 FETDocument38 pagesAnalogEl 2 FETAlbert GenceNo ratings yet

- Unit 4 JFETDocument13 pagesUnit 4 JFETpranjaldesai453No ratings yet

- Mosfet Characteristics Mosfets Are Tri-Terminal, Unipolar, Voltage-Controlled, High Input Impedance DevicesDocument5 pagesMosfet Characteristics Mosfets Are Tri-Terminal, Unipolar, Voltage-Controlled, High Input Impedance DeviceseswaranNo ratings yet

- PH3007 Logic Families L 29 - 31Document33 pagesPH3007 Logic Families L 29 - 31Nethmi LokusuriyaNo ratings yet

- Controlled Devices FET, BJT, IGBTDocument51 pagesControlled Devices FET, BJT, IGBTHolloGramNo ratings yet

- FET TransistorsDocument19 pagesFET TransistorsOmer BallakNo ratings yet

- Mos Transistor TheoryDocument144 pagesMos Transistor TheorymailtolokiNo ratings yet

- Mosfet CharacteristicsDocument10 pagesMosfet CharacteristicsAnonymous eWMnRr70qNo ratings yet

- MOSFET Characteristics (ECE126: Laboratory 1)Document13 pagesMOSFET Characteristics (ECE126: Laboratory 1)Klinn Cabresos100% (1)

- Chapter 4 Ele IDocument16 pagesChapter 4 Ele Ibiruk satnawNo ratings yet

- Experiment 3: N-Channel Jfet Characteristics: ED Sem IiiDocument6 pagesExperiment 3: N-Channel Jfet Characteristics: ED Sem IiiDipankar PokhrelNo ratings yet

- Field Effect Transistors (FET) : Comparison Between BJT and FETDocument9 pagesField Effect Transistors (FET) : Comparison Between BJT and FETpranavraikar1No ratings yet

- Egr CycloidDocument1 pageEgr CycloidharshNo ratings yet

- MCQ Test Fac-Sy (Cca) : EmailDocument7 pagesMCQ Test Fac-Sy (Cca) : EmailharshNo ratings yet

- SY BTech CSE T4 Online Time TableDocument3 pagesSY BTech CSE T4 Online Time TableharshNo ratings yet

- Solid State NumericalsDocument4 pagesSolid State NumericalsharshNo ratings yet

- ECE Events ScheduleDocument1 pageECE Events ScheduleharshNo ratings yet

- Trimester II - DivB (ECE)Document1 pageTrimester II - DivB (ECE)harshNo ratings yet

- Experiment No: 01: Trimester: VI Subject: Communication SystemsDocument4 pagesExperiment No: 01: Trimester: VI Subject: Communication SystemsharshNo ratings yet

- Student Examination Manual - CodetantraDocument56 pagesStudent Examination Manual - CodetantraharshNo ratings yet

- Assignment 4 Implementation (PPS)Document8 pagesAssignment 4 Implementation (PPS)harshNo ratings yet

- IESA SAEISS Advanced Battery Technologies BrochureDocument1 pageIESA SAEISS Advanced Battery Technologies BrochureharshNo ratings yet

- Faculty of Engineering School of Polytechnic & Skill DevelopmentDocument3 pagesFaculty of Engineering School of Polytechnic & Skill DevelopmentharshNo ratings yet

- Op-Amps Experiment Theory: 1. ObjectiveDocument14 pagesOp-Amps Experiment Theory: 1. ObjectiveharshNo ratings yet

- FY SY TY Integrated B TechDocument1 pageFY SY TY Integrated B TechharshNo ratings yet

- Recitation 11: Small Signal Model of MOSFET/MOSFET in Digital CircuitsDocument9 pagesRecitation 11: Small Signal Model of MOSFET/MOSFET in Digital CircuitsharshNo ratings yet

- Homogeneous TransformDocument12 pagesHomogeneous TransformharshNo ratings yet

- Account Statement From 1 Apr 2019 To 31 Mar 2020: TXN Date Value Date Description Ref No./Cheque No. Debit Credit BalanceDocument3 pagesAccount Statement From 1 Apr 2019 To 31 Mar 2020: TXN Date Value Date Description Ref No./Cheque No. Debit Credit BalanceharshNo ratings yet

- MT-063 Tutorial: Basic Three Op Amp In-Amp ConfigurationDocument5 pagesMT-063 Tutorial: Basic Three Op Amp In-Amp ConfigurationharshNo ratings yet

- Booking Details: What Documents I Need To Board My Bus?Document2 pagesBooking Details: What Documents I Need To Board My Bus?harshNo ratings yet

- TD830Document47 pagesTD830edomaldoNo ratings yet

- Inversor - PV35 PRO - 6KDocument1 pageInversor - PV35 PRO - 6KPaolo Cesar Castro DiazNo ratings yet

- EGS300BS-6: Generator Set PerformanceDocument8 pagesEGS300BS-6: Generator Set PerformancefajarputraNo ratings yet

- DG Set PF CorrectionDocument22 pagesDG Set PF CorrectionPRIYANK ARORANo ratings yet

- IV Year Syllabus-2023-24Document34 pagesIV Year Syllabus-2023-24yashwanth h nNo ratings yet

- Diomedes: Inno Vation T Ha T Lif Tsy OuDocument2 pagesDiomedes: Inno Vation T Ha T Lif Tsy Outhanggimme.phanNo ratings yet

- ADC Lab3 PDFDocument11 pagesADC Lab3 PDFFarhan NitrateNo ratings yet

- Ikhtiyar Ali Khan PDFDocument2 pagesIkhtiyar Ali Khan PDFikhtiyar ali khan ikhtiyarNo ratings yet

- "Automatic Solar Energy Tracking System": Project Presentation ONDocument15 pages"Automatic Solar Energy Tracking System": Project Presentation ONPawan GuptaNo ratings yet

- Smoke Detector 2351EC HoneywellDocument2 pagesSmoke Detector 2351EC HoneywellFAMYA FIRE SAFETY SYSTEMSNo ratings yet

- 12V To 120V DC DC Converter Using Power Electronics For Higher Efficiency and Reliable Operation PDFDocument23 pages12V To 120V DC DC Converter Using Power Electronics For Higher Efficiency and Reliable Operation PDFAndy Espinosa GutiérrezNo ratings yet

- Lecture # 1Document28 pagesLecture # 1PhD EENo ratings yet

- Vin FastDocument4 pagesVin FastHạnh TrươngNo ratings yet

- Samson Servo 120 - Power Amplifier ManualDocument13 pagesSamson Servo 120 - Power Amplifier ManualTiestoworld CrewNo ratings yet

- Eee 2021Document16 pagesEee 2021Marami BaishyaNo ratings yet

- Weidmuller Cat10 ShortForm SmartDocument164 pagesWeidmuller Cat10 ShortForm SmartCesar Solis TarangoNo ratings yet

- Service Manual: CDX-L480XDocument40 pagesService Manual: CDX-L480XjohnnybiliNo ratings yet

- Silver Engineering Co Solar PanelDocument1 pageSilver Engineering Co Solar PanelPankaj JaiswalNo ratings yet

- Charger Ripple Current Effect v2Document4 pagesCharger Ripple Current Effect v2diyitNo ratings yet

- Simulation of Inverter Fed Induction Motor Drive With LabviewDocument5 pagesSimulation of Inverter Fed Induction Motor Drive With LabviewRAVIKANTH BALIVADANo ratings yet

- Payback CalculationDocument2 pagesPayback CalculationVenkat CherukuriNo ratings yet

- 1MRK511310-UUS A en Application Manual Bay Control REC670 2.0 ANSIDocument570 pages1MRK511310-UUS A en Application Manual Bay Control REC670 2.0 ANSIGilcimar DiasNo ratings yet

- Assignment Topics: Dominant ModeDocument67 pagesAssignment Topics: Dominant ModeXyzNo ratings yet

- Termistor NTC Mf73t-1Document4 pagesTermistor NTC Mf73t-1Tatys SoleNo ratings yet

- DatasheetDocument48 pagesDatasheetIng Salinas RodriguezNo ratings yet

- MTH 103e050719revisedDocument2 pagesMTH 103e050719revisedAchmad Jauhar EfendiNo ratings yet

- 01 Laboratory Exercise 2Document4 pages01 Laboratory Exercise 2ruzzelNo ratings yet

- F-MPC60B Series: User's ManualDocument146 pagesF-MPC60B Series: User's Manualpika100% (1)